## CY39C502/503/504

High Efficiency Step Down DC/DC Controller Datasheet

## Description

CY39C502 is a single output step down DC/DC controller using external FETs. It achieves the high efficiency with "Enhanced Low Power Mode (LPM) Operation" in light load. In Enhanced LPM, this controller operates that the quiescent current is reduced only 30µA and the switching frequency is fallen by extending on time. These operations enable to improve the efficiency in light load. Internal compensation circuit with current mode architecture and internal boost switch allow reducing the BOM parts and the component area.

## Features

- High Efficiency with Enhanced LPM Operation

- Automatic Transition for PFM/PWM

- Enhanced LPM Operation Transferred by SLP\_N Assertion

- Over Current Alerting

- Reference Voltage Accuracy: ±1%

- Output Voltage Range : 0.7V to 2

- : 0.7V to 2.0V (CY39C502) : 2.4V to 3.5V (CY39C503) : fixed 5V (CY39C504)

- VIN Input Voltage Range : 4.0V to 25V (CY39C502/C503) : 5.4V to 25V (CY39C504)

- VDD Input Voltage Range: 4.5V to 5.5V (CY39C502/C503)

- Internal 5V LDO with Switchover (CY39C504)

- Fixed Frequency Emulated On-Time Control: 800kHz

- Current Mode Architecture with Internal Compensation Circuit

- Internal Boost Switch

- Fixed 700µs Soft Start Time without Load Dependence

- Internal Discharge FET

- Power Good Monitor

- Enhanced Protection Functions: OVP, UVP, ILIM

- Thermal Shutdown

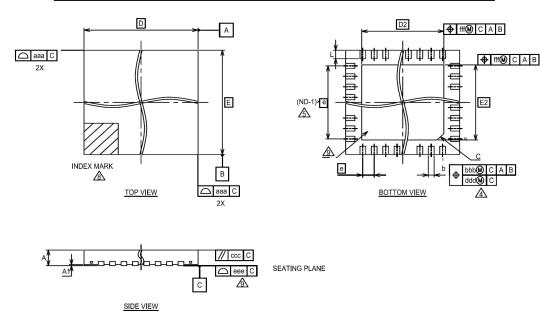

- Small 3mm × 3mm × 0.75mm QFN16 Package

## Applications

- Point of Load VR for Note PC

- General Purpose Step Down Regulator

## Contents

| 1.                                                                                                         | Typical Application                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.                                                                                                         | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                                                                                                                              |

| 3.                                                                                                         | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                              |

| 4.                                                                                                         | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                                                                              |

| 5.                                                                                                         | Absolute Maximum Rating                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                             |

| 6.                                                                                                         | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                             | .11                                                                                                                                            |

| 7.                                                                                                         | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                             |

| 8.                                                                                                         | Protections and Power Good function                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                                                                                             |

| 8.1<br>8.2                                                                                                 | Description<br>Timing Chart                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                |

| 9.                                                                                                         | Enhanced LPM Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                |

| 9.1<br>9.2<br>9.3<br><b>10.</b>                                                                            | Ultra Low Quiescent Current<br>Extended On Time<br>Timing Chart of Enhanced LPM<br>Over Current Alerting Description                                                                                                                                                                                                                                                                                                                                         | 28<br>29                                                                                                                                       |

| 11.                                                                                                        | Application Note                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                                                                             |

| 11.1<br>11.1.<br>11.1.<br>11.2<br>11.2                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31<br>31                                                                                                                                       |

| 11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.:<br>11.2.: | <ol> <li>Selection of Smoothing Inductor</li> <li>Selection of Switching FET</li> <li>Selection of Fly Back Diode</li> <li>Selection of Boost Diode</li> <li>Selection of Input Capacitor</li> <li>Selection of Output Capacitor</li> <li>Selection of Boost Capacitor</li> <li>Selection of VDD Capacitor</li> </ol>                                                                                                                                        | 32<br>33<br>35<br>35<br>36<br>37<br>38<br>39<br>39                                                                                             |

| 11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.                              | 1       Selection of Smoothing Inductor         2       Selection of Switching FET         3       Selection of Fly Back Diode         4       Selection of Boost Diode         5       Selection of Input Capacitor         6       Selection of Output Capacitor         7       Selection of Boost Capacitor         8       Selection of VDD Capacitor         9       Selection of VCC Capacitor and Resistor         Layout       Ordering Information | 32<br>33<br>35<br>35<br>36<br>37<br>38<br>39<br>39<br>40<br><b>43</b>                                                                          |

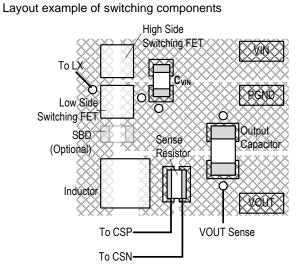

| 11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.2.<br>11.3             | <ol> <li>Selection of Smoothing Inductor</li> <li>Selection of Switching FET</li> <li>Selection of Fly Back Diode</li> <li>Selection of Boost Diode</li> <li>Selection of Input Capacitor</li> <li>Selection of Output Capacitor</li> <li>Selection of Boost Capacitor</li> <li>Selection of VDD Capacitor</li> <li>Selection of VCC Capacitor and Resistor</li> <li>Layout</li> </ol>                                                                       | <ul> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>36</li> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>43</li> <li>44</li> </ul> |

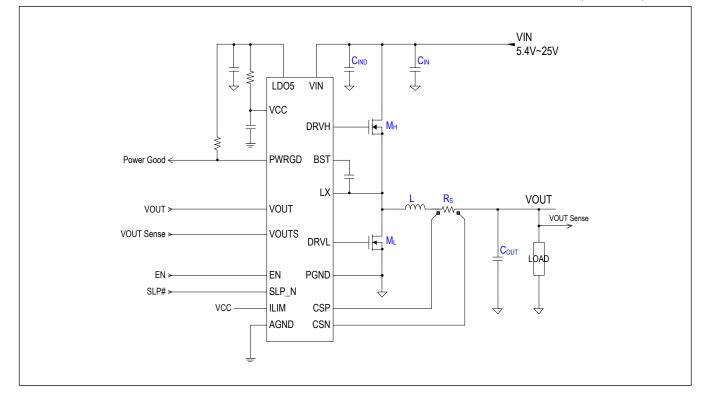

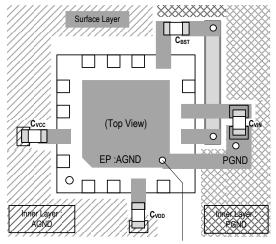

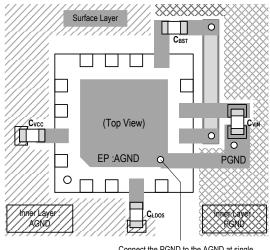

# 1. Typical Application

VIN V5 -4.0V~25V CIND Ţ Ş VDD VIN VCC ⊣<mark>⊾</mark> м<sub>н</sub> DRVH ≶ ş Power Good ← PWRGD BST ALERT\_N OC Alert ← LX Rs VOUT VOUT Sense > FB w VOUT Sense ╢┫ DRVL Соит LOAD PGND ΕN EN≯ SLP# > SLP\_N  $\checkmark$ VCC -ILIM CSP AGND CSN

# CY39C502/503/504

(CY39C504)

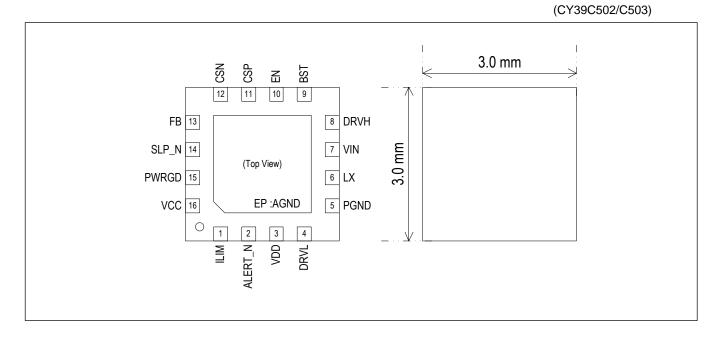

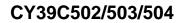

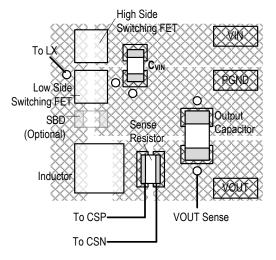

## 2. Pin Configuration

# CY39C502/503/504

(CY39C504)

# 3. Pin Configuration

(CY39C502/C503)

| Pin Number | Pin Name | I/O | Description                                                                                            |

|------------|----------|-----|--------------------------------------------------------------------------------------------------------|

| 1          | ILIM(*1) | I   | Connect to VCC terminal.                                                                               |

| 2          | ALERT_N  | 0   | Open drain output terminal with over current alerting.                                                 |

| 3          | VDD      | I   | Power supply voltage input terminal of switching FET gate driver.                                      |

| 4          | DRVL     | 0   | Low side switching FET gate driver output terminal.                                                    |

| 5          | PGND     | -   | Power ground.                                                                                          |

| 6          | LX       | -   | Inductor and high side switching FET source connection terminal.                                       |

| 7          | VIN      | I   | Power supply of switching regulator input terminal.                                                    |

| 8          | DRVH     | 0   | High side switching FET gate driver output terminal.                                                   |

| 9          | BST      | I   | Boost capacitor connection terminal.                                                                   |

|            |          |     | Enable input of PWM controller.                                                                        |

| 10         | EN       | I   | When turning on, apply greater than 0.65V and less than 5.5V. When turning off, apply less than 0.25V. |

| 11         | CSP      | I   | Current sensing positive input terminal.                                                               |

| 12         | CSN      | I   | Current sensing negative input terminal.                                                               |

| 13         | FB       | I   | Feedback voltage input of switching regulator.                                                         |

| 4.4        |          |     | Low power mode signal input terminal.                                                                  |

| 14         | SLP_N    | 1   | Transferred to low power mode by connecting to "L" level                                               |

| 15         | PWRGD    | 0   | Open drain output terminal with power good.                                                            |

| 16         | VCC      | I   | Power supply voltage input terminal of PWM controller.                                                 |

| EP         | AGND     | -   | Analog ground.                                                                                         |

\*1: ILIM terminal should be fixed to connect to VCC terminal.

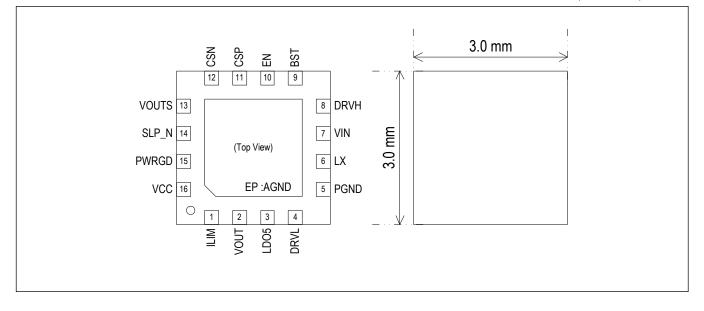

(CY39C504)

| Pin Number | Pin Name | I/O | Description                                                                                         |

|------------|----------|-----|-----------------------------------------------------------------------------------------------------|

| 1          | ILIM(*1) | 1   | Connect to VCC terminal whenever.                                                                   |

| 2          | VOUT     | 1   | DCDC output voltage input for switchover.                                                           |

| 3          | LDO5     | 0   | 5V LDO output terminal.                                                                             |

| 4          | DRVL     | 0   | Low side switching FET gate driver output terminal.                                                 |

| 5          | PGND     | -   | Power ground.                                                                                       |

| 6          | LX       | -   | Inductor and high side switching FET source connection terminal.                                    |

| 7          | VIN      | 1   | Power supply of switching regulator input terminal.                                                 |

| 8          | DRVH     | 0   | High side switching FET gate driver output terminal.                                                |

| 9          | BST      | 1   | Boost capacitor connection terminal.                                                                |

|            |          |     | Enable input of PWM controller.                                                                     |

| 10         | EN       | I   | When turning on, apply greater than 2.5V and less than 25V. When turning off, apply less than 0.6V. |

| 11         | CSP      | 1   | Current sensing positive input terminal.                                                            |

| 12         | CSN      | I   | Current sensing negative input terminal.                                                            |

| 13         | VOUTS    | 1   | DCDC output voltage input terminal.                                                                 |

|            |          |     | Low power mode signal input terminal.                                                               |

| 14         | SLP_N    | I   | Transferred to low power mode by connecting to "L" level                                            |

| 15         | PWRGD    | 0   | Open drain output terminal with power good.                                                         |

| 16         | VCC      | I   | Power supply voltage input terminal of PWM controller.                                              |

| EP         | AGND     | -   | Analog ground.                                                                                      |

\*1: ILIM terminal should be fixed to connect to VCC terminal.

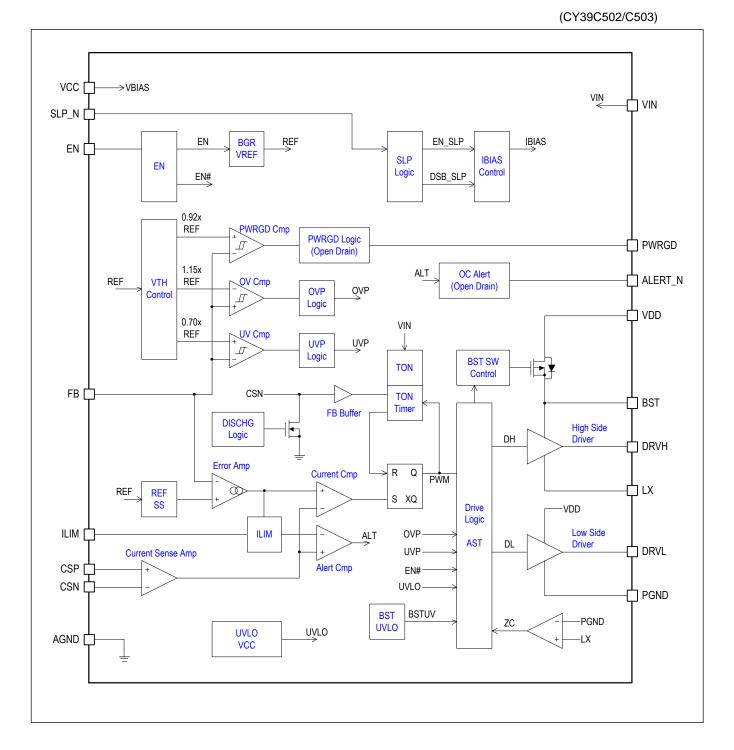

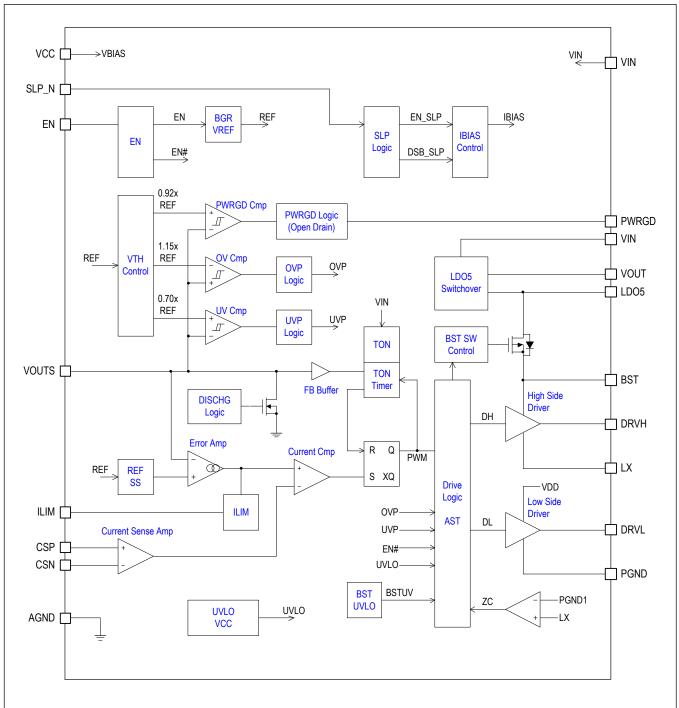

## 4. Block Diagram

# CY39C502/503/504

## 5. Absolute Maximum Ratings

|                      |                       |                                                 | (CY39C502 | 2/C503/C504)          |      |  |

|----------------------|-----------------------|-------------------------------------------------|-----------|-----------------------|------|--|

| Demonster            | Cumula al             | Condition                                       |           | Unit                  |      |  |

| Parameter            | Symbol                | Condition                                       | Min       | Max                   | Unit |  |

|                      | V <sub>VIN</sub>      | VIN input voltage                               | -0.3      | +28                   | V    |  |

| Development          | V <sub>VCC</sub>      | VCC input voltage                               | -0.3      | +6.5                  | V    |  |

| Power supply voltage | V <sub>VDD</sub>      | VDD input voltage (CY39C502/C503)               | -0.3      | +6.5                  | V    |  |

|                      | V <sub>VOUT</sub>     | VOUT input voltage (CY39C504)                   | -0.3      | +6.5                  | V    |  |

|                      | V <sub>BST</sub>      | BST bias voltage                                | -0.3      | +34.5                 | V    |  |

|                      | V <sub>LX</sub>       | LX switching voltage                            | -2        | +28                   | V    |  |

|                      | V <sub>FB</sub>       | FB input voltage (CY39C502/C503)                | -0.3      | V <sub>VCC</sub> +0.3 | V    |  |

|                      | V <sub>VOUTS</sub>    | VOUTS input voltage                             | -0.3      | +6.5                  | V    |  |

| <b>-</b>             | VINPUT                | ILIM input voltage                              | -0.3      | V <sub>VCC</sub> +0.3 | V    |  |

| Terminal voltage     | V <sub>cs</sub>       | CSP, CSN input voltage                          | -0.3      | +6.5                  | V    |  |

|                      | V <sub>EN</sub>       | EN input voltage (CY39C502/C503)                | -0.3      | +6.5                  | V    |  |

|                      |                       | EN input voltage (CY39C504)                     | -0.3      | +28                   | V    |  |

|                      | V <sub>SLP</sub>      | SLP_N input voltage                             | -0.3      | +6.5                  | V    |  |

|                      | V <sub>NOD</sub>      | PWRGD, ALERT_N bias voltage                     | -0.3      | +6.5                  | V    |  |

|                      | V <sub>BST-LX</sub>   | BST–LX difference voltage                       | -0.3      | +6.5                  | V    |  |

|                      | V <sub>BST-VDD</sub>  | BST–VDD difference voltage<br>(CY39C502/C503)   | -         | +28                   | V    |  |

| Difference voltage   | V <sub>BST-LDO5</sub> | BST–VOUT, LDO5 difference voltage<br>(CY39C504) | -         | +28                   | V    |  |

|                      | V <sub>GND</sub>      | AGND–PGND difference voltage                    | -0.3      | +0.3                  | V    |  |

|                      | V <sub>CSP-CSN</sub>  | CSP–CSN difference voltage                      | -0.3      | +0.3                  | V    |  |

|                      | I <sub>DRV</sub>      | DRVH, DRVL DC current                           | -60       | +60                   | mA   |  |

| Output current       | I <sub>NOD</sub>      | PWRGD                                           | -         | +2                    | mA   |  |

|                      | I <sub>ALERT</sub>    | ALERT_N sink current (CY39C502/C503)            | -         | +2                    | mA   |  |

| Power dissipation    | P <sub>D</sub>        | Ta ≤ ±25°C                                      | -         | 2100(*1)              | mW   |  |

| Storage temperature  | T <sub>STG</sub>      | -                                               | -55       | +125                  | °C   |  |

\*1: When the IC is mounted on 10cm × 10cm four-layer square epoxy board. IC is mounted on a four-layer epoxy board, which terminal bias, and the IC's thermal pad is connected to the epoxy board.

### WARNING

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# 6. Recommended Operating Conditions

| Parameter                        | Quert at              | Symbol Condition                                 |         | 11   |                  |      |

|----------------------------------|-----------------------|--------------------------------------------------|---------|------|------------------|------|

|                                  | Symbol                |                                                  | Min     | Тур  | Max              | Unit |

|                                  | V <sub>VIN</sub>      | VIN input voltage (CY39C502/C503)                | 4.0     | -    | 25               | V    |

|                                  | V <sub>VIN</sub>      | VIN input voltage (CY39C504)                     | 5.4     | -    | 25               | V    |

| D                                | V <sub>vcc</sub>      | VCC input voltage                                | 4.5     | -    | 5.5              | V    |

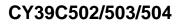

| Power supply voltage             | V <sub>VDD</sub>      | VDD input voltage (CY39C502)                     | 4.5(*1) | -    | 5.5              | V    |

|                                  | V <sub>VDD</sub>      | VDD input voltage (CY39C503)                     | 4.5     | -    | 5.5              | V    |

|                                  | V <sub>LDO5</sub>     | VOUT input voltage (CY39C504)                    | 4.5     | -    | 5.5              | V    |

|                                  | V <sub>BST</sub>      | BST bias voltage                                 | 0       | -    | 30.5             | V    |

|                                  | V <sub>LX</sub>       | LX switching voltage                             | -1      | -    | 25               | V    |

|                                  | V <sub>INPUT</sub>    | FB, ILIM input voltage<br>(CY39C502/C503)        | 0       | -    | V <sub>VCC</sub> | V    |

|                                  | VINPUT                | ILIM input voltage (CY39C504)                    | 0       | -    | V <sub>VCC</sub> | V    |

|                                  | V <sub>cs</sub>       | CSP, CSN input voltage (CY39C502)                | 0       | -    | 2.0              | V    |

|                                  | V <sub>cs</sub>       | CSP, CSN input voltage (CY39C503)                | 0       | -    | 3.5              | V    |

| Terminal voltage                 | V <sub>cs</sub>       | CSP, CSN, VOUTS input voltage<br>(CY39C504)      | 0       | -    | 5.5              | V    |

|                                  | V <sub>EN</sub>       | EN, SLP_N input voltage<br>(CY39C502/C503)       | 0       | -    | 5.5              | V    |

|                                  | V <sub>EN</sub>       | EN input voltage (CY39C504)                      | 0       | -    | 25               | V    |

|                                  | V <sub>SLP</sub>      | SLP_N input voltage (CY39C504)                   | 0       | -    | 5.5              | V    |

|                                  | V <sub>NOD</sub>      | PWRGD, ALERT_N bias voltage<br>(CY39C502/C503)   | 0       | -    | 5.5              | V    |

|                                  | V <sub>NOD</sub>      | PWRGD bias voltage (CY39C504)                    | 0       | -    | 5.5              | V    |

|                                  | V <sub>BST-LX</sub>   | BST-LX difference voltage                        | 0       | -    | 5.5              | V    |

|                                  | V <sub>BST-VDD</sub>  | BST–VDD difference voltage<br>(CY39C502/C503)    | -       | -    | 25               | V    |

| Difference voltage               | V <sub>BST-LDO5</sub> | BST–VOUT, LDO5 difference voltage (CY39C504)     | -       | -    | 25               | V    |

|                                  | V <sub>GND</sub>      | AGND–PGND difference voltage                     | -0.05   | -    | 0.05             | V    |

|                                  | V <sub>CSP-CSN</sub>  | CSP–CSN difference voltage                       | 0       | -    | 35               | mV   |

| 0.1                              | I <sub>DRV</sub>      | DRVH, DRVL DC current                            | -45     | -    | 45               | mA   |

| Output current                   | I <sub>NOD</sub>      | PWRGD, ALERT_N sink current                      | -       | -    | 1                | mA   |

| BST capacitor                    | C <sub>BST</sub>      | Connect BST to LX capacitor                      | -       | 0.47 | -                | μF   |

| VCC capacitor                    | C <sub>VCC</sub>      | Connect VCC to AGND capacitor                    | -       | 1.0  | -                | μF   |

| VDD capacitor                    | C <sub>VDD</sub>      | Connect VDD to PGND capacitor<br>(CY39C502/C503) | -       | 4.7  | -                | μF   |

| LDO5 capacitor                   | C <sub>LDO5</sub>     | Connect LDO5 to PGND capacitor(CY39C504)         | -       | 4.7  | -                | μF   |

| Operating ambient<br>temperature | T <sub>A</sub>        | Ambient temperature                              | -30     | -    | 85               | °C   |

\*1: This VDD minimum input voltage indicates dynamic input range below 1ms. Refer to figure (next page) about the static VDD minimum input voltage.

### WARNING

- The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

- Always use semiconductor devices within their recommended operating condition ranges.

- Operation outside these ranges may adversely affect reliability and could result in device failure.

- No warranty is made with respect to use, conditions, or combinations not represented on the data sheet. Users

considering application outside the listed conditions are advised to contact their representatives beforehand.

## 7. Electrical Characteristics

## (CY39C502)

VIN = 7.4V, VDD, BST and EN connect to 5V power supply, PGND, LX = 0V.  $T_A = -30^{\circ}C$  to +85°C, unless otherwise noted.

| Deremeter                  |                     |                                                                                                        |       | Value |       |      |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Parameter                  | Symbol              | Condition                                                                                              | Min   | Тур   | Max   | Unit |

|                            |                     | REFERENCE VOLTAGE                                                                                      |       | •     |       | •    |

| Internal reference voltage | V <sub>REE</sub>    | This voltage is compared to feedback voltage. Ta = $25^{\circ}$ C                                      | 0.693 | 0.700 | 0.707 | V    |

| Ũ                          |                     | $Ta = -10^{\circ}C$ to $85^{\circ}C$                                                                   | 0.686 | -     | 0.714 | V    |

| FB input current           | I <sub>FB</sub>     | VFB = 1.0V                                                                                             | -0.1  | -     | 0.1   | μA   |

|                            |                     | ENABLE, SLP_N                                                                                          |       |       |       |      |

| Fachle condition           | V <sub>EN</sub>     | Enable voltage range                                                                                   | 0.65  | -     | 5.5   | V    |

| Enable condition           | V <sub>DSB</sub>    | Disable voltage range                                                                                  | 0     | -     | 0.25  | V    |

| EN input current           | I <sub>EN</sub>     | V <sub>EN</sub> = 5.0V                                                                                 | -     | 0     | 0.1   | μA   |

|                            | V <sub>SLPDSB</sub> | LPM disable voltage range                                                                              | 0.65  | -     | 5.5   | V    |

| SLP_N enable condition     | V <sub>SLPEN</sub>  | LPM enable voltage range                                                                               | 0     | -     | 0.35  | V    |

| SLP_N input current        | I <sub>SLP_N</sub>  | $V_{SLP_N} = 5.0V$                                                                                     | -     | 0     | 0.1   | μA   |

|                            |                     | SUPPLY CURRENT                                                                                         | •     |       | •     | •    |

|                            | I <sub>VDDPWM</sub> | VDD, VCC input current at PWM operating. $T_A = 25^{\circ}C$                                           | -     | 380   | 760   | μA   |

| VDD supply current         | I <sub>VDDPFM</sub> | VDD, VCC input current at idle state in PFM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 180   | 360   | μA   |

|                            | I <sub>VDDLPM</sub> | VDD, VCC input current at idle state in LPM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 30    | 60    | μA   |

| VDD shutdown current       |                     | VDD, VCC input current at $V_{EN} = 0V$                                                                | -     | 0.1   | 1.0   | μA   |

| VIN supply current         | I <sub>VIN</sub>    | V <sub>VIN</sub> = 25V                                                                                 | -     | 10    | 15    | μA   |

| VIN shutdown current       | I <sub>VINSDN</sub> | VIN input current at V <sub>EN</sub> = 0V                                                              | -     | 0.1   | 1.0   | μA   |

|                            |                     | UNDER VOLTAGE LOCKOUT                                                                                  |       | 1     |       |      |

|                            | V <sub>UVLO</sub>   | UVLO release voltage                                                                                   | 3.99  | 4.14  | 4.29  | V    |

| VCC UVLO threshold         | V <sub>HYS</sub>    | Hysteresis                                                                                             | 0.005 | 0.070 | 0.200 | V    |

|                            | •                   | SOFT START, DISCHARGE                                                                                  | •     |       | •     |      |

| Period of power on reset   | t <sub>POR</sub>    | From enable ON to the switching initiating.                                                            | 200   | -     | 1000  | μs   |

| Ramp up time               | t <sub>ss</sub>     | From the switching initiating after<br>enable ON to the output voltage<br>reaches 95%.                 | 598   | 665   | 732   | μs   |

| Discharge resistance       | R <sub>DISCHG</sub> | VOUT = 0.2V, discharge enable.                                                                         | 50    | 100   | 200   | Ω    |

| Discharge ends voltage     | V <sub>DISCHG</sub> | V <sub>CSN</sub> voltage.                                                                              | 0.07  | 0.10  | 0.13  | V    |

|                                       | -                   |                                                              |       | (CY39C  | 502) |      |

|---------------------------------------|---------------------|--------------------------------------------------------------|-------|---------|------|------|

| Parameter                             | Symbol              | Condition                                                    | Value |         |      | Unit |

| Faianletei                            | Cymbol              | Condition                                                    | Min   | Тур     | Max  | Unit |

|                                       |                     | ON TIMER                                                     |       |         |      |      |

| On time                               | t <sub>ON</sub>     | $V_{VIN} = 7.4V, V_{CSN} = 1.2V$                             | 193   | 210     | 227  | ns   |

| Minimum on time                       | t <sub>MINON</sub>  | $V_{VIN}=7.4V,V_{CSN}=0.2V$                                  | 80    | 120     | -    | ns   |

| Minimum off time                      | t <sub>MINOFF</sub> |                                                              | -     | 200     | 400  | ns   |

|                                       |                     | CURRENTLIMITATION                                            |       |         |      |      |

| Current limitation threshold          | V <sub>ILIMIT</sub> | CSP–CSN difference voltage at ILIM connects to VCC.          | 19.0  | 24.0    | 29.0 | mV   |

| ILIM input current                    | I <sub>ILIM</sub>   | $V_{ILIM} = 5.0V$                                            | -     | 0       | 0.1  | μA   |

| CSP, CSN input current                | I <sub>cs</sub>     | $V_{CS} = 1.2V$                                              | -5.0  | -2.0    | -    | μA   |

|                                       |                     | OVER AND UNDER VOLTAGE PROTEC                                | TION  |         |      |      |

| Over voltage threshold ratio          | RT <sub>ov</sub>    | For target output voltage. At output voltage increasing.     | 110   | 115     | 125  | %    |

| Propagation delay of OV               | t <sub>ov</sub>     | -                                                            | 4     | 10      | 25   | μs   |

| Under voltage threshold ratio         | RT <sub>UV</sub>    | For target output voltage. At output voltage decreasing.     | 65    | 70      | 75   | %    |

| Propagation delay of UV               | t <sub>UV</sub>     | -                                                            | 40    | 100     | 200  | μs   |

| POWER GOOD MONITOR                    | •                   | ·                                                            |       |         |      |      |

| Power good threshold ratio            | RT <sub>PG</sub>    | For target output voltage. At output voltage increasing.     | 86    | 92      | 98   | %    |

| Hysteresis Ratio                      | RT <sub>HYS</sub>   | -                                                            | 3     | 5       | 7    | %    |

| Dropogation dolou                     | t <sub>PG</sub>     | Power good                                                   | 20    | 50      | 200  | μs   |

| Propagation delay                     | t <sub>PB</sub>     | Power bad                                                    | 4     | 10      | 25   | μs   |

| PWRGD leak current                    | I <sub>LKPG</sub>   | $V_{PWRGD} = 5.5V$                                           | -     | 0       | 1    | μA   |

| PWRGD output voltage "L" level        | V <sub>OLPG</sub>   | I <sub>PWRGD</sub> = 1mA sink                                | -     | 0.05    | 0.10 | V    |

|                                       |                     | THERMAL SHUT DOWN                                            |       |         |      |      |

|                                       | T <sub>TSDH</sub>   | Shut down temperature.                                       | -     | 150(*1) | -    | °C   |

| Shut down temperature                 | T <sub>TSDL</sub>   | Exited temperature from thermal shut down state.             | -     | 125(*1) | -    | °C   |

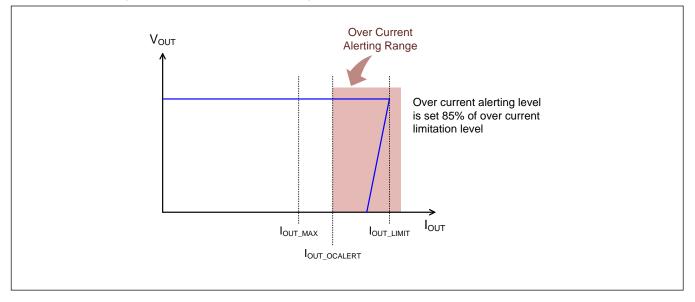

|                                       |                     | OVER CURRENT ALERTING                                        |       |         |      |      |

| Over current alerting threshold ratio | RT <sub>ALT</sub>   | For target current limitation. At output current increasing. | 78    | 85      | 92   | %    |

| Propagation delay                     | t <sub>ALTON</sub>  | On alerting assertion                                        | 20    | 50      | 200  | μs   |

| Propagation delay                     | t <sub>ALTOFF</sub> | On alerting de-assertion                                     | 3     | 10      | 25   | μs   |

| ALERT_N leak current                  | I <sub>lkalt</sub>  | $V_{ALERT_N} = 5.5V$                                         | -     | 0       | 1    | μA   |

| ALERT_N output voltage "L" level      | V <sub>OLALT</sub>  | I <sub>ALERT_N</sub> = 1mA sink                              | -     | 0.05    | 0.10 | V    |

\*1: No production tested, ensure by design.

|                            |                    |                                                        |       |          | •   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|----------------------------|--------------------|--------------------------------------------------------|-------|----------|-----|-----------------------------------------|

| Parameter                  | 0 milion           | O an dition                                            | Value |          |     |                                         |

|                            | Symbol             | Condition                                              | Min   | Тур      | Max | Unit                                    |

|                            | -                  | DRIVER                                                 |       |          |     |                                         |

| High side on registeres    | R <sub>HOH</sub>   | At 100mA current sourcing                              | -     | 3(*1)    | -   | Ω                                       |

| High side on resistance    | R <sub>HOL</sub>   | At 100mA current sinking                               | -     | 1(*1)    | -   | Ω                                       |

| Low side on registeres     | R <sub>LOH</sub>   | At 100mA current sourcing                              | -     | 4(*1)    | -   | Ω                                       |

| Low side on resistance     | R <sub>LOL</sub>   | At 100mA current sinking                               | -     | 0.75(*1) | -   | Ω                                       |

| High side source current   | I <sub>SRCH</sub>  | $V_{DRVH} = 2.5V$                                      | -     | 0.7(*1)  | -   | А                                       |

| High side sink current     | I <sub>SINKH</sub> | $V_{DRVH} = 2.5V$                                      | -     | 1.1(*1)  | -   | А                                       |

| Low side source current    | I <sub>SRCL</sub>  | $V_{DRVL} = 2.5V$                                      | -     | 0.5(*1)  | -   | А                                       |

| Low side sink current      | I <sub>SINKL</sub> | $V_{DRVL} = 2.5V$                                      | -     | 1.7(*1)  | -   | А                                       |

| Dead time                  | t <sub>DEAD</sub>  | From DRVH turn off to DRVL turn on.<br>And reverse it. | 10    | 20       | -   | ns                                      |

|                            |                    | BOOST SWITCH                                           |       |          |     |                                         |

| Boost switch on resistance | R <sub>BST</sub>   | I <sub>BST</sub> = 10mA                                | -     | 30       | 50  | Ω                                       |

| BST leak current           | I <sub>LKBST</sub> | V <sub>BST</sub> = 30V                                 | -     | 0.1      | 1.0 | μA                                      |

\*1: No production tested, ensure by design.

(CY39C502)

|                            |                     |                                                                                                        |       | (CY390     | -505) |       |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------------------|-------|------------|-------|-------|

| Demonstern                 | 0 milest            | O an dition                                                                                            |       | Value      |       | 11-24 |

| Parameter                  | Symbol              | Symbol Condition Mir                                                                                   |       | Тур        | Max   | Unit  |

|                            |                     | REFERENCE VOLTAGE                                                                                      |       |            |       |       |

| Internal reference voltage | V <sub>REF</sub>    | This voltage is compared to feedback voltage. Ta = 25°C                                                | 0.99  | 1.00       | 1.01  | V     |

| -                          |                     | Ta = -10°C to 85°C                                                                                     | 0.98  | -          | 1.02  | V     |

| FB input current           | I <sub>FB</sub>     | VFB = 1.0V                                                                                             | -0.1  | -          | 0.1   | μA    |

|                            |                     | ENABLE, SLP_N                                                                                          |       |            |       |       |

| Enchla condition           | V <sub>EN</sub>     | Enable voltage range                                                                                   | 0.65  | -          | 5.5   | V     |

| Enable condition           | V <sub>DSB</sub>    | Disable voltage range                                                                                  | 0     | -          | 0.25  | V     |

| EN input current           | I <sub>EN</sub>     | V <sub>EN</sub> = 5.0V                                                                                 | -     | 0          | 0.1   | μA    |

|                            | V <sub>SLPDSB</sub> | LPM disable voltage range                                                                              | 0.65  | -          | 5.5   | V     |

| SLP_N enable condition     | V <sub>SLPEN</sub>  | LPM enable voltage range                                                                               | 0     | -          | 0.35  | V     |

| SLP_N input current        | I <sub>SLP_N</sub>  | $V_{SLP_N} = 5.0V$                                                                                     | -     | 0          | 0.1   | μA    |

|                            |                     | SUPPLY CURRENT                                                                                         |       |            |       |       |

|                            |                     | VDD, VCC input current at PWM operating. $T_A = 25^{\circ}C$                                           | -     | 380        | 760   | μΑ    |

| VDD supply current         | I <sub>VDDPFM</sub> | VDD, VCC input current at idle state in PFM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 180        | 360   | μΑ    |

|                            | Ivddlpm             | VDD, VCC input current at idle state in LPM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 30         | 60    | μΑ    |

| VDD shutdown current       | IVDDSDN             | VDD, VCC input current at $V_{EN} = 0V$                                                                | -     | 0.1        | 1.0   | μA    |

| VIN supply current         | I <sub>VIN</sub>    | $V_{VIN} = 25V$                                                                                        | -     | 10         | 15    | μA    |

| VIN shutdown current       | I <sub>VINSDN</sub> | VIN input current at $V_{EN} = 0V$                                                                     | -     | 0.1        | 1.0   | μA    |

|                            |                     | UNDER VOLTAGE LOCKOUT                                                                                  |       |            |       |       |

|                            | V <sub>UVLO</sub>   | UVLO release voltage                                                                                   | 3.99  | 4.14       | 4.29  | V     |

| VCC UVLO threshold         | V <sub>HYS</sub>    | Hysteresis                                                                                             | 0.005 | 0.070      | 0.200 | V     |

|                            |                     | SOFT START, DISCHARGE                                                                                  |       | - <b>·</b> | ·     |       |

| Period of power on reset   | t <sub>POR</sub>    | From enable ON to the switching initiating.                                                            | 200   | -          | 1000  | μs    |

| Ramp up time               | t <sub>SS</sub>     | From the switching initiating after<br>enable ON to the output voltage<br>reaches 95%.                 | 598   | 665        | 732   | μs    |

| Discharge resistance       | R <sub>DISCHG</sub> | VOUT = 0.2V, discharge enable.                                                                         | 50    | 100        | 200   | Ω     |

| Discharge ends voltage     | V <sub>DISCHG</sub> | V <sub>CSN</sub> voltage.                                                                              | 0.07  | 0.10       | 0.13  | V     |

|                                       |                     |                                                              |       | (CY39C  | )    |      |

|---------------------------------------|---------------------|--------------------------------------------------------------|-------|---------|------|------|

| Parameter                             | Symbol              | Condition                                                    | Value |         |      | Unit |

|                                       |                     |                                                              | Min   | Тур     | Max  |      |

| ON TIMER                              |                     | 1                                                            |       |         |      |      |

| On time                               | t <sub>on</sub>     | $V_{VIN} = 7.4V, V_{CSN} = 3.3V$                             | 529   | 575     | 621  | ns   |

| Minimum on time                       | t <sub>MINON</sub>  | $V_{VIN} = 7.4V, V_{CSN} = 0.2V$                             | 100   | 200     |      | ns   |

| Minimum off time                      | t <sub>MINOFF</sub> | -                                                            |       | 90      | 180  | ns   |

|                                       |                     | CURRENTLIMITATION                                            |       |         |      |      |

| Current limitation threshold          | VILIMIT             | CSP–CSN difference voltage at ILIM connects to VCC.          | 21.0  | 26.0    | 31.0 | mV   |

| ILIM input current                    | I <sub>ILIM</sub>   | $V_{ILIM} = 5.0V$                                            | -     | 0       | 0.1  | μA   |

| CSP input current                     | I <sub>CSP</sub>    | $V_{CSP} = 3.3V$                                             | -     | 2.0     | 5.0  | μA   |

| CSN input current                     | I <sub>CSN</sub>    | $V_{CSP} = 3.3V$                                             | -     | 8.0     | 20.0 | μA   |

|                                       |                     | OVER AND UNDER VOLTAGE PROTEC                                | TION  |         | ·    | •    |

| Over voltage threshold ratio          | RT <sub>ov</sub>    | For target output voltage. At output voltage increasing.     | 110   | 115     | 125  | %    |

| Propagation delay of OV               | t <sub>ov</sub>     | -                                                            | 4     | 10      | 25   | μs   |

| Under voltage threshold ratio         | RT <sub>uv</sub>    | For target output voltage. At output voltage decreasing.     | 65    | 70      | 75   | %    |

| Propagation delay of UV               | t <sub>UV</sub>     | -                                                            | 40    | 100     | 200  | μs   |

|                                       |                     | POWER GOOD MONITOR                                           |       | •       | •    | •    |

| Power good threshold ratio            | RT <sub>PG</sub>    | For target output voltage. At output voltage increasing.     | 86    | 92      | 98   | %    |

| Hysteresis Ratio                      | RT <sub>HYS</sub>   | -                                                            | 3     | 5       | 7    | %    |

| Dress exetting delay                  | t <sub>PG</sub>     | Power good                                                   | 20    | 50      | 200  | μs   |

| Propagation delay                     | t <sub>PB</sub>     | Power bad                                                    | 4     | 10      | 25   | μs   |

| PWRGD leak current                    | I <sub>LKPG</sub>   | V <sub>PWRGD</sub> = 5.5V                                    | -     | 0       | 1    | μA   |

| PWRGD output voltage "L" level        | V <sub>OLPG</sub>   | I <sub>PWRGD</sub> = 1mA sink                                | -     | 0.05    | 0.10 | V    |

|                                       |                     | THERMAL SHUT DOWN                                            |       | •       | •    | •    |

|                                       | T <sub>TSDH</sub>   | Shut down temperature.                                       | -     | 150(*1) | -    | °C   |

| Shut down temperature                 | T <sub>TSDL</sub>   | Exited temperature from thermal shut down state.             | -     | 125(*1) | -    | °C   |

|                                       |                     | OVER CURRENT ALERTING                                        |       | •       | •    | •    |

| Over current alerting threshold ratio | RT <sub>ALT</sub>   | For target current limitation. At output current increasing. | 78    | 85      | 92   | %    |

| Development in a state of             | t <sub>ALTON</sub>  | On alerting assertion                                        | 20    | 50      | 200  | μs   |

| Propagation delay                     | t <sub>ALTOFF</sub> | On alerting de-assertion                                     | 3     | 10      | 25   | μs   |

| ALERT_N leak current                  | I <sub>lkalt</sub>  | $V_{ALERT_N} = 5.5V$                                         | -     | 0       | 1    | μA   |

| ALERT_N output voltage "L" level      | V <sub>OLALT</sub>  | I <sub>ALERT_N</sub> = 1mA sink                              | -     | 0.05    | 0.10 | V    |

\*1: No production tested, ensure by design.

|                            |                    |                                                        |     | (CY39C   | 503) |      |

|----------------------------|--------------------|--------------------------------------------------------|-----|----------|------|------|

| <b>-</b>                   |                    | Symbol                                                 |     |          |      |      |

| Parameter                  | Symbol             | Condition                                              | Min | Тур      | Max  | Unit |

|                            |                    | DRIVER                                                 |     |          |      |      |

| Lligh aide en registence   | R <sub>HOH</sub>   | At 100mA current sourcing                              | -   | 3(*1)    | -    | Ω    |

| High side on resistance    | R <sub>HOL</sub>   | At 100mA current sinking                               | -   | 1(*1)    | -    | Ω    |

| Low oldo on registeres     | R <sub>LOH</sub>   | At 100mA current sourcing                              | -   | 4(*1)    | -    | Ω    |

| Low side on resistance     | R <sub>LOL</sub>   | At 100mA current sinking                               | -   | 0.75(*1) | -    | Ω    |

| High side source current   | I <sub>SRCH</sub>  | $V_{DRVH} = 2.5V$                                      | -   | 0.7(*1)  | -    | А    |

| High side sink current     | I <sub>SINKH</sub> | $V_{DRVH} = 2.5V$                                      | -   | 1.1(*1)  | -    | А    |

| Low side source current    | I <sub>SRCL</sub>  | $V_{DRVL} = 2.5V$                                      | -   | 0.5(*1)  | -    | А    |

| Low side sink current      | I <sub>SINKL</sub> | $V_{DRVL} = 2.5V$                                      | -   | 1.7(*1)  | -    | А    |

| Dead time                  | t <sub>DEAD</sub>  | From DRVH turn off to DRVL turn on.<br>And reverse it. | 10  | 20       | -    | ns   |

|                            |                    | BOOST SWITCH                                           |     |          |      |      |

| Boost switch on resistance | R <sub>BST</sub>   | I <sub>BST</sub> = 10mA                                | -   | 30       | 50   | Ω    |

| BST leak current           | I <sub>LKBST</sub> | V <sub>BST</sub> = 30V                                 | -   | 0.1      | 1.0  | μA   |

\*1: No production tested, ensure by design.

|                            |                      |                                                                                                         |       |       | (CY39C | 504) |

|----------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-------|-------|--------|------|

| Parameter                  | Symbol               | Condition                                                                                               | Value |       |        | Unit |

| Parameter                  | Symbol               | Condition                                                                                               | Min   | Тур   | Max    | Unit |

|                            |                      | REFERENCE VOLTAGE                                                                                       |       |       |        |      |

| Internal reference voltage | V <sub>REF</sub>     | This voltage is compared to feedback voltage. Ta = 25°C                                                 | 4.95  | 5.00  | 5.05   | V    |

|                            |                      | $Ta = -10^{\circ}C$ to $85^{\circ}C$                                                                    | 4.90  | -     | 5.10   | V    |

| VOUTS input current        | I <sub>VOUTS</sub>   | V <sub>VOUTS</sub> = 5.0V                                                                               | 2.5   | 5.0   | 12.5   | μA   |

|                            | •                    | ENABLE, SLP_N                                                                                           |       |       |        |      |

|                            | V <sub>EN</sub>      | Enable voltage range                                                                                    | 2.5   | -     | 25     | V    |

| Enable condition           | V <sub>DSB</sub>     | Disable voltage range                                                                                   | 0     | -     | 0.6    | V    |

| EN input current           | I <sub>EN</sub>      | $V_{EN} = 5.0V$                                                                                         | -     | 0.5   | 1.2    | μA   |

|                            | V <sub>SLPDSB</sub>  | LPM disable voltage range                                                                               | 0.65  | -     | 5.5    | V    |

| SLP_N enable condition     | V <sub>SLPEN</sub>   | LPM enable voltage range                                                                                | 0     | -     | 0.35   | V    |

| SLP_N input current        | I <sub>SLP_N</sub>   | $V_{SLP_N} = 5.0V$                                                                                      | -     | 0     | 0.1    | μA   |

|                            |                      | SUPPLY CURRENT                                                                                          | •     | •     | •      |      |

|                            | I <sub>VOUTPWM</sub> | VOUT, VCC input current at PWM operating. $T_A = 25^{\circ}C$                                           | -     | 400   | 800    | μΑ   |

| VOUT supply current        | I <sub>VOUTPFM</sub> | VOUT, VCC input current at idle state in PFM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 200   | 400    | μΑ   |

|                            | Ivoutlpm             | VOUT, VCC input current at idle state in LPM operation. Static 0A inductor current. $T_A = 25^{\circ}C$ | -     | 50    | 100    | μA   |

| VOUT shutdown current      | IVOUTSDN             | VOUT, VCC input current at $V_{EN} = 0V$                                                                | -     | 0.1   | 1.0    | μA   |

| VIN supply current         | I <sub>VIN</sub>     | $V_{VIN} = 25V$                                                                                         | -     | 20    | 30     | μA   |

| VIN shutdown current       | I <sub>VINSDN</sub>  | VIN input current at $V_{EN} = 0V$                                                                      | -     | 0.1   | 1.0    | μA   |

| UNDER VOLTAGE LOCKO        | UT                   |                                                                                                         |       |       |        |      |

|                            | V <sub>UVLO</sub>    | UVLO release voltage                                                                                    | 3.99  | 4.14  | 4.29   | V    |

| VCC UVLO threshold         | V <sub>HYS</sub>     | Hysteresis                                                                                              | 0.005 | 0.070 | 0.200  | V    |

|                            |                      | SOFT START, DISCHARGE                                                                                   |       |       |        |      |

| Period of power on reset   | t <sub>POR</sub>     | From enable ON to the switching initiating.                                                             | 300   | -     | 1400   | μs   |

| Ramp up time               | t <sub>ss</sub>      | From the switching initiating after<br>enable ON to the output voltage<br>reaches 95%.                  | 598   | 665   | 732    | μs   |

| Discharge resistance       | R <sub>DISCHG</sub>  | VOUT = 0.2V, discharge enable.                                                                          | 50    | 100   | 200    | Ω    |

| Discharge ends voltage     | V <sub>DISCHG</sub>  | V <sub>CSN</sub> voltage.                                                                               | 0.07  | 0.10  | 0.13   | V    |

|                                               |                     |                                                          |       | (CY39C  | 504) |       |

|-----------------------------------------------|---------------------|----------------------------------------------------------|-------|---------|------|-------|

| D                                             | 0                   | O and Hitland                                            | Value |         |      | 11-14 |

| Parameter                                     | Symbol              | Condition                                                | Min   | Min Typ |      | Unit  |

| ON TIMER                                      |                     |                                                          |       |         |      |       |

| On time                                       | t <sub>on</sub>     | $V_{VIN} = 7.4V, V_{VOUT} = 5.0V$                        | 802   | 872     | 942  | ns    |

| Minimum on time                               | t <sub>MINON</sub>  | $V_{VIN} = 7.4V, V_{VOUT} = 0.2V$                        | 100   | 200     | -    | ns    |

| Minimum off time                              | t <sub>MINOFF</sub> | -                                                        | -     | 120     | 240  | ns    |

|                                               |                     | CURRENTLIMITATION                                        |       |         |      |       |

| Current limitation threshold                  | V <sub>ILIMIT</sub> | CSP–CSN difference voltage at ILIM connects to VCC.      | 21.0  | 26.0    | 31.0 | mV    |

| ILIM input current                            | I <sub>ILIM</sub>   | $V_{ILIM} = 5.0V$                                        | -     | 0       | 0.1  | μA    |

| CSP input current                             | I <sub>CSP</sub>    | $V_{CSP} = 5.0V$                                         | -     | 2.0     | 5.0  | μA    |

| CSN input current                             | I <sub>CSN</sub>    | $V_{CSN} = 5.0V$                                         | -     | 8.0     | 20.0 | μA    |

|                                               |                     | OVER AND UNDER VOLTAGE PROTEC                            | TION  |         |      |       |

| Over voltage threshold ratio RT <sub>ov</sub> |                     | For target output voltage. At output voltage increasing. | 110   | 115     | 125  | %     |

| Propagation delay of OV                       | t <sub>ov</sub>     | -                                                        | 4     | 10      | 25   | μs    |

| Under voltage threshold ratio                 | RT <sub>uv</sub>    | For target output voltage. At output voltage decreasing. |       | 70      | 75   | %     |

| Propagation delay of UV                       | t <sub>UV</sub>     | -                                                        | 40    | 100     | 200  | μs    |

|                                               |                     | POWER GOOD MONITOR                                       |       |         |      |       |

| Power good threshold ratio                    | RT <sub>PG</sub>    | For target output voltage. At output voltage increasing. | 86    | 92      | 98   | %     |

| Hysteresis Ratio                              | RT <sub>HYS</sub>   | -                                                        | 3     | 5       | 7    | %     |

| Propagation delay                             | t <sub>PG</sub>     | Power good                                               | 20    | 50      | 200  | μs    |

| Propagation delay                             | t <sub>PB</sub>     | Power bad                                                | 4     | 10      | 25   | μs    |

| PWRGD leak current                            | I <sub>LKPG</sub>   | V <sub>PWRGD</sub> = 5.5V                                | -     | 0       | 1    | μA    |

| PWRGD output voltage "L"<br>level             | V <sub>OLPG</sub>   | I <sub>PWRGD</sub> = 1mA sink                            | -     | 0.05    | 0.10 | V     |

| THERMAL SHUT DOWN                             |                     |                                                          |       |         |      |       |

|                                               | T <sub>TSDH</sub>   | Shut down temperature.                                   | -     | 150(*1) | -    | °C    |

| Shut down temperature                         | T <sub>TSDL</sub>   | Exited temperature from thermal shut down state.         | -     | 125(*1) | -    | °C    |

\*1: No production tested, ensure by design.

| Parameter                                | Symbol             | Symbol Condition                                                |      | Min Typ  |      | Unit |

|------------------------------------------|--------------------|-----------------------------------------------------------------|------|----------|------|------|

|                                          |                    | 5V LDO                                                          |      | . 76     | Max  |      |

| Output voltage                           | V <sub>LDO5</sub>  | No switchover.<br>VOUT input voltage < 4.4V                     | 4.75 | 5.00     | 5.25 | V    |

| Output current                           | I <sub>LDO5</sub>  | No switchover.<br>V <sub>VIN</sub> = 5.4V                       | 25   | -        | -    | mA   |

| Output short current                     | I <sub>LDO5S</sub> | No switchover.<br>V <sub>LDO5</sub> = 0V                        | -    | 80       | 125  | mA   |

| Switchover voltage                       | V <sub>SWOVR</sub> | VOUT voltage rising.                                            | 4.35 | 4.50     | 4.60 | V    |

| Switchover voltage                       | V <sub>HYS</sub>   | Hysteresis voltage.                                             | 0.08 | 0.10     | 0.12 | V    |

| Startup time t <sub>SLDO5</sub>          |                    | LDO5 voltage reaches to 4.2V.<br>$C_{LDO5}$ , $C_{VCC}$ = 1.0µF | 100  | 150      | 400  | μs   |

|                                          |                    | DRIVER                                                          |      |          |      |      |

| . I finde and de la seconda factoria e a | R <sub>HOH</sub>   | At 100mA current sourcing                                       | -    | 3(*1)    | -    | Ω    |

| High side on resistance                  | R <sub>HOL</sub>   | At 100mA current sinking                                        | -    | 1(*1)    | -    | Ω    |

|                                          | RLOH               | At 100mA current sourcing                                       | -    | 4(*1)    | -    | Ω    |

| Low side on resistance                   | R <sub>LOL</sub>   | At 100mA current sinking                                        | -    | 0.75(*1) | -    | Ω    |

| High side source current                 | I <sub>SRCH</sub>  | V <sub>DRVH</sub> = 2.5V                                        | -    | 0.7(*1)  | -    | А    |

| High side sink current                   | I <sub>SINKH</sub> | $V_{DRVH} = 2.5V$                                               | -    | 1.1(*1)  | -    | А    |

| Low side source current                  |                    | $V_{DRVL} = 2.5V$                                               | -    | 0.5(*1)  | -    | А    |

| Low side sink current                    | I <sub>SINKL</sub> | $V_{DRVL} = 2.5V$                                               | -    | 1.7(*1)  | -    | А    |

| Dead time t <sub>DEAD</sub>              |                    | From DRVH turn off to DRVL turn on.<br>And reverse it.          | 10   | 20       | -    | ns   |

|                                          |                    | BOOST SWITCH                                                    |      |          |      |      |

| Boost switch on resistance               | R <sub>BST</sub>   | I <sub>BST</sub> = 10mA                                         | -    | 30       | 50   | Ω    |

| BST leak current I <sub>LKBST</sub> V    |                    | V <sub>BST</sub> = 30V                                          | -    | 0.1      | 1.0  | μA   |

\*1: No production tested, ensure by design.

| (CY39C504) |

|------------|

|------------|

## 8. Protections and Power Good function

### 8.1 Description

#### (CY39C502/C503/C504)

This PWM Control IC has some protection functions UVLO, OVP, UVP, ILIM, and TSD for the assumed various power system failures. Details of these protections are written as follows.

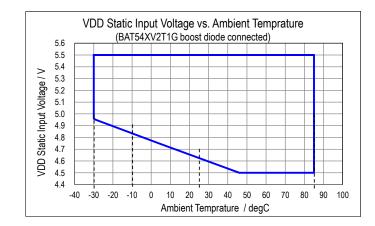

#### Under Voltage Lockout (UVLO)

The under voltage lockout (UVLO) protects ICs from malfunction and protects the system from destruction/deterioration, according to the reasons mentioned below.

- Transitional state when the voltage inputs to VCC (5V power supply) terminal.

- Momentary decrease

To prevent such a malfunction, this function detects a voltage drop of the 5V power supply, and stops IC operations. When the voltage of 5V power supply exceeds the threshold voltage of the under voltage lockout protection circuit, the system is restored.

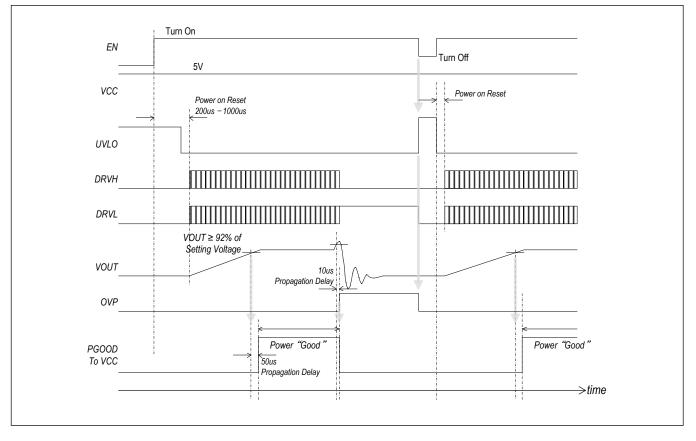

#### Over Voltage Protection (OVP)

This function stops the output voltage when the output voltage has increased, and protects devices connected to the output. When the over voltage is detected, the controller is fixed that the high side switching FET is turned off and the low side switching FET is turned on with 10µs propagation delay. When the enable is reentered, this fixed state is released and beginning soft start.

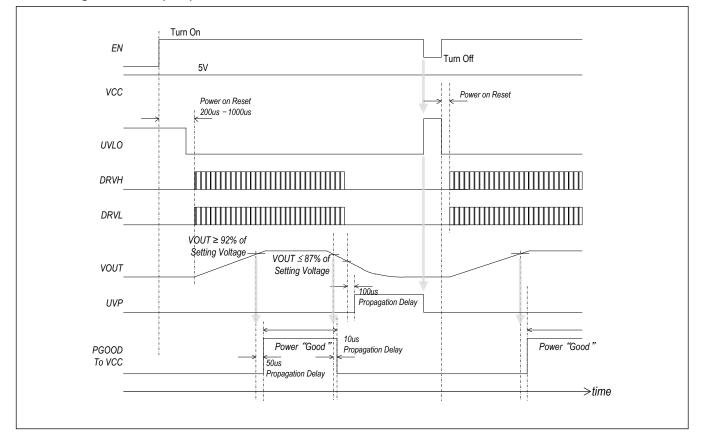

#### Under Voltage Protection (UVP)

This function stops the output voltage when the output voltage has lowered, and protects devices connected to the output. When the under voltage is detected, the controller is fixed that the high side switching FET is turned off and the low side switching FET is turned off with 100µs propagation delay. When the enable is reentered, this fixed state is released and beginning soft start.

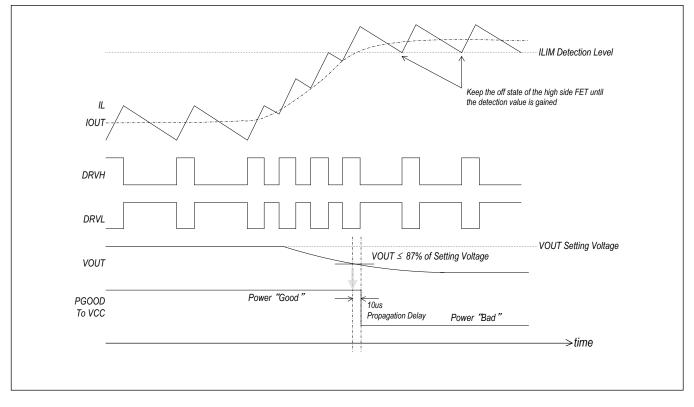

#### **Over Current Limitation (ILIM)**

This function limits the output current when it has increased, and protects devices connected to the output. This function detects the inductor valley current with current sense resister RSENSE. The differential voltage of the CSP-CSN terminals is amplified to x20 by internal current sense amplifier, and compared to the limit voltage of 480mV fixed at internal preset condition. Until the amplified voltage fall the limit voltage, the high side switching FET is held in the off state. After the voltage has fallen below the limit voltage, the high side switching FET is placed into the ON state. This limits the lower bound of the inductor current and also restricts the over current. As a result, it becomes operation that the output voltage droops.

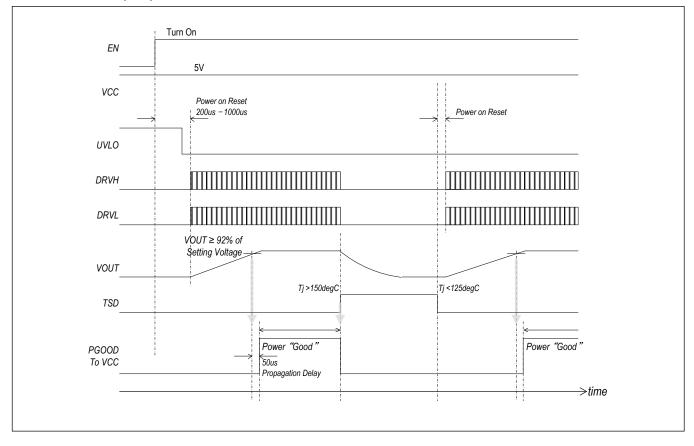

#### Thermal Shutdown (TSD)

This function prevents the PWM Control IC from a thermal destruction. If the junction temperature reaches +150°C, the high side and low side switching FET are turned off. Then the discharge operation is carried out to discharge the output capacitor (The discharge operation continues until the state of the thermal shutdown released). If the junction temperature drops to +125°C, the soft start is automatically reactivated.

#### Power Good (PWRGD)

Power good flag is hoisted at PWRGD terminal (Open Drain) to "Hi-Z" level with 50µs propagation delay, when the output voltage becomes larger than 92% of the output setting voltage. It is related by the OVP protection written above. When the output voltage becomes lower than power good threshold level, the PWRGD terminal is changed to "L" level with 10µs propagation delay.

## **State Table of Protection Function**

#### (CY39C502/C503/C504)

| Protection Function                 | High Side<br>FET | Low Side<br>FET | Output<br>state | Remarks                                                                       |

|-------------------------------------|------------------|-----------------|-----------------|-------------------------------------------------------------------------------|

| Under Voltage Lockout (UVLO)        | OFF              | OFF             | OFF             | After releasing UVLO, the System is an automatic restoration with soft start. |

| Over Voltage Protection (OVP)       | OFF              | ON              | Latch           | Latch stall.                                                                  |

| Over voltage Frotection (OVF)       | UFF              |                 | OFF             | It returns the System by enable reentry.                                      |

| Linder Vielterse Protection (LIV/P) | OFF              | OFF             | Latch           | Latch stall.                                                                  |

| Under Voltage Protection (UVP)      |                  | UFF             | OFF             | It returns the System by enable reentry.                                      |

| Over Current Limitation (ILIM)      | Switching        | Switching       | -               | The output voltage is drooped with current limitation.                        |

| Thermal Shutdown (TSD)              | OFF              | OFF             | OFF             | After releasing TSD, the System is an automatic restoration with soft start.  |

## 8.2 Timing Chart

## (CY39C502/C503/C504)

## **Over Voltage Protection (OVP)**

## **Under Voltage Protection (UVP)**

## **Over Current Limitation (ILIM)**

## **Thermal Shutdown (TSD)**

## 9. Enhanced LPM Description

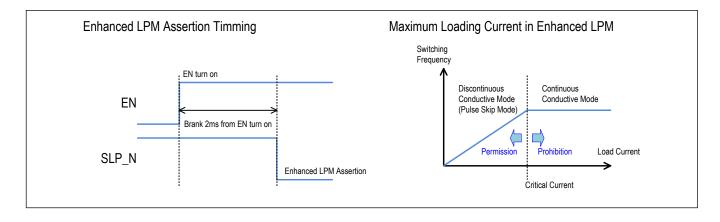

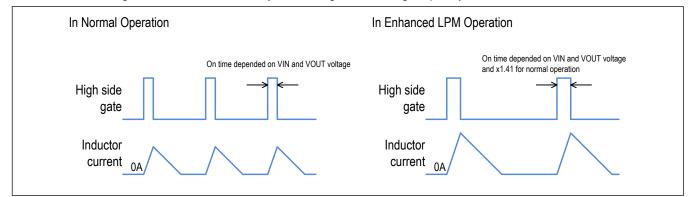

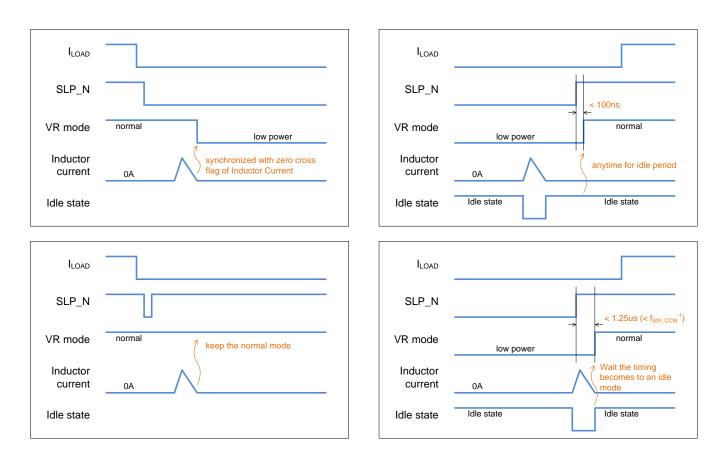

## (CY39C502/C503/C504)