# Power Factor Corrected LED Boost Switching Regulator

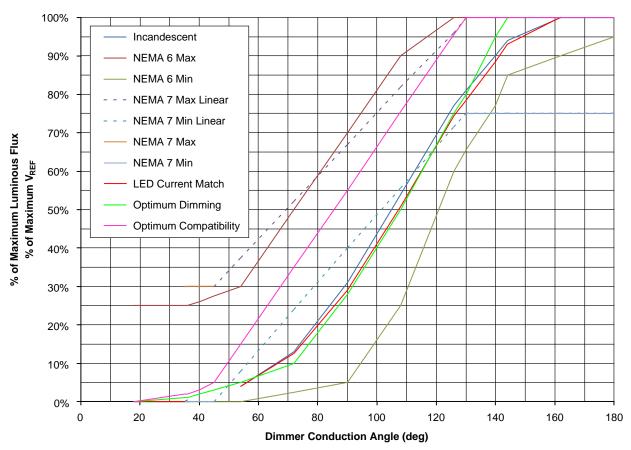

The NCL30167 high power factor boost PWM switching regulator is designed to regulate the average current through a string of LEDs. The circuit operates in Critical Conduction Mode (CrM) based on a proven constant on-time control scheme to achieve near unity power factor. In addition to regulating a constant current, the switching regulator is optimized to support leading and trailing edge phase dimming applications. When a dimmer is detected on the AC input, an internal voltage reference of the current regulation loop adjusts the current level based on the dimmer conduction angle so the current through the LED string has a desired value based on a programmed dimming curve. The shape of the dimming curve is intended to emulate the response of an incandescent bulb while achieving NEMA SSL6 and NEMA SSL7A recommendations.

A cascoded configuration supports biasing the controller during operation and eliminates the need for an auxiliary winding to provide bias power. A robust suite of protection features are included to ensure proper handling of expected fault conditions without the need for extra circuitry and a dedicated thermal fold-back input proves gradually reduction of the current above a user defined set-point.

#### **Features**

- Near-Unity Power Factor

- Critical Conduction Mode (CrM)

- Constant On-time Control

- Accurate Current Regulation (±2% Typical)

- Compatible with Leading and Trailing Edge Phase Controlled Dimmers

- Fast Startup Time (< 100 ms Typical)

- Integrated ZCD Detection

- User Programmable Thermal Current Fold-back

- V<sub>CC</sub> Operation up to 20 V

- This Device is Pb-Free and is RoHS Compliant

#### **Safety Features**

- Output Overvoltage Protection

- Cycle-by-Cycle Current Limiting

- V<sub>CC</sub> UVLO

# **Typical Applications**

- LED Bulbs

- LED Downlights

- LED Light Engines

- LED Modules

# ON Semiconductor®

www.onsemi.com

#### MARKING DIAGRAM

L30167 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

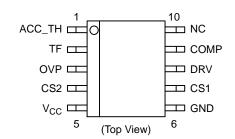

# PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| NCL30167DR2G | SOIC-10<br>(Pb-Free) | 2500 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

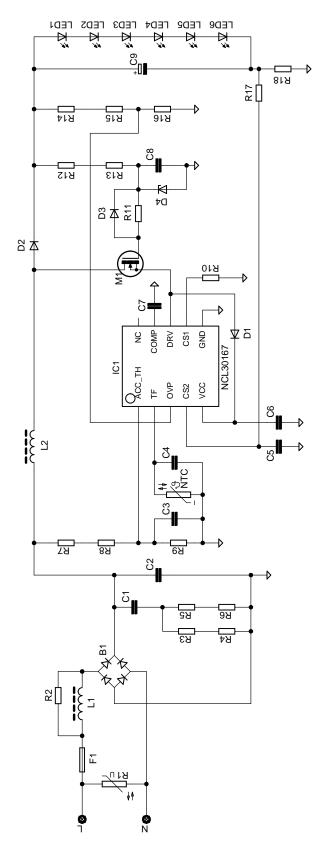

# **TYPICAL APPLICATION EXAMPLE**

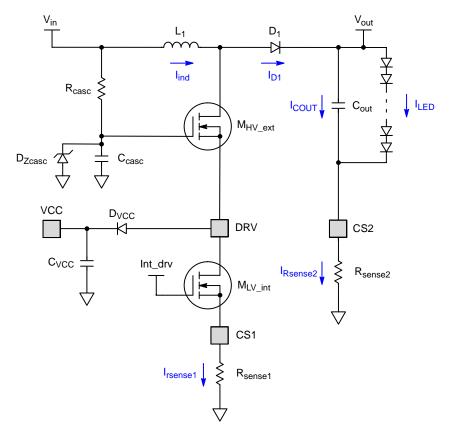

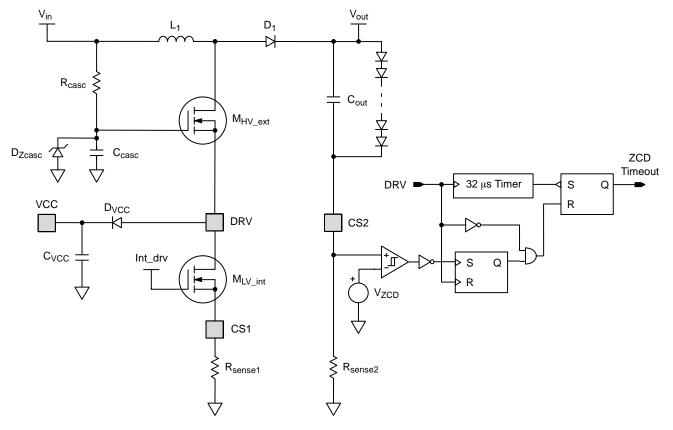

Figure 1. NCL30167 Application Schematic

# **PIN FUNCTION DESCRIPTION**

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin<br>Number | Pin<br>Name     | Function                            | Description                                                                                                                                                                                                                                                  |

|---------------|-----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | ACC_TH          | Dimming Detection Input             | This pin receives a portion of the AC input voltage. It is compared to an internal reference voltage in order to determine the presence of a dimmer state and the phase angle.                                                                               |

| 2             | TF              | Thermal Fold-back                   | Connecting an NTC to this pin allows linear reduction of the output current above a user programmed temperature set-point.                                                                                                                                   |

| 3             | OVP             | Over Voltage Protection Input       | This pin receives a portion of the Boost output voltage V <sub>OUT</sub> and serves to trigger an OVP fault in the event the LED string is open.                                                                                                             |

| 4             | CS2             | 2 <sup>nd</sup> Current Sense Input | This pin monitors the LED load current across the R <sub>sense2</sub> resistor during the off time. This pin is used to monitor the instantaneous load current for regulation loop, and to determine when the Zero Current Detection (ZCD) point is reached. |

| 5             | V <sub>CC</sub> | V <sub>CC</sub> Input               | This positive supply pin accepts up to 20 Vdc. The supply for the device is ensured by the external diode from the source pin.                                                                                                                               |

| 6             | GND             | -                                   | The switching regulator ground                                                                                                                                                                                                                               |

| 7             | CS1             | 1 <sup>st</sup> Current Sense Input | This pin monitors the inductor current across the R <sub>sense1</sub> resistor during the on-time. This pin monitors the maximum current cycle by cycle.                                                                                                     |

| 8             | DRV             | Drive for HV Switch                 | The Driving Pin for Source of the External High Voltage NMOS. Connect the external diode between the source and $V_{\rm CC}$ pin to provide the IC supply.                                                                                                   |

| 9             | COMP            | Compensation                        | Feedback loop compensation pin of the IC.                                                                                                                                                                                                                    |

| 10            | NC              | Not Connected                       |                                                                                                                                                                                                                                                              |

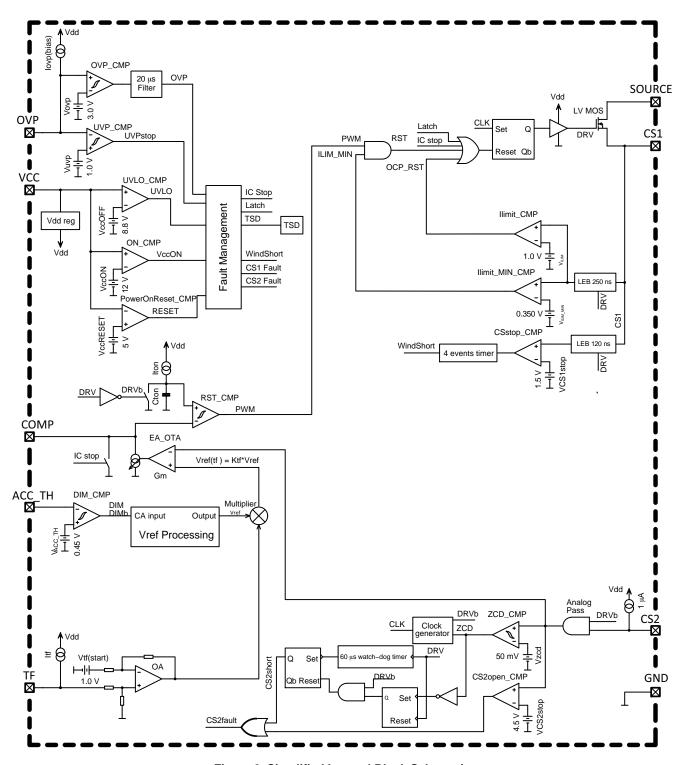

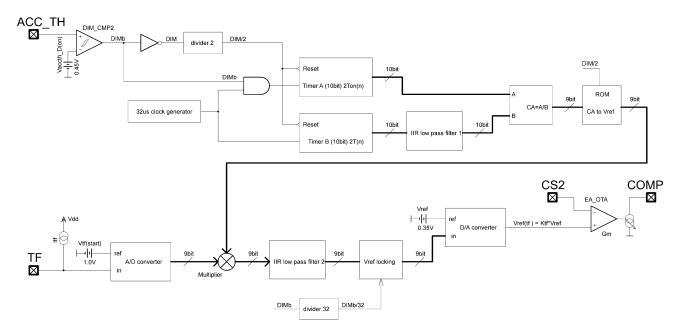

### SIMPLIFIED INTERNAL BLOCK SCHEMATIC

Figure 2. Simplified Internal Block Schematic

**Table 2. MAXIMUM RATINGS**

| Symbol               | Pin | Rating                                                                                                                                                  | Value                    | Unit        |

|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|

| DRV                  | 8   | External NMOS Source Driving Pin                                                                                                                        | -0.3 to 20               | V           |

|                      |     | Continuous Current $R_{\theta J-C}$ Steady State, $T_C$ = 25 °C (Note 1) $R_{\theta J-C}$ Steady State, $T_C$ = 100°C (Note 1) Peak Current             | 0.5<br>0.25<br>-0.01/1.7 | A<br>A<br>A |

| V <sub>CC</sub>      | 5   | V <sub>CC</sub> Power Supply Voltage, V <sub>CC</sub> Pin, Continuous Voltage<br>Power Supply Voltage, V <sub>CC</sub> Pin, Continuous Voltage (Note 2) | -0.3 to 20<br>±30 (Peak) | V<br>mA     |

| CS1                  | 7   | Maximum Voltage<br>Continuous Current                                                                                                                   | -0.3 to 5.5<br>-1.7/0.01 | V<br>A      |

| V <sub>max</sub>     |     | Maximum Voltage on Low Power Pins (except pins 5, 7, 8) Maximum Peak Current to Low Power Pins                                                          | - 0.3 to 9<br>±10        | V<br>mA     |

| $R_{\theta J-A}$     |     | Thermal Resistance Junction-to-Air                                                                                                                      | 180                      | °C/W        |

| $T_{JMAX}$           |     | Operating Junction Temperature                                                                                                                          | -40 to +125              | °C          |

| T <sub>STRGMAX</sub> |     | Storage Temperature Range                                                                                                                               | -60 to +150              | °C          |

| T <sub>Lmax</sub>    |     | Lead Temperature (Soldering, 10 s)                                                                                                                      | 300                      | °C          |

| MSL                  |     | Moisture Sensitivity Level                                                                                                                              | 3                        | _           |

|                      |     | ESD Capability, HBM model (Note 2)                                                                                                                      | 3.5                      | kV          |

|                      |     | ESD Capability, Machine Model (Note 2)                                                                                                                  | 250                      | V           |

|                      |     | ESD Capability, CDM model (Note 2)                                                                                                                      | 1                        | kV          |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **Table 3. ELECTRICAL CHARACTERISTICS**

(For typical values  $T_j = 25^{\circ}C$ , for min/max values  $T_j = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 13$  V unless otherwise noted)

| Characteristics                                                     | Test Conditions            | Symbol                  | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------|----------------------------|-------------------------|------|------|------|------|

| SUPPLY                                                              |                            |                         |      |      |      | •    |

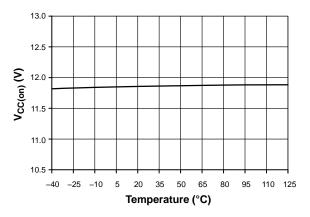

| Turn-on Threshold Level                                             | V <sub>CC</sub> Going Up   | V <sub>CC(on)</sub>     | 11.0 | 12.0 | 13.0 | V    |

| Minimum Operating Voltage, Turn-off<br>Threshold                    | V <sub>CC</sub> Going Down | V <sub>CC(off)</sub>    | 8.2  | 8.8  | 9.4  | V    |

| Hysteresis V <sub>CC(on)</sub> – V <sub>CC(off)</sub>               |                            | V <sub>CC(hyst)</sub>   | 2.8  | -    | _    | V    |

| V <sub>CC</sub> Decreasing Level at which the Internal Logic Resets |                            | V <sub>CC(reset)</sub>  | 4.0  | 5.0  | 6.0  | V    |

| Blanking Duration on V <sub>CC(off)</sub>                           |                            | t <sub>VCC(off)</sub>   | _    | 10   | -    | μS   |

| Blanking Duration on V <sub>CC(reset)</sub>                         |                            | t <sub>VCC(reset)</sub> | _    | 10   | -    | μS   |

| Internal Current Consumption of Device before Start-up              | V <sub>CC</sub> = 10 V     | I <sub>CC1</sub>        | _    | 10   | 100  | μΑ   |

| Internal Current Consumption, when DRV Pin is Switching             | f <sub>SW</sub> = 65 kHz   | I <sub>CC2</sub>        | -    | 1.0  | 1.5  | mA   |

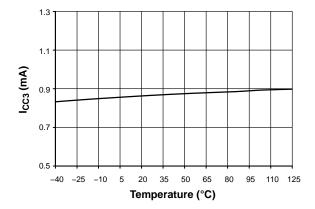

| Internal Current Consumption, when DRV Pin is Turned-on             | V <sub>CS1</sub> < 0.3 V   | I <sub>CC3</sub>        | -    | 0.9  | 1.1  | mA   |

<sup>1.</sup> Limited by the junction temperature.

This device contains ESD protection and exceeds the following tests:

Human Body Model 3500 V per JEDEC Standard JESD22–A114E,

Machine Model Method 250 V per JEDEC Standard JESD22–A115B,

Charged Device Model 1000 V per JEDEC Standard JESD22–C101E.

<sup>3.</sup> This device contains Latch-up protection and has been tested per JEDEC JESD78D, Class I and exceeds ±100 mA.

Table 3. ELECTRICAL CHARACTERISTICS (continued)

(For typical values  $T_j = 25^{\circ}C$ , for min/max values  $T_j = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 13$  V unless otherwise noted)

| Characteristics                                                            | Test Conditions                                          | Symbol                    | Min        | Тур        | Max        | Unit |

|----------------------------------------------------------------------------|----------------------------------------------------------|---------------------------|------------|------------|------------|------|

| OUTPUT OVER VOLTAGE PROTECTION                                             | 1                                                        | - 1                       |            | 1          |            |      |

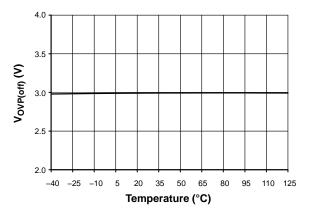

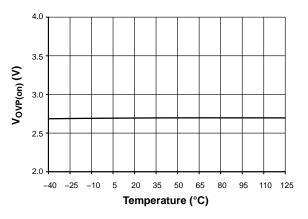

| Over Voltage Protection Thresholds                                         | V <sub>OVP</sub> Going Up<br>V <sub>OVP</sub> Going Down | V <sub>OVP(off)</sub>     | 2.9<br>2.6 | 3.0<br>2.7 | 3.1<br>2.8 | V    |

| Over Voltage Protection Hysteresis                                         |                                                          | V <sub>OVP(hyst)</sub>    | -          | 300        | -          | mV   |

| Timer Duration for Over Voltage Detection                                  |                                                          | t <sub>OVP</sub>          | 23         | 33         | 43         | μs   |

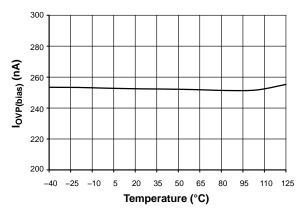

| Internal OVP Pin Pull-up Current                                           |                                                          | I <sub>OVP(bias)</sub>    | 50         | 250        | 450        | nA   |

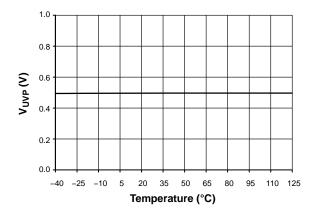

| Under Voltage Detect Threshold                                             |                                                          | V <sub>UVP</sub>          | 0.4        | 0.5        | 0.6        | V    |

| Under Voltage Detect Propagation Delay                                     |                                                          | t <sub>UVP</sub>          | 23         | 33         | 43         | μs   |

| LED CURRENT REGULATION LOOP                                                |                                                          |                           |            |            |            |      |

| Error Amplifier Trans-conductance                                          |                                                          | G <sub>EA</sub>           | 85         | 100        | 115        | μS   |

| Error Amplifier Current Capability                                         |                                                          | I <sub>EA</sub>           | ±13        | ±25        | _          | μΑ   |

| Error Amplifier Input Offset                                               | T <sub>j</sub> = 25°C                                    | V <sub>EAIO</sub>         | -20        | _          | 20         | mV   |

| Maximum Control Voltage                                                    | V <sub>CS2</sub> < 0.5 V                                 | V <sub>COMP(max)</sub>    | 4.2        | -          | -          | V    |

| Minimum Control Voltage                                                    | V <sub>CS2</sub> > 1.5 V                                 | V <sub>COMP(min)</sub>    | -          | _          | 0.7        | V    |

| COMP Pin Discharge Resistance                                              |                                                          | R <sub>COMP(dis)</sub>    | _          | 200        | _          | Ω    |

| CURRENT SENSE 1 – INDUCTOR OVER CU                                         | RRENT LIMITATION                                         | CONT (dis)                |            |            |            |      |

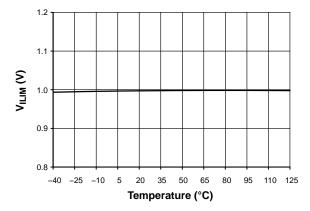

| Maximum Internal Current Set-point                                         | V <sub>COMP</sub> > 4 V                                  | V <sub>ILIM</sub>         | 0.95       | 1.00       | 1.05       | V    |

| Propagation Delay from V <sub>Ilimit</sub> Detection to Switch Off         | V <sub>CS1</sub> > 1.2 V                                 | t <sub>delay</sub>        | _          | 50         | 90         | ns   |

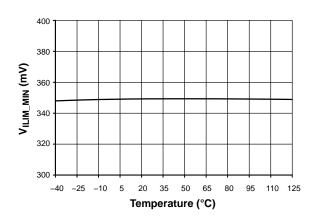

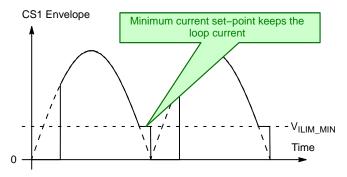

| Minimum Internal Current Set-point (Dimming is Detected)                   | V <sub>COMP</sub> < 0.7 V                                | V <sub>ILIM_MIN</sub>     | 300        | 350        | 400        | mV   |

| Propagation Delay from Reduced V <sub>Ilimit</sub><br>Detection to DRV Off | V <sub>CS1</sub> > 1.2 V                                 | t <sub>delay_DIM</sub>    | -          | 50         | 90         | ns   |

| Leading Edge Blanking Duration for V <sub>ILIM</sub>                       |                                                          | t <sub>LEB</sub>          | 220        | 320        | 420        | ns   |

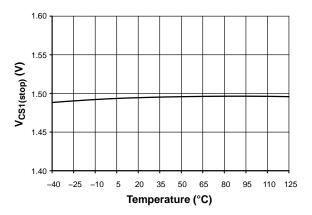

| Threshold for Winding Short Fault Protection Activation                    |                                                          | V <sub>CS1(stop)</sub>    | 1.42       | 1.50       | 1.58       | V    |

| Leading Edge Blanking Duration for V <sub>CS(stop)</sub> (Note 1)          |                                                          | t <sub>BCS</sub>          | 90         | 120        | 150        | ns   |

| CURRENT SENSE 2 – ZERO CURRENT DET                                         | ECTION AND LED REGU                                      | ILATION INPUT             |            |            |            | •    |

| Input Pull-up Current                                                      | V <sub>CS2</sub> = 0.7 V                                 | I <sub>CS2(bias)</sub>    | _          | 1          | _          | μΑ   |

| Internal Reference for Nominal LED Current                                 | -                                                        | V <sub>REF</sub>          | 233        | 250        | 267        | mV   |

| Lower ZCD Threshold                                                        | V <sub>CS2</sub> Falling                                 | V <sub>ZCD(falling)</sub> | 15         | 50         | 80         | mV   |

| Upper ZCD Threshold                                                        | V <sub>CS2</sub> Rising                                  | V <sub>ZCD(rising)</sub>  | 30         | 65         | 95         | mV   |

| ZCD Comparator Hysteresis                                                  |                                                          | V <sub>ZCD(hyst)</sub>    | _          | 15         | -          | mV   |

| Propagation Delay from ZCD to Turn-on Internal Switch                      | V <sub>CS2</sub> Falling                                 | t <sub>DEM</sub>          | 400        | 500        | 600        | ns   |

| Current Sense Threshold for CS2 Pin Open Protection                        |                                                          | V <sub>CS2(stop)</sub>    | 4.0        | 4.5        | 5.0        | V    |

| Blanking duration for ZCD Detection                                        |                                                          | t <sub>ZCD(blank)</sub>   | 200        | 300        | 400        | ns   |

| ZCD Timeout                                                                |                                                          | t <sub>ZCD(timeout)</sub> | 20         | 32         | 45         | μs   |

Table 3. ELECTRICAL CHARACTERISTICS (continued)

(For typical values  $T_j = 25^{\circ}C$ , for min/max values  $T_j = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 13$  V unless otherwise noted)

| Characteristics                                                                            | Test Conditions                                              | Symbol                                       | Min            | Тур            | Max            | Unit |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------|----------------|----------------|----------------|------|

| DIMMING DETECTION                                                                          |                                                              |                                              |                | •              | •              |      |

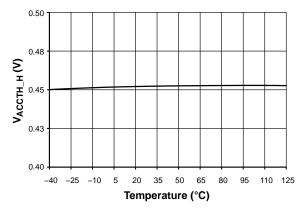

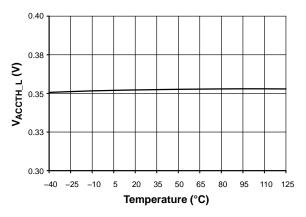

| Dimming Detection Comparator Thresholds                                                    | V <sub>ACCTH</sub> Going Up<br>V <sub>ACCTH</sub> Going Down | V <sub>ACCTH</sub> H<br>V <sub>ACCTH</sub> L | 0.400<br>0.300 | 0.450<br>0.350 | 0.500<br>0.400 | V    |

| Dimming Detection Comparator Hysteresis                                                    |                                                              | V <sub>ACCTH_Hyst</sub>                      | -              | 100            | -              | mV   |

| Dimming Detection Comparator Delay                                                         | V <sub>ACCTH</sub> = V <sub>ACCTH</sub> + 0.1 V              | t <sub>DIM_D</sub>                           | 40             | 70             | 90             | μs   |

| ON-TIME GENERATOR                                                                          |                                                              |                                              |                |                |                | •    |

| Maximum On Time                                                                            | V <sub>COMP</sub> = 4.2 V                                    | t <sub>ONmax</sub>                           | 15             | 18             | 22             | μS   |

| On Time                                                                                    | V <sub>COMP</sub> = 2.5 V                                    | t <sub>ON</sub>                              | 8.0            | 9.5            | 11.0           | μS   |

| Minimum On Time                                                                            | V <sub>COMP</sub> = 0.7 V                                    | t <sub>ONmin</sub>                           | -              | 0.6            | 1.2            | μS   |

| THERMAL FOLDBACK                                                                           | •                                                            |                                              |                |                |                |      |

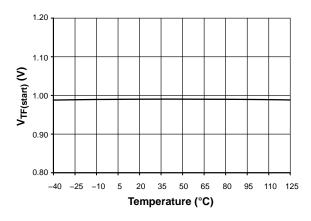

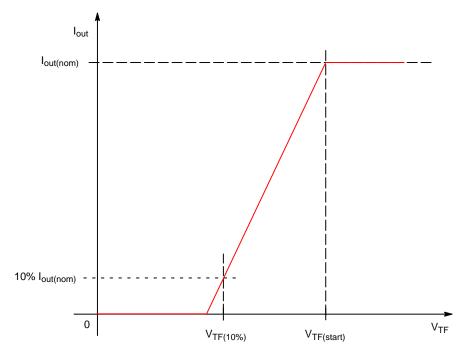

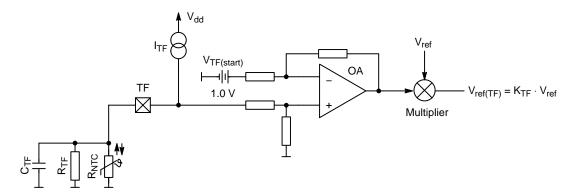

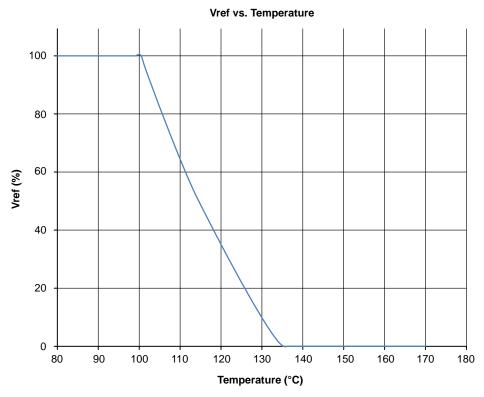

| TF Pin Voltage at which Thermal Fold-back Starts (V <sub>REF</sub> is Decreased)           |                                                              | V <sub>TF(start)</sub>                       | 0.94           | 1.00           | 1.06           | V    |

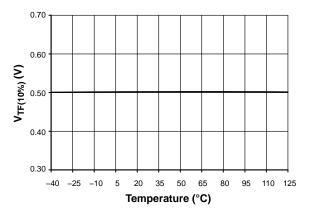

| TF Pin Voltage at which Thermal Fold-back Reduces V <sub>REF</sub> to 10% V <sub>REF</sub> |                                                              | V <sub>TF(10%)</sub>                         | 0.45           | 0.5            | 0.55           | V    |

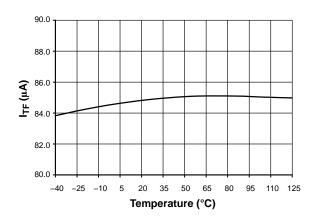

| Current Source for Direct NTC Connection                                                   | V <sub>TF</sub> = 0 V                                        | I <sub>TF</sub>                              | 80             | 85             | 90             | μΑ   |

| Blanking Duration for TF Detection after Start-up                                          | V <sub>TF</sub> < V <sub>TF(5%)</sub>                        | t <sub>TF(blank)</sub>                       | 250            | 300            | 350            | μs   |

| INTERNAL TEMPERATURE SHUTDOWN                                                              |                                                              |                                              |                |                |                | •    |

| Temperature Shutdown (Note 1)                                                              | T <sub>J</sub> Going Up                                      | T <sub>TSD</sub>                             | 135            | 150            | 165            | °C   |

| Temperature Shutdown Hysteresis (Note 1)                                                   | T <sub>J</sub> Going Down                                    | T <sub>TSD(HYS)</sub>                        | -              | 30             | -              | °C   |

| INTERNAL DRIVING SWITCH                                                                    | •                                                            |                                              |                | _              |                |      |

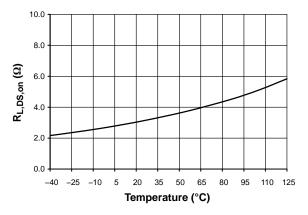

| On State Resistance of the Driving NMOS                                                    | $I_{DRV}$ = 500 mA,<br>$T_j$ = 25°C                          | R <sub>L,DS,on</sub>                         | _              | 3.5            | 4.5            | Ω    |

| Maximum Drain to Source Voltage of the Driving NMOS (Note 1)                               |                                                              | $V_{L,DS,max}$                               | 30             | -              | _              | V    |

| Maximum Off State Leakage Current                                                          | V <sub>DRAIN</sub> = 19 V                                    | I <sub>DSS</sub>                             | -              | -              | 5              | μА   |

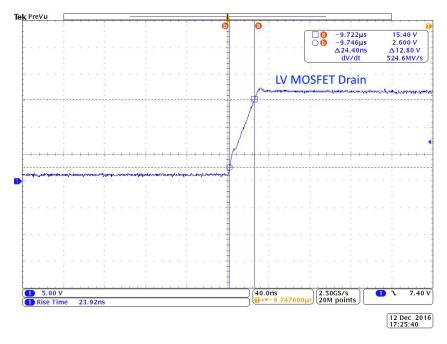

| Turn-on Time, 90 to 10 % of V <sub>DRV</sub>                                               | I <sub>DRV</sub> = 500 mA                                    | t <sub>on</sub>                              | _              | 10             | -              | ns   |

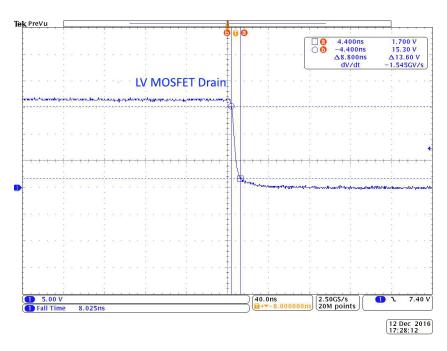

| Turn-off Time, 10 to 90 % of V <sub>DRV</sub>                                              | I <sub>DRV</sub> = 500 mA                                    | t <sub>off</sub>                             | -              | 30             | _              | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Guaranteed by design.

Figure 3. Turn-On Threshold Level, V<sub>CC(on)</sub>

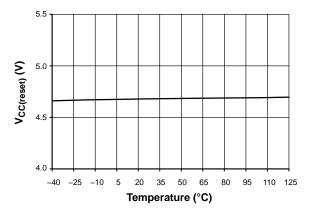

Figure 5.  $V_{CC}$  Decreasing Level at which the Internal Logic Resets,  $V_{CC(reset)}$

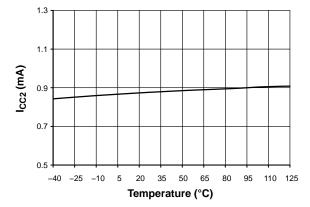

Figure 7. Internal Current Consumption when DRV Pin is Switching,  $I_{CC2}$

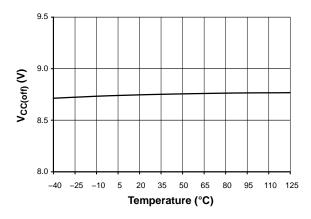

Figure 4. Minimum Operating Voltage, V<sub>CC(off)</sub>

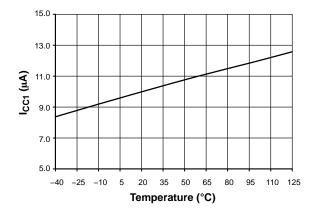

Figure 6. Internal Current Consumption before Start-Up,  $I_{CC1}$

Figure 8. Internal Current Consumption when DRV Pin is Turned-On, I<sub>CC3</sub>

Figure 9. Over-Voltage Protection Threshold (V<sub>OVP</sub> Going Up), V<sub>OVP(off)</sub>

Figure 11. Internal OVP Pin Pull-Up Current, I<sub>OVP(bias)</sub>

Figure 13. Maximum Internal Current Set-Point,  $V_{\text{ILIM}}$

Figure 10. Over-Voltage Protection Threshold (V<sub>OVP</sub> Going Down), V<sub>OVP(on)</sub>

Figure 12. Under-Voltage Detect Threshold, V<sub>UVP</sub>

Figure 14. Minimum Internal Current Set-Point, V<sub>ILIM MIN</sub>

Figure 15. Threshold for Winding Short Fault Protection Activation, V<sub>CS1(stop)</sub>

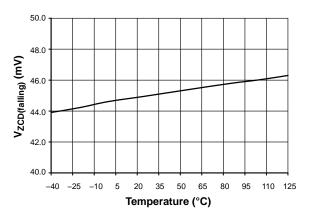

Figure 17. Lower ZCD Threshold, V<sub>ZCD(falling)</sub>

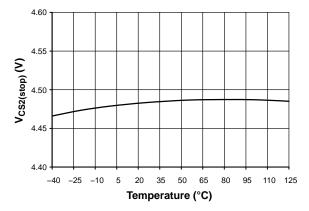

Figure 19. Current Sense Threshold for CS2 Pin Open Protection, V<sub>CS2(stop)</sub>

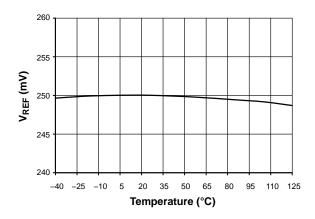

Figure 16. Internal Reference for Nominal LED Current, V<sub>REF</sub>

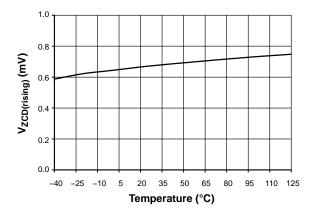

Figure 18. Upper ZCD Threshold, V<sub>ZCD(rising)</sub>

Figure 20. Dimming Detection Comparator Threshold,  $V_{ACCTH}$  Going Up,  $V_{ACCTH\_H}$

Figure 21. Dimming Detection Comparator Threshold, V<sub>ACCTH</sub> Going Down, V<sub>ACCTH\_L</sub>

Figure 23. TF Pin Voltage at which Thermal Fold-Back Reduces V<sub>REF</sub> to 10%, V<sub>TF(10%)</sub>

Figure 25. On-State Resistance of the Driving NMOS,  $R_{L,DS,on}$

Figure 22. TF Pin Voltage at which Thermal Fold-Back Starts, V<sub>TF(start)</sub>

Figure 24. Current Source for Direct NTC Connection, I<sub>TF</sub>

Figure 26. Typical On-Time of the Internal Driving Switch

Figure 27. Typical Off-Time of the Internal Driving Switch

#### APPLICATION INFORMATION

#### **Functional Description**

NCL30167 uses a Constant On-time Boost architecture in order to target a unity power factor, when no dimming is detected. The cascoded drain architecture shown in Figure 28, where M<sub>HV\_ext</sub> is the High Voltage Cascode NMOS, allows a simple implementation of a V<sub>CC</sub> supply by including a diode D<sub>VCC</sub>, external to the switcher IC,

between the DRAIN pin and capacitor  $C_{VCC}$ . Thanks to the cascoded drain architecture, the startup time is very fast (typ < 100 ms). Unlike a traditional asynchronous boost architecture, the cascoded architecture uses two MOSFETS. The low voltage MOSFET  $M_{LV\_int.}$ , which is housed inside the IC, drives the external High Voltage NMOS  $M_{HV\_ext}$  via the DRV pin.

Figure 28. Cascode Architecture

The NCL30167 operates in Critical Conduction Mode (CrM) under all working conditions, regulating the average current flowing through the string of LEDs whether the dimmer is present or not.

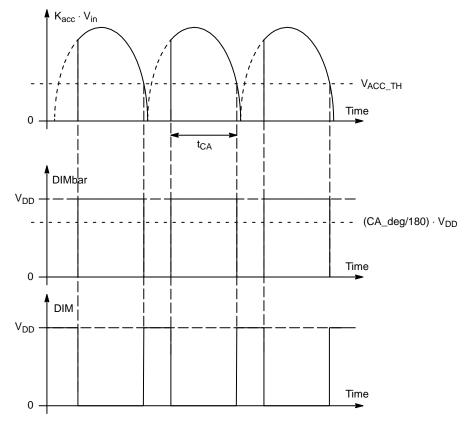

The ACC\_TH pin senses a scaled down input voltage (Vin) and by comparing it to an internal reference voltage named V<sub>ACC\_TH</sub> it provides a digital signal DIM/DIMb that contains the amount of dimming information. DIM/DIMb is

processed then by a circuit block named "Vref processing", which provides analog signal Vref. The reference voltage named Vref serves for the LED current regulation loop. The LED current regulation loop is working for all conduction angles, it is then possible by programming the Vref processing circuit block to get the desired dimming curve as depicted in Figure 30.

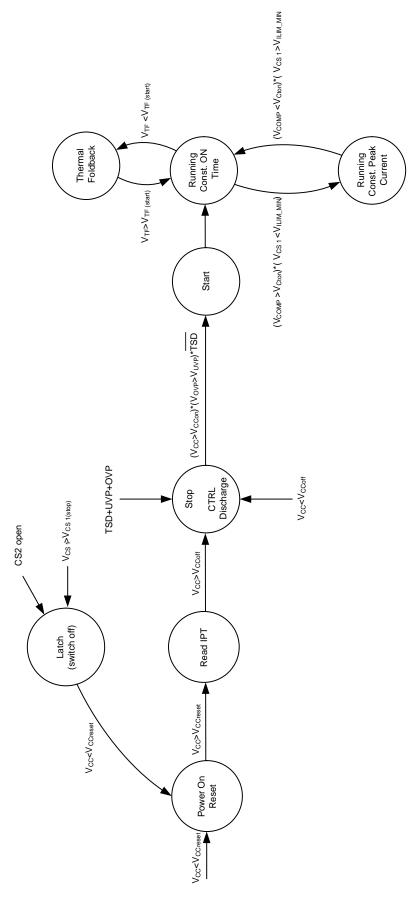

Figure 29. Operating Status Diagram of the Device

#### **Critical Conduction Mode**

By looking at Figure 28 it can be seen that, the current  $I_{Rsense1}$  flowing through the external resistor  $R_{sense1}$ , connected between pin CS1 and GND, is the same as the inductor current  $I_{ind}$  plus current spikes associated with the turning on or turning off of  $M_{LV\_int}$  NMOS FET. The inductor current information carried by the pin CS1 is used for the inductor peak current limitation. This voltage  $V_{CS1}$  is used to generate a reset signal (OCP\_RST) resulting from having reached the inductor maximum peak current controlled by  $V_{ILIM}$  reference voltage. If the maximum peak inductor current is not reached it is the second branch that takes care of the reset signal (RST) indicating the end of the on-time. The second branch monitors the off-time current information at current sense input CS2. The CS2 sensing is inhibited during the MOSFET on-time.

As shown in Figure 2, the second branch voltage is an image of the off-time inductor current. It is sent to the input of an OTA and by comparing to a reference voltage ( $V_{REF}$ ) a control voltage is generated at the COMP pin. The COMP pin voltage is proportional to the average LED current. It is compared to a constant on-time ramp voltage generated by charging the capacitor  $C_{TON}$  by a constant current  $I_{TON}$ . The output of the comparator generates constant on-time reset signal (RST). This process represents the "constant  $t_{on}$  average LED regulation loop" which, when steady state is reached, ensures that:

$$I_{LEDavg} = \frac{V_{REF}}{R_{sense2}}$$

(eq. 1)

There is one more condition to end the on-time cycle. The power MOSFET is turned-off only under a condition that the inductor peak current reaches a level set by the reference voltage named V<sub>ILIM\_MIN</sub>. Minimum input current is maintained by switching in Constant Peak Current mode. When a dimmer is present this feature helps to avoid the leakage current of the dimmer from charging the C<sub>in</sub> capacitor. At the same time this feature sets a minimum input current to avoid the current loop cut off when the triac dimming is applied.

The reset signal (RST or OCP\_RST) indicates an end of the on-time and a start of the off-time. Once the off-time has started, the CS2 pin senses the inductor off-time current across  $R_{sense2}$ . It is compared to a reference voltage  $V_{ZCD}$  in order to generate a zero-crossing signal (ZCD) that in turn is processed by the clock generation block. The generated clock pulse triggers a start of the new on-time cycle.

#### **LED Current Regulation and Dimming Curve**

As long as the max peak current limitation is not exceeded or a thermal foldback condition is present, the average LED current regulation loop is controlled by the OTA via Equation 1 and Triac Dimming Curve of Figure 30.

Figure 30. Triac Dimming Curve Digitally Generated

For example if  $R_{sense2} = 20 \Omega$  and  $V_{REF} = 0.5 V$  it gives  $I_{LED} = 25$  mA. The circuit block named  $V_{REF}$  processing which can be seen in Figure 2 will be programmed for the

optimum compatibility acceleration curve by default (see Figure 30) with an option of the optimum diming acceleration curve.

Table 4. COORDINATES OF DIMMING CURVE PROGRAMMING POINTS

| Dimmer Conduction Angle (Deg) | Optimum Dimming<br>V <sub>REF</sub> /V <sub>REF,max</sub> | Optimum Compatibility V <sub>REF</sub> /V <sub>REF,max</sub> |

|-------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|

| 18                            | 0.0%                                                      | 0.0%                                                         |

| 35                            | 1.0%                                                      | 2.0%                                                         |

| 36                            | 1.0%                                                      | 2.0%                                                         |

| 40                            | 2.0%                                                      | 3.0%                                                         |

| 45                            | 3.0%                                                      | 5.0%                                                         |

| 54                            | 5.0%                                                      | 15.0%                                                        |

| 72                            | 10.0%                                                     | 35.0%                                                        |

| 90                            | 28.0%                                                     | 55.0%                                                        |

| 108                           | 50.0%                                                     | 75.5%                                                        |

| 126                           | 75.0%                                                     | 95.5%                                                        |

| 130                           | 80.0%                                                     | 100.0%                                                       |

| 140                           | 95.0%                                                     | 100.0%                                                       |

| 144                           | 100.0%                                                    | 100.0%                                                       |

| 162                           | 100.0%                                                    | 100.0%                                                       |

| 180                           | 100.0%                                                    | 100.0%                                                       |

To regulate an average LED current in a single stage architecture the instantaneous LED current can have as much as  $\pm 50\%$  ripple component (this ripple component depends on the value of  $C_{out}$  capacitor and LED string dynamic resistance). The OTA must work linearly while a voltage with ripple is applied. The transconductance  $(G_m)$  value is set as low as  $100~\mu S$  and the minimal output current capability is at  $\pm 40~\mu A$  to ensure the OTA linear operation, without entering the saturation level.

#### **Dimming Presence Sensing**

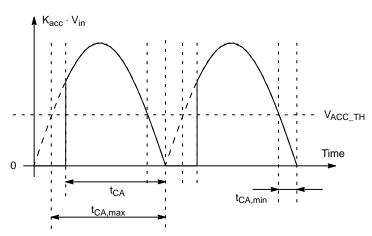

The conduction angle of the dimmer is sensed through pin ACC\_TH. The rectified and dimmed  $V_{in}$  voltage (see Figure 1) appears on pin ACC\_TH divided by the resistor bridge composed of  $R_{acc\_top}$  and  $R_{acc\_bot}$ . The ACC\_TH voltage is equal to:

$$V_{ACC\_TH} = K_{acc} \cdot V_{in}$$

(eq. 2)

where:

$$K_{acc} = \frac{R_{acc\_bot}}{R_{acc\_bot} + R_{acc\_top}}$$

(eq. 3)

Figure 31. ACC\_TH Pin Waveforms and Max/Min Detectable Dimmer Conduction Angles

Voltage sensed at the ACC\_TH pin is compared to the  $V_{ACC\_TH}$  reference voltage (see Figure 31) in order to generate a digital signal (DIM/DIMbar) (see Figure 2 and Figure 32). The DIM/DIMbar signal is used as the input of the block named "Vref processing block". Every half period of the mains voltage, the "Vref processing block" computes and holds the dimmer duty cycle and sets the corresponding  $V_{REF}$  voltage.

Unless the minimum peak current at CS1 pin reaches the  $V_{ILIM\_MIN}$  level the internal power MOSFET connected

between DRAIN and CS pins is kept open to avoid a leakage current of the dimmer from charging the  $C_{in}$  capacitor (see Figure 1) and providing a low impedance path for "SMART" dimmer operation.

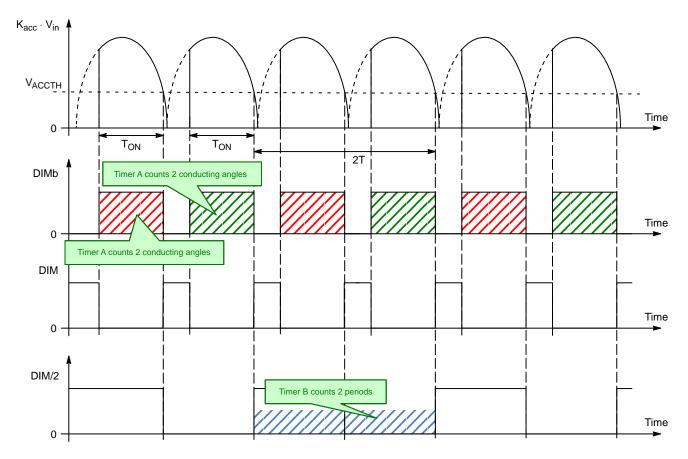

CA is the Dimmer Conduction Angle expressed in degrees and can be calculated based on the Dimmer Conduction Time  $t_{CA}$  (see Figure 32) and the AC mains frequency  $f_{mains}$  described in the following formula:

$$CA = 360 \cdot t_{CA} \cdot f_{mains}$$

(eq. 4)

Figure 32. Dimming Waveforms

# Detailed Description of the V<sub>REF</sub> Processing

The conduction angle is obtained by the digital division of the sampled values of the conduction time and the period. The conduction time is counted by the timer A over the both periods of mains as the period of mains. This type of sensing decreases the diming system sensitivity to the asymmetry of the diming triac and reduces flickering. The conducting angle is obtained as the ratio of Timer A (conduction time) and Timer B (the mains period). Please refer to Figure 33 and Figure 34.

$$CA = \frac{2 \cdot T_{on}}{2 \cdot T}$$

(eq. 5)

The additional IIR filters and the conduction angle lockout for 32 cycles of the rectified mains signal helps to reduce flickering caused by the differing leading edges and quantization error of the A/D conversion at TF pin and CA measurement.

Figure 33. Detailed Block Schematic of the Conduction Angle Measurement and the  $V_{\mathsf{REF}}$  Processing

Figure 34. Time Diagram of the Implemented Conduction Angle Measurement

The minimum current set-point feature is implemented. It starts play a role in case when the Vref is so small that the current set-point observed at CS1 pin is below the  $V_{\rm ILIM\_MIN}$  level. Then the regulation loop requirement is ignored and higher level of current set-point  $V_{\rm ILIM\_MIN}$  is

applied. This feature sets the minimum current to avoid the current loop cut off when the triac dimming is applied. This feature increases the compatibility with the most of the triac dimmers.

Figure 35. The Minimum Current Set-Point Effect to Keep the Loop Current

**Table 5. OPERATING MODES AND PROTECTION MODES**

| Event                                                                | Timer Protection     | Next Device Status                           | Release to Normal<br>Operation Mode              |

|----------------------------------------------------------------------|----------------------|----------------------------------------------|--------------------------------------------------|

| Overcurrent<br>V <sub>ILIM</sub> = 1.0 V                             | N/A                  | Normal Operation                             | N/A                                              |

| Reduced Peak Current<br>V <sub>ILIM_MIN</sub> = 0.35 V               | N/A                  | Normal Operation                             | N/A                                              |

| Winding Short<br>V <sub>sense1</sub> > V <sub>CS1(stop)</sub>        | 4 Consecutive Pulses | Latch                                        | V <sub>CC</sub> < V <sub>CC(reset)</sub>         |

| Low Supply<br>V <sub>CC</sub> < V <sub>CC(off)</sub>                 | 10 μs Timer          | Device Stops                                 | V <sub>CC</sub> > V <sub>CC(on)</sub>            |

| Thermal Fold-back Event<br>V <sub>OTP</sub> < V <sub>TF(start)</sub> | Immediate Reaction   | Reduced Output Current,<br>Thermal Fold-back | $V_{OTP} > V_{TF(start)}$                        |

| Output Overvoltage<br>V <sub>OVP</sub> > V <sub>OVP(off)</sub>       | 20 μs Timer          | Device Stops                                 | $V_{OVP} < V_{OVP(on)}$<br>$V_{CC} > V_{CC(on)}$ |

| Overvoltage Pin Shorted to GND V <sub>OVP</sub> < V <sub>UVP</sub>   | Immediate Reaction   | Device Stops                                 | V <sub>CC</sub> < V <sub>CC(reset)</sub>         |

| Internal TSD                                                         | 10 μs Timer          | Device Stops                                 | $(V_{CC} > V_{CC(on)})$ &TSDb                    |

#### **CS2 ZCD Timeout Protection**

The second CS2 pin has an additional feature. In case of very low average current is regulated the CS2 voltage can be too low. The CS2 sensed voltage can be too low so that the

CS2 ZCD is not detected. To avoid stopping the device under this condition the ZCD timeout feature is added. If no ZCD event is detected until the ZCD timer (t<sub>ZCD(timeout)</sub>) elapses the internal cascode switch is turned on anyway.

Figure 36. CS2 Pin ZCD Timeout Protection – Principal Diagram

## **Protection Against a Winding Short**

Under some conditions, such as a winding short-circuit of the boost inductor, the on-time duration is at a minimum (based on the internal propagation delay of the detector and LEB duration). In this event, the current sense voltage increases above  $V_{ILIM}$ , because the controller is blanked due to the LEB time and fast current slope. Dangerously high current can occur in the system if nothing is done to stop the controller. To avoid this, an additional fast comparator senses when a voltage on the current sense pin CS1 reaches  $V_{CS1(stop)} = 1.5 \cdot V_{ILIM}$ . If the fast comparator toggles 4 times, the controller immediately enters a protection mode. See the block diagram at Figure 2 for more details.

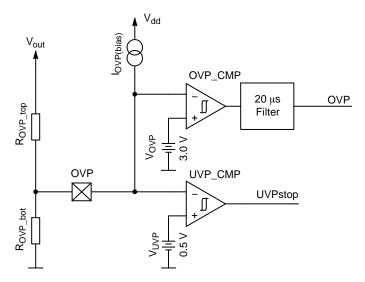

#### **Overvoltage Protection**

An overvoltage condition, for example if the LED string is open, can be sensed at  $V_{out}$  voltage by the external resistor divider comprised of  $R_{ovp\_top}$  and  $R_{ovp\_bot}$  resistors (see Figure 37) which is connected to the OVP pin. If the voltage of the OVP pin exceeds the  $V_{OVP(off)}$  reference voltage, the OVP fault state goes high and the switching regulator stops switching. When the voltage at OVP pin drops below the  $V_{OVP(on)}$  the device starts switching again. In addition the OVP input also has under-voltage protection (UVP) to ensure the resistor divider is properly connected. If the voltage at OVP pin is below the  $V_{UVP}$  threshold the device stops.

Figure 37. Overvoltage Protection Circuit

#### Thermal Fold-Back

The thermal fold-back circuit reduces the current supplying to the LED string if the temperature monitored by an external NTC resistor is too high.

The current is reduced down to 0% of its nominal value. The thermal fold-back starting temperature depends on the NTC resistor value selected by the power supply designer.

The TF pin allows the direct connection of an NTC. When the TF pin voltage  $V_{TF}$  drops below  $V_{TF(start)}$ , the internal reference for the constant current control  $V_{REF}$  is decreased proportionally to  $V_{TF}$ . When  $V_{TF}$  reaches  $V_{TF(10\%)}$ ,  $V_{REF}$  is

set to  $V_{REF10}$ , corresponding to 10% of the required output current. If  $V_{TF}$  drops below  $V_{TF(10\%)}$  the switching regulator still reduces the  $V_{REF}$ . If  $V_{REF}$  drops below the 5% of its required value then the switching regulator enters the stop mode.

The thermal fold-back and OTP thresholds correspond roughly to the following resistances:

- Thermal fold-back starts when  $R_{NTC} \le 11.76 \text{ k}\Omega$ .

- Thermal fold-back sets the 10% of  $V_{REF}$  when  $R_{NTC} \leq 5.88 \; k\Omega$

Figure 38. Output Current Reduction vs. TF Pin Voltage

At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the TF pin sensing is blanked for at least 300  $\mu s$  in order to allow the TF pin voltage to reach its nominal value if a filtering capacitor is connected to the TF pin. This is to avoid flickering of the LED light in case of over temperature or noise coupled to TF pin. The maximum value of OTP pin capacitor is given by

the following formula (The standard start-up condition is considered and the NTC current is neglected):

$$\begin{split} C_{\text{TF max}} &= \frac{t_{\text{TF(blank)min}} \cdot I_{\text{TF min}}}{V_{\text{TF(start)max}}} \\ &= \frac{200 \cdot 10^{-6} \cdot 80 \cdot 10^{-6}}{1.06} \text{ F} = 15.1 \text{ nF} \end{split}$$

Figure 39. Thermal Fold-Back Circuitry

Figure 40. Typical Thermal Fold-Back Characteristics when the 330 k $\Omega$  NTC and 39 k $\Omega$  Parallel Resistor are Connected to TF Pin

#### **Temperature Shutdown**

The NCL30167 includes a temperature shutdown protection with a trip point typically at 150°C and the typical hysteresis of 30°C. When the temperature rises above the high threshold, the switcher stops switching

instantaneously, and goes to the stop mode with low power consumption. Specific blocks are still powered from the  $V_{CC}$  supply to keep the TSD information. When the temperature falls below the low threshold, the device restarts. See the status diagrams at the Figure 29.

The product described herein (NCL30167) may be covered by one or more of U. S. patents.

**DATE 26 NOV 2013**

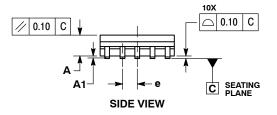

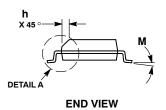

# SCALE 1:1 0.10 C A-B 2X 0.10 C A-B Ε АЗ C SEATING PLANE △ 0.20 С 10X **b DETAIL A** 2X 5 TIPS ⊕ 0.25 M C A-B D **TOP VIEW**

#### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE PROTRUSION

- SHALL BE 0.10mm TOTAL IN EXCESS OF 'b'

AT MAXIMUM MATERIAL CONDITION.

DIMENSIONS D AND E DO NOT INCLUDE

MOLD FLASH, PROTRUSIONS, OR GATE

BURRS. MOLD FLASH, PROTRUSIONS, OR

GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSIONS D AND E ARE DE-TERMINED AT DATUM F.

- DIMENSIONS A AND B ARE TO BE DETERM-INED AT DATUM F.

- INED AT DATUM F. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIMETERS |          |  |  |

|-----|-------------|----------|--|--|

| DIM | MIN         | MAX      |  |  |

| Α   | 1.25        | 1.75     |  |  |

| A1  | 0.10        | 0.25     |  |  |

| A3  | 0.17        | 0.25     |  |  |

| b   | 0.31        | 0.51     |  |  |

| D   | 4.80        | 5.00     |  |  |

| E   | 3.80        | 4.00     |  |  |

| е   | 1.00        | BSC      |  |  |

| Н   | 5.80        | 6.20     |  |  |

| h   | 0.37        | 7 REF    |  |  |

| L   | 0.40        | 0.80     |  |  |

| L2  | 0.25        | 0.25 BSC |  |  |

| М   | 0° 8°       |          |  |  |

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code

= Assembly Location = Wafer Lot

L Υ = Year W

= Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.

| DOCUMENT NUMBER: | 98AON52341E | Electronic versions are uncontrolled except when accessed directly from the Document Reposite<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-10 NB  |                                                                                                                                                                                  | PAGE 1 OF 1 |  |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative