# TRIPLE SYNCHRONOUS BUCK CONTROLLER WITH NMOS LDO CONTROLLER

#### **FEATURES**

- Qualified for Automotive Applications

- Three Independent Step-Down DC/DC Controllers and One LDO Controller

- Input Voltage Range

- Switcher: 4.5 V to 28 VLDO: 1.1 V to 3.6 V

- Output Voltage Range

- Switcher: 0.9 V to 8.5 VLDO: 0.9 V to 2.5 V

- Synchronous for High Efficiency

- Precision V<sub>ref</sub> (±1.5%)

- PWM Mode Control: 500-kHz Operation (Max)

- Auto PWM/SKIP Mode Available

- High-Speed Error Amplifier

- Overcurrent Protection With Temperature Compensation Circuit for Each Channel

- Overvoltage and Undervoltage Protection

- Programmable Short-Circuit Protection

- Power Good Output (PGOUT) With Programmable Delay Time

- 5-V and 3.3-V Linear Regulators

### **APPLICATIONS**

- Notebook PCs, PDAs

- Consumer Game Systems

- DSP Applications

#### **DESCRIPTION**

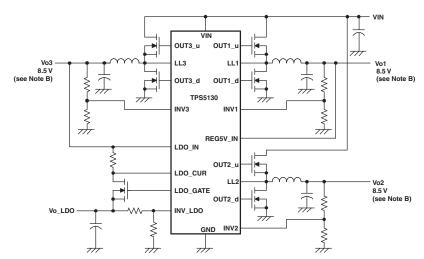

The TPS5130 is composed of three independent synchronous buck regulator controllers (SBRC) and one low dropout (LDO) regulator controller. On-chip high-side and low-side synchronous rectifier drivers are integrated to drive less expensive N-channel MOSFETs. The LDO controller can also drive an external N-channel MOSFET. Because the input current ripple is minimized by operating 180° out of phase, it allows a smaller input capacitance, resulting in reduced power supply cost. The SBRC of the TPS5130 automatically adjusts from PWM mode to SKIP mode to maintain high efficiency under light-load conditions. Resistorless current protection for the synchronous buck controller and the fixed high-side driver voltage simplifies the system design and reduces the external parts count. The LDO controller has a current-limit protection and overshoot protection to suppress output voltage spikes at load transient. To further extend battery life, the TPS5130 features dead-time control and very low quiescent current.

- A. See the Application Information section for more details.

- B. To determine input voltage, see Duty Control in Electrical Characteristics.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

**ISTRUMENTS**

SLVS866-MARCH 2009 www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>J</sub> | PACKAGE <sup>(2)</sup> |              | PACKAGE <sup>(2)</sup> ORDERABLE PART NUMBER |       |

|----------------|------------------------|--------------|----------------------------------------------|-------|

| -40°C to 125°C | LQFP – PT              | Reel of 1000 | TPS5130QPTRQ1                                | 5130Q |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**(1)(2)

over junction temperature range (unless otherwise noted)

| $V_{CC}$         | Supply voltage range           | VIN                                                                                                                                     | –0.3 V to 30 V |

|------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                  |                                | LH1, LH2, LH3                                                                                                                           | −0.3 V to 35 V |

| Vı               | Input voltage range            | VIN_SENSE12, VIN_SENSE3, LL1, LL2, LL3, STBY_LDO, STBY_VREF3.3, STBY_VREF5, TRIP1, TRIP2, TRIP3                                         | −0.3 V to 30 V |

| ,                | input voltage range            | INV1, INV2, INV3, CT, SS_STBY1, SS_STBY2, SS_STBY3, INV_LDO, LDO_OUT, FLT, PG_DELAY, VREF3.3, VREF5, LDO_IN, LDO_CUR, PWM_SEL, REG5V_IN | –0.3 V to 7 V  |

|                  |                                | OUT1_u, OUT2_u, OUT3_u                                                                                                                  | –0.3 V to 35 V |

| V                | Outside additional management  | FB1, FB2, FB3, PGOUT, OUT1_d, OUT2_d, OUT3_d                                                                                            |                |

| Vo               | Output voltage range           | LDO_GATE                                                                                                                                | –0.3 V to 9 V  |

|                  |                                | REF                                                                                                                                     | –0.3 V to 3 V  |

| TJ               | Junction temperature range     |                                                                                                                                         | -40°C to 125°C |

| T <sub>stg</sub> | Storage temperature range      |                                                                                                                                         | –55°C to 150°C |

|                  |                                | Human-Body Model (HBM)                                                                                                                  | 2000 V         |

| ESD              | Electrostatic discharge rating | Machine Model (MM)                                                                                                                      | 200 V          |

|                  |                                | Charged-Device Model (CDM)                                                                                                              | 500 V          |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **PACKAGE DISSIPATION RATINGS**

| PACKAGE     | LOW K/<br>HIGH K | DERATING<br>FACTOR ABOVE<br>T <sub>A</sub> = 25°C | POWER RATING<br>T <sub>A</sub> ≤ 25°C | POWER RATING<br>T <sub>A</sub> = 70°C | POWER RATING<br>T <sub>A</sub> = 85°C | θЈС      |

|-------------|------------------|---------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----------|

| 48-pin PT   | High             | 14.60 mW/°C                                       | 1459.85 mW                            | 802.92 mW                             | 583.94 mW                             |          |

| 40-piii F i | Low              | 9.28 mW/°C                                        | 927.64 mW                             | 510.20 mW                             | 371.06 mW                             | 11.8°C/W |

Product Folder Link(s): TPS5130-Q1

<sup>(2)</sup> Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

<sup>(2)</sup> All voltage values are with respect to the network ground terminal.

### RECOMMENDED OPERATING CONDITIONS

|                  |                      |                                                                                     | MIN  | NOM | MAX | UNIT |

|------------------|----------------------|-------------------------------------------------------------------------------------|------|-----|-----|------|

|                  | -                    | VIN                                                                                 | 4.5  |     | 28  |      |

| $V_{CC}$         |                      | LDO_IN                                                                              | 1.1  |     | 3.6 | V    |

|                  |                      | REG5V_IN                                                                            | 4.5  |     | 5.5 |      |

|                  |                      | OUT1_u, OUT2_u, OUT3_u, LH1, LH2, LH3                                               | -0.1 |     | 33  |      |

|                  |                      | VIN_SENSE12, VIN_SENSE3                                                             | 4.5  |     | 28  |      |

|                  |                      | STBY_LDO, LL1, LL2, LL3, TRIP, STBY_VREF3.3, STBY_VREF5                             | -0.1 |     | 28  |      |

| Vı               | Input voltage        | LDO_GATE                                                                            | -0.1 |     | 8   | V    |

| • 1              | input voltago        | INV1, INV2, INV3, INV_LDO, CT, PWM_SEL, FLT, PG_DELAY, SS_STBY1, SS_STBY2, SS_STBY3 | -0.1 |     | 6   | •    |

|                  |                      | PGOUT, FB1, FB2, FB3, OUT1_d, OUT2_d, OUT3_d                                        | -0.1 |     | 5.5 |      |

|                  |                      | LDO_CUR, LDO_OUT                                                                    | -0.1 |     | 3.5 |      |

| f <sub>OSC</sub> | Oscillator frequency |                                                                                     |      | 300 | 500 | kHz  |

| TJ               | Junction temperature |                                                                                     | -40  |     | 125 | °C   |

### **ELECTRICAL CHARACTERISTICS**

over junction temperature range,  $V_{(VIN)} = V_{(VIN\_SENSE12)} = V_{(VIN\_SENSE3)} = 12 \text{ V}$  (unless otherwise noted)

|                       | PARAMETER                    | TEST CONDITI                                                                                      | ONS                                                           | MIN  | TYP   | MAX  | UNIT |

|-----------------------|------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|-------|------|------|

| Supply Co             | urrent                       |                                                                                                   |                                                               |      |       |      |      |

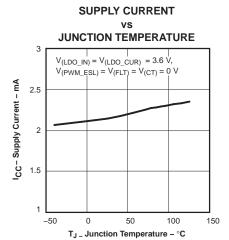

| I <sub>CC</sub>       | Supply current               | $T_A = 25^{\circ}C$ , $V_{(LDO\_IN)} = 3.6$ V,<br>$V_{(CT)} = V_{(INVx)} = V_{(INV\_LDO)} = 0$ V, |                                                               | 2    | 3     | mA   |      |

| I <sub>CC(STBY)</sub> | Standby current              | $V_{(SS\_STBYx)} = 0 \text{ V}, V_{(STBY\_LDO)} = 0$<br>$V_{(STBY\_VREF3.3/5)} = 5 \text{ V}$     | V,                                                            |      | 150   | 250  | μΑ   |

| $I_{\text{CC}(S)}$    | Shutdown current             | $V_{(SS\_STBYx)} = 0 \text{ V}, V_{(STBY\_LDO)} = 0$<br>$V_{(STBY\_VREF3.3/5)} = 0 \text{ V}$     | V,                                                            |      | 0.001 | 10   | μΑ   |

| Reference             | ⊋ Voltage                    |                                                                                                   |                                                               |      |       |      |      |

| V <sub>ref</sub>      | Reference voltage            |                                                                                                   |                                                               |      | 0.85  |      | V    |

|                       |                              | T <sub>A</sub> = 25°C                                                                             |                                                               | -1.5 |       | 1.5  |      |

| $V_{ref(tol)}$        | Reference voltage tolerance  | $I_{ref} = 50 \mu A$                                                                              | $T_J = 0$ °C to 125°C                                         | -2   |       | 2    | %    |

|                       |                              |                                                                                                   | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | -2.5 |       | 2.5  |      |

|                       | Line regulation              | $V_{(VIN)} = 4.5 \text{ V to } 28 \text{ V, } I_{ref} = 50  \mu\text{A}$                          |                                                               |      |       |      |      |

|                       | Load regulation              | I <sub>ref</sub> = 0.1 μA to 1 mA                                                                 |                                                               |      | 0.15  | 5    | mV   |

| 5-V Intern            | al Switch                    |                                                                                                   |                                                               |      |       |      |      |

| $V_{T(LH)}$           | Threshold voltage, high      | REG5V_IN voltage                                                                                  | 4.2                                                           |      | 4.8   | V    |      |

| V <sub>T(HL)</sub>    | Threshold voltage, low       | REG5V_IN voltage                                                                                  |                                                               | 4.1  |       | 4.7  | V    |

| V <sub>hys</sub>      | Hysteresis                   | REG5V_IN voltage                                                                                  |                                                               | 30   |       | 200  | mV   |

| 5-V Regul             | ator                         |                                                                                                   |                                                               |      |       | •    |      |

| Vo                    | Output voltage               | $I_{O} = 0$ mA to 50 mA, $V_{(VIN)} = 5.5$ V                                                      | to 28 V, T <sub>A</sub> = 25°C                                | 4.8  |       | 5.2  | V    |

|                       | Line regulation              | $V_{(VIN)} = 5.5 \text{ V to } 28 \text{ V}, I_O = 10 \text{ mA}$                                 |                                                               |      |       | 20   | mV   |

|                       | Load regulation              | $I_{O} = 1 \text{ mA to } 10 \text{ mA}, V_{(VIN)} = 5.5 \text{ V}$                               | 1                                                             |      |       | 40   | mV   |

| Ios                   | Short-circuit output current | V <sub>(VREF5)</sub> = 0 V, T <sub>A</sub> = 25°C                                                 |                                                               | 65   |       |      | mA   |

| V <sub>T(LH)</sub>    | UVLO threshold voltage, high | VREF5 voltage                                                                                     |                                                               | 3.6  |       | 4.2  | V    |

| V <sub>T(HL)</sub>    | UVLO threshold voltage, low  | VREF5 voltage                                                                                     |                                                               | 3.5  |       | 4.1  | V    |

| V <sub>hys</sub>      | Hysteresis                   | VREF5 voltage                                                                                     |                                                               | 30   |       | 200  | mV   |

| 3.3-V Reg             | ulator                       |                                                                                                   |                                                               |      |       |      |      |

| Vo                    | Output voltage               | $I_{O} = 0$ mA to 30 mA, $V_{(VIN)} = 5.5$ V                                                      | to 28 V, T <sub>A</sub> = 25°C                                | 3.15 | 3.30  | 3.45 | V    |

|                       | Line regulation              | $V_{(VIN)} = 5.5 \text{ V to } 28 \text{ V}, I_O = 10 \text{ mA}$                                 |                                                               |      |       | 20   | mV   |

|                       | Load regulation              | $I_{O} = 1$ mA to 10 mA, $V_{(VIN)} = 5.5$ V                                                      | ,                                                             |      |       | 40   | mV   |

| Ios                   | Short-circuit output current | V <sub>(VREF3.3)</sub> = 0 V, T <sub>A</sub> = 25°C                                               |                                                               | -30  |       |      | mA   |

# **ELECTRICAL CHARACTERISTICS (continued)**

over junction temperature range,  $V_{(VIN)} = V_{(VIN\_SENSE12)} = V_{(VIN\_SENSE3)} = 12 \text{ V}$  (unless otherwise noted)

|                         | PARAMETER                                        | TEST CONDIT                                            | TIONS        | MIN  | TYP  | MAX  | UNIT |

|-------------------------|--------------------------------------------------|--------------------------------------------------------|--------------|------|------|------|------|

| Control                 |                                                  |                                                        |              |      |      |      |      |

| V <sub>IH</sub>         | High-level input voltage                         | SS_STBY1, SS_STBY2, SS_ST<br>PWM_SEL, STBY_VREF3.3, ST | 2.2          |      |      | V    |      |

| $V_{IL}$                | Low-level input voltage                          | SS_STBY1, SS_STBY2, SS_ST<br>PWM_SEL, STBY_VREF3.3, ST |              |      |      | 0.3  | V    |

| Output Vol              | tage Monitor                                     |                                                        |              |      |      |      |      |

|                         | OVP comparator threshold                         | SBRC, LDO                                              |              | 0.91 | 0.95 | 0.99 | V    |

|                         | UVP comparator threshold                         | SBRC, LDO                                              |              | 0.51 | 0.55 | 0.59 | V    |

|                         | PG comparator low-level threshold                |                                                        |              | 0.75 | 0.79 | 0.81 | V    |

|                         | PG comparator high-level threshold               |                                                        |              | 0.88 | 0.91 | 0.94 | V    |

|                         | PG propagation delay from INVx, INV_LDO to PGOUT | No load at PG_DELAY                                    | PGOUT H to L |      | 6.5  |      | μs   |

| I <sub>(PG DELAY)</sub> | PG_DELAY source current                          |                                                        |              |      | -1.8 |      | μА   |

|                         |                                                  | UVP protection                                         |              | -1.5 | -2.3 | -3.1 |      |

|                         | Timer latch current source                       | OVP protection                                         |              | -80  | -125 | -180 | μΑ   |

| Oscillator              |                                                  | <u> </u>                                               |              |      |      |      |      |

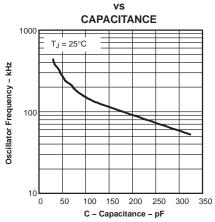

| f <sub>OSC</sub>        | Oscillation frequency                            | PWM mode, C <sub>(CT)</sub> = 44 pF, T <sub>A</sub> =  | 25°C         |      | 300  |      | kHz  |

|                         |                                                  | dc                                                     |              | 1    | 1.1  | 1.2  |      |

| $V_{OH}$                | High-level output voltage                        | f <sub>OSC</sub> = 300 kHz                             |              | 1.17 |      | V    |      |

| .,                      |                                                  | dc                                                     | 0.4          | 0.5  | 0.6  |      |      |

| $V_{OL}$                | Low-level output voltage                         | f <sub>OSC</sub> = 300 kHz                             |              | 0.43 |      | V    |      |

| Error Ampl              | lifier for SBRC                                  |                                                        |              |      |      |      |      |

| V <sub>IO</sub>         | Input offset voltage                             | INVx voltage, T <sub>A</sub> = 25°C                    |              |      | 2    | 10   | mV   |

|                         | Open-loop voltage gain                           |                                                        |              | 50   |      |      | dB   |

|                         | Unity-gain bandwidth                             |                                                        |              |      | 2.5  |      | MHz  |

| I <sub>O(snk)</sub>     | Output sink current                              | V <sub>(FBx)</sub> = 1 V                               |              | 0.2  | 0.7  |      | mA   |

| I <sub>O(src)</sub>     | Output source current                            | V <sub>(FBx)</sub> = 1 V                               |              | -0.2 | -0.9 |      | mA   |

| Duty Contr              | ol                                               |                                                        |              |      |      |      |      |

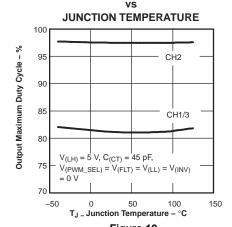

|                         |                                                  |                                                        | CH1, CH3     |      | 82   |      |      |

|                         | Maximum duty control                             | $f_{OSC} = 300 \text{ kHz}, V_{(INVx)} = 0 \text{ V}$  | CH2          |      | 97   |      | %    |

| Output Driv             | vers                                             |                                                        |              |      |      |      |      |

| -                       | OUTx_u sink current                              | $V_{(OUTx_u)} - V_{(LLx)} = 3 \text{ V}$               |              |      | 1.2  |      | Α    |

|                         | OUTx_u source current                            | $V_{(LHx)} - V_{(OUTx_u)} = 3 \text{ V}$               |              |      | -1.2 |      | Α    |

|                         | OUTx_d sink current                              | $V_{(OUTx_d)} = 3 \text{ V}$                           |              |      | 1.5  |      | Α    |

|                         | OUTx_d source current                            | $V_{(OUTx_d)} = 2 V$                                   |              |      | -1.5 |      | Α    |

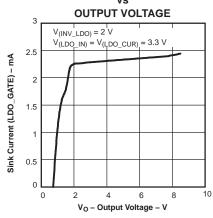

|                         | LDO_GATE sink current                            | $V_{(LDO\_GATE)} = 2 V$                                |              |      | 2    |      | mΑ   |

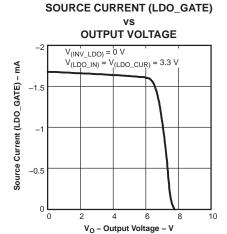

|                         | LDO_GATE source current                          | $V_{(LDO\_GATE)} = 2 V$                                |              |      | -1.4 |      | mA   |

| I <sub>(TRIPx)</sub>    | Output current                                   | TRIP1, TRIP2, TRIP3                                    |              | 11   | 13   | 15   | μΑ   |

| Soft Start              |                                                  | 1                                                      |              |      |      |      |      |

| I <sub>(SS_STBYx)</sub> | Soft-start current                               | $V_{(SS\_STBYx)} = 0.7 \text{ V}$                      |              | -1.6 | -2.3 | -2.9 | μΑ   |

|                         | lifier for LDO Controller                        |                                                        |              |      |      |      |      |

| VIO                     | Input offset voltage                             | V <sub>(LDO_IN)</sub> = 3.3 V, T <sub>A</sub> = 25°C   |              |      | 2    | 10   | mV   |

|                         |                                                  |                                                        |              | - 50 |      |      | dB   |

|                         | Open-loop voltage gain                           | $V_{(LDO_{IN})} = 3.3 \text{ V}$                       |              | 50   |      |      | uБ   |

# **ELECTRICAL CHARACTERISTICS (continued)**

over junction temperature range,  $V_{(VIN)} = V_{(VIN\_SENSE12)} = V_{(VIN\_SENSE3)} = 12 \text{ V}$  (unless otherwise noted)

| PARAMETER                                  | TEST CONDITIONS                                    | MIN | TYP | MAX | UNIT |  |  |  |

|--------------------------------------------|----------------------------------------------------|-----|-----|-----|------|--|--|--|

| Current Limit for LDO Controller           |                                                    |     |     |     |      |  |  |  |

| Current limit comparator threshold voltage | V <sub>(LDO_IN)</sub> = 3.3 V                      |     | 50  | 60  | mV   |  |  |  |

| Overshoot Protection for LDO Controller    |                                                    |     |     |     |      |  |  |  |

| LDO_OUT sink current                       | $V_{(LDO\_OUT)} = V_{(LDO\_GATE)} = 1.5 \text{ V}$ |     | 25  |     | mA   |  |  |  |

Submit Documentation Feedback

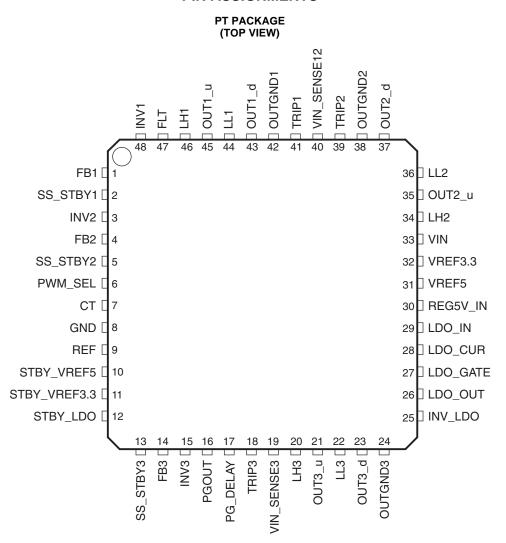

### **PIN ASSIGNMENTS**

### **TERMINAL FUNCTIONS**

| TERMINAI | L   | 1/0 | DESCRIPTION                                                                                                                                                                                                 |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                 |

| СТ       | 7   | I/O | External capacitor from CT to GND adjusts frequency of the triangle oscillator.                                                                                                                             |

| FB1      | 1   | 0   | Feedback output of SBRC-CH1 error amplifier                                                                                                                                                                 |

| FB2      | 4   | 0   | Feedback output of SBRC-CH2 error amplifier                                                                                                                                                                 |

| FB3      | 14  | 0   | Feedback output of SBRC-CH3 error amplifier                                                                                                                                                                 |

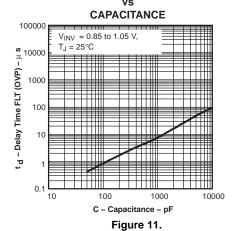

| FLT      | 47  | I/O | Fault latch timer pin. An external capacitor connected between FLT and GND sets FLT enable time up.                                                                                                         |

| GND      | 8   |     | Signal GND                                                                                                                                                                                                  |

| INV1     | 48  | 1   | Inverting input of SBRC-CH1 error amplifier, skip comparator, OVP1/UVP1 comparator, and PG comparator                                                                                                       |

| INV2     | 3   | I   | Inverting input of SBRC-CH2 error amplifier, skip comparator, OVP2/UVP2 comparator, and PG comparator                                                                                                       |

| INV3     | 15  | I   | Inverting input of SBRC-CH3 error amplifier, skip comparator, OVP3/UVP3 comparator, and PG comparator                                                                                                       |

| INV_LDO  | 25  | I   | Inverting input of LDO error amplifier, OVP/UVP comparators, and PG comparator                                                                                                                              |

| LDO_CUR  | 28  | I   | Current sense input of LDO regulator                                                                                                                                                                        |

| LDO_GATE | 27  | 0   | Gate control output of external MOSFET for LDO regulator                                                                                                                                                    |

| LDO_OUT  | 26  | I/O | LDO regulator output. If output voltage has an overshoot when output current changes high to low quickly, it absorbs electrical charge from this pin.                                                       |

| LDO_IN   | 29  | I   | Supply voltage input and current sense input of LDO regulator                                                                                                                                               |

| LH1      | 46  | I/O | Bootstrap capacitor connection for SBRC-CH1 high-side gate driver                                                                                                                                           |

| LH2      | 34  | I/O | Bootstrap capacitor connection for SBRC-CH2 high-side gate driver                                                                                                                                           |

| LH3      | 20  | I/O | Bootstrap capacitor connection for SBRC-CH3 high-side gate driver                                                                                                                                           |

| LL1      | 44  | I/O | SBRC-CH1 high-side gate driving return. Connect this pin to the junction of the high-side and low-side MOSFETs for floating drive configuration. This pin is also an input terminal for current comparator. |

| LL2      | 36  | I/O | SBRC-CH2 high-side gate driving return. Connect this pin to the junction of the high-side and low-side MOSFETs for floating drive configuration. This pin is also an input terminal for current comparator. |

| LL3      | 22  | I/O | SBRC-CH3 high-side gate driving return. Connect this pin to the junction of the high-side and low-side MOSFETs for floating drive configuration. This pin is also an input terminal for current comparator. |

| OUT1_d   | 43  | 0   | Gate drive output for SBRC-CH1 low-side MOSFETs                                                                                                                                                             |

| OUT2_d   | 37  | 0   | Gate drive output for SBRC-CH2 low-side MOSFETs                                                                                                                                                             |

| OUT3_d   | 23  | 0   | Gate drive output for SBRC-CH3 low-side MOSFETs                                                                                                                                                             |

| OUT1_u   | 45  | 0   | Gate drive output for SBRC-CH1 high-side MOSFETs                                                                                                                                                            |

| OUT2_u   | 35  | 0   | Gate drive output for SBRC-CH2 high-side MOSFETs                                                                                                                                                            |

| OUT3_u   | 21  | 0   | Gate drive output for SBRC-CH3 high-side MOSFETs                                                                                                                                                            |

| OUTGND1  | 42  | 0   | Ground for SBRC-CH1 MOSFETs drivers. It is connected to the current limiting comparator's negative input.                                                                                                   |

| OUTGND2  | 38  | 0   | Ground for SBRC-CH2 MOSFETs drivers. It is connected to the current limiting comparator's negative input.                                                                                                   |

| OUTGND3  | 24  | 0   | Ground for SBRC-CH3 MOSFETs drivers. It is connected to the current limiting comparator's negative input.                                                                                                   |

| PGOUT    | 16  | 0   | Power good open-drain output. PG comparators monitor all SBRCs and LDOs overvoltage and undervoltage status. The threshold is ±7%. When one of the outputs is beyond this condition, PGOUT goes low.        |

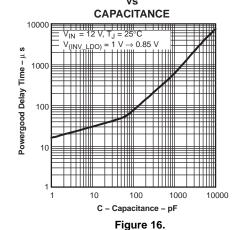

| PG_DELAY | 17  | I/O | Programmable delay for PGOUT. Connect an external capacitor between this pin and GND to specify time delay.                                                                                                 |

| PWM_SEL  | 6   | ı   | PWM or auto PWM/SKIP mode select H= Auto PWM/SKIP L = PWM fixed                                                                                                                                             |

# **TERMINAL FUNCTIONS (continued)**

| TERMINAL     | 1/0 |     | DESCRIPTION                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME         | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                           |  |  |  |  |  |

| REF          | 9   | 0   | 0.85-V reference voltage output. This 0.85-V reference voltage is used to set the output voltage and the reference for the over and undervoltage protections. This reference voltage is dropped down from the internal 5-V regulator. |  |  |  |  |  |

| REG5V_IN     | 30  | - 1 | External 5-V input                                                                                                                                                                                                                    |  |  |  |  |  |

| SS_STBY1     | 2   | I/O | Soft start control and stand by control for SBRC-CH1. Connect an external capacitor between this pin and GND to specify soft start time.                                                                                              |  |  |  |  |  |

| SS_STBY2     | 5   | I/O | Soft start control and stand by control for SBRC-CH2. Connect an external capacitor between this pin and GND to specify soft start time.                                                                                              |  |  |  |  |  |

| SS_STBY3     | 13  | I/O | Soft start control and stand by control for SBRC-CH3. Connect an external capacitor between this pin and GND to specify soft start time.                                                                                              |  |  |  |  |  |

| STBY_LDO     | 12  | ı   | Standby control input for LDO regulator. LDO regulator can be switched into standby mode by grounding the STBY_LDO pin.                                                                                                               |  |  |  |  |  |

| STBY_VREF3.3 | 11  | I   | Standby control for 3.3-V linear regulator                                                                                                                                                                                            |  |  |  |  |  |

| STBY_VREF5   | 10  | I   | Standby control for 5-V linear regulator                                                                                                                                                                                              |  |  |  |  |  |

| TRIP1        | 41  | I   | External resistor connection for SBRC-CH1 output current protection control                                                                                                                                                           |  |  |  |  |  |

| TRIP2        | 39  | I   | External resistor connection for SBRC-CH2 output current protection control                                                                                                                                                           |  |  |  |  |  |

| TRIP3        | 18  | ı   | External resistor connection for SBRC-CH3 output current protection control                                                                                                                                                           |  |  |  |  |  |

| VIN          | 33  | ı   | Supply voltage input                                                                                                                                                                                                                  |  |  |  |  |  |

| VIN_SENSE12  | 40  | Į   | SBRC-CH1/2 supply voltage monitor for reference of current limit. Input range is 4.5 V to 28 V.                                                                                                                                       |  |  |  |  |  |

| VIN_SENSE3   | 19  | I   | SBRC-CH 3 supply voltage monitor for reference of current limit. Input range is 4.5 V to 28 V.                                                                                                                                        |  |  |  |  |  |

| VREF3.3      | 32  | 0   | 3.3-V linear regulator output                                                                                                                                                                                                         |  |  |  |  |  |

| VREF5        | 31  | 0   | 5-V linear regulator output                                                                                                                                                                                                           |  |  |  |  |  |

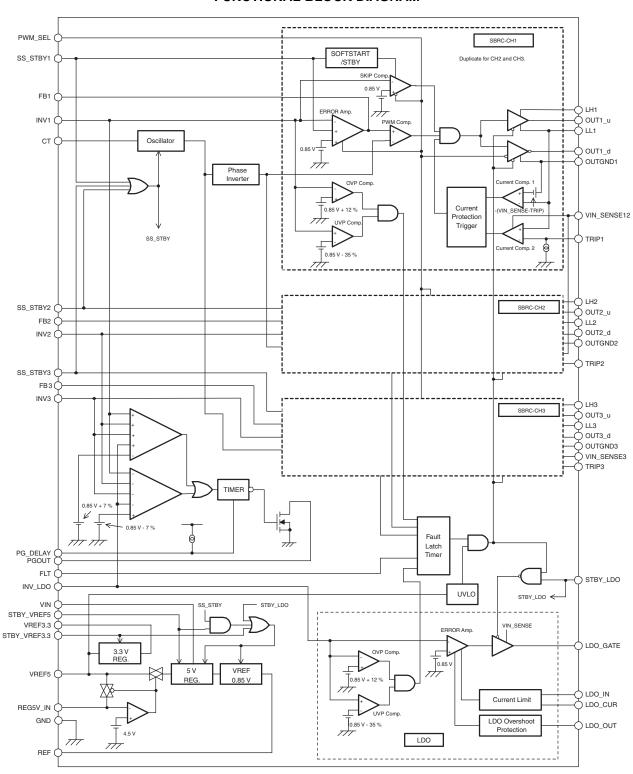

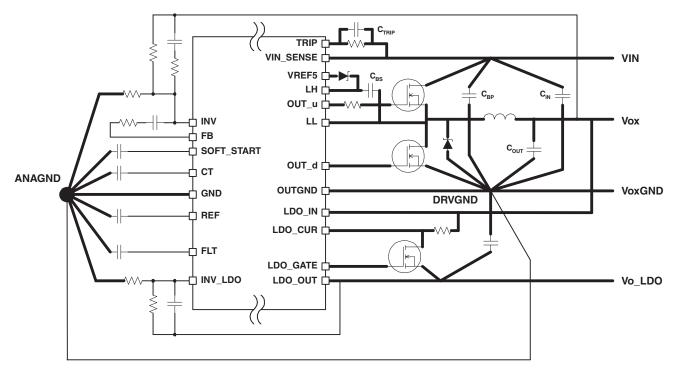

#### **FUNCTIONAL BLOCK DIAGRAM**

#### DETAILED DESCRIPTION

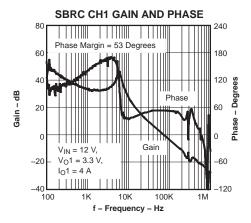

### **PWM Operation**

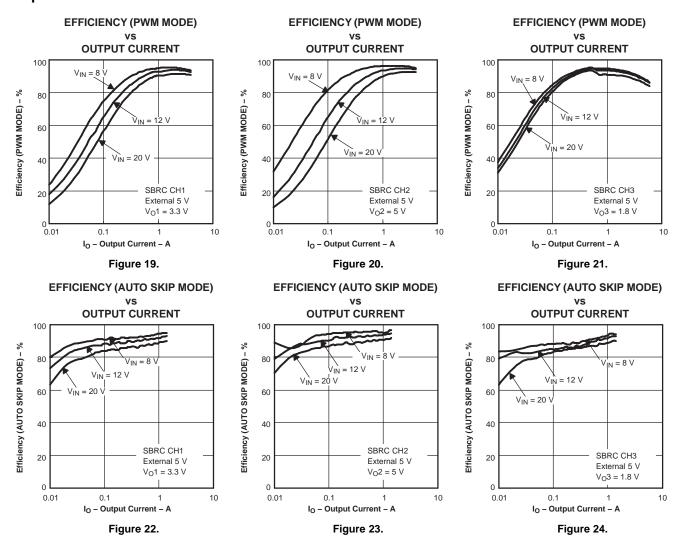

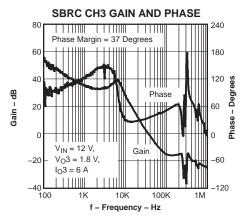

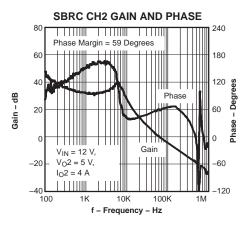

The SBRC block has a high-speed error amplifier to regulate the output voltage of the synchronous buck converter. The output voltage of the SBRC is fed back to the inverting input [INVx (x=1,2,3)] of the error amplifier. The noninverting input is internally connected to a 0.85-V precise band gap reference circuit. The unity gain bandwidth of the amplifier is 2.5 MHz. This decreases the amplifier delay during fast load transients and contributes to a fast response. Loop gain and phase compensation is programmable by an external C, R network between the FBx and INVx pins. The output signal of the error amplifier is compared with a triangular wave to achieve the PWM control signal. The oscillation frequency of this triangular wave sets the switching frequency of the SBRC and is determined by the capacitor connected between the CT and GND pins. The PWM mode is used for the entire load range if the PWM\_SEL pin is set LOW, or used in high output current condition if auto PWM/SKIP mode is selected by setting the same pin to HIGH.

### **Skip Mode Operation**

The PWM\_SEL pin selects either the auto PWM/SKIP mode or fixed PWM mode. If this pin is lower than 0.3-V, the SBRC operates in the fixed PWM mode. If 2.5 V (minimum) or higher is applied, it operates in auto PWM/SKIP mode. In the auto PWM/SKIP mode, the operation changes from constant frequency PWM mode to an energy-saving SKIP mode automatically in accordance with load conditions. Using a MOSFET with ultra-low  $r_{DS(on)}$  when the auto SKIP function is implemented is not recommended. The SBRC block has a hysteretic comparator to regulate the output voltage of the synchronous buck converter during SKIP mode. The delay from the comparator input to the driver output is typically 1.2  $\mu$ s. In the SKIP mode, the frequency varies with load current and input voltage.

### **High-Side Driver**

The high-side driver is designed to drive high current and low  $r_{DS(on)}$  N-channel MOSFET(s). The current rating of the driver is 1.2 A at source and sink. When configured as a floating driver, a 5-V bias voltage is delivered from VREF5 pin. The instantaneous drive current is supplied by the flying capacitor between the LHx and LLx pins since a 5-V power supply does not usually have low impedance. It is recommended to add a 5- $\Omega$  to 10- $\Omega$  resistor between the gate of the high-side MOSFET(s) and the OUTx\_u pin to suppress noise. The maximum voltage that can be applied between the LHx and OUTGNDx pins is 33 V.

When selecting the high-current rating MOSFET(s), it is important to pay attention to both gate drive power dissipation and the rise/fall time against the dead-time between high-side and low-side drivers. The gate drive power is dissipated from the controller IC and it is proportional to the gate charge at  $V_{GS} = 5$  V, PWM switching frequency, and the numbers of all MOSFETs used for low-side and high-side switches. This gate drive loss should not exceed the maximum power dissipation of the device.

### **Low-Side Driver**

The low-side driver is designed to drive high current and low rDS(on) N-channel MOSFET(s). The maximum drive voltage is 5 V from the internal regulator or REG5V\_IN pin. The current rating of the driver is typically 1.5 A at source and sink. Gate resistance is not necessary for the low-side MOSFET for switching noise suppression since it turns on after the parallel diode is turned on (ZVS). It needs the same dissipation consideration when using high current rating MOSFET(s). Another issue that needs precaution is the gate threshold voltage. Even though the OUTx\_d pin is shorted to the OUTGNDx pin with low resistance when the low-side MOSFET(s) is OFF, high dv/dt of the LLx pin during turnon of the high-side arm generates a voltage peak at the OUTx\_d pin through the drain to gate capacitance,  $C_{\rm dg}$ , of the low-side MOSFET(s). To prevent a short period shoot-through during this switching event, the application designer should select MOSFET(s) with adequate threshold voltage.

#### **Dead Time**

The internally defined dead-time prevents shoot-through-current flowing through the main power MOSFETs during switching transitions. Typical value of the dead-time is 100 ns.

Submit Documentation Feedback

#### Standby

The SBRC controller, the LDO controller, and the internal regulators can be switched into standby mode separately as shown in Table 1. The standby mode current, when both controllers and regulators are off, can be as low as 1 nA.

**INPUT FUNCTION** STBY\_VREF3.3  $V_{(REG5V_{IN})} > 4.5 V^{(1)}$ STBY\_VREF5 SS\_STBYx STBY\_LDO VREF5 VREF3.3 **SBRCx** LDO False **OFF** OFF OFF OFF L L<sup>(2)</sup> L<sup>(2)</sup> OFF<sup>(2)</sup> True<sup>(2)</sup> OFF (2) L<sup>(2)</sup> J (2) ON<sup>(2)</sup> OFF<sup>(2)</sup> L L Χ OFF Н L ON OFF OFF L Н L L Χ OFF OFF OFF **OFF** Χ Н Н L L OFF OFF ON ON L L Н L Χ ON ON OFF OFF Χ Н L Н L ON ON OFF OFF Н Н L Χ ON ON OFF **OFF** L Н Н Н L Χ ON ON ON **OFF** L L L Н Χ ON OFF OFF ON Χ OFF OFF ON Н L L Н ON Χ L Н L Н ON OFF OFF ON Н Χ Н L Н ON **OFF** ON ON L L Н Н Χ ON ON OFF ON Χ ON ON OFF ON Н L Н Н Χ ON ON OFF ON L Н Н Н Χ Н Н Н Н ON ON ON ON

Table 1. Standby Logic

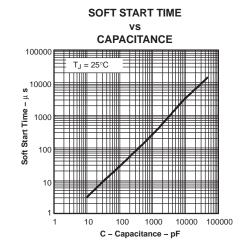

#### Soft Start

Soft start ramp up of the SBRC is controlled by the SS\_STBYx pin voltage, which is controlled by an internal current source and an external capacitor connected between the SS\_STBYx and GND pins. When the STBY\_VREF5 and/or SS\_STBYx pin voltages are forced to LOW, the SBRCx is disabled. When the STBY\_VREF5 pin voltage is set to HIGH and the SS\_STBYx pin floats, the internal current source starts to charge the external capacitor. The output voltage ramps up as the SS\_STBYx pin voltage increases from 0 V to 0.85 V. The soft start time is easily calculated from the supply current and the capacitance value (see application information). The soft start timing circuit for the LDO is integrated into the device. The soft start time is fixed and can be as short as 600 ms. This is observed when the LDO is turned on separately from the SBRC. Simultaneous start-up of one of the SBRC and the LDO, is also possible. Tie the LDO input to the SBRCx output, let both the STBY\_VREF5 and STBY\_LDO voltages rise to the HIGH level, and invoke soft start on the SS\_STBYx pin; the LDO output follows the ramp of the SBRCx output.

### **Overcurrent Protection (OCP)**

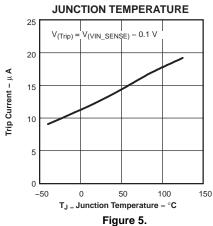

Overcurrent protection (OCP) is achieved by comparing the drain-to-source voltage of the high-side and low-side MOSFET to a set-point voltage, which is defined by both the internal current source,  $I_{(TRIP)}$ , and the external resistor connected between the VIN\_SENSEx and the TRIPx pins.  $I_{(TRIP)}$  has a typical value of 13  $\mu$ A at 25°C. When the drain-to-source voltage exceeds the set-point voltage during low-side conduction, the high-side current comparator becomes active, and the low-side pulse is extended until this voltage comes back below the threshold. If the set-point voltage is exceeded during high-side conduction in the following cycle, the current limit circuit terminates the high-side driver pulse. Together this action has the effect of decreasing the output voltage until the under voltage protection circuit is activated to latch both the high-side and low-side drivers OFF. In the TPS5130, trip current  $I_{(TRIP)}$  has a temperature coefficient of 3400 ppm/°C to compensate for temperature drift of the MOSFET on-resistance.

<sup>(1)</sup> x = True or False

<sup>(2)</sup> This functional mode is not recommended.

#### **OCP for the LDO**

To achieve the LDO current limit, a sense resistor must be placed in series with the N-channel MOSFET drain, connected between the LDO\_IN and LDO\_CUR pins (see reference schematic). If the voltage drop across this sense resistor exceeds 50 mV, the output voltage is reduced to approximately 22% of the nominal value, thus it activates the UVP to start the FLT latch timer. When the time is up, the LDO\_GATE pin is pulled LOW to makes the LDO regulator shut down. Note that all of the SBRCs are latched OFF at the same time since the LDO and the SBRCs share the same FLT capacitor.

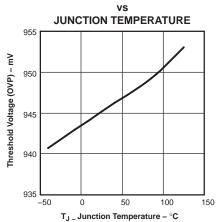

### **Overvoltage Protection (OVP)**

For OVP, the TPS5130 monitors the INVx and INV\_LDO pin voltages. When the INVx or INV\_LDO pin voltage is higher than 0.95 V (0.85 V + 12%), the OVP comparator output goes low and the FLT timer starts to charge an external capacitor connected to FLT pin. After a set time, the FLT circuit latches the high-side MOSFET driver, the low-side MOSFET drivers, and the LDO. The latched state of each block is summarized in Table 2. The timer source current for the OVP latch is 125 mA(typ.), and the time-up voltage is 1.185 V (typ.). The OVP timer is designed to be 50 times faster than the under voltage protection timer described in Table 2.

Table 2. OVP Logic

| OVP OCCURRED AT | HIGH-SIDE MOSFET DRIVER | LOW-SIDE MOSFET DRIVER | LDO |

|-----------------|-------------------------|------------------------|-----|

| SBRC            | Off                     | On                     | Off |

| LDO             | Off                     | Off                    | Off |

### **Undervoltage Protection (UVP)**

For UVP, the TPS5130 monitors the INVx and INV\_LDO pin voltages. When the INVx or INV\_LDO pin voltage is lower than 0.55 V (0.85 V - 35%), the UVP comparator output goes low, and the FLT timer starts to charge the external capacitor connected to FLT pin. Also, when the current comparator triggers the OCP, the UVP comparator detects the under voltage output and starts the FLT capacitor charge, too. After a set time, the FLT circuit latches all of the MOSFET drivers to the OFF state. The timer latch source current for UVP is 2.3  $\mu$ A (typ), and the time-up voltage is also 1.185 V (typ). The UVP function of the LDO controller is disabled when voltage across the pass transistor is less than 0.23 V (typ).

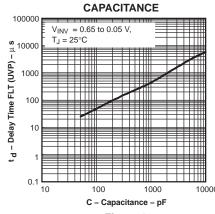

### Fault Latch Timer (FLT)

When an OVP or UVP comparator output goes low, the FLT circuit starts to charge the FLT capacitor. If the FLT pin voltage goes beyond a constant level, the TPS5130 latches the MOSFET drivers. At this time, the state of MOSFET is different depending on the OVP alert and the UVP alert (see Table 2). The enable time used to latch the MOSFET drivers is decided by the value of the FLT capacitor. The charging constant current value depends on whether it is an OVP alert or a UVP alert as shown in the following equation:

FLT source current (OVP) = FLT source current (UVP)  $\times$  50

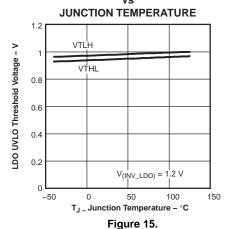

## **Undervoltage Lockout (UVLO)**

When the output voltage of the internal 5-V regulator or the REG5V\_IN voltage decreases below about 4 V, the output stages of all the SBRCs and the LDO are turned off. This state is not latched, and the operation recovers immediately after the input voltage becomes higher than the turnon value again. The typical hysteresis voltage is 100 mV.

#### **UVLO for LDO**

The LDO\_IN voltage is monitored with a hysteretic comparator. When this voltage is less than 1 V, the UVLO circuit disables the UVP/OVP comparators that monitor the INV\_LDO voltage. In case the SBRC overcurrent protection is activated prior to that of the LDO's, this protection function may also be observed.

2 Submit Documentation Feedback

#### **LDO Control**

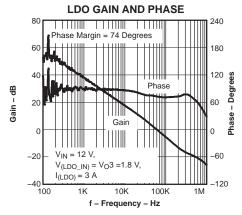

The LDO controller can drive an external N-channel MOSFET. This realizes a fast response as well as an ultralow dropout voltage regulator. For example, it is easy to configure both a 1.8-V and a 1.5-V high current power supply for core and I/O of modern digital processors, one from the SBRC and the other from the LDO. The LDO\_IN voltage range is from 1.1 V to 3.6 V, and the output voltage is adjustable from 0.9 V to 2.5 V by an external resistor divider. Gain and phase of the high-speed error amplifier for this LDO control is internally compensated and is connected to the 0.85-V band gap reference circuit. The gate driver buffer is supplied by VIN\_SENSE voltage. In the relatively high output voltage applications, make sure that output voltage plus threshold voltage of the pass transistor is less than the minimum VIN. More precisely,

$VIN - 0.7 \ge V_{thn} + V_{(LDO\ OUT)}$

where  $V_{thn}$  is the threshold voltage of the  $N_{ch}$  MOSFET.

The LDO controller is also equipped with OVP, UVP, overcurrent limit, and overshoot protection functions.

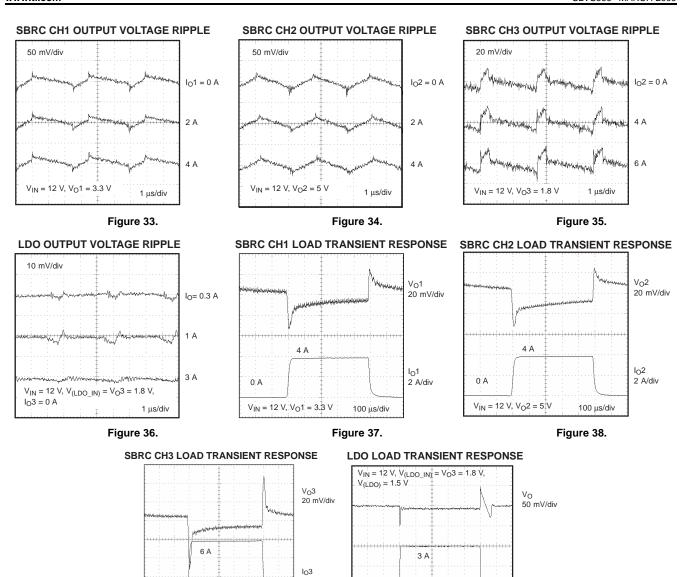

#### **Overshoot Protection**

If the load current changes from high to low very quickly, the LDO regulator output voltage may start to overshoot. To resist this phenomenon, the LDO controller has an overshoot protection function. If the LDO regulator output overshoots, the controller draws electrical charge out from the LDO\_OUT pin to hold it stable.

#### **Power Good**

A single power good circuit monitors the SBRCx output voltages and the LDO output voltage. The PGOUT pin is an open-drain output. When the INV or INV\_LDO voltage goes beyond ±7% of 0.85 V, the PGOUT pin is pulled down to the low level. PGOUT propagation delay is programmable by controlling rising time using an external capacitor connected to the PG\_DELAY pin. During the soft-start period, PGOUT indicates low, in other words, power bad.

| SS_STBY1 | SS_STBY2 | SS_STBY3 | STBY_LDO | PGOUT |

|----------|----------|----------|----------|-------|

| L        | L        | L        | L        | L     |

| Н        | L        | L        | L        | Н     |

| L        | Н        | L        | L        | Н     |

| Н        | Н        | L        | L        | Н     |

| L        | L        | Н        | L        | Н     |

| Н        | L        | Н        | L        | Н     |

| L        | Н        | Н        | L        | Н     |

| Н        | Н        | Н        | L        | Н     |

| H or L   | H or L   | H or L   | Н        | Н     |

Table 3. PGOUT Logic

### 5-V Regulator

An internal linear voltage regulator is used for the high-side driver bootstrap. Since the input voltage ranges from 4.5 V to 28 V, this feature offers a fixed bootstrap voltage to simplify the drive design. It is active if the STBY\_VREF5 is HIGH and has a tolerance of 4%. The 5-V regulator is used for powering the low-side driver and the VREF. When this regulator is disconnected from the MOSFET drivers, it is used only for the source of VREF.

#### 3.3-V Regulator

The TPS5130 has a 3.3-V linear regulator. The output is made from the internal 5-V regulator or an external 5 V from the REG5V\_IN pin. The maximum output current of this regulator is limited to 30 mA by an output current limit control. A ceramic capacitor of 4.7  $\mu$ F should be connected between the VREF3.3 and GND pins to stabilize the output voltage.

### External 5-V Input and 5-V Switch

If the internal 5-V switch detects 5-V input from the REG5V\_IN pin, the internal 5-V regulator is disconnected from the MOSFET drivers. The external 5 V is used for both the high-side bootstrap and the low-side driver, thus increasing the efficiency. When an excess voltage is applied to the REG5V\_IN pin, the OVP timer starts to charge the FLT capacitor and latches all the MOSFET drivers and the LDO at OFF state after a set time.

#### **Phase Inverter**

The SBRC3 of the TPS5130 operates in the same phase as the internal triangular oscillator output while the SBRC1 and the SBRC2 operate 180° out of phase. When the SBRC1 and the SBRC3 (or the SBRC2 and the SBRC3) share the same input power supply, the TPS5130 realizes 180° out of phase operation that reduces input current ripple and enables the input capacitor value smaller.

Submit Documentation Feedback

### TYPICAL CHARACTERISTICS

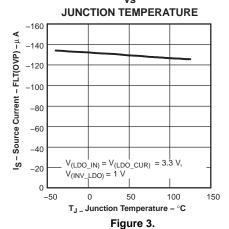

Figure 1. SOURCE CURRENT FLT(OVP)

TRIP CURRENT vs

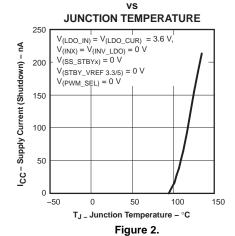

### **SUPPLY CURRENT (SHUTDOWN)**

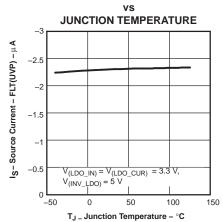

SOURCE CURRENT FLT(UVP)

Figure 4.

SINK CURRENT (LDO\_GATE)

Figure 6.

### TYPICAL CHARACTERISTICS (continued)

Figure 7. OSCILLATOR FREQUENCY

Figure 9.

DELAY TIME FLT(OVP)

THRESHOLD VOLTAGE (OVP)

Figure 8.

OUTPUT MAXIMUM DUTY CYCLE

Figure 10.

DELAY TIME FLT(UVP)

Figure 12.

### **TYPICAL CHARACTERISTICS (continued)**

Figure 13.

LDO UVLO THRESHOLD VOLTAGE

CURRENT LIMIT THRESHOLD VOLTAGE FOR LDO

VS

JUNCTION TEMPERATURE

60

40

40

V(LDO\_IN) = 3.3 V

V(INV\_LDO) = 0.5 V

-50

0

50

100

150

Figure 14.

POWERGOOD DELAY TIME

vs

$T_{J}$  \_ Junction Temperature –  $^{\circ}C$

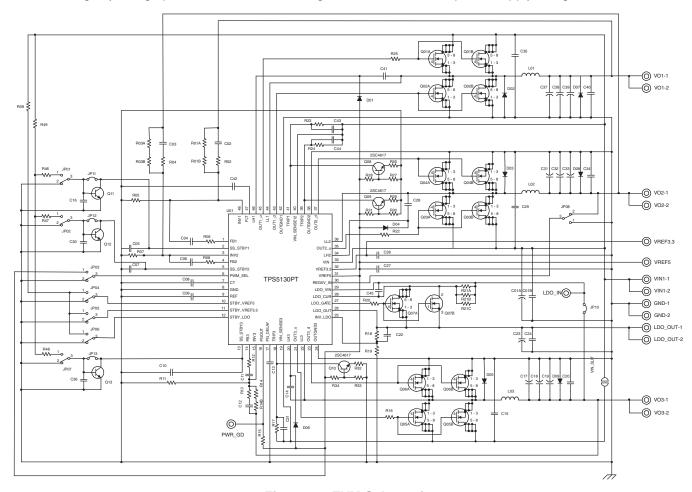

### **APPLICATION INFORMATION**

The design shown is a reference design for a notebook PC application. An evaluation module (EVM) is available for customer testing and evaluation.

The following key design procedures aid in the design of the notebook PC power supply using TPS5130.

Figure 17. EVM Schematic

An optional circuit composed of Q08, Q09, Q10, R26, R27, R28, R29, R30, R31, R32, R33, and R34 can be used to increase temperature coefficient of the trip current.

Submit Documentation Feedback

### **Output Voltage Setpoint Calculation**

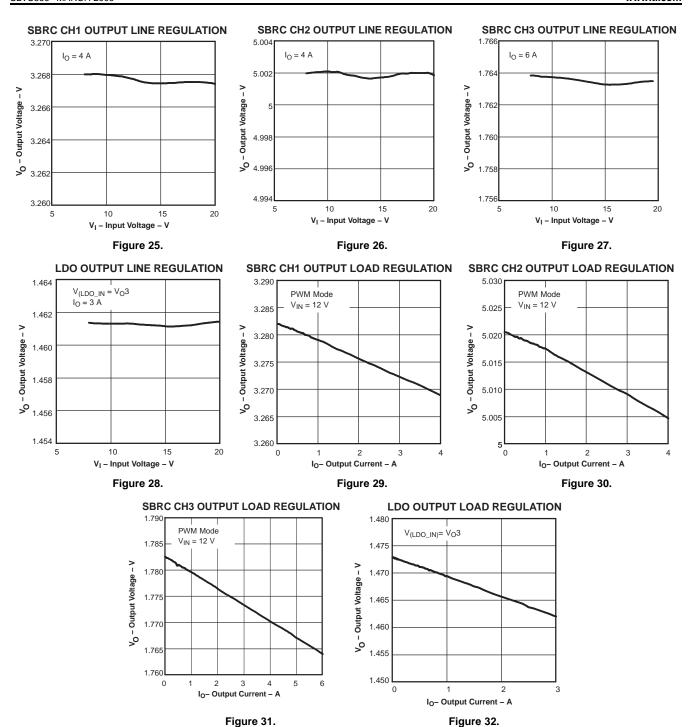

In Equation 1, assume the output voltage of SBRC1 ( $V_O1$ ), SBRC2 ( $V_O2$ ), SBRC3 ( $V_O3$ ), and LDO ( $V_O4$ ) are 3.3 V, 5 V, 1.8 V, and 1.5 V respectively. The reference voltage and the voltage divider set the output voltage. In the TPS5130, the reference voltage is 0.85 V, and the divider is composed of three resistors in the EVM design:

- R01A, R01B, and R05 for the first SBRC output

- R03A, R03B, and R07 for the second SBRC output

- R14A, R14B, and R11 for the third SBRC output

- R18 and R19 for LDO regulator output

$$V_{O} = \frac{R1 \times V_{ref}}{R2} + V_{ref} \text{ or } R2 = \frac{R1 \times V_{ref}}{V_{O} - V_{ref}}$$

$$\tag{1}$$

where

R1 is the top resistor ( $k\Omega$ ) (R01A + R01B or R03A + R03B or R14A + R14B or R18)

R2 is the bottom resistor ( $k\Omega$ ) (R05 or R07 or R11 or R19)

V<sub>O</sub> is the required output voltage (V)

V<sub>ref</sub> is the reference voltage (0.85 V in TPS5130).

The value for R1 is set as a part of the compensation circuit and the value of R2 may be calculated to achieve the desired output voltage. In the EVM design, the value of R1 is determined as R01A = 27 k $\Omega$  and R01B = 1.8 k $\Omega$  for V<sub>0</sub>1, R03A = 47 k $\Omega$  and R03B = 1.8 k $\Omega$  for V<sub>0</sub>2, R14A = 10 k $\Omega$  and R14B = 1.2 k $\Omega$  for V<sub>0</sub>3, and R18 = 6.8 k $\Omega$  + 820  $\Omega$  for V<sub>0</sub>4 considering stability. For V<sub>0</sub>1, see Equation 2.

$$R05 = \frac{(27 \text{ k} + 1.8 \text{ k}) \times 0.85}{3.3 - 0.85} = 9.99 \text{ k}\Omega$$

(2)

Therefore, use 10 k $\Omega$ .

In a same manner, R07 = R11 = R19 =  $10 \text{ k}\Omega$  as shown in Equation 3.

$$R07 = \frac{(47 \text{ k} + 1.8 \text{ k}) \times 0.85}{5 - 0.85} = 10.00 \text{ k}\Omega$$

$$R11 \, = \, \frac{(10 \; k \, + \, 1.2 \; k) \, \times \, 0.85}{1.8 \, - \, 0.85} \, = \, 10.02 \; k\Omega$$

$$R19 = \frac{(6.8 \text{ k} + 820) \times 0.85}{1.5 - 0.85} = 9.96 \text{ k}\Omega$$

(3)

The values of R01B, R03B, R14B and R19 are chosen so that the calculated values of R05, R07, R11, and R19 are standard value resistors and the  $V_{\rm O}$  setpoint maintains the highest precision. This is best accomplished by combining two resistor values. If a standard value resistor cannot be applied, use a value for R01A, R03A, R14A, and R18 that is just slightly less than the desired total. A small resistor value in the range of tens or hundreds of ohms for R01B, R03B, R14B and R18 can then be added to generate the desired final value.

### **Output Inductor Selection**

The required value for the output filter inductor can be calculated by using Equation 4, assuming the magnitude of the ripple current is 20% of the maximum output current:

$$L_{(out)} = \frac{VIN - V_O}{0.2 \times I_O} \times \frac{V_O}{VIN} \times \frac{1}{f_S}$$

(4)

where

I<sub>(ripple)</sub> is the peak-to-peak ripple current (A) through the inductor

Io is the output current

$r_{DS(on)}$  is the on-time resistance of MOSFET ( $\Omega$ )

R<sub>L</sub> is the inductor dc resistance (W).

From the equation, it can be seen that the current ripple can be adjusted by changing the output inductor value.

TEXAS INSTRUMENTS

SLVS866-MARCH 2009 www.ti.com

For example,

If VIN = 8 V,

$$V_O$$

= 3.3 V,  $I_O$  = 4 A,  $r_{DS(on)}$  = 25 m $\Omega$ ,  $R_L$  = 10 m $\Omega$ ,  $f_s$  = 300 kHz,  $L_{(out)}$  = 4  $\mu$ H Then, the ripple current  $I_{(ripple)}$  = 1.57 A

#### **Output Capacitor Selection**

Selection of the output capacitor is basically dependent on the amount of peak-to-peak ripple voltage allowed on the output and the ability of the capacitor to dissipate the RMS ripple current. Assuming that the ESR of the output filter sees the entire inductor ripple current then  $V_{pp}$  can be calculated as shown in Equation 5:

$$V_{pp} = I_{(ripple)} \times R_{(esr)}$$

(5)

A suitable capacitor must be chosen so that the peak-to-peak output ripple is within the limits allowable for the application.

### **Output Capacitor RMS Current**

Assuming the inductor ripple current totally goes through the output capacitor to ground, the RMS current in the output capacitor can be calculated as shown in Equation 6:

$$I_{O}(rms) = \frac{I_{(ripple)}}{\sqrt{12}}$$

(6)

where

I<sub>O(rms)</sub> is maximum RMS current in the output capacitor (A)

$I_{(ripple)}$  is the peak-to-peak inductor ripple current (A)

For example, if  $I_{(ripple)} = 1.57$  A, then  $I_{O(rms)} = 0.45$  A.

### **Input Capacitor RMS Current**

Because the SBRC3 of the TPS5130 operates 180 $^{\circ}$  off phase against the SBRC1 and SBRC2, total RMS current in the input capacitor ( $I_{I(rms)}$ ) is calculated as follows, assuming the input current totally goes into the input capacitor to the power ground, and ignoring ripple current in the inductor.

When the duty cycle of the SBRC2 (D2) is over 50%, I<sub>I(rms)</sub> is calculated as shown in Equation 7.

$$I_{I}(rms) = \sqrt{(D1 \times I_{O}1^{2}) + (D2 \times I_{O}2^{2}) + (D3 \times I_{O}3^{2}) + (2D1 \times I_{O}1 \times I_{O}2) + (2D2 - 1) \times I_{O}2 \times I_{O}3 - I_{O}x^{2}}$$

$$I_{O}x = (D1 \times I_{O}1) + (D2 \times I_{O}2) + (D3 \times I_{O}3) \qquad D2 \ge 0.5 \ge D1 \ge D3$$

$$(7)$$

where

I<sub>I(rms)</sub> is the input RMS current in the input capacitor

Dx is duty cycles, defined in this case as V<sub>O</sub>/V<sub>I</sub> of the SBRCx

When D2 is less than 50%, I<sub>I(rms)</sub> is calculated as shown in Equation 8.

$$I_{I}(rms) = \sqrt{(D1 \times I_{O}1^{2}) + (D2 \times I_{O}2^{2}) + (D3 \times I_{O}3^{2}) + (2D1 \times I_{O}1 \times I_{O}2) - I_{O}x^{2}}$$

(8)

For example,

If VIN = 12 V,

$$V_O1$$

= 3.3 V,  $V_O2$  = 5 V (D2 = 0.42),  $V_O3$  = 1.8 V,  $I_O1$  =  $I_O2$  = 4 A,  $I_O3$  = 6 A Then,  $I_{I(rms)}$  = 3.44 A

On the contrary, if three SBRCs operate in a same phase the RMS current is calculated as shown in Equation 9.

$$I_{1}(rms) = \sqrt{(D1 \times I_{O}1^{2}) + (D2 \times I_{O}2^{2}) + (D3 \times I_{O}3^{2}) + (2D1 \times I_{O}1 \times I_{O}2) + (2D3 \times I_{O}3) \times (I_{O}1 + I_{O}2) - I_{O}x^{2}}}$$

(9)

20

#### **Soft Start**

The soft start timing can be adjusted by selecting the soft-start capacitor value (see Equation 10).

$$C(soft) = 2.3 \times 10^{-6} \times \frac{t(soft)}{0.85}$$

(10)

where

$C_{(soft)}$  is the soft-start capacitor ( $\mu F$ ) (C05, C07, and C10 in EVM design)  $t_{(soft)}$  is the start-up time (seconds)

For example

If  $t_{(soft)}$  = 5 ms Then,  $C_{(soft)}$  = 0.0135  $\mu F$

#### **Current Protection**

The current limit in TPS5130 is set using an internal current source and an external resistor (R17, R23, and R24). The current limit protection circuit compares the drain to source voltage of the high-side and low-side MOSFET(s) with respect to the set-point voltage. If the voltage up exceeds the limit during high-side conduction, the current limit circuit terminates the high-side driver pulse. If the set point voltage is exceeded during low-side conduction, the low side pulse is extended through the next cycle. Together this action has the effect of decreasing the output voltage until the under voltage protection circuit is activated and the fault latch is set and both the high-side and low-side MOSFET drivers are shut off. Equation 11 should be used for calculating the external resistor value for current protection set point.

$$R(cl) = \frac{r_{DS(on)} \times \left(I_{(trip)} + \frac{I_{(ripple)}}{2}\right)}{13 \times 10^{-6}}$$

(11)

where

$R_{(cl)}$  is the external current limit resistor (R17, R23 and R24)  $r_{DS(on)}$  is the low-side MOSFET(Q02, Q04, and Q06) on-time resistance  $I_{(trip)}$  is the required current limit

For example

If  $r_{DS(on)} = 25 \text{ m}\Omega$ ,  $I_{(trip)} = 4 \text{ A}$ ,  $I_{(ripple)} = 1.57 \text{ A}$

Then,  $R_{(cl)}$ = 9.2 k $\Omega$

It should be noted that  $r_{DS(on)}$  of a FET is highly dependent on temperature, so to ensure full output at maximum operating temperature, the value of  $r_{DS(on)}$  in Equation 11 should be adjusted. For maximum stability, it is recommended that the high-side MOSFET(s) has the same, or slightly higher  $r_{DS(on)}$  than the low-side MOSFET(s). If the low-side MOSFET(s) has a higher  $r_{DS(on)}$ , in certain low duty cycle applications it may be possible for the device to regulate at an output current higher than that set by Equation 11 by increasing the high-side conduction time to compensate for the missed conduction cycle caused by the extension of the previous low-side pulse.

TEXAS INSTRUMENTS

SLVS866-MARCH 2009 www.ti.com

#### **Timer Latch**

The TPS5130 includes fault-latch function with a user-adjustable timer to latch the MOSFET drivers in case of a fault condition. When either the OVP or UVP comparator detect a fault condition, the timer starts to charge FLT capacitor (C42), which is connected with FLT pin. The circuit is designed so that, for any value of FLT capacitor, the undervoltage latch time  $t_{(uvplatch)}$  is approximately 50 times larger than the overvoltage latch time  $t_{(ovplatch)}$ . Equation 12 shows the equations needed to calculate the required value of the FLT capacitor for the desired overvoltage and undervoltage latch delay times are:

$$C_{\text{(lat)}} = 2.3 \times 10^{-6} \times \frac{t_{\text{(uvplatch)}}}{1.185}$$

and

$$C_{\text{(lat)}} = 125 \times 10^{-6} \times \frac{t_{\text{(ovplatch)}}}{1.185}$$

(12)

where

C<sub>(lat)</sub> is the external capacitor

$t_{(uvplatch)}$  is the time from UVP detection to latch

t<sub>(ovplatch)</sub> is the time from OVP detection to latch

For the EVM,  $t_{(uvplatch)} = 5$  ms and  $t_{(ovplatch)} = 0.1$  ms, so  $C_{(lat)} = 0.01$   $\mu F$ . If the voltage on the FLT pin reaches 1.185 V, the fault latch is set, and the MOSFET drivers are set as described in the following sections.

#### **Undervoltage Protection**

The undervoltage comparator circuit continually monitors the voltage at the INV and INV\_LDO pins. If the voltage at either pin falls below 65% of the 0.85 V reference, the timer begins to charge the FLT capacitor. if the fault condition persists beyond the time  $t_{(uvplatch)}$ , the fault latch is set and both the high-side and low-side drivers, and LDO regulator drivers are forced OFF.

#### **Short-Circuit Protection**

The short-circuit protection circuitry uses the UVP circuit to latch the MOSFET drivers. When the current limit circuit limits the output current, then the output voltage goes below the target output voltage and UVP comparator detects a fault condition as described above.

#### **Overvoltage Protection**

The overvoltage comparator circuit continually monitors the voltage at the INV and INV\_LDO pins. If the voltage at either pin rises above 112% of the 0.85 V reference, the timer begins to charge the FLT capacitor. If the fault condition persists beyond the time  $t_{\text{(ovplatch)}}$ , the fault latch is set and the high-side drivers are forced OFF, while the low-side drivers are forced ON, and LDO regulator drivers are forced OFF

#### **CAUTION:**

Do not set the FLT terminal to a lower voltage (or GND) while the device is timing out an OVP or UVP event. If the FLT terminal is manually set to a lower voltage during this time, output overshoot may occur. The TPS5130 must be reset by grounding SS\_STBYx and STBY\_LDO, or dropping down REG5V\_IN.

#### **Disablement of the Protection Function**

If it is necessary to inhibit the protection functions of the TPS5130 for troubleshooting or other purposes, the OCP, OVP, and UVP circuits may be disabled.

- OCP(SBRC): Remove the current limit resistors R17, R23 and R24 to disable the current limit function.

- OCP(LDO): Short-circuit R21 to disable the current limit function.

- OVP, UVP: Grounding the FLT terminal can disable OVP and UVP.

22

### **LDO Regulator Application Information**

#### **Output Capacitor Selection**

To keep stable operation of the LDO, capacitance of more than 33  $\mu F$  and  $R_{(esr)}$  of more than 30 m $\Omega$  are recommended for the output capacitor.

#### **Power MOSFET Selection**

Also, to keep stable operation of LDO, lower input capacitance is recommended for the external power MOSFET. However, input capacitance that is too small may lead the feedback loop into an unstable region. In this case, the gate resistor of several hundreds ohms keeps the LDO operation in the stable state.

#### **Current Protection**

If excess output current flows through sense resistor (R21) and the voltage drop exceeds 50 mV, the output voltage is reduced to approximately 22% of the nominal value, thus activates UVP to start the FLT latch timer.

When the set current is 3 A, the value of R21 is 16.7 m $\Omega$ .

### **Layout Guidelines**

Good power supply results occur only when care is given to proper design and layout. Layout affects noise pickup and generation and can cause a good design to perform with less than expected results. With a range of currents from milliamps to tens amps, good power supply layout is much more difficult than most general PCB designs. The general design should proceed from the switching node to the output, then back to the driver section and, finally, parallel the low-level components. Below are specific points to consider before the layout of a TPS5130 design begins.

- A four-layer PCB design is recommended for design using the TPS5130. For the EVM design, the top layer

contains the interconnection to the TPS5130, plus some additional signal traces. Layer2 is fully devoted to the

ground plane. Layer3 has some signal traces. The bottom layer is almost devoted to ANAGND, and the rest

is to other signal trace.

- All sensitive analog components such as INV, REF, CT, GND, FLT, and SS\_STBY should be referenced to ANAGND.

- Ideally, all of the area directly under the TPS5130 chip should also be ANAGND.

- ANAGND and DRVGND should be isolated as much as possible, with a single point connection between them.

Copyright © 2009, Texas Instruments Incorporated

Figure 18. PCB Diagram

#### Low-Side MOSFET(s)

- The source of low-side MOSFET(s) should be referenced to DRVGND, otherwise ANAGND is subject to the noise of the outputs.

- DRVGND should be connected to the main ground plane close to the source of the low-side MOSFET.

- OUTGND should be placed close to the source of low side MOSFET(s).

- The Schottky diode anode, the returns for the high frequency bypass capacitor for the MOSFETs, and the source of the low-side MOSFET(s) traces should be routed as close together as possible.

### **Connections**

- Connections from the drivers to the gate of the power MOSFETs should be as short and wide as possible to

reduce stray inductance. This becomes more critical if external gate resistors are not being used. In addition,

as for the current limit noise issue, use of a gate resistor on the high-side MOSFET(s) considerably reduces

the noise at the LL node, improving the performance of the current limit function.

- The connection from LL to the power MOSFETs should be as short and wide as possible.

#### **Bypass Capacitor**

- The bypass capacitor for VIN\_SENSE should be placed close to the TPS5130.

- The bulk storage capacitors across VIN should be placed close to the power MOSFETs. High-frequency bypass capacitors should be placed in parallel with the bulk capacitors and connected close to the drain of the high-side MOSFET(s) and to the source of the low-side MOSFET(s).

- For aligning phase between the drain of high-side MOSFET(s) and the trip-pin, and for noise reduction, a 0.1 μF capacitor C<sub>(TRIP)</sub> should be placed in parallel with the trip resistor.

#### **Bootstrap Capacitor**

- The bootstrap capacitor C<sub>(BS)</sub> (connected from LH to LL) should be placed close to the TPS5130.

- LH and LL should be routed close to each other to minimize noise coupling to these traces.

- LH and LL should not be routed near the control pin area (INV, FB, REF, etc.).

24

### **Output Voltage**

- The output voltage sensing trace should be isolated by either ground plane.

- The output voltage sensing trace should not be placed under the inductors on same layer.

- The feedback components should be isolated from output components, such as, MOSFETs, inductors, and output capacitors. Otherwise the feedback signal line is susceptible to output noise.

- The resistors for setup output voltage should be referenced to ANAGND.

- The INV trace should be as short as possible.

### **Output Characteristics**

Figure 39.

100 μs/div

0 A

$V_{IN} = 12 \text{ V}, V_{O}3 = 1.8 \text{ V}$

2 A/div

30 mA

100 μs/div

I<sub>O</sub> 1 A/div

Figure 41.

Figure 43.

Figure 42.

Figure 44.

10-Dec-2020

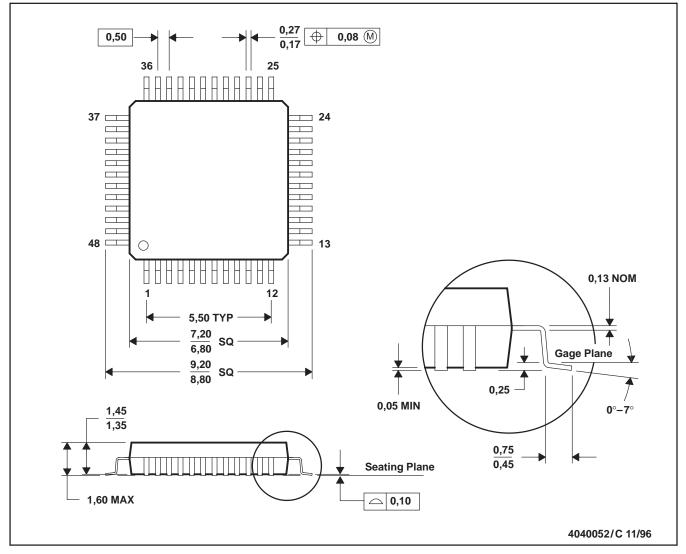

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                         |         |

| TPS5130QPTRQ1    | ACTIVE | LQFP         | PT                 | 48   | 1000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 125   | 5130Q                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.