One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## How to Set Up and Use the ADuCM310

### SCOPE

This reference manual provides a detailed description of the ADuCM310 functionality and features.

Full specifications on the ADuCM310 are available in the product data sheet, which must be consulted in conjunction with this reference manual when using the device.

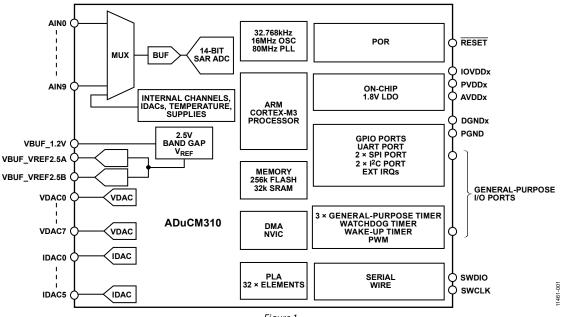

**FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# TABLE OF CONTENTS

| Scope 1                                      |

|----------------------------------------------|

| Functional Block Diagram 1                   |

| Revision History                             |

| Using the ADuCM310 Hardware Reference Manual |

| Number Notations                             |

| Register Access Conventions 5                |

| Acronyms and Abbreviations 5                 |

| Introduction to the ADuCM310                 |

| Main Features of the ADuCM3107               |

| Memory Organization                          |

| Clocking Architecture                        |

| Clocking Architecture Features9              |

| Clocking Architecture Block Diagram9         |

| Clocking Architecture Overview10             |

| Clocking Architecture Operation10            |

| Register Summary: Clock Architecture10       |

| Register Details: Clock Architecture10       |

| Power Management Unit14                      |

| Power Management Unit Features14             |

| Power Management Unit Overview14             |

| Power Management Unit Operation14            |

| Code Examples15                              |

| Register Summary: Power Management Unit      |

| Register Details: Power Management Unit      |

| ARM Cortex-M3 Processor17                    |

| ARM Cortex-M3 Processor Features17           |

| ARM Cortex-M3 Processor Overview             |

| ARM Cortex-M3 Processor Operation            |

| ARM Cortex-M3 Processor Related Documents18  |

| ADC Circuit 19                               |

| ADC Circuit Features 19                      |

| ADC Circuit Block Diagram19                  |

| ADC Circuit Overview19                       |

| ADC Circuit Operation                        |

| ADC Transfer Function                        |

| ADC Typical Setup Sequence                   |

| ADC Input Buffer                             |

| ADC Internal Channels                        |

| ADC Support Circuits                         |

| Register Summary: ADC Circuit                |

| Register Details: ADC Circuit                  | 28 |

|------------------------------------------------|----|

| Register Summary: Additional Registers         | 32 |

| Register Details: Additional Registers         | 32 |

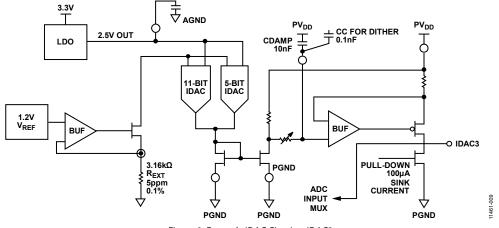

| IDACs                                          | 34 |

| IDAC Features                                  | 34 |

| IDAC Block Diagram                             | 34 |

| IDAC Overview                                  | 34 |

| Register Summary: IDAC                         | 40 |

| Register Details: IDAC                         | 40 |

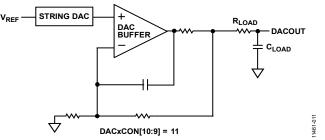

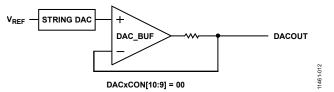

| VDACs                                          | 46 |

| VDAC Features                                  | 46 |

| VDAC Block Diagram                             | 46 |

| VDAC Overview                                  | 46 |

| VDAC Operation                                 | 47 |

| Register Summary: VDAC                         | 49 |

| Register Details: VDAC                         | 49 |

| System Exceptions and Peripheral Interrupts    | 56 |

| Cortex-M3 and Fault Management                 | 56 |

| External Interrupt Configuration               | 59 |

| Register Summary: External Interrupts          | 59 |

| Register Details: External Interrupts          | 60 |

| Low Voltage Analog Die Interrupt Configuration | 63 |

| Register Summary: Low Voltage Die Interrupts   | 63 |

| Register Details: Low Voltage Die Interrupts   | 64 |

| Reset                                          | 65 |

| Reset Features                                 | 65 |

| Reset Operation                                | 65 |

| Register Summary: Reset                        | 65 |

| Register Details: Reset                        | 66 |

| DMA Controller                                 | 67 |

| DMA Features                                   | 67 |

| DMA Overview                                   | 67 |

| DMA Operation                                  | 67 |

| Interrupts                                     | 68 |

| DMA Priority                                   | 68 |

| Channel Control Data Structure                 | 68 |

| Control Data Configuration                     | 69 |

| DMA Transfer Types (CHNL_CFG[2:0])             | 70 |

| Address Calculation                            | 72 |

| Aborting DMA Transfers                         | 72 |

# ADuCM310 Hardware Reference Manual

| ]      | Register Summary: DMA                    | .73 |

|--------|------------------------------------------|-----|

| ]      | Register Details: DMA                    | .73 |

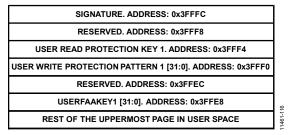

| Fla    | sh Controller                            | .79 |

| ]      | Flash Controller Features                | .79 |

| ]      | Flash Controller Overview                | .79 |

| ]      | Flash Controller Operation               | .80 |

| ]      | Flash Memory Operation                   | .81 |

| ]      | Register Summary: Flash Controller       | .87 |

| ]      | Register Details: Flash Controller       | .88 |

| Sil    | icon Identification                      | .97 |

| ]      | Register Summary: Silicon Identification | .97 |

| ]      | Register Details: Silicon Identification | .97 |

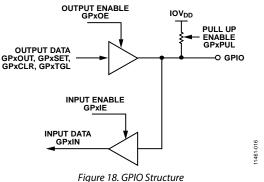

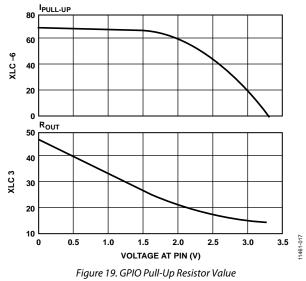

| Di     | gital Inputs/Outputs                     | .98 |

| ]      | Digital Inputs/Outputs Features          | .98 |

| ]      | Digital Inputs/Outputs Block Diagram     | .98 |

| ]      | Digital Inputs/Outputs Overview          | .98 |

| ]      | Digital Inputs/Outputs Operation         | .99 |

| ]      | Digital Port Multiplex                   | 100 |

| ]      | Register Summary: Digital Input/Output   | 102 |

| ]      | Register Details: Digital Input/Output   | 103 |

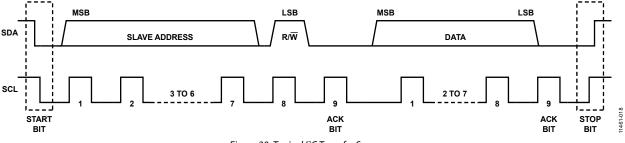

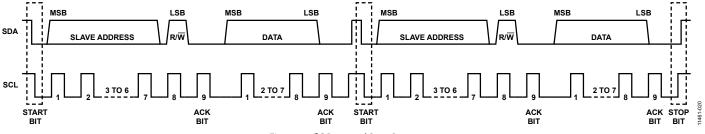

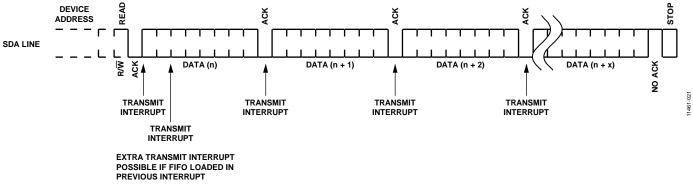

| $I^2C$ | C Serial Interface                       | 110 |

| ]      | I <sup>2</sup> C Features                | 110 |

| ]      | I <sup>2</sup> C Overview                | 110 |

| ]      | I <sup>2</sup> C Operation               | 110 |

| ]      | I <sup>2</sup> C Operating Modes         | 112 |

| ]      | Register Summary: I <sup>2</sup> C0      | 114 |

| ]      | Register Details: I <sup>2</sup> C0      | 115 |

| ]      | Register Summary: I <sup>2</sup> C1      | 124 |

| ]      | Register Details: I <sup>2</sup> C1      | 125 |

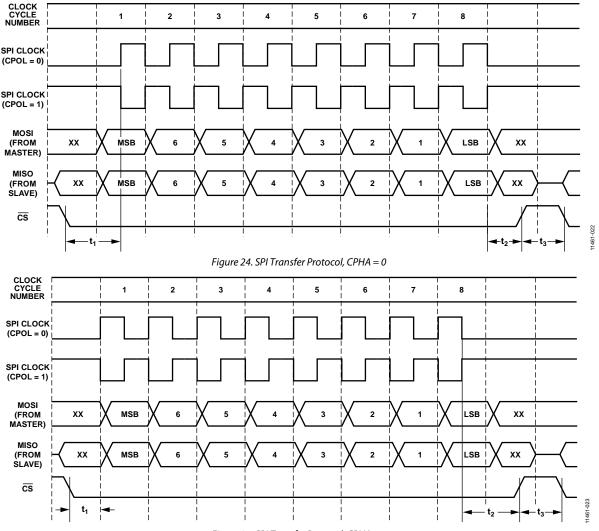

| Sei    | rial Peripheral Interfaces               | 134 |

| :      | SPI Features                             | 134 |

| :      | SPI Overview                             | 134 |

| :      | SPI Operation                            | 134 |

| 5      | SPI Transfer Initiation                  | 135 |

| 5      | SPI Interrupts                           | 137 |

| :      | SPI Wire-OR'ed Mode (WOM)                | 138 |

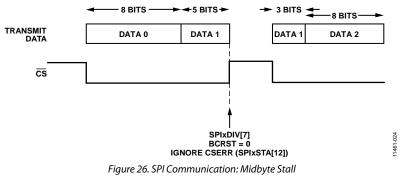

| 5      | SPI CSERR Condition                      | 138 |

| :      | SPI DMA                                  | 138 |

| 1      | SPI and Power-Down Modes                 | 139 |

| ]      | Register Summary: SPI0                   | 140 |

| ]      | Register Details: SPI0                   | 140 |

|        |                                          |     |

| Register Summary: SPI1                    | 144 |

|-------------------------------------------|-----|

| Register Details: SPI1                    | 144 |

| UART Serial Interface                     | 148 |

| UART Features                             | 148 |

| UART Overview                             | 148 |

| UART Operation                            | 148 |

| Register Summary: UART                    | 152 |

| Register Details: UART                    | 152 |

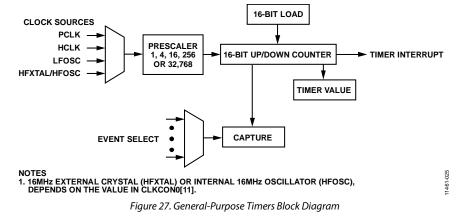

| General-Purpose Timers                    | 157 |

| General-Purpose Timers Features           | 157 |

| General-Purpose Timers Block Diagram      | 157 |

| General-Purpose Timers Overview           | 157 |

| General-Purpose Timers Operation          | 158 |

| Register Summary: General-Purpose Timer 0 | 160 |

| Register Details: General-Purpose Timer 0 | 160 |

| Register Summary: General-Purpose Timer 1 | 163 |

| Register Details: General-Purpose Timer 1 | 163 |

| Register Summary: General-Purpose Timer 2 | 166 |

| Register Details: General-Purpose Timer 2 | 166 |

| Watchdog Timer                            | 169 |

| Watchdog Timer Features                   | 169 |

| Watchdog Timer Block Diagram              | 169 |

| Watchdog Timer Overview                   | 169 |

| Watchdog Timer Operation                  | 169 |

| Register Summary: Watchdog Timer          | 169 |

| Register Details: Watchdog Timer          | 170 |

| Wake-Up Timer                             | 172 |

| Wake-Up Timer Features                    | 172 |

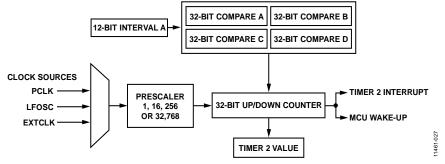

| Wake-Up Timer Block Diagram               | 172 |

| Wake-Up Timer Overview                    | 172 |

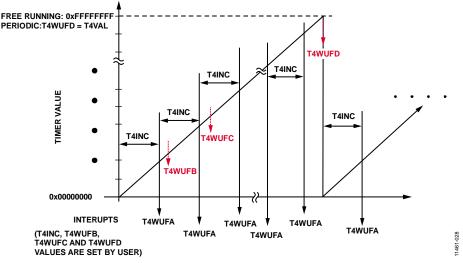

| Wake-Up Timer Operation                   | 172 |

| Register Summary: Wake-Up Timer           | 174 |

| Register Details: Wake-Up Timer           | 174 |

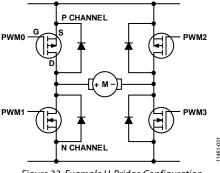

| Pulse Width Modulation (PWM)              | 178 |

| PWM Features                              | 178 |

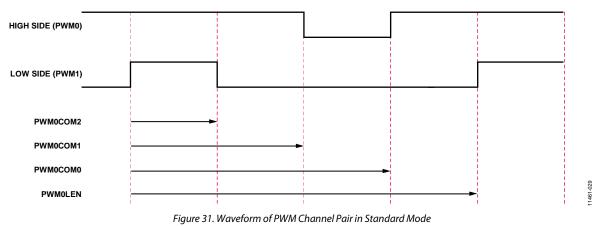

| PWM Overview                              | 178 |

| PWM Operation                             | 178 |

| PWM Interrupt Generation                  | 180 |

| Register Summary: PWM                     | 181 |

| Register Details: PWM                     | 181 |

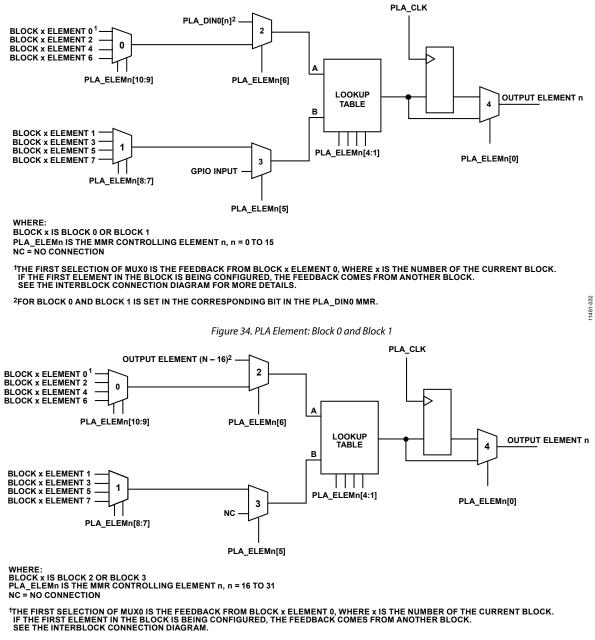

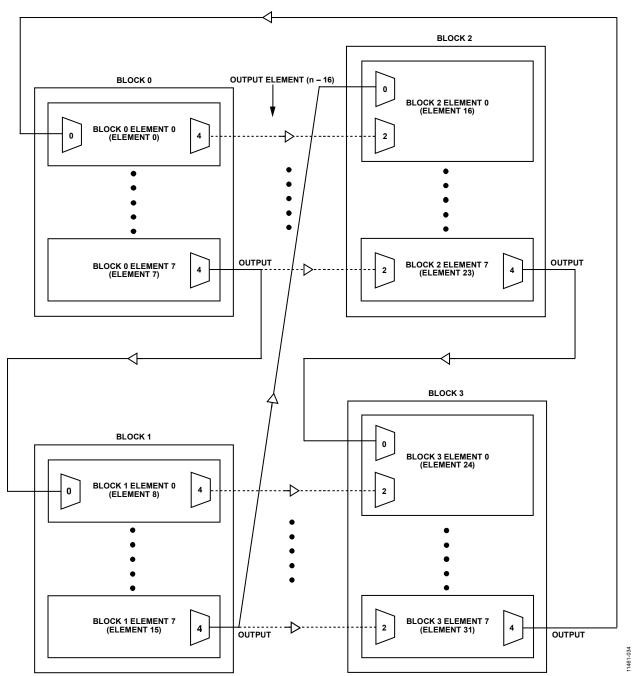

| Programmable Logic Array (PLA)            | 185 |

# UG-549

# ADuCM310 Hardware Reference Manual

| PLA Features  |  |

|---------------|--|

| PLA Overview  |  |

| PLA Operation |  |

## **REVISION HISTORY**

| 6/2019—Rev. A to Rev. B |  |

|-------------------------|--|

| Added Table 44 Title 48 |  |

| Changes to Table 201141 |  |

## 3/2016—Rev. 0 to Rev. A

| Changes to Table 18                                      | 30 |

|----------------------------------------------------------|----|

| Deleted Endnote 1, Table 74; Renumbered Sequentially     | 64 |

| Changes to Protection, Integrity Section                 | 78 |

| Added ECC Error Handling Section                         | 81 |

| Added ECC Error During Read Section and ECC Error During |    |

| Execution of Sign Command                                | 82 |

| Register Summary: PLA | 189 |

|-----------------------|-----|

| Register Details: PLA | 189 |

| Changes to Table 104                                         | 86 |

|--------------------------------------------------------------|----|

| Changes to Table 105                                         | 87 |

| Added ECC Enable/Disable, Error Response Register Section    |    |

| and Table 121; Renumbered Sequentially                       | 93 |

| Added Flash 0 ECC Error Address Register Section, Table 122, |    |

| Flash 1 ECC Error Address Register Section, and Table 123    | 94 |

| Change to Table 130                                          | 99 |

#### 5/2015—Revision 0: Initial Version

# USING THE ADuCM310 HARDWARE REFERENCE MANUAL

## NUMBER NOTATIONS

## Table 1.

| Notation | Description                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------|

| Bit N    | Bits are numbered in little endian format, that is, the least significant bit of a number is referred to as Bit 0. |

| V[x:y]   | Bit field representation covering Bit x to Bit y of a value or a field (V).                                        |

| 0xNN     | Hexadecimal (Base 16) numbers are preceded by the prefix 0x.                                                       |

| 0bNN     | Binary (Base 2) numbers are preceded by the prefix 0b.                                                             |

| NN       | Decimal (Base 10) numbers are represented using no additional prefixes or suffixes.                                |

## **REGISTER ACCESS CONVENTIONS**

## Table 2.

| Mode | Description                                                                               |

|------|-------------------------------------------------------------------------------------------|

| RW   | Memory location has read and write access.                                                |

| RC   | Memory location is cleared after reading it.                                              |

| R    | Memory location is read access only. A read always returns 0, unless otherwise specified. |

| W    | Memory location is write access only.                                                     |

MMR bits that are not documented are reserved. Reserved bits must not be changed by the user.

## ACRONYMS AND ABBREVIATIONS

## Table 3.

| Acronym/Abbreviation | Description                          |

|----------------------|--------------------------------------|

| ADC                  | Analog-to-digital converter          |

| DMA                  | Direct memory access                 |

| GPIO                 | General-purpose input and output     |

| LSB                  | Least significant byte/bit           |

| MMR                  | Memory mapped register               |

| MSB                  | Most significant byte/bit            |

| NMI                  | Nonmaskable interrupt                |

| NVIC                 | Nested vectored interrupt controller |

| Rx                   | Receive                              |

| SAR                  | Successive approximation register    |

| SOA                  | Semiconductor optical amplifier      |

| SPI                  | Serial peripheral interface          |

| SWD                  | Sync word detect/serial wire debug   |

| Тх                   | Transmit                             |

| UART                 | Universal asynchronous transmitter   |

| WDT                  | Watchdog timer                       |

| WUT                  | Wake-up timer                        |

## **INTRODUCTION TO THE ADuCM310**

The ADuCM310 is a triple-die stack, system on-chip designed for diagnostic control on tunable laser optical module application. The ADuCM310 features a 16-bit (14-bit no missing codes), multichannel, successive approximation register (SAR) ADC; an ARM Cortex<sup>™</sup>-M3 processor; eight voltage DACs; six current output DACs; and Flash/EE memory packaged in a 6 mm × 6 mm, 112-ball BGA package.

The bottom die in the stack supports the bulk of the low voltage analog circuitry and is largest of the three die. It contains the ADC, VDAC, main IDAC circuits, as well as other analog support circuits like the low drift, precision 2.5 V voltage reference source.

The middle die in the stack supports the bulk of the digital circuitry including the ARM Cortex-M3 processor, the flash and SRAM blocks, and all of the digital communication peripherals. Also provided on this die are the clock sources for the whole chip. A 16 MHz internal oscillator is the source of an internal phase-locked loop (PLL) that outputs an 80 MHz system clock.

The top die, which is the smallest die, is developed on a high voltage process and supports the -5 V and +5 V VDAC outputs. It also implements the SOA IDAC current sink circuit, which allows the external SOA diode to be pulled to a -3.0 V level to implement the fast shutdown of the laser module.

Regarding the individual blocks, the ADC is capable of operating at conversion rates of up to 800 kSPS. There are 10 external inputs to the ADC, and these can be configured as single-ended or differential. Several internal channels are available, including supply monitor channels, an on-chip temperature sensor, and internal voltage reference monitor.

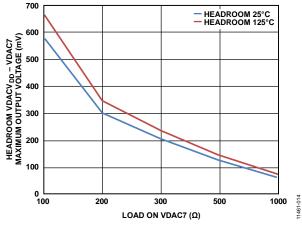

The voltage DACs are 12-bit string DACs with output buffers capable of sourcing between 10 mA and 50 mA, and all are capable of driving 10 nF capacitive loads.

The low drift current DACs have 14-bit resolution and have varied full-scale output ranges from 0 mA to 20 mA to 0 mA to 250 mA on the SOA IDAC. The SOA IDAC also comes with a 0 mA to -60 mA current sink capability.

A precision 2.5 V on-chip reference source is also provided. This reference is used by the internal ADC, IDACs, and VDAC circuits, ensuring low drift performance for all of these peripherals. Also provided are two buffered reference outputs capable of sourcing up to 1.2 mA. These can be used externally to the chip.

The ADuCM310 integrates an 80 MHz ARM Cortex-M3 processor, which is a 32-bit RISC machine, offering up to 100 DMIPS peak performance. The ARM Cortex-M3 processor also has a flexible 14-channel DMA controller supporting communication peripherals SPI, UART, and I<sup>2</sup>C. There are 256 kB of nonvolatile Flash/EE memory and 32 kB of SRAM integrated on-chip.

A 16 MHz on-chip oscillator generates the 80 MHz system clock. This clock can be internally divided for the processor to operate at a lower frequency, thus saving power. A low power, internal, 32 kHz oscillator is available and can clock the timers. There are three general-purpose timers, a wake-up timer, and a system watchdog timer.

A range of communication peripherals can be configured as required in a specific application. These peripherals include UART, two I<sup>2</sup>Cs, two SPI serial input/output communication controllers, GPIO ports, and PWM.

On-chip factory firmware supports in-circuit serial download via the UART, while nonintrusive emulation and program download is also supported via the serial wire interface. These features are incorporated into a low cost development system supporting this precision analog microcontroller family.

The ADuCM310 operates from 2.9 V to 3.6 V and is specified over a temperature range of -10°C to +85°C.

## MAIN FEATURES OF THE ADuCM310

## ADC

- Multichannel, 14-bit, 800 kSPS SAR ADC

- 14-bit no missing codes

- Low drift, on-chip voltage reference

## DACs

- Eight voltage output DACs

- VDACs are 12-bit monotonic

- Six current output DACs

- One of these can source or sink current

- Current DACs when used as current sources are 14-bit monotonic

- Low drift, on-chip 2.5 V voltage reference source

- Two buffered reference outputs

## Communication

- UART

- Industry standard, 16450 UART peripheral

- Support for DMA

- Two I<sup>2</sup>Cs

- 2-byte transmit and receive FIFOs for the master and slave

- Support for DMA

- Automatic clock stretching option

- Two SPIs

- Master or slave mode with separate 4-byte Rx and Tx FIFOs

- Rx and Tx DMA channels

- 8-channel PWM

- Multiple GPIO pins

### Processing

- ARM Cortex-M3 processor operating from an internal 80 MHz system clock

- 256 kB Flash/EE memory, 32 kB SRAM

- In-circuit download and debug via serial wire

- On-chip UART download capability

## **On-Chip Peripherals**

- Three general-purpose timers

- Wake-up timer

- Watchdog timer

- 32-element programmable logic array (PLA)

### Packages and Temperature Range

• 6 mm × 6 mm, 112-ball BGA package: -10°C to +85°C

### Tools

- Low cost development system

- Third-party compiler and emulator tool support

## Applications

• Tunable laser modules

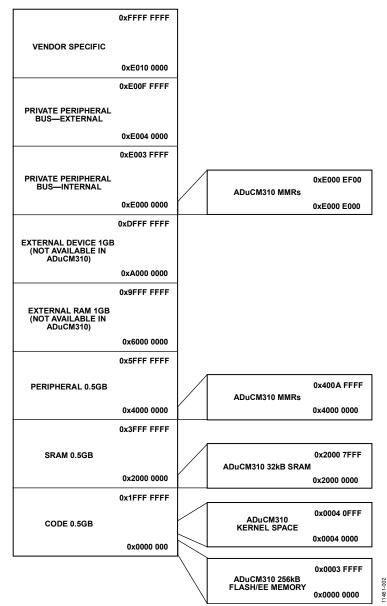

## MEMORY ORGANIZATION

The ADuCM310 memory organization is described in this section.

### Features

- Cortex-M3 memory system features

- Predefined memory map

- Support for bit-band operation for atomic operations

- Unaligned data access

- ADuCM310 on-chip peripherals are accessed via memory mapped registers, situated in the bit band region.

- User memory sizes options:

- 32 kB SRAM

- 256 kB Flash/EE memory

There is an on-chip kernel for manufacturer data and in-circuit download.

Figure 2. Cortex-M3 Memory Map Diagram

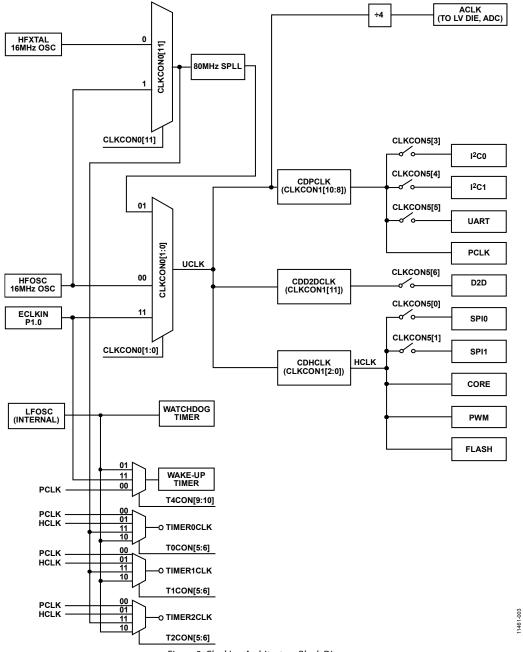

# **CLOCKING ARCHITECTURE**

## **CLOCKING ARCHITECTURE FEATURES**

The ADuCM310 integrates two on-chip oscillators and circuitry for an external crystal and external clock source:

- LFOSC is a 32 kHz, low power internal oscillator that is used in low power modes.

- HFOSC is a 16 MHz internal oscillator that is used in active mode. This is the default input to the PLL.

- HFXTAL is a 16 MHz external crystal oscillator.

- External clock input (ECLKIN) is available via the GPIO pin.

## **CLOCKING ARCHITECTURE BLOCK DIAGRAM**

Figure 3. Clocking Architecture Block Diagram

## **CLOCKING ARCHITECTURE OVERVIEW**

The system clock, UCLK can be selected from an 80 MHz PLL output (default). An external clock on P1.0 can also be used for test purposes.

Internally, the system clock is divided into separate clocks:

- UCLK system clock

- System bus clock (HCLK) for the flash, SRAM, and DMA

- ACLK for the analog section of the chip; this is based on the 20 MHz peripheral bus clock (PCLK) output and goes to the low voltage analog die

- PCLK for most peripherals

All ADC performance details are based on a 20 MHz ACLK (CLKCON1[10:8] = 010b). Performance at other clock speeds is not guaranteed; therefore, do not change CLKCON1[10:8] when the ADC is being used.

## **CLOCKING ARCHITECTURE OPERATION**

At power-up, the processor executes at 80 MHz, sourced from the 80 MHz PLL output. The clock source for the 80 MHz PLL is the internal 16 MHz oscillator by default. User code can select the clock source for the system clock and can divide the clock by a factor of 1 to 128, where the clock divider bits are controlled by CLKCON1[2:0]. This allows slower code execution and reduced power consumption.

Note that P1.0 must be configured first as a clock input before the clock source is switched in the clock control register.

If the clock source for the 80 MHz SPLL is required to change from the internal 16 MHz oscillator to the external HFXTAL, observe the following procedure:

- 1. Check that HFXTAL is stable by reading CLKSTAT0[14:12].

- 2. Change the system clock to the internal 16 MHz oscillator using CLKCON0[1:0].

- 3. Switch the input to the SPLL using CLKCON0[11].

- 4. Wait until the SPLL has locked by monitoring CLKSTAT0[2:0].

- 5. Change the system clock back to the SPLL clock.

## **REGISTER SUMMARY: CLOCK ARCHITECTURE**

#### **Table 4. Clocking Register Summary**

| Address    | Name     | Description                           | Reset  | Access |  |

|------------|----------|---------------------------------------|--------|--------|--|

| 0x40028000 | CLKCON0  | Miscellaneous clock settings register | 0x0041 | RW     |  |

| 0x40028004 | CLKCON1  | Clock dividers register               | 0x0200 | RW     |  |

| 0x40028014 | CLKCON5  | User clock gating control register    | 0x0040 | RW     |  |

| 0x40028018 | CLKSTAT0 | Clocking status register              | 0x0003 | RW     |  |

## **REGISTER DETAILS: CLOCK ARCHITECTURE**

### Miscellaneous Clock Settings Register

Address: 0x40028000, Reset: 0x0041, Name: CLKCON0

### Table 5. Bit Descriptions for CLKCON0

| Bits | Bit Name | Description                                                                   | Reset | Access |

|------|----------|-------------------------------------------------------------------------------|-------|--------|

| 15   | HFXTALIE | High frequency crystal interrupt enable.                                      | 0x0   | RW     |

|      |          | 0: an interrupt to the core is not generated on a HFXTAL OK or HFXTAL not OK. |       |        |

|      |          | 1: an interrupt to the core is generated on a HFXTAL OK or HFXTAL not OK.     |       |        |

| 14   | UPLLIE   | UPLL interrupt enable.                                                        | 0x0   | RW     |

|      |          | 0: UPLL interrupt is not generated.                                           |       |        |

|      |          | 1: UPLL interrupt is generated.                                               |       |        |

| 13   | SPLLIE   | SPLL interrupt enable.                                                        | 0x0   | RW     |

|      |          | 0: system PLL interrupt is not generated.                                     |       |        |

|      |          | 1: system PLL interrupt is generated.                                         |       |        |

| 12   | RESERVED | Reserved.                                                                     | 0x0   | R      |

| 11   | PLLMUX   | PLL source selection.                                                         | 0x0   | RW     |

|      |          | 0: internal oscillator is selected (HFOSC).                                   |       |        |

|      |          | 1: external oscillator is selected (HFXTAL).                                  |       |        |

# ADuCM310 Hardware Reference Manual

| Bits   | Bit Name | Description                                     | Reset | Access |

|--------|----------|-------------------------------------------------|-------|--------|

| [10:8] | RESERVED | Reserved.                                       | 0x0   | RW     |

| [7:4]  | CLKOUT   | GPIO clock out selection.                       | 0x4   | RW     |

|        |          | 0000: UCLK.                                     |       |        |

|        |          | 0001: LFOSC (32 kHz).                           |       |        |

|        |          | 0010: HFOSC (16 MHz).                           |       |        |

|        |          | 0100: core clock (default).                     |       |        |

|        |          | 0101: PCLK.                                     |       |        |

|        |          | 1011: General-Purpose Timer 0 clock.            |       |        |

|        |          | 1100: wake-up timer clock.                      |       |        |

|        |          | 1110: HFXTAL.                                   |       |        |

|        |          | All other combinations are reserved.            |       |        |

| [3:2]  | RESERVED | Reserved.                                       | 0x0   | R      |

| [1:0]  | CLKMUX   | Clock selection.                                | 0x1   | RW     |

|        |          | 00: high frequency internal oscillator (HFOSC). |       |        |

|        |          | 01: SPLL is selected (80 MHz).                  |       |        |

|        |          | 10: UPLL is selected (60 MHz).                  |       |        |

|        |          | 11: external GPIO port is selected (ECLKIN).    |       |        |

UG-549

## **Clock Dividers Register**

#### Address: 0x40028004, Reset: 0x0200, Name: CLKCON1

#### Table 6. Bit Descriptions for CLKCON1

| Bits    | Bit Name | Description                                                                                                                                                                                 | Reset | Access |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:11] | RESERVED | Reserved                                                                                                                                                                                    | 0x0   | R      |

| [10:8]  | CDPCLK   | PCLK divide bits.                                                                                                                                                                           | 0x2   | RW     |

|         |          | 000: Reserved.                                                                                                                                                                              |       |        |

|         |          | 001: Reserved.                                                                                                                                                                              |       |        |

|         |          | 010: DIV4. Divide by 4 (PCLK is a quarter the frequency of root clock, 20 MHz).<br>All ADC specifications are based on this setting. Using any other setting may<br>affect ADC performance. |       |        |

|         |          | 011: DIV8. Divide by 8.                                                                                                                                                                     |       |        |

|         |          | 100: DIV16. Divide by 16.                                                                                                                                                                   |       |        |

|         |          | 101: DIV32. Divide by 32.                                                                                                                                                                   |       |        |

|         |          | 110: DIV64. Divide by 64.                                                                                                                                                                   |       |        |

|         |          | 111: DIV128. Divide by 128.                                                                                                                                                                 |       |        |

| [7:3]   | RESERVED | Reserved. Always returns 0 when read.                                                                                                                                                       | 0x0   | R      |

| [2:0]   | CDHCLK   | HCLK divide bits.                                                                                                                                                                           | 0x0   | RW     |

|         |          | 000: DIV1. Divide by 1 (HCLK is equal to root clock).                                                                                                                                       |       |        |

|         |          | 001: DIV2. Divide by 2 (HCLK is half the frequency of root clock).                                                                                                                          |       |        |

|         |          | 010: DIV4. Divide by 4 (HCLK is quarter the frequency of root clock).                                                                                                                       |       |        |

|         |          | 011: DIV8. Divide by 8.                                                                                                                                                                     |       |        |

|         |          | 100: DIV16. Divide by 16.                                                                                                                                                                   |       |        |

|         |          | 101: DIV32. Divide by 32.                                                                                                                                                                   |       |        |

|         |          | 110: DIV64. Divide by 64.                                                                                                                                                                   |       |        |

|         |          | 111: DIV128. Divide by 128.                                                                                                                                                                 |       |        |

### User Clock Gating Control Register

## Address: 0x40028014, Reset: 0x0040, Name: CLKCON5

The user clock gating control register (CLKCON5) controls the gates of the peripheral UCLKs.

#### Table 7. Bit Descriptions for CLKCON5

| Bits          | Bit Name    | Description                                                                                                                                                                                                                                                                       | Reset | Access |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:7]        | RESERVED    | Reserved. Always returns 0 when read.                                                                                                                                                                                                                                             | 0x0   | R      |

| 6             | RESERVED    | Reserved. Always set to 1.                                                                                                                                                                                                                                                        | 0x1   | RW     |

| 5 UCLKUARTOFF |             | UART clock user control. This bit disables the UCLK UART clock. It controls the gate on UCLK UART in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3, the UCLK_UART is always off and this bit has no effect.                                                     | 0x0   | RW     |

|               |             | 0: die-to-die clock on permanently.                                                                                                                                                                                                                                               |       |        |

|               |             | 1: die-to-die clock enabled only during die-to-die transfers (recommended).                                                                                                                                                                                                       |       |        |

| 4             | UCLKI2C1OFF | I <sup>2</sup> C1 clock user control. This bit disables the UCLK I <sup>2</sup> C1 clock. It controls the gate on UCLK I <sup>2</sup> C1 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3, the I <sup>2</sup> C1 UCLK is always off and this bit has no effect. | 0x0   | RW     |

|               |             | 0: clock on.                                                                                                                                                                                                                                                                      |       |        |

|               |             | 1: clock off.                                                                                                                                                                                                                                                                     |       |        |

| 3 UCLKI2C0OFF | UCLKI2C0OFF | I <sup>2</sup> C0 clock user control. This bit disables the UCLK I <sup>2</sup> C0 clock. It controls the gate on UCLK I <sup>2</sup> C0 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3, the UCLK I <sup>2</sup> C0 is always off and this bit has no effect. | 0x0   | RW     |

|               |             | 0: clock on.                                                                                                                                                                                                                                                                      |       |        |

|               |             | 1: clock off.                                                                                                                                                                                                                                                                     |       |        |

| 2             | RESERVED    | Reserved.                                                                                                                                                                                                                                                                         | 0x0   | R      |

| 1             | UCLKSPI1OFF | SPI1 clock user control. This bit disables the UCLK SPI1 clock. It controls the gate on UCLK SPI1 in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3, the UCLK SPI1 is always off and this bit has no effect.                                                     | 0x0   | RW     |

|               |             | 0: clock on.                                                                                                                                                                                                                                                                      |       |        |

|               |             | 1: clock off.                                                                                                                                                                                                                                                                     |       |        |

| 0             | UCLKSPI0OFF | SPIO clock user control. This bit disables the UCLK SPIO clock. It controls the gate on UCLK SPIO in Power Mode 0 and Power Mode 1. In Power Mode 2 and Power Mode 3, the UCLK SPIO is always off and this bit has no effect.                                                     | 0x0   | RW     |

|               |             | 0: clock on.                                                                                                                                                                                                                                                                      |       |        |

|               |             | 1: clock off.                                                                                                                                                                                                                                                                     |       |        |

## **Clocking Status Register**

## Address: 0x40028018, Reset: 0x0003, Name: CLKSTAT0

The clocking status register monitors PLL and oscillator status.

| Bits        | Bit Name     | Description                                                                                                                                                                                                                                                                                                    | Reset | Access |

|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| 15          | RESERVED     | Reserved. Always returns 0 when read.                                                                                                                                                                                                                                                                          | 0x0   | R      |

| 14          | HFXTALNOK    | HF crystal not stable. This bit is sticky. It interrupts the core when interrupts are enabled. Write a 1 to this location to clear it.                                                                                                                                                                         | 0x0   | RW     |

|             |              | 0: HF crystal stable signal has not been deasserted.                                                                                                                                                                                                                                                           |       |        |

|             |              | 1: HF crystal stable signal has been deasserted.                                                                                                                                                                                                                                                               |       |        |

| 13          | HFXTALOK     | HF crystal stable. This bit is sticky. It interrupts the core when interrupts are enabled. Write a 1 to this location to clear it.                                                                                                                                                                             | 0x0   | RW     |

|             |              | 0: HF crystal stable signal has not been asserted.                                                                                                                                                                                                                                                             |       |        |

|             |              | 1: HF crystal stable signal has been asserted.                                                                                                                                                                                                                                                                 |       |        |

| 12          | HFXTALSTATUS | HF crystal status.                                                                                                                                                                                                                                                                                             | 0x0   | R      |

|             |              | 0: HF crystal is not stable or not enabled.                                                                                                                                                                                                                                                                    |       |        |

|             |              | 1: HF crystal is stable.                                                                                                                                                                                                                                                                                       |       |        |

| [11:3]      | RESERVED     | Reserved.                                                                                                                                                                                                                                                                                                      | 0x0   | R      |

| 2 SPLLUNLOO | SPLLUNLOCK   | System PLL unlock. This bit is sticky. SPLLUNLOCK is set when the PLL loses its lock. SPLLUNLOCK is used as the interrupt source to signal the core that a lock was lost. Writing a 1 to this bit clears it. SPLLUNLOCK does not set again unless the system PLL gains a lock and subsequently loses it again. | 0x0   | RW     |

|             |              | 0: no loss of PLL lock was detected.                                                                                                                                                                                                                                                                           |       |        |

|             |              | 1: PLL loss of lock was detected.                                                                                                                                                                                                                                                                              |       |        |

| 1           | SPLLLOCK     | System PLL lock. This bit is sticky. SPLLLOCK is set when the PLL locks.<br>SPLLLOCK is used as the interrupt source to signal the core that a lock was<br>detected. Writing a 1 to this bit clears it. SPLLLOCK does not set again<br>unless the system PLL loses lock and subsequently locks again.          | 0x1   | RW     |

|             |              | 0: no PLL lock event was detected.                                                                                                                                                                                                                                                                             |       |        |

|             |              | 1: PLL lock event was detected.                                                                                                                                                                                                                                                                                |       |        |

| 0           | SPLLSTATUS   | System PLL status. Indicates the current status of the PLL. Initially, the system PLL is unlocked. After a stabilization period, the PLL locks and is ready for use as the system clock source. This is a read only bit. A write has no effect.                                                                | 0x1   | R      |

|             |              | 0: the PLL is not locked or not properly configured. The PLL is not ready for use as the system clock source.                                                                                                                                                                                                  |       |        |

|             |              | 1: the PLL is locked and is ready for use as the system clock source.                                                                                                                                                                                                                                          |       |        |

## POWER MANAGEMENT UNIT

## **POWER MANAGEMENT UNIT FEATURES**

The power management unit (PMU) controls the different power modes of the ADuCM310.

The following four power modes are available:

- Active

- CORE\_SLEEP

- SYS\_SLEEP

- Hibernate

## POWER MANAGEMENT UNIT OVERVIEW

The Cortex-M3 sleep modes are linked to the PMU modes and are described in this section. The PMU is in the always-on section. Each mode provides a power reduction benefit with a corresponding reduction in functionality.

## **POWER MANAGEMENT UNIT OPERATION**

The debug tools can prevent the Cortex-M3 from fully entering its power saving modes by setting bits in the debug logic. Only a power-on reset resets the debug logic. Therefore, the device must be power cycled after using serial wire debug with application code containing the WFI instruction.

### Power Mode: Active Mode, Mode 0

The system is fully active. Memories and all user enabled peripherals are clocked, and the Cortex-M3 processor is executing instructions. Note that the Cortex-M3 processor manages the internal clocks and can be in a partial clock gated state. This clock gating affects only the internal Cortex-M3 processing core. Automatic clock gating is used on all blocks. User code can use a WFI command to put the Cortex-M3 processor into sleep mode; it is independent of the power mode settings of the PMU.

When the ADuCM310 wakes up from any of the low power modes, the device returns to Mode 0.

### Power Mode: CORE\_SLEEP Mode, Mode 1

In CORE\_SLEEP mode, the system gates the clock to the Cortex-M3 core after the Cortex-M3 has entered sleep mode. The rest of the system remains active. No instructions can be executed; however, DMA transfers can continue to occur between peripherals and memories. The Cortex-M3 processor FCLK is active, and the device wakes up using the NVIC.

### Power Mode: SYS\_SLEEP Mode, Mode 2

In SYS\_SLEEP mode, the system gates HCLK and PCLK after the Cortex-M3 has entered sleep mode. The gating of these clocks stops all AHB attached masters/slaves and all peripherals attached to APB. Peripheral clocks are all off, and they are no longer user programmable. The NVIC clock (FCLK) remains active, and the NVIC processes wake-up events.

### Power Mode: Hibernate Mode, Mode 3

In hibernate mode, the system disables power to all combinational logic and places sequential logic in retain mode. Because FCLK is stopped, the number of sources capable of waking up the system is restricted. The sources listed in Table 64 are the only sources able to wake up the system.

Enter Power Mode 1 to Power Mode 3 when the processor is not in an interrupt handler. If Power Mode 1 to Power Mode 3 is entered when the processor is in an interrupt handler, the power-down mode can be exited only by a reset or a higher priority interrupt source.

## **CODE EXAMPLES**

## Code Example to Enter Power Saving Modes

| SCB -> SCR = 0x04;                          | // sleepdeep mode |

|---------------------------------------------|-------------------|

| <pre>pADI_PWRCTL-&gt;PWRKEY = 0x4859;</pre> | // keyl           |

| <pre>pADI_PWRCTL-&gt;PWRKEY = 0xF27B;</pre> | // key2           |

| <pre>pADI_PWRCTL-&gt;PWRMOD = 0x3;</pre>    | // Hibernate      |

| DSB();                                      |                   |

| nop();                                      |                   |

| WFI();                                      |                   |

| nop();                                      |                   |

|                                             |                   |

| Code Example to Achieve Further Pow         | ver Savings       |

| pADI_ADC->ADCCON = 0;                       | // Power off      |

| <pre>pADI_IDAC0-&gt;IDACCON = 0x1;</pre>    | // Turn off       |

|                                             |                   |

| <pre>pADI_ADC-&gt;ADCCON = 0;</pre>               | // Power off the ADC              |

|---------------------------------------------------|-----------------------------------|

| <pre>pADI_IDAC0-&gt;IDACCON = 0x1;</pre>          | // Turn off IDAC0                 |

| <pre>pADI_IDAC1-&gt;IDACCON = 0x1;</pre>          | // Turn off IDAC1                 |

| <pre>pADI_IDAC2-&gt;IDACCON = 0x1;</pre>          | // Turn off IDAC2                 |

| <pre>pADI_IDAC3-&gt;IDACCON = 0x1;</pre>          | // Turn off IDAC3                 |

| <pre>pADI_VDAC0-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC0                 |

| <pre>pADI_VDAC1-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC1                 |

| <pre>pADI_VDAC2-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC2                 |

| <pre>pADI_VDAC3-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC3                 |

| <pre>pADI_VDAC4-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC4                 |

| <pre>pADI_VDAC5-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC5                 |

| <pre>pADI_VDAC6-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC6                 |

| <pre>pADI_VDAC7-&gt;DACCON = 0x100;</pre>         | // Turn off VDAC7                 |

| <pre>pADI_CLKCTL-&gt;CLKCON0 &amp;= 0xFFFC;</pre> | // Switch to 16MHz clock          |

| <pre>pADI_CLKCTL-&gt;CLKCON1 = 0x505;</pre>       | // Slow down system clocks        |

| <pre>pADI_CLKCTL-&gt;CLKCON5 = 0x7B;</pre>        | // Turn off clocks to peripherals |

|                                                   |                                   |

### **REGISTER SUMMARY: POWER MANAGEMENT UNIT**

| Table 9. Power Ma | Table 9. Power Management Register Summary |                           |        |        |  |  |

|-------------------|--------------------------------------------|---------------------------|--------|--------|--|--|

| Address           | Name                                       | Description               | Reset  | Access |  |  |

| 0x40002400        | PWRMOD                                     | Power modes               | 0x0000 | RW     |  |  |

| 0x40002404        | PWRKEY                                     | Key protection for PWRMOD | 0x0000 | RW     |  |  |

## Table 9. Power Management Register Summary

### **REGISTER DETAILS: POWER MANAGEMENT UNIT**

#### Power Modes Register

#### Address: 0x40002400, Reset: 0x0000, Name: PWRMOD

#### Table 10. Bit Descriptions for PWRMOD

| Bits   | Bit Name | Description                                                                                                                                                                                                                                                                                                                                                               | Reset | Access |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [14:2] | RESERVED | Reserved. These bits must be written 0 by user code.                                                                                                                                                                                                                                                                                                                      | 0x0   | R      |

| [1:0]  | PWRMOD   | Power modes control bits. When read, these bits contain the last power<br>mode value entered by user code. Note that, to place the Cortex in<br>SLEEPDEEP mode for hibernate, the Cortex-M3 system control register<br>(Register 0xE000ED10) must be configured to 0x4 or 0x06.<br>00: active mode.<br>01: CORE_SLEEP mode.<br>10: SYS_SLEEP mode.<br>11: hibernate mode. | 0x0   | RW     |

## Key Protection for PWRMOD Register

#### Address: 0x40002404, Reset: 0x0000, Name: PWRKEY

#### Table 11. Bit Descriptions for PWRKEY

| Bits   | Bit Name | Description                                                                                                                                                                                                                                                                                                                         | Reset | Access |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| [15:0] | PWRKEY   | Power control key register. The PWRMOD register is key-protected. Two<br>writes to the key are necessary to change the value in the PWRMOD register:<br>first 0x4859, then 0xF27B. The PWRMOD register must then be written. A<br>write to any other register before writing to PWRMOD returns the protection<br>to the lock state. | 0x0   | RW     |

# ARM CORTEX-M3 PROCESSOR

## ARM CORTEX-M3 PROCESSOR FEATURES

## High Performance

- 1.25 DMIPS/MHz.

- Many instructions, including multiply, are single cycle.

- Separate data and instruction buses allow simultaneous data and instruction accesses to be performed.

- Optimized for single-cycle flash usage.

### Low Power

- Low standby current.

- Core implemented using advanced clock gating so that only the actively used logic consumes dynamic power.

- Power-saving mode support (sleep and deep sleep modes). The design has separate clocks to allow unused parts of the processor to be stopped.

## Advanced Interrupt Handling

- The nested vectored interrupt controller (NVIC) supports up to 240 interrupts, of which the ADuCM310 supports 50. The vectored interrupt feature greatly reduces interrupt latency because there is no need for software to determine which interrupt handler to serve. In addition, there is no need to have software to set up nested interrupt support.

- The ARM Cortex-M3 processor automatically pushes registers onto the stack at the entry interrupt and retrieves them at the exit interrupt. This reduces interrupt handling latency and allows interrupt handlers to be normal C functions.

- Dynamic priority control for each interrupt.

- Latency reduction using late arrival interrupt acceptance and tail-chain interrupt entry.

- Immediate execution of a nonmaskable interrupt request for safety-critical applications.

## System Features

- Support for bit-band operation and unaligned data access.

- Advanced fault handling features include various exception types and fault status registers.

### **Debug Support**

- Serial wire debug interfaces (SW-DP).

- Flash patch and breakpoint (FPB) unit for implementing breakpoints. Limited to two hardware breakpoints.

- Data watchpoint and trigger (DWT) unit for implementing watchpoints trigger resources and system profiling. Limited to one hardware watchpoint. The DWT does not support data matching for watchpoint generation because it only has one comparator.

## **ARM CORTEX-M3 PROCESSOR OVERVIEW**

The ADuCM310 contains an embedded ARM Cortex-M3 processor, Revision r2p1. The ARM Cortex-M3 processor provides a high performance, low-cost platform that meets the system requirements of minimal memory implementation, reduced pin count, and low power consumption while delivering outstanding computational performance and exceptional system response to interrupts.

### **ARM CORTEX-M3 PROCESSOR OPERATION**

Several ARM Cortex-M3 processor components are flexible in their implementation. This section details the actual implementation of these components in the ADuCM310.

### Serial Wire Debug (SW/JTAG-DP)

The ADuCM310 only supports the serial wire interface via the SWCLK and SWDIO pins. It does not support the 5-wire JTAG interface.

#### **ROM Table**

The ADuCM310 implements the default ROM table.

### Nested Vectored Interrupt Controller Interrupts (NVIC)

The ARM Cortex-M3 processor includes an NVIC, which offers several features:

- Nested interrupt support

- Vectored interrupt support

- Dynamic priority changes support

- Interrupt masking

In addition, the NVIC has a nonmaskable interrupt (NMI) input.

The NVIC is implemented on the ADuCM310, and more details are available in the System Exceptions and Peripheral Interrupts section.

### Wake-Up Interrupt Controller (WIC)

The ADuCM310 has a modified WIC, which provides the lowest possible power-down current. More details are available in the Power Management Unit section. It is not recommended to enter a power saving mode while servicing an interrupt. However, if the device does enter a power saving mode while servicing an interrupt, it can be woken up only by a higher priority interrupt source.

### μDMA

The ADuCM310 implements the ARM µDMA. More details are available in the DMA Controller section.

## **ARM CORTEX-M3 PROCESSOR RELATED DOCUMENTS**

- Cortex-M3 Revision r2p1 Technical Reference Manual (DDI0337)

- ARM Processor Cortex-M3 (AT420) and Cortex-M3 with ETM (AT425): Errata Notice

- ARMv7-M Architecture Reference Manual (DDI0403)

- ARMv7-M Architecture Reference Manual Errata Markup

- ARM Debug Interface v5 Architecture Specification (IHI 0031)

- PrimeCell<sup>®</sup> µDMA Controller (PL230) Technical Reference Manual Revision r0p0 (DDI0417)

The ADuCM310 incorporates a fast, multichannel, 16-bit ADC. The ADC is specified to be 14-bit no missing codes.

The flexible input multiplexer supports 10 external inputs and 14 internal channels. The internal channels include the following:

- Temperature sensor channel

- Internal 2.505 V reference

- External reference

- BUF\_BREF2.5A and BUF\_BREF2.5B

- Six IDAC channels. These are the voltage at each of the IDAC output pins

- PVDD\_IDAC2 supply voltage

- IOV<sub>DD</sub>/2 supply voltage.

- AV<sub>DD</sub>/2 supply voltage

The input buffer can be selected for any channel to allow very low input current/input leakage specifications on these input channels. It is recommended to use the input buffer for the  $AV_{DD}/2$ ,  $IOV_{DD}/2$ , and temperature sensor channels.

The ADC features a high precision, low drift internal 2.505 V reference source.

An external reference can also be connected to the ADC\_CAPP and ADC\_CAPN pins.

The programmable ADC update rate is from 19.55 kSPS to 800 kSPS.

There is an internal digital comparator for the AIN4 channel. An interrupt can be generated if the digital comparator detects an ADC result above/below a user defined threshold.

Each channel has its own distinct data register for its conversion result. For example, when AIN0 is selected, the result appears in ADCDAT0; if AIN7 is selected, the result appears in ADCDAT7. For a differential measurement, the result always appears in the data register of the positive channel.

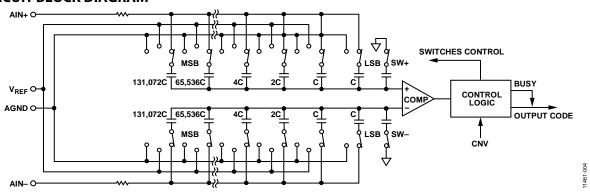

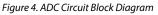

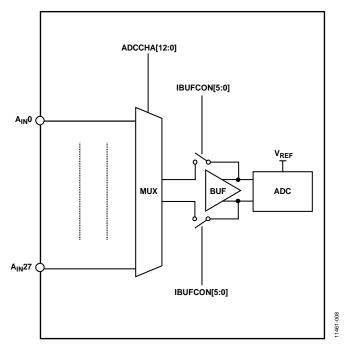

## ADC CIRCUIT BLOCK DIAGRAM

## ADC CIRCUIT OVERVIEW

The ADuCM310 incorporates a fast, multichannel, 16-bit ADC. The ADC is specified to be 14-bit no missing codes. The ADC can operate from a 2.9 V to 3.6 V supply and is capable of providing a throughput of up to 800 kSPS. This ADC block provides the user with a multichannel multiplexer, input buffer for high impedance input channels, on-chip reference, and SAR ADC.

The SAR ADC circuit is implemented on the low voltage analog die. The ARM Cortex-M3 processor interfaces to the ADC via an internal parallel die-to-die interface.

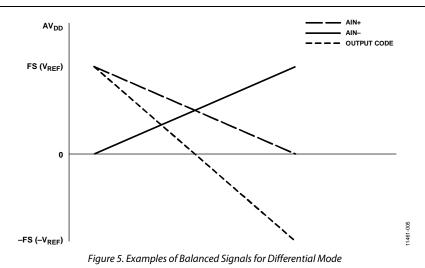

Depending on the input signal configuration, the ADC can operate in one of the following two modes:

- Differential mode, to measure the difference between two signals.

- Single-ended mode, to measure any signal relative to AGND.

The converter accepts an analog input range of 0 to  $V_{REF}$  when operating in single-ended mode. In fully differential mode, the measurement range is  $\pm V_{REF}$  while each signal must be between the range of AGND to AV<sub>DD</sub>.

A high precision, low drift, factory-calibrated 2.505 V reference is provided on-chip. An external reference can also be connected to the ADC\_CAPP and ADC\_CAPN pins.

Single or continuous conversion modes can be initiated in software. An external pin (alternate function of P2.4) can also generate a repetitive trigger for ADC conversions.

## ADC CIRCUIT OPERATION

The SAR ADC is based on a charge redistribution DAC. The capacitive DAC consists of two identical arrays of 18 binary weighted capacitors that are connected to the two inputs of the comparator.

The ADC converts the voltage applied to the positive analog inputs (AIN+) and negative analog inputs (AIN-) in the following three steps:

- 1. Precharge Phase: during this phase, the precharge buffers connect the inputs to the capacitor arrays. This charges the capacitors quickly with minimal loading of the external input source.

- 2. Acquisition Phase: during the acquisition phase, the capacitor arrays are connected directly to the inputs to fully charge the capacitor arrays and eliminate any precharge buffer errors. The timing for the acquisition phase is set by ADCCNVC[25:16]; set this value to 1 µs for ADC update rates  $\leq$ 500 kSPS (for example, ADCCNVC = 0x140028 for 500 kSPS). If the input buffer is not used when measuring AV<sub>DD</sub>/2, IOV<sub>DD</sub>/2, or temperature sensor channels, set this value to 1.5 µs.

- 3. Conversion Phase: at the end of the acquisition phase, the internal CNV signal goes high and initiates the conversion phase. The conversion begins with the SW+ and SW- switches being opened. This disconnects the two capacitor arrays from the analog inputs and connects the analog inputs to AGND ( $-V_{REF}$ ). The conversion is completed by normal successive approximation.

The ADC block operates from an internally generated 20 MHz clock.

The ADC conversion rate is set by ADCCNVC[9:0].

## ADC TRANSFER FUNCTION

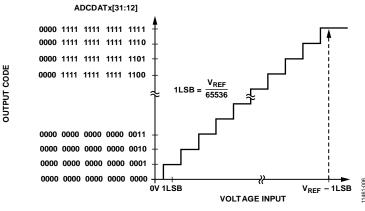

### Single-Ended Mode

In single-ended mode, the input range is 0 to  $V_{REF}$ . The output coding is straight binary with 1 LSB = FS/65,536 or  $V_{REF}/65,536 = 2.5 \text{ V}/65,536 = 38.14 \mu\text{V}$ .

The data values in ADCDATx are aligned such that the MSB is in ADCDATx[27] and, therefore, the LSB is in ADCDATx[12].

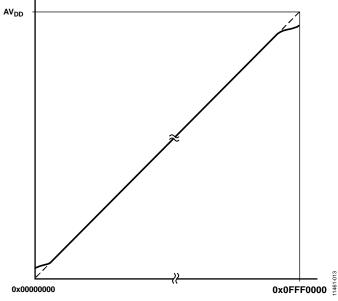

The ideal code transitions occur midway between successive integer LSB values (that is, 1/2 LSB, 3/2 LSB, 5/2 LSB, ..., FS – 3/2 LSBs). The ideal input/output transfer characteristic is shown in Figure 6.

Figure 6. ADC Transfer Function: Single-Ended Mode

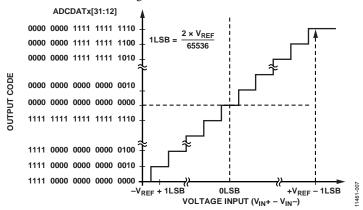

#### **Differential Mode**

The amplitude of the differential signal is the difference between the signals applied to the positive and negative AINx pins (that is, AIN+ – AIN–). The maximum amplitude of the differential signal is, therefore,  $-V_{REF}$  to  $+V_{REF}$  p-p (2 ×  $V_{REF}$ ). This is regardless of the common mode (CM). The common mode is the average of the two signals (AIN+ + AIN–)/2, and is, therefore, the voltage that the two inputs are centered on. This results in the span of each input being CM ±  $V_{REF}/2$ . This voltage must be set up externally, and its range varies with  $V_{REF}$ . The voltage at the positive and negative AINx pins must be within the allowed input voltage range.

The output coding is twos complement in fully differential mode, with

$1 \text{ LSB} = 2 \text{ V}_{\text{REF}}/65,536$

Or

$2 \times 2.5 \text{ V}/65,536 = 76.29 \,\mu\text{V}$

where  $V_{REF} = 2.5$  V.

The ideal input/output transfer characteristic is shown in Figure 7.

Figure 7. ADC Transfer Function: Differential Mode

UG-549

2.

## ADC TYPICAL SETUP SEQUENCE

After being configured via the ADC control and channel selection registers, the ADC converts the analog input and provides a 16-bit result in the ADC data registers.

The following is an example sequence to set up the ADC and generate a single conversion on AIN0 using a single-ended measurement:

1. Configure the device as follows:

```

ADCCON = 0x280;// Power up the ADC, enable reference buffer, idle mode.ADCCHA = 0x1100;// Select AIN0 as the positive ADC input (AIN+) and<br/>VREFN as the negative ADC input (AIN-)ADCCNVC = 0x1400C8;// Select 100 kSPS ADC update rate, 500 ns acquisition<br/>time.ADCCON |=0x2;// Enable single conversionWait for low voltage die interrupt.

```

lADCResult = ADCDAT0; // read the ADC result

Note that if the ADC is set from continuous conversion mode to idle mode after a full ADC sequence is completed, ADCSEQ[31] must be set to 1 before starting another sequence and reconfiguring the ADC back to continuous conversion mode. This ensures that the sequencer restarts with the first selected channel in ADCSEQ.

## **ADC INPUT BUFFER**

Figure 8. ADC Input Buffer

An optional input buffer can be enabled for any ADC input channel on the ADuCM310.

The IBUFCON control register controls the input buffer switches as follows:

- IBUFCON[1:0] controls the bypass switches on the ADC input buffer. If the input buffer is required on either the positive or negative input, the bypass switch must be turned off.

- IBUFCON[3:2] power up or power down the ADC input buffer.

The input buffer has two options to eliminate the input buffer offset error.

### Chop Mode

This mode requires IBUFCON[10] = [1]b. Set IBUFCON[5] = 1 to enable chopping of the positive input buffer.

IBUFCON[4] may be optionally set to enable chopping of the N-side buffer, especially for differential measurements. For single-ended input measurements where the ADC negative input is ground, it is recommended to clear IBUFCON[4] = 0.

Chopping is a common method of offset elimination on input buffers to ADCs.

Chopping requires 2 × ADC conversions per measurement of a buffered ADC input channel.

For example, assume that the input buffer is two input pairs: positive (+) and negative (-) input.  $V_{IN}$  applied is 100 mV and the offset on the buffer is 500  $\mu$ V. Normally, the ADC measures  $V_{IN} + V_{OFFSET}$  and reports 100.5 mV when the buffer is enabled. With chopping enabled, the first ADC sample measures  $V_{IN} + V_{OFFSET}$  and reports 100.5 mV.

For the second ADC sample of this channel, with chopping enabled, the input pairs are switched and the voltage measured by the ADC is

$V_{IN} - V_{OFFSET} = 99.5 \text{ mV}$

Averaging the two results provides the correct result of 100 mV.

To average ADC measurements when the input buffer is enabled, sample an even number of times (that is, 2×, 4×, 6×, and so on).

### Auto-Zero Mode

Auto-zero mode does not require averaging so a single ADC measurement gives an accurate result. Signal-to-noise performance of auto-zero mode is slightly degraded compared to chop mode (see Table 1 of the ADuCM310 data sheet for more details).

## ADC INTERNAL CHANNELS

## Temperature Sensor Settings

The ADuCM310 provides a voltage output from an on-chip band gap reference that is proportional to the absolute temperature of the low voltage die. This voltage output is routed through the front end of the ADC multiplexer (effectively, an additional ADC channel input), facilitating an internal temperature sensor channel that measures die temperature.

The internal temperature sensor is not designed for use as an absolute ambient temperature calculator. The intended use is as an approximate indicator of the temperature of the ADuCM310 low voltage analog die.

An ADC temperature sensor conversion differs from a standard ADC voltage. The ADC performance specifications do not apply to the temperature sensor.

When the temperature sensor channel is selected, the ADC update rate must be <80 kSPS.

- The ADC automatically changes the ADC update rate to 80 kSPS when the temperature sensor, AV<sub>DD</sub>/2, or IOV<sub>DD</sub>/2 input channel is selected. If a different ADC sampling rate is required for other channels after the conversion on any of these three channels is completed, the ADCCNVC register must be updated.

- Note that when the sequencer is enabled and includes any of these three channels, the value in the ADCCNVC does not change and the ADC sampling rate does not change.

The temperature sensor settings are as follows.

To enable the temperature sensor on the ADC, set ADCCHA[12:0] = 0x1116.

To calculate the die temperature, use the following formula:

$T - T_{REF} = (V_{ADC} - V_{TREF}) \times K$

where:

T is the temperature result.

$T_{REF}$  is 25°C.

$V_{ADC}$  is the average ADC result from two consecutive conversions.

$V_{TREF}$  is the ADC result in millivolts that corresponds to  $T_{REF} = 25^{\circ}$ C. The user must measure this in their own application because this value varies from device to device. The typical value used for demonstration purposes is 1290 mV.

*K* is the gain of the ADC in temperature sensor mode. Determine the gain by performing a two-point temperature calibration, because this value varies from device to device. The typical value used for demonstration purposes only is 4.394 mV/°C.

This corresponds to 1/V TC.

Using the default values from the data sheet without any calibration, the equation becomes the following:

$T - 25^{\circ}\text{C} = (V_{ADC} - 1290) \times 1/K$

Therefore, assuming  $V_{\text{ADC}}$  at 25°C = 1290 mV and the slope mV/C as 4.394mV/°C,

$T = ((V_{ADC} - 1290)/4.394) + 25$

where  $V_{ADC}$  is in millivolts.

See the latest version of the ADuCM310 data sheet for the most up to date figures.

Rev. B | Page 23 of 192

## UG-549

For increased accuracy, perform a two-point calibration at a controlled temperature value.

The values used in this example for  $V_{\text{TREF}}$  and K are not guaranteed values. The values  $V_{\text{TREF}}$  and K vary from device to device; therefore, the user must derive the appropriate values by performing a calibration at ambient temperature.

### IDAC Channels

The ADuCM310 allows the voltage on the IDAC output pins to be selected as inputs to the ADC for debug purposes.

Take care when selecting the SOA IDAC (IDAC6) as the ADC input; it must never be selected when the SOA shutdown circuit is enabled (sink current source enabled, HVCON[3] = 1).

Applying a negative voltage less than -0.3 V to ADC MUX results in a latch-up condition that is outside the absolute maximum input voltage ratings to the low voltage analog die.

To select the SOA IDAC as an ADC input, HVCON[0] must be set to 1.

## AV<sub>DD</sub>/2 and IOV<sub>DD</sub>/2 Supply Voltage Channels

These supply voltage channels are measured via internal resistor dividers. Because the resistors used are high impedance and the divided voltage is not buffered, a slower ADC update rate must be used.

The ADC automatically changes the ADC update rate to 80 kSPS when the temperature sensor,  $AV_{DD}/2$ , or  $IOV_{DD}/2$  input channels are selected.

If a different ADC sampling rate is required for other channels after the conversion on any of these three channels is completed, the ADCCNVC register must be updated.

Note that when the sequencer is enabled and includes any of these three channels, the value in the ADCCNVC register does not change and the ADC sampling rate does not change. At rates above 80 kSPS, the accuracy is reduced if the input buffer is disabled.

## ADC SUPPORT CIRCUITS

## ADC Offset and Gain Calibration

For ADC offset calibration, ADCOF[13:0] provides a 14-bit offset calibration. The default value is 0x2000. The calibration resolution is  $\frac{1}{4}$  of the ADCDAT LSB resolution. Therefore, if the 2.505V internal reference is used, the LSB resolution of ADCDAT is ~38.225  $\mu$ V. In this case, the ADCOF LSB resolution is 9.556  $\mu$ V.

When performing an offset calibration, apply 0 V to the analog input channel when the input buffer is disabled. If the input buffer is enabled, apply 150 mV.

Similarly, for ADC gain calibration, ADCGN[13:0] provides a 14-bit gain calibration. The default value is 0x2000. The calibration resolution is ¼ of the ADCDAT LSB resolution. Therefore, if the 2.5 V internal reference is used, the LSB resolution of ADCDAT is again~38.225  $\mu$ V, ADCGN LSB resolution is 9.556  $\mu$ V. When performing a gain calibration, apply a voltage close to full-scale to the analog input channel. For example, if 2.505 V is the required full-scale value, apply 2.5 V to the input.

### ADC Digital Comparator

A digital comparator is provided to allow an interrupt to be triggered if the ADCDAT4 result is above or below a programmable threshold.

Note that only external input channel AIN4 can be used with the digital comparator.

To set up the ADC digital comparator, note the following:

- ADCCMP[17:2] are set a 16-bit ADC threshold value. This value is compared with ADCDAT4[27:12].

- ADCCMP[1] configures the comparator to be triggered when the ADC result is above or below the trigger value.

- To enable the ADC comparator interrupt, set INTSEL[2] = 1 to enable the digital comparator to the Low Voltage Die Interrupt 1 signal.

- Similarly, set INTSEL[10] = 1 to enable the digital comparator interrupt to the Low Voltage Die Interrupt 0 signal.

- The comparator output is asserted when the value in ADCDAT4[27:12] rises above the value in ADCCMP[17:2] if ADCCMP[1] = 1. If ADCDAT4[27:12] remains above ADCCMP[17:2], no further comparator interrupts occur. The interrupt only occurs when the comparator circuit detects a rise above the threshold.

- Similarly, if ADCCMP[1] = 0, the comparator output is asserted when the value in ADCDAT4[27:12] falls below the value in ADCCMP[17:2]. If ADCDAT4[27:12] remains below ADCCMP[17:2], no further comparator interrupts occur. The interrupt only occurs when the comparator circuit detects a fall below the threshold value.

## ADC Channel Sequencer