# R1272S032A033-0500EV

# 34 V Input Synchronous Step-down DC / DC Controller Evaluation Board

NO.EEV-351-032A033-0500-200729

R1272S032A033-0500EV is the evaluation board for R1272 which has the below features, benefits and specifications.

#### **OUTLINE**

The R1272S is a step-down DC/DC controller which can generate an output voltage of 0.7 V to 5.3 V by driving external high- / low-side NMOSs. By the adoption of a unique current mode PWM architecture without an external current sense resistor, the R1272S can make up a stable DC/DC converter with high-efficiency even if adding low Ron MOSFETs and a low DCR inductor externally. And, by the frequency characteristics optimization with using external phase compensation capacitor, the R1272S can achieve a high-speed response to variations of input voltage and load current. The user-settable oscillation frequency is adjustable over a range of 250 kHz to 1 MHz<sup>(1)</sup> by external resistors, and also can be synchronized to an external clock. Output Voltage Control Methods have three operating modes: Forced PWM mode, PLL\_PWM mode, and PWM/VFM Auto-switching mode. These modes are selectable according to conditions of the MODE pin. Especially, the PWM/VFM Auto-switching mode can improve efficiency under light load conditions.

The R1272S can minimize the output voltage drop caused by an input voltage drop at cranking, with reducing the operating frequency (the lowest possible limit is a quarter of the frequency) so that the off-duty is reduced. Protection functions include a current limit function, an UVLO (Under Voltage Lock Out) function, an OVP (Over Voltage Protection) function, a soft-start function, a low-inductor current shutdown function, and so on. Also, a power good function provides the status of output with using a power good (PGOOD) pin.

For EMI reduction, SSCG (Spread-Spectrum Clock Generator) for diffused oscillation frequency at the PWM operation is optionally available.

#### **FEATURES**

| • | Operating Voltage (Maximum Rating)                     | 4.0 V to 34 V (36 V)                            |

|---|--------------------------------------------------------|-------------------------------------------------|

| • | Operating Temperature Range                            | -40°C ≤ Ta ≤ 105°C                              |

|   |                                                        | (Usable in high-temperature environment)        |

| • | Start-up Voltage ·····                                 | 4.5 V                                           |

| • | Output Voltage ······                                  | 3.3 V                                           |

| • | Feedback Voltage Tolerance ······                      | 0.64 V ± 1%                                     |

| • | Consumption Current at No Load (at VFM mode)           | Typ.15 μA                                       |

| • | Adjustable Oscillation Frequency                       | 500 kHz                                         |

| • | Synchronizable Clock Frequency                         | 250 kHz to 1 MHz                                |

| • | Spreading Rate for SSCG ······                         | Typ. ±3.6%                                      |

| • | Minimum On-Time · · · · · · · · · · · · · · · · · · ·  | <b>7</b> 1                                      |

| • | Minimum Off-Time · · · · · · · · · · · · · · · · · · · | Typ.120 ns (at regulation mode)                 |

|   |                                                        | At dropout, actual minimum off-time is reduced. |

| • | Adjustable Soft-start Time (1)                         | Typ.500 μs                                      |

| • | Pre-bias Start-up                                      |                                                 |

<sup>(1) 500</sup> µs (Typ.) as a lower limit with using an external capacitor. Otherwise, available the tracking function through the application of an external voltage.

NO.EEV-351-032A033-0500-200729

Anti-phase Clock Output

• Thermal Shutdown Function · · · · Tj = 160°C (Typ.)

• Under Voltage Lockout (UVLO) Function ...... Typ. 3.3 V

• Over Voltage Detection (OVD) Function ...... FB pin voltage (V<sub>FB</sub>) + 10% (Typ.) Detection/Release Hysteresis ..... FB pin voltage (V<sub>FB</sub>) x 3% (Typ.)

Power Good Output ------ NMOS Open-drain Output

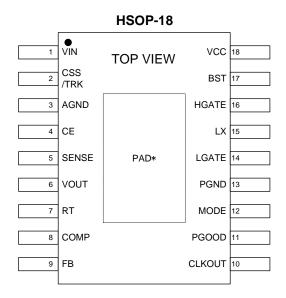

• Package ..... HSOP-18

For more details on R1272 IC, please refer to https://www.n-redc.co.jp/en/pdf/datasheet/r1272-ea.pdf.

#### PART NUMBER INFORMATION

| Product Name       | Package |

|--------------------|---------|

| R1272S032A033-0500 | HSOP-18 |

03: Combination of processing and function.

| Over Current Protection | SSCG   |

|-------------------------|--------|

| Latch mode              | Enable |

2: 70 mV, Set Voltage for Current Limit Threshold (Typ.)

A: Fixed

033: 3.3 V, Output Voltage

0500: 500 kHz, Frequency

# **PCB LAYOUT**

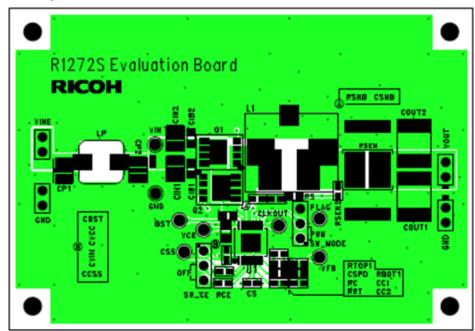

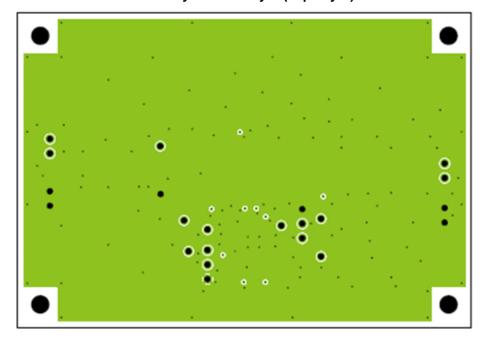

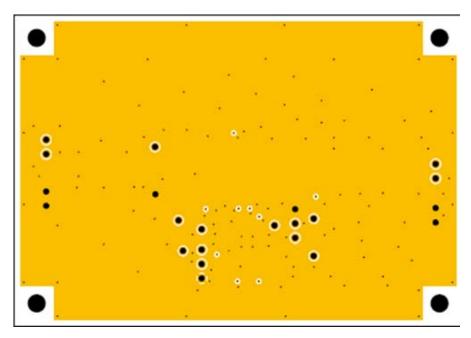

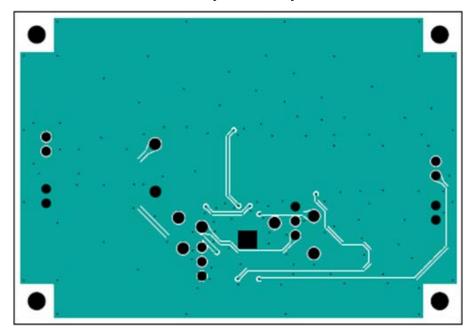

# R1272SxxxA PCB Layouts

PCB Layout - 1st Layer (Top Layer)

PCB Layout - 2<sup>nd</sup> Layer

PCB Layout - 3<sup>rd</sup> Layer

PCB Layout – 4<sup>th</sup> Layer (Bottom Layer) R1272SxxxA

# **PIN DESCRIPTIONS**

#### **HSOP-18 Pin Description**

| Pin No. | Pin Name | Description                                                        |

|---------|----------|--------------------------------------------------------------------|

| 1       | VIN      | Power supply pin                                                   |

| 2       | CSS/TRK  | Soft-start adjustment pin                                          |

| 3       | AGND     | Analog GND pin                                                     |

| 4       | CE       | Chip enable pin (Active "H")                                       |

| 5       | SENSE    | Sense pin for inductor current                                     |

| 6       | VOUT     | Output voltage feedback input pin                                  |

| 7       | RT       | Oscillation adjustment pin                                         |

| 8       | COMP     | Capacitor connecting pin for phase compensation of error amplifier |

| 9       | FB       | Feedback input pin to the error amplifier                          |

| 10      | CLKOUT   | Clock output pin                                                   |

| 11      | PGOOD    | Power-good output pin                                              |

| 12      | MODE     | Mode-set input pin                                                 |

| 13      | PGND     | Power GND pin                                                      |

| 14      | LGATE    | L-side FET control pin                                             |

| 15      | LX       | Switchingpin                                                       |

| 16      | HGATE    | H-side FET control pin                                             |

| 17      | BST      | Boostrap pin                                                       |

| 18      | VCC      | VCC output pin                                                     |

<sup>\*</sup> The tab on the bottom of the package must be electrically connected to GND (substrate level) when mounted on the board.

#### ABSOLUTE MAXIMUM RATINGS

| Symbol                             | Item                                                                         | Rating             | Unit |

|------------------------------------|------------------------------------------------------------------------------|--------------------|------|

| Vin                                | VIN pin voltage                                                              | -0.3 to 36         | V    |

| V <sub>CE</sub>                    | CE pin voltage                                                               | -0.3 to 36         | V    |

| V <sub>CSS</sub> /V <sub>TRK</sub> | CSS/TRK pin voltage                                                          | -0.3 to 3          | V    |

| Vout                               | VOUTpin voltage                                                              | -0.3 to 6          | V    |

| Vsense                             | SENSEpin voltage                                                             | -0.3 to 6          | V    |

| V <sub>RT</sub>                    | RT pin voltage                                                               | -0.3 to 3          | V    |

| V <sub>COMP</sub>                  | COMP pin voltage <sup>(1)</sup>                                              | -0.3 to 6          | V    |

| V <sub>FB</sub>                    | FB pin voltage                                                               | -0.3 to 3          | V    |

|                                    | VCC pin voltage                                                              | -0.3 to 6          | V    |

| $V_{CC}$                           | Output current for VCC pin                                                   | Internally limited | mA   |

| V <sub>BST</sub>                   | BST pin voltage                                                              | LX-0.3 to LX+6     | V    |

| VHGATE                             | HGATE pin voltage                                                            | LX-0.3 to BST      | V    |

| $V_{LX}$                           | LX pin voltage <sup>(2)</sup>                                                | -0.3 to 36         | V    |

| VLGATE                             | LGATE pin voltage <sup>(1)</sup>                                             | -0.3 to 6          | V    |

| V <sub>MODE</sub>                  | MODE pin voltage                                                             | -0.3 to 6          | V    |

| V <sub>PGOOD</sub>                 | PGOOD pin voltage                                                            | -0.3 to 6          | V    |

| V <sub>CLKOUT</sub>                | CLKOUT pin voltage <sup>(1)</sup>                                            | -0.3 to 6          | V    |

| P <sub>D</sub>                     | Power Dissipation <sup>(3)</sup> (HSOP-18, JEDEC STD.51-7 Test Land Pattern) | 3100               | mW   |

| Tj                                 | Junction Temperature                                                         | -40 to 125         | °C   |

| Tstg                               | Storage Temperature Range                                                    | -55 to 125         | °C   |

#### **ABSOLUTE MAXIMUM RATINGS**

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the life time and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings are not assured.

## RECOMMENDED OPERATING CONDITIONS

| Symbol   | Item                        | Rating     | Unit |

|----------|-----------------------------|------------|------|

| $V_{IN}$ | Input Voltage               | 4.0 to 34  | V    |

| Ta       | Operating Temperature Range | -40 to 105 | °C   |

| Vouт     | Output Voltage Range        | 0.7 to 5.3 | V    |

#### **RECOMMENDED OPERATING CONDITIONS**

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if they are used over such ratings by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

**RICOH**

6

$<sup>^{(1)}</sup>$  The pin voltage must be prevented from exceeding  $V_{\text{CC}}$  +0.3V.

$<sup>^{(2)}</sup>$  The pin voltage must be prevented from exceeding  $V_{IN}$  +0.3V.

<sup>(3)</sup> Refer to POWER DISSIPATION for detailed information.

NO.EEV-351-032A033-0500-200729

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}}$  = 12 V, CE =  $V_{\text{IN}}$ , unless otherwise specified.

The specifications surrounded by are guaranteed by design engineering at  $-40^{\circ}$ C  $\leq$  Ta  $\leq$  105 $^{\circ}$ C.

R1272SxxxA (Ta = 25°C)

| Symbol               | Iter                                                    | n                              | Conditions                                                                       | Min.            | Тур.                     | Max.                  | Unit |

|----------------------|---------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------|-----------------|--------------------------|-----------------------|------|

| VSTART               | Start-up Voltage                                        |                                |                                                                                  |                 |                          | 4.5                   | V    |

| Vcc                  | VCC Pin Voltage                                         | (VCC–AGND)                     | V <sub>FB</sub> = 0.672 V                                                        | 4.9             | 5.1                      | 5.3                   | V    |

| ISTANDBY             | Standby Current                                         |                                | V <sub>IN</sub> = 34 V, CE = 0 V                                                 |                 | 3                        | 20                    | μA   |

| I <sub>VIN1</sub>    | VIN Consumption Current 1 at Switching Stop in PWM mode | R1272S0xx                      | V <sub>FB</sub> = 0.672 V,<br>MODE = 5 V,<br>V <sub>OUT</sub> = SENSE = LX = 5 V |                 | 1.0                      | 1.3                   | mA   |

| Ivin2                | VIN Consumption Current 2 at Switching Stop in VFM mode | R1272S0xx                      | V <sub>FB</sub> = 0.672 V,<br>MODE = 0 V<br>V <sub>OUT</sub> = SENSE = LX = 5 V  |                 | 15                       | 75                    | μА   |

| $V_{UVLO2}$          | LIVI O Throobold                                        | Valtaga                        | V <sub>CC</sub> Rising                                                           | 3.85            | 4.0                      | 4.2                   | V    |

| V <sub>UVLO1</sub>   | UVLO Threshold                                          | vollage                        | V <sub>CC</sub> Falling                                                          | 3.1             | 3.3                      | 3.4                   | V    |

| \/                   | FB Voltage Accuracy                                     |                                | Ta = 25°C                                                                        | 0.6336          | 0.64                     | 0.6464                | V    |

| $V_{FB}$             | FB Vollage Accu                                         | ge Accuracy -40°C ≤ Ta ≤ 105°C |                                                                                  | 0.6272          | 0.04                     | 0.6528                | V    |

| fosco                | Oscillation Frequ                                       | ency 0                         | RT = 135 kΩ                                                                      | 225             | 250                      | 275                   | kHz  |

| fosc <sub>1</sub>    | Oscillation Frequ                                       | ency 1                         | RT = 32 kΩ                                                                       | 900             | 1000                     | 1100                  | kHz  |

| toff                 | Minimum OFF Ti                                          | me                             | $V_{IN} = 5 \text{ V}, V_{OUT} = 5 \text{ V}$                                    |                 | 120                      | 190                   | ns   |

| ton                  | Minimum ON Tin                                          | ne                             |                                                                                  |                 | 100                      | 120                   | ns   |

| fsync                | Synchronizing Fr                                        | equency                        | fosc as the reference                                                            | fosc×0.5<br>250 |                          | fosc×1.5              | kHz  |

| tss1                 | Soft-start Time 1                                       |                                | CSS / TRK = OPEN                                                                 | 0.4             |                          | 0.75                  | ms   |

| t <sub>SS2</sub>     | Soft-start Time 2                                       |                                | Css = 4.7 nF                                                                     | 1.4             |                          | 2.0                   | ms   |

| ITSS                 | Charge Current Pin                                      |                                | CSS / TRK = 0 V                                                                  | 1.8             | 2                        | 2.2                   | μΑ   |

| Vssend               | CSS/TRK Pin Vo<br>Soft-start                            | J                              |                                                                                  | V <sub>FB</sub> | V <sub>FB</sub><br>+0.03 | V <sub>FB</sub> +0.06 | V    |

| R <sub>DIS_CSS</sub> | Discharge Resist CSS/TRK Pin                            |                                | V <sub>IN</sub> = 4.5 V, CE = 0 V,<br>CSS / TRK = 3 V                            | 2.0             | 3.0                      | 5.0                   | kΩ   |

| RUPHGATE             | On-resistance of<br>Transistor (HGA                     | •                              | (BST – LX) = 5 V,<br>I <sub>HGATE</sub> = -100 mA                                |                 | 2.5                      | 5.0                   | Ω    |

$V_{\text{IN}}$  = 12 V, CE =  $V_{\text{IN}}$ , unless otherwise specified.

The specifications surrounded by are guaranteed by design engineering at  $-40^{\circ}\text{C} \le \text{Ta} \le 105^{\circ}\text{C}$ .

#### **R1272SxxxA Continued**

$(Ta = 25^{\circ}C)$

| Symbol                | Item                                                         | Conditions                                           | Min.  | Тур. | Max.  | Unit |

|-----------------------|--------------------------------------------------------------|------------------------------------------------------|-------|------|-------|------|

| RDOWNHGATE            | On-resistance of Pull-down Transistor (HGATE Pin)            | (BST – LX) = 5 V,<br>I <sub>HGATE</sub> = 100 mA     |       | 1.5  | 3.5   | Ω    |

| RUPLGATE              | On-resistance of Pull-up<br>Transistor (LGATE Pin)           | (VCC - PGND) = 5 V,<br>$I_{LGATE} = -100 \text{ mA}$ |       | 4.0  | 7.0   | Ω    |

| RDOWNLGATE            | On-resistance of Pull-down Transistor (LGATE Pin)            | (VCC – PGND) = 5 V,<br>I <sub>LGATE</sub> = 100 mA   |       | 1.5  | 3.5   | Ω    |

|                       | Current Limit Threshold                                      |                                                      | 40    | 50   | 60    | mV   |

| VILIMIT               | Voltage                                                      |                                                      | 60    | 70   | 80    | mV   |

|                       | (SENSE – VOUT)                                               |                                                      | 90    | 100  | 110   | mV   |

|                       | Reverse Current Sense                                        |                                                      | -35   | -25  | -15   | mV   |

| VIREVLIMIT            | Threshold                                                    | MODE = H / CLK                                       | -45   | -35  | -25   | mV   |

|                       | (SENSE – VOUT)                                               |                                                      | -60   | -50  | -40   | mV   |

| V <sub>LXSHORTL</sub> | LX Shot to GND Detector<br>Threshold Voltage<br>(VIN – LX)   |                                                      | 0.345 | 0.43 | 0.520 | V    |

| VLXSHORTH             | LX Short to VCC Detector<br>Threshold Voltage<br>(LX – PGND) |                                                      | 0.330 | 0.43 | 0.515 | V    |

| V <sub>CEH</sub>      | CE "High" Input Voltage                                      |                                                      | 1.27  |      |       | V    |

| V <sub>CEL</sub>      | CE "Low" Input Voltage                                       |                                                      |       |      | 1.14  | V    |

| I <sub>CEH</sub>      | CE "High" Input Current                                      | CE = 34 V                                            | 0.20  |      | 2.45  | μA   |

| I <sub>CEL</sub>      | CE "Low" Input Current                                       | CE = 0 V                                             | -1.00 | 0    | 1.00  | μA   |

| I <sub>FBH</sub>      | FB "High" Input Current                                      | $V_{FB} = 3 V$                                       | -0.10 |      | 0.10  | μA   |

| I <sub>FBL</sub>      | FB "Low" Input Current                                       | $V_{FB} = 0 V$                                       | -0.10 |      | 0.10  | μA   |

| $V_{MODEH}$           | MODE "High" Input Voltage                                    |                                                      | 1.33  |      |       | V    |

| VMODEL                | MODE "Low" Input Voltage                                     |                                                      |       |      | 0.74  | V    |

| I <sub>моден</sub>    | MODE "High" Input Current                                    | MODE = 6 V                                           | 1.00  |      | 6.60  | μA   |

| IMODEL                | MODE "Low" Input Current                                     | MODE = 0 V                                           | -1.00 | 0    | 1.00  | μA   |

| Vclkouth              | CLKOUT Pin "High" Output Voltage                             | CLKOUT = Hi-z                                        | 4.7   |      | Vcc   | V    |

| Vclkoutl              | CLKOUT Pin "Low" Output Voltage                              | CLKOUT = Hi-z                                        | 0     |      | 0.1   | V    |

| T <sub>TSD</sub>      | Thermal Shutdown                                             | Ta Rising                                            | 150   | 160  |       | °C   |

| T <sub>TSR</sub>      | Threshold Temperature                                        | Ta Falling                                           | 125   | 140  |       | °C   |

$V_{\text{IN}}$  = 12 V, CE =  $V_{\text{IN}}$ , unless otherwise specified.

|                                                 | R1272S                                         |

|-------------------------------------------------|------------------------------------------------|

|                                                 | NO.EEV-351-032A033-0500-200729                 |

| The specifications surrounded by are guaranteed | d by design engineering at -40°C ≤ Ta ≤ 105°C. |

| R1272SxxxA Continued                            | (Ta = 25°C)                                    |

| Symbol                | Item                            | Conditions                                       | Min   | Тур                   | Max.  | Unit |

|-----------------------|---------------------------------|--------------------------------------------------|-------|-----------------------|-------|------|

| V <sub>PGOODOFF</sub> | PGOOD Pin "OFF" Voltage         | V <sub>IN</sub> = 4.0 V,<br>PGOOD = 1 mA         |       | 0.26                  | 0.54  | V    |

| Ipgoodoff             | PGOOD Pin "OFF" Current         | V <sub>IN</sub> = 34 V, CE = 0 V,<br>PGOOD = 6 V | -0.10 | 0                     | 0.10  | μΑ   |

| V <sub>FBOVD1</sub>   | FB Pin OVD Threshold Voltage    | V <sub>FB</sub> Rising                           | 0.680 | V <sub>FB</sub> ×1.10 | 0.740 | V    |

| V <sub>FBOVD2</sub>   | FB FIII OVD Tillesiloid Vollage | V <sub>FB</sub> Falling                          | 0.664 | V <sub>FB</sub> ×1.07 | 0.712 | V    |

| V <sub>FBUVD1</sub>   | FB Pin UVD Threshold Voltage    | V <sub>FB</sub> Falling                          | 0.556 | V <sub>FB</sub> ×0.90 | 0.604 | V    |

| V <sub>FBUVD2</sub>   | TE FIII OVD TITIESTIOID VOItage | V <sub>FB</sub> Rising                           | 0.574 | V <sub>FB</sub> ×0.93 | 0.628 | V    |

| gm (EA)               | Trans Conductance Amplifier     | COMP = 1.5 V                                     | 0.35  | 1                     | 1.55  | mS   |

All test items listed under Electrical Characteristics are done under the pulse load condition ( $Tj \approx Ta = 25$ °C).

NO.EEV-351-032A033-0500-200729

### **APPLICATION INFORMAITON**

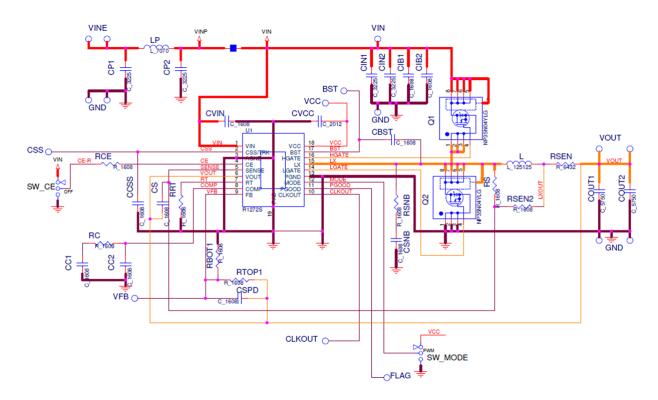

R1272SxxxA Typical Application Circuit at 500 kHz

# R1272S032A033-0500 Recommended External Components<sup>(1)</sup>

| CP1<br>[μF] | LP<br>[µH]     | CP2<br>[µF]   | Q1(FET)      | Q2(FET)      | L<br>[μH]    | CIN1<br>[µF] | CIN2<br>[µF]  |

|-------------|----------------|---------------|--------------|--------------|--------------|--------------|---------------|

| 10          | 1.0            | 10            | _            | _            | 2.2          | 10           | 10            |

| CVIN        | COUT 1<br>[µF] | COUT2<br>[µF] | CBST<br>[µF] | CVCC<br>[µF] | CCSS<br>[nF] | CSPD<br>[pF] | CC1<br>[nF]   |

| OPEN        | 100            | 22*2          | 0.22         | 2.2          | 3.3          | 100          | 6.8           |

| CC2<br>[pF] | RTOP1<br>[kΩ]  | RBOT1<br>[kΩ] | RC<br>[kΩ]   | RRT<br>[kΩ]  | RS           | RSEN<br>[mΩ] | RSEN2<br>[kΩ] |

| 47          | 91.43          | 22            | 12           | 68           | OPEN         | 3            | 1             |

RCE [Ω] 0

<sup>(1)</sup> The bill of materials will be attached on the shipment of each purchased evaluation board.

#### **TECHNICAL NOTES**

The performance of power source circuits using this IC largely depends on peripheral circuits. When selecting the peripheral components, please consider the conditions of use. Do not allow each component, PCB pattern or the IC to exceed their respected rated values (voltage, current, and power) when designing the peripheral circuits.

- External components must be connected as close as possible to the Ics and make wiring as short as

possible. Especially, the capacitor connected in between VIN pin and GND pin must be wiring the shortest.

If their impedance is high, internal voltage of the IC may shift by the switching current, and the operating

may be unstable. Make the power supply and GND lines sufficient.

- Place a capacitor (Cout) to keep a distance between C<sub>IN</sub> and Cout in order to avoid the high-frequency noise by input.

- AGND and PGND for the controller must be wired to the GND line at the low impedance point of the same layer with C<sub>IN</sub> and C<sub>OUT</sub>.

- Place a capacitor (C<sub>BST</sub>) as close as possible to the LX pin and the BST pin. If controlling slew rate for EMI, a resistor (R<sub>BST</sub>) should be in series between the BST pin and the capacitor (C<sub>BST</sub>), but not be in series to FET for HGATE and LGATE pins. Because connecting the resistor in series to the FET becomes a cause of a through-current.

- The tab on the bottom of the HSOP-18 package must be connected to GND when mounted on the board.

To improve thermal dissipation on the multilayer board, set via to release the heat to the other layer in the connecting part of the tab on the bottom. Likewise, thermal dissipation for FET is required.

- The NC pin must be set to "Open".

- The MODE pin requires the H / L voltages with the high stability when the forced PWM mode (MODE = "H") or the VFM mode (MODE = "L") is enabled. If the voltage with the high stability cannot be applied, connection to the VCC pin as "H" level or the AGND pin as "L" level is recommended. If connecting to the PGND pin as noisy, a malfunction may occur. Avoid the use of the MODE pin being "Open".

- If V<sub>OUT</sub> is a minus potential, the setup cannot occur.

- The power for the controller and for the high-side FET must be used on the same power supply, since the internal slope compensation is applied as the power supply voltage of the high-side FET is equal to the controller's. If applying the other power supply voltage, the controller will become unstable owing to the inappropriate slope compensation.

- 1. The products and the product specifications described in this document are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to Ricoh sales representatives for the latest information thereon.

- 2. The materials in this document may not be copied or otherwise reproduced in whole or in part without prior written consent of Ricoh.

- 3. Please be sure to take any necessary formalities under relevant laws or regulations before exporting or otherwise taking out of your country the products or the technical information described herein.

- 4. The technical information described in this document shows typical characteristics of and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under Ricoh's or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, telecommunication equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death (aircraft, spacevehicle, nuclear reactor control system, traffic control system, automotive and transportation equipment, combustion equipment, safety devices, life support system etc.) should first contact us.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order to prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. Anti-radiation design is not implemented in the products described in this document.

- 8. The X-ray exposure can influence functions and characteristics of the products. Confirm the product functions and characteristics in the evaluation stage.

- 9. WLCSP products should be used in light shielded environments. The light exposure can influence functions and characteristics of the products under operation or storage.

- 10. There can be variation in the marking when different AOI (Automated Optical Inspection) equipment is used. In the case of recognizing the marking characteristic with AOI, please contact Ricoh sales or our distributor before attempting to use AOI.

- 11. Please contact Ricoh sales representatives should you have any questions or comments concerning the products or the technical information.

Ricoh is committed to reducing the environmental loading materials in electrical devices with a view to contributing to the protection of human health and the environment.

Halogen Free

Ricoh has been providing RoHS compliant products since April 1, 2006 and Halogen-free products since April 1, 2012.

# RICOH RICOH ELECTRONIC DEVICES CO., LTD.

Official website

https://www.n-redc.co.jp/en/

**Contact us**

https://www.n-redc.co.jp/en/buy/