# TLE9868QXB20

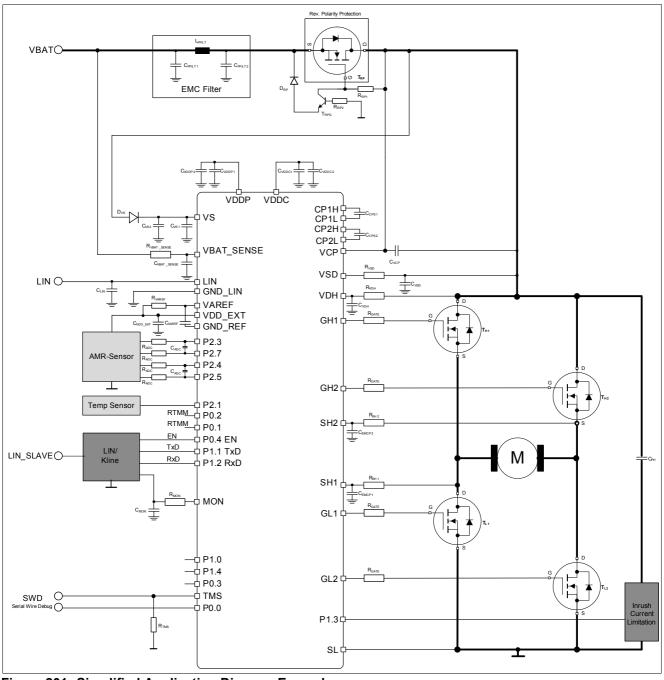

Microcontroller with LIN and H-Bridge MOSFET Driver for Automotive Applications

**BF-Step**

# User's Manual

Rev. 1.3, 2017-07-05

# Automotive Power

| <b>1</b><br>1.1                                 | Overview                                                                                                                                                                                      |                      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

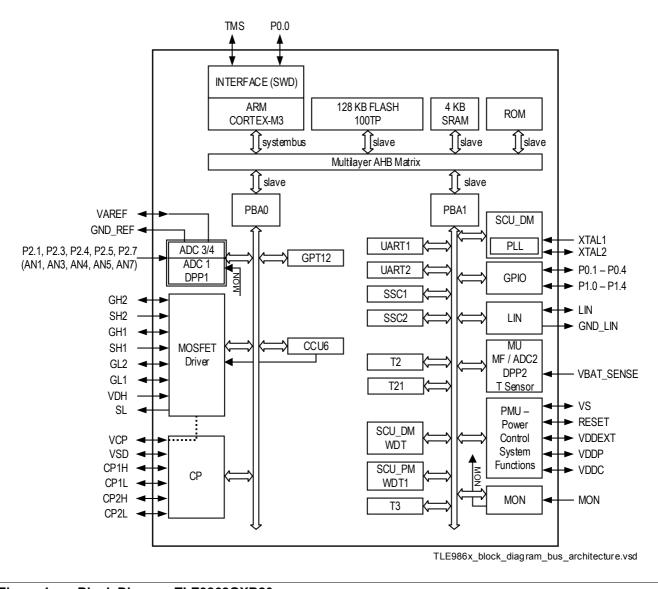

| 2                                               | Block Diagram                                                                                                                                                                                 | 17                   |

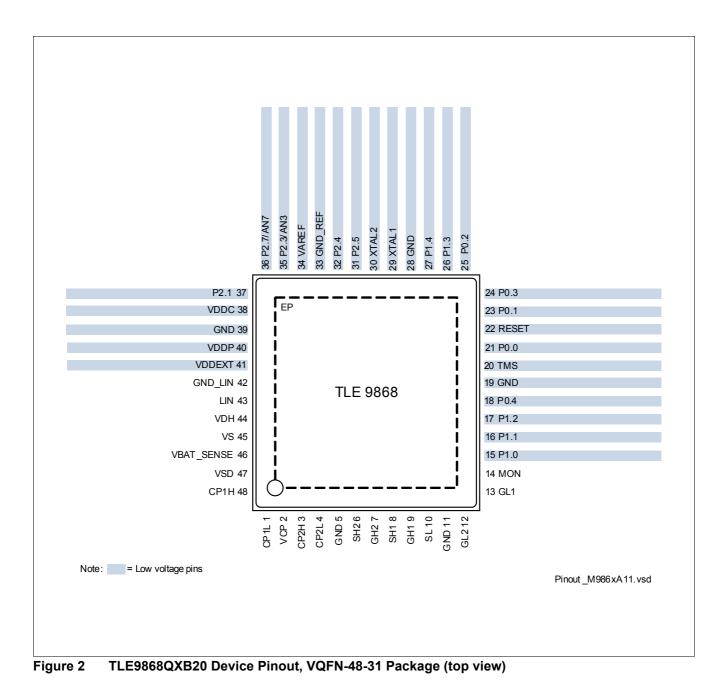

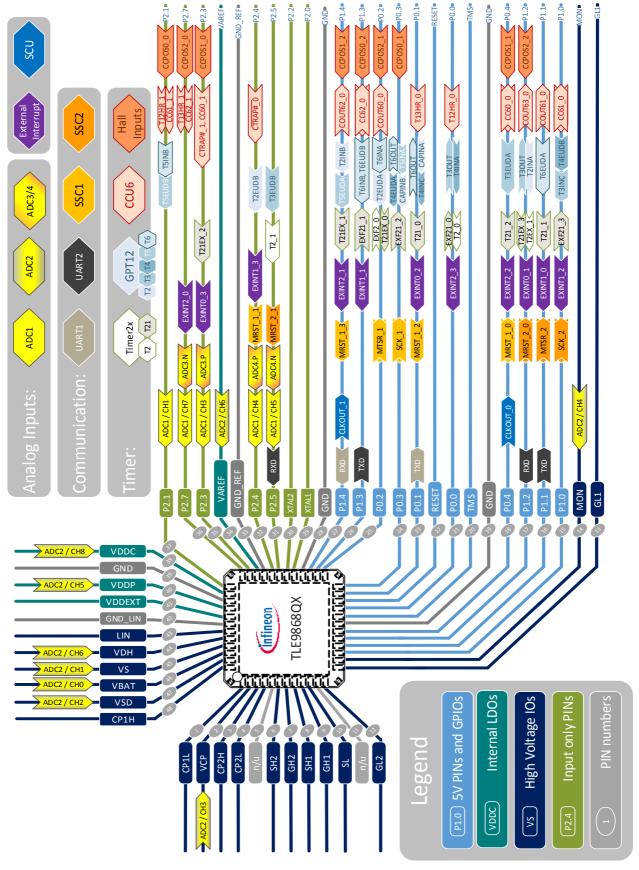

| <b>3</b><br>3.1<br>3.2                          | Device Pinout and Pin Configuration         Device Pinout         Pin Configuration                                                                                                           | 18                   |

| 4                                               | Modes of Operation                                                                                                                                                                            | 22                   |

| 5                                               | Device Register Types                                                                                                                                                                         | 24                   |

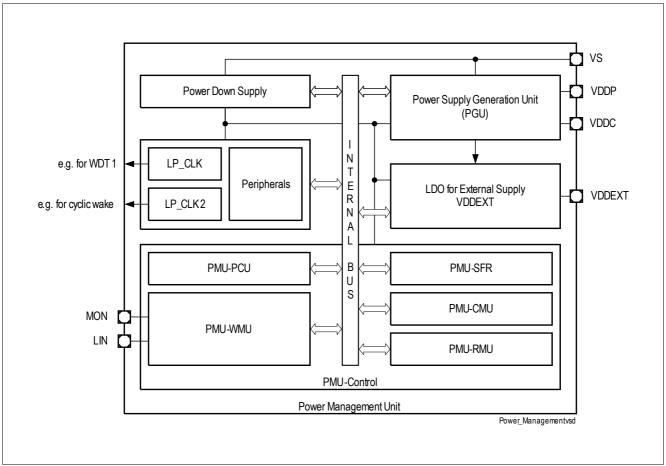

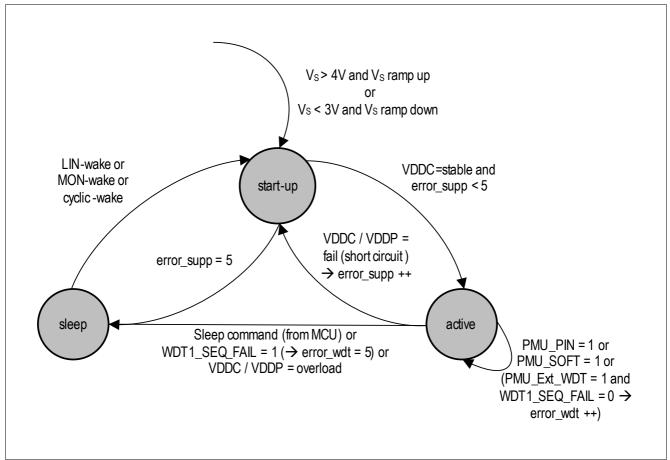

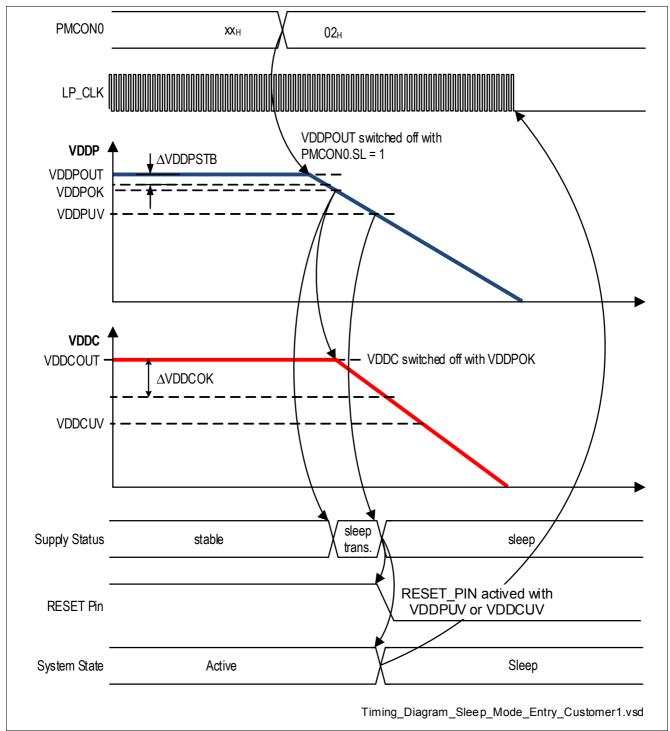

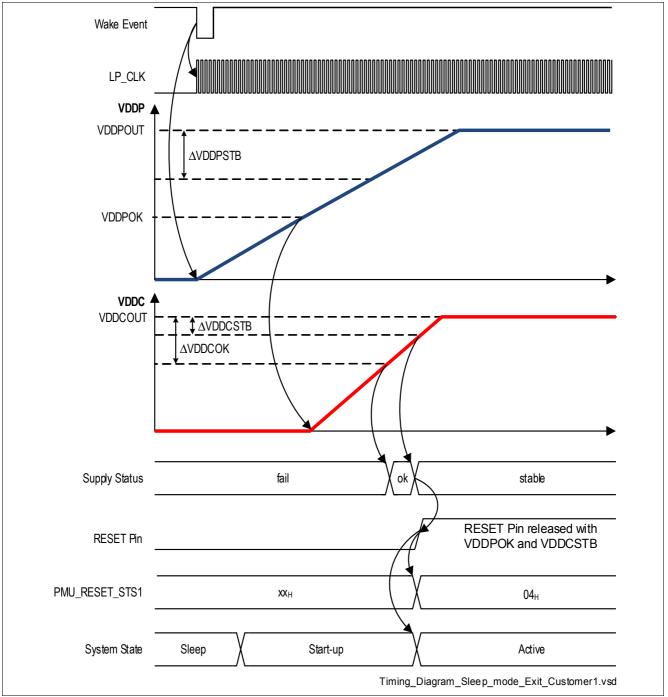

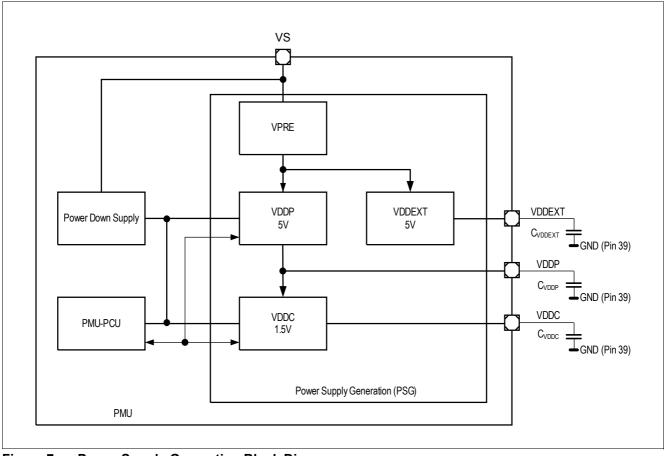

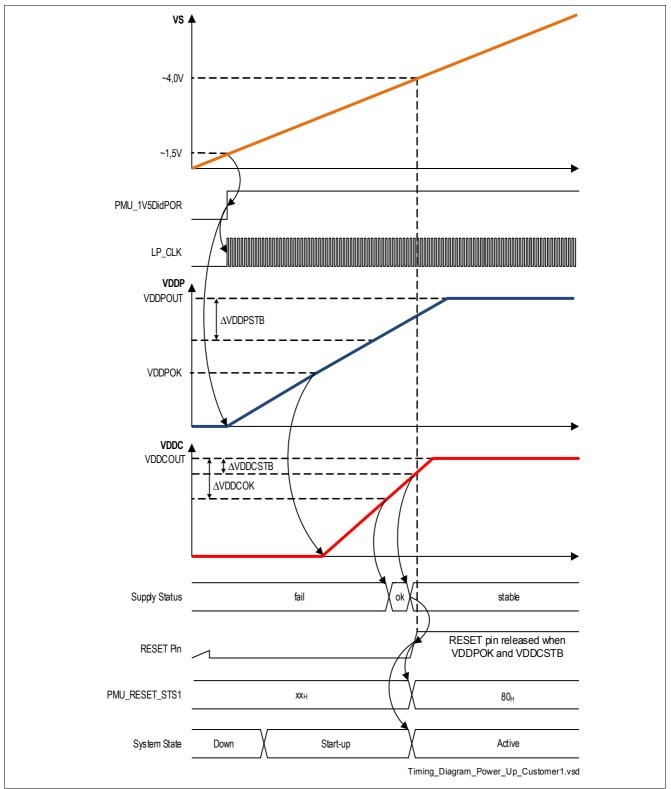

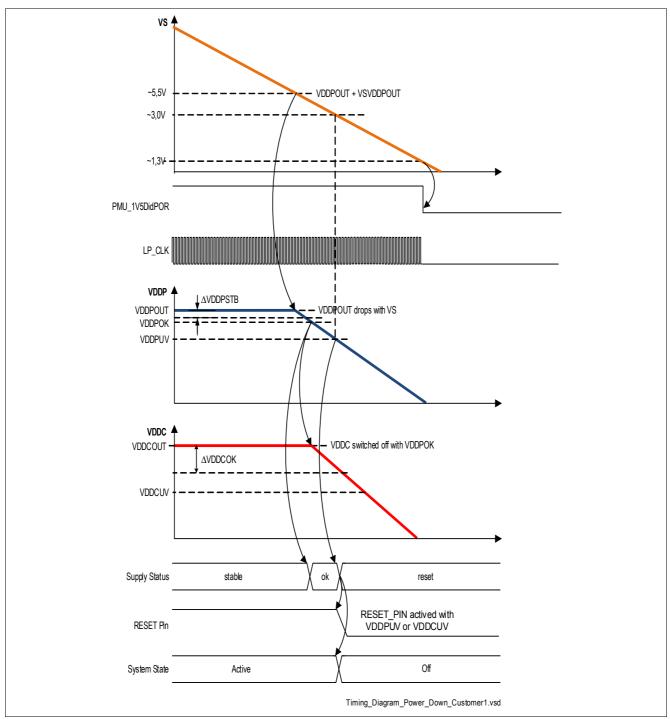

| <b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.3 | Power Management Unit (PMU)<br>Features<br>Introduction<br>Block Diagram<br>PMU Modes Overview<br>Power Supply Generation Unit (PGU)                                                          | 25<br>25<br>26<br>28 |

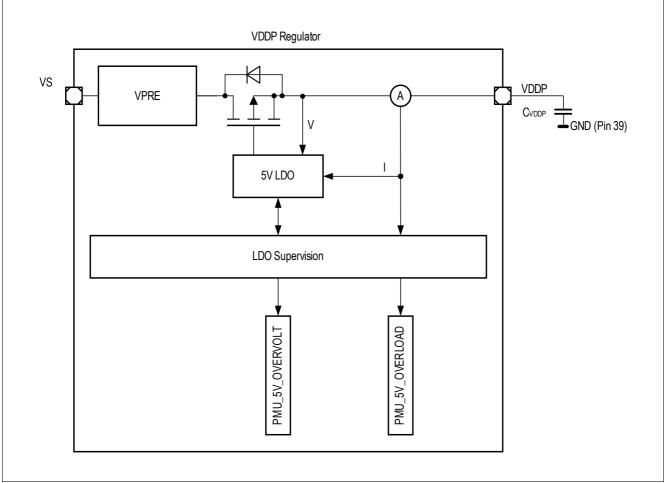

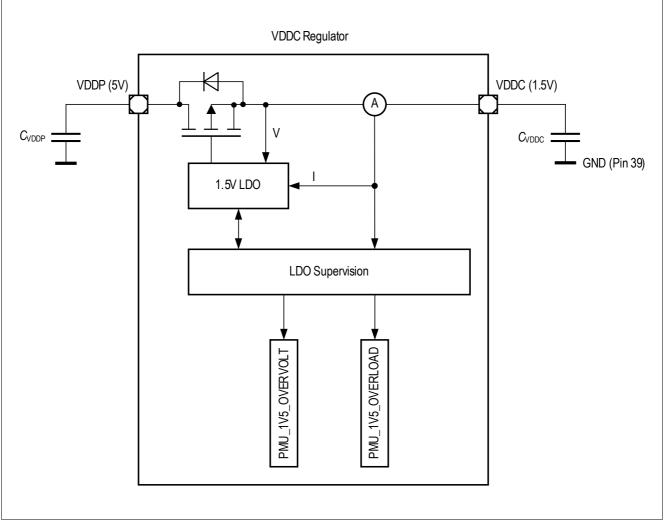

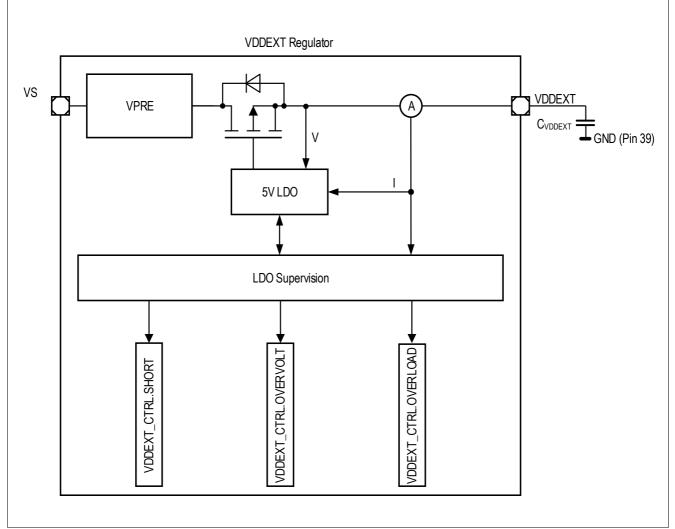

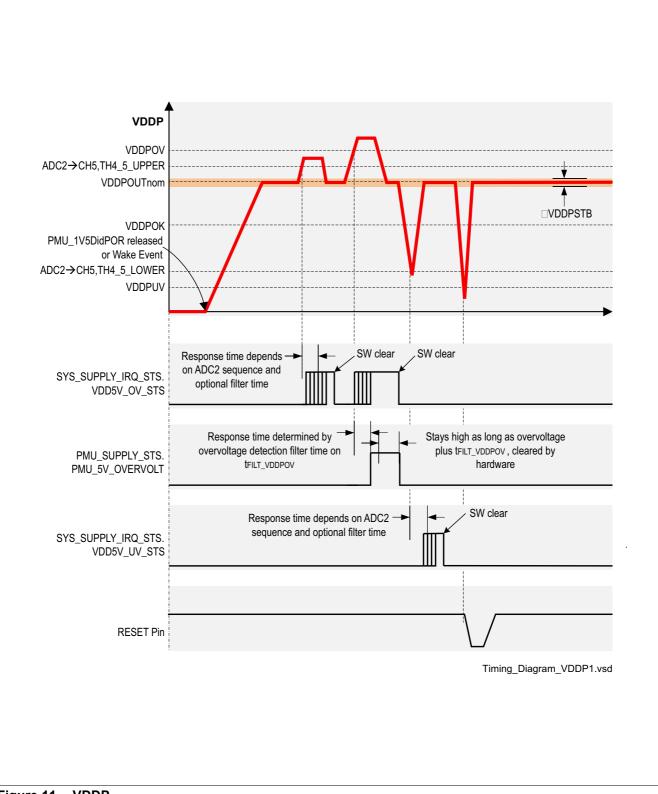

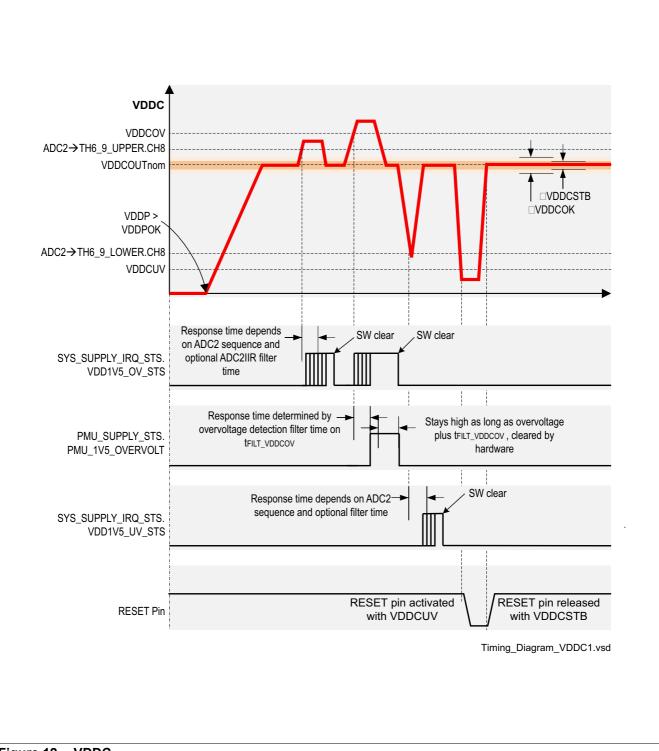

| 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                | Power Supply Generation Unit (PGU)         Voltage Regulator 5.0V (VDDP)         Voltage Regulator 1.5V (VDDC)         External Voltage Regulator 5.0V (VDDEXT)         PMU Register Overview | 31<br>33<br>34       |

| 6.3.5<br>6.3.5.1<br>6.3.5.2<br>6.4              | Register Definition       Power Supply Generation Register         VDDEXT Control Register       Power Control Unit                                                                           | 36<br>40             |

| 6.4.1<br>6.4.1.1<br>6.4.1.2<br>6.4.1.3          | Power Control Unit - Fail Safe Scenarios                                                                                                                                                      | 41<br>41<br>41       |

| 6.4.2<br>6.4.2.1<br>6.5                         | Register Definition         PMU System Fail Register         Wake-Up Management Unit (WMU)                                                                                                    | 44<br>44             |

| 6.5.1<br>6.5.2<br>6.5.2.1<br>6.5.2.2            | Functional Description         Register Definition         PMU Wake-Up Configuration Register         DMU Wake Up Status Descriptor                                                           | 46<br>47             |

| 6.6<br>6.6.1<br>6.6.2                           | PMU Wake-Up Status Register         Cyclic Management Unit (CMU)         Functional Description         Cyclic Wake Mode                                                                      | 50<br>50             |

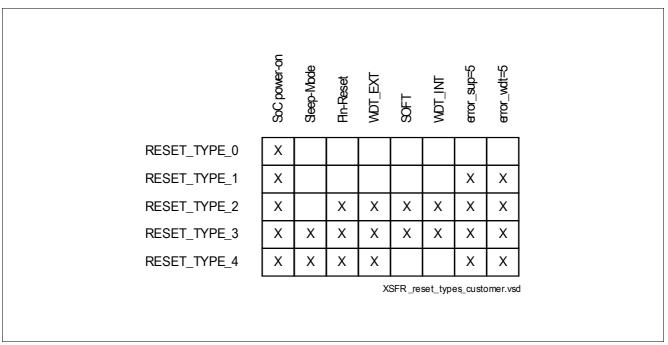

| 6.6.3<br>6.6.3.1<br>6.7                         | Register Definition       Cyclic Wake Configuration Registers (CYCMU)         Reset Management Unit (RMU)       Cyclic Wake Configuration Registers                                           | 50<br>51             |

| 6.7.1<br>6.7.2<br>6.7.2.1                       | Reset Management Unit (RMO)         Functional Description         Register Definition         Reset Management Unit Registers (RMU)                                                          | 54<br>58             |

| 6.8<br>6.8.1<br>6.8.2<br>6.8.2.1                | PMU Data Storage Area                                                                                                                                                                         | 62<br>62<br>62       |

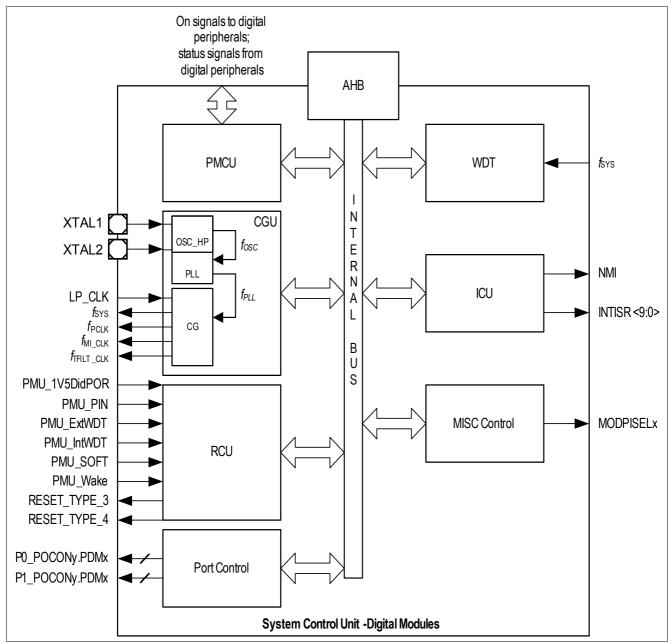

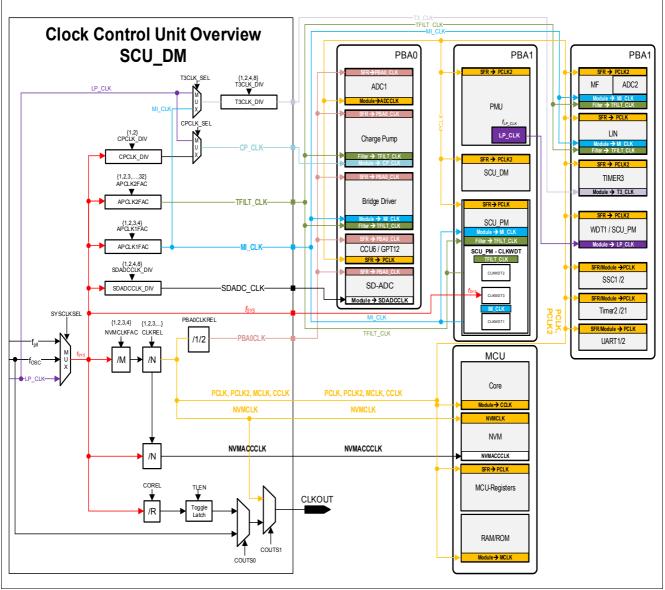

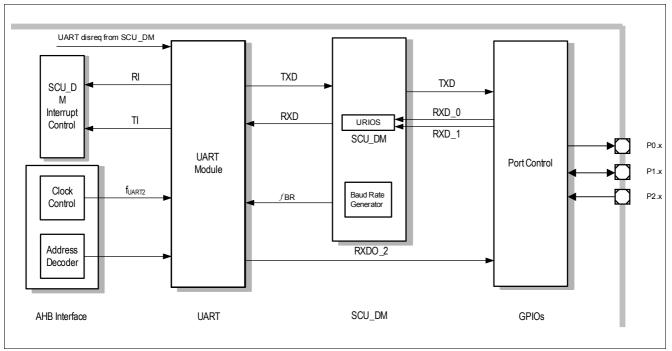

| 7       | System Control Unit - Digital Modules (SCU-DM)          | 69 |

|---------|---------------------------------------------------------|----|

| 7.1     | Features                                                |    |

| 7.2     | Introduction                                            | 69 |

| 7.2.1   | Block Diagram                                           | 70 |

| 7.2.2   | SCU Register Overview                                   | 71 |

| 7.2.2.1 | Register Map                                            | 71 |

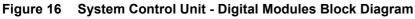

| 7.3     | Clock Generation Unit                                   | 73 |

| 7.3.1   | Low Precision Clock                                     | 74 |

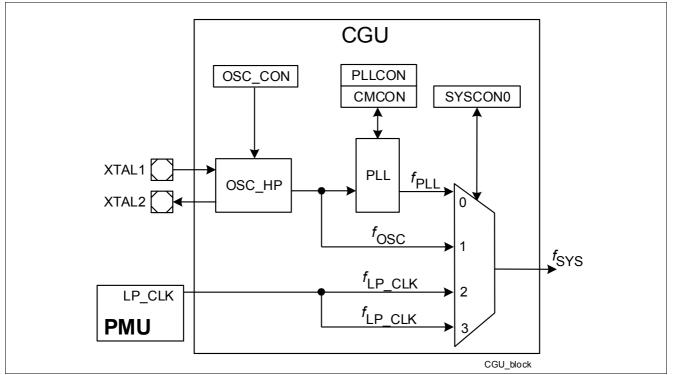

| 7.3.2   | High Precision Oscillator Circuit (OSC_HP)              | 74 |

| 7.3.2.1 | External Input Clock Mode                               |    |

| 7.3.2.2 | External Crystal Mode                                   | 74 |

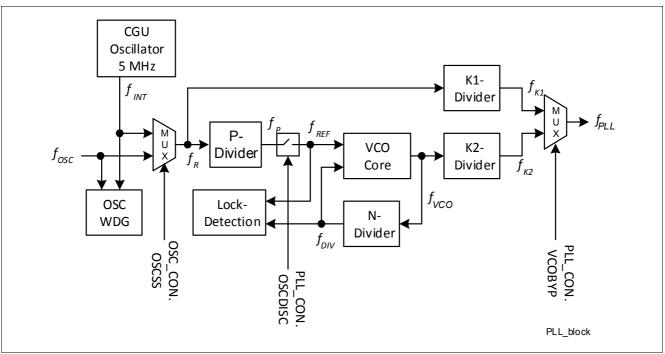

| 7.3.3   | Phase-Locked Loop (PLL) Module                          | 75 |

| 7.3.3.1 | Features                                                | 75 |

| 7.3.3.2 | PLL Functional Description                              | 76 |

| 7.3.3.3 | Oscillator Watchdog                                     |    |

| 7.3.3.4 | PLL VCO Lock Detection                                  |    |

| 7.3.3.5 | Internal Oscillator (OSC PLL)                           |    |

| 7.3.3.6 | Switching PLL Parameters                                |    |

| 7.3.3.7 | Oscillator Watchdog Event or PLL Loss of Lock Detection |    |

| 7.3.3.8 | Oscillator Watchdog Event or Loss of Lock Recovery      |    |

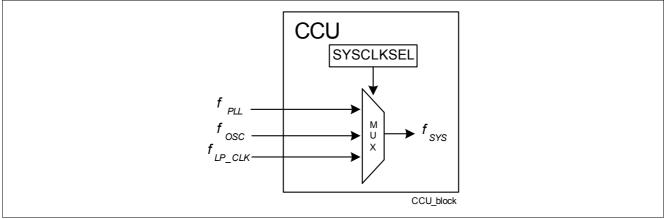

| 7.3.4   |                                                         |    |

| 7.3.4.1 | Clock Tree                                              |    |

| 7.3.4.2 | Startup Control for System Clock                        |    |

| 7.3.5   | External Clock Output                                   |    |

| 7.3.6   | CGU Registers                                           |    |

| 7.3.6.1 | PLL Oscillator Register                                 |    |

| 7.3.6.2 | PLL Registers                                           |    |

| 7.3.6.3 | System Clock Control Registers                          |    |

| 7.3.6.4 | Analog Peripherals Clock Control Registers              |    |

| 7.3.6.5 | External Clock Control Register 1                       |    |

| 7.4     | Reset Control                                           |    |

| 7.4.1   | Types of Reset                                          | 02 |

| 7.4.2   | Overview                                                |    |

| 7.4.3   | Module Reset Behavior                                   |    |

| 7.4.4   |                                                         | 04 |

| 7.4.4.1 | Power-On / Brown-out Reset                              | 04 |

| 7.4.4.2 | Wake-up Reset                                           | 04 |

| 7.4.4.3 | Hardware Reset                                          | 04 |

| 7.4.4.4 | WDT1 Reset                                              | 04 |

| 7.4.4.5 | WDT / Soft Reset                                        | 04 |

| 7.4.5   | Reset Register Description                              | 05 |

| 7.4.6   | Booting Scheme                                          |    |

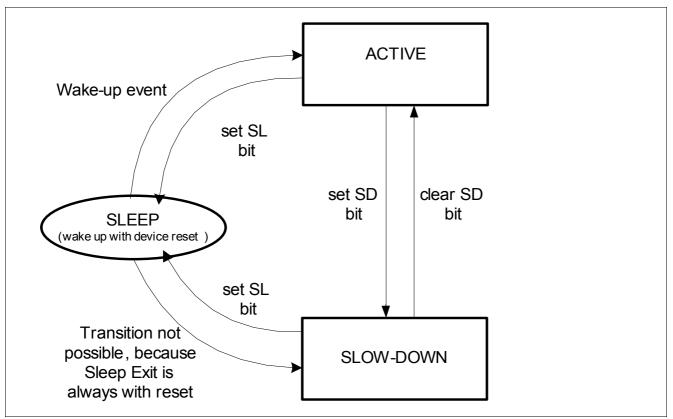

| 7.5     | Power Management                                        |    |

| 7.5.1   | Overview                                                | 07 |

| 7.5.2   | Functional Description                                  | 80 |

| 7.5.2.1 | Slow Down Mode                                          |    |

| 7.5.2.2 | Sleep Mode                                              |    |

| 7.5.3   | Register Description                                    |    |

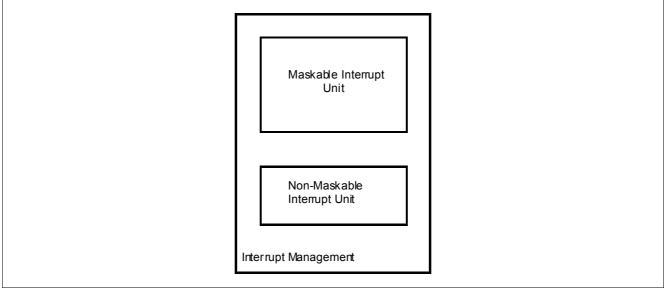

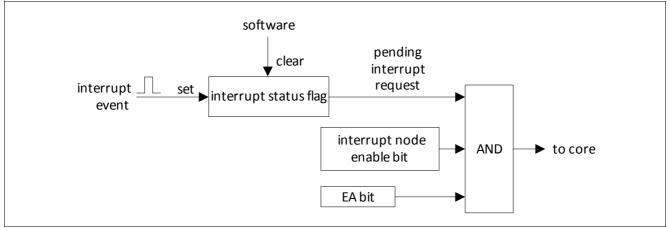

| 7.6     | Interrupt Management                                    |    |

| 7.6.1   | Overview                                                |    |

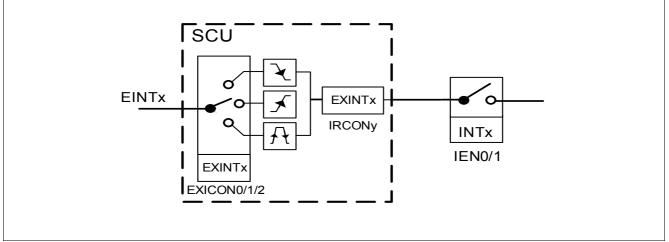

| 7.6.1.1 | External Interrupts                                     | 10 |

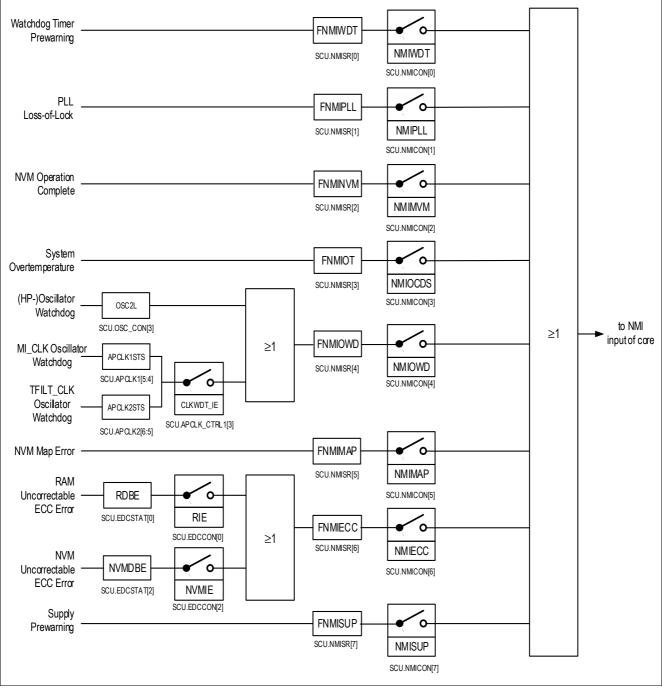

| 7.6.1.2<br>7.6.2<br>7.6.3<br>7.6.3.1<br>7.6.4<br>7.7<br>7.7.1<br>7.7.1<br>7.7.2<br>7.8<br>7.8.1<br>7.9<br>7.10                                                              | Extended Interrupts .<br>Interrupt Node Assignment .<br>Interrupt Related Registers .<br>Interrupt Event Enable Control .<br>NMI Event Flags Handling .<br>General Port Control .<br>Input Pin Function Selection .<br>Port Output Control .<br>Flexible Peripheral Management .<br>Peripheral Management Registers .<br>Module Suspend Control .<br>Watchdog Timer .                                                                                                                               | <ol> <li>111</li> <li>113</li> <li>117</li> <li>118</li> <li>122</li> <li>128</li> <li>129</li> <li>131</li> <li>134</li> </ol> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

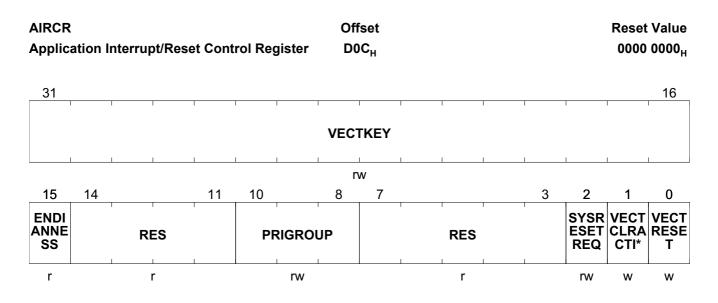

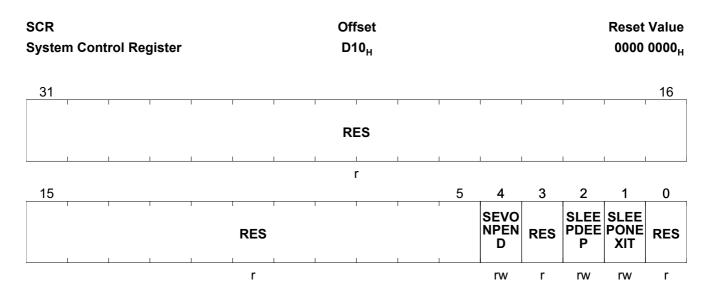

| 7.10.1<br>7.10.2<br>7.11<br>7.11.1<br>7.11.2<br>7.12<br>7.12.1<br>7.12.2<br><b>8</b>                                                                                        | Functional Description         Register Description         Error Detection and Correction Control for Memories         Error Detection and Correction Control Register         Error Detection and Correction Status Register         Miscellaneous Control         Bit Protection Register         System Control and Status Registers    System Control Unit - Power Modules (SCU-PM)                                                                                                            | 136<br>138<br>138<br>140<br>142<br>142<br>142                                                                                   |

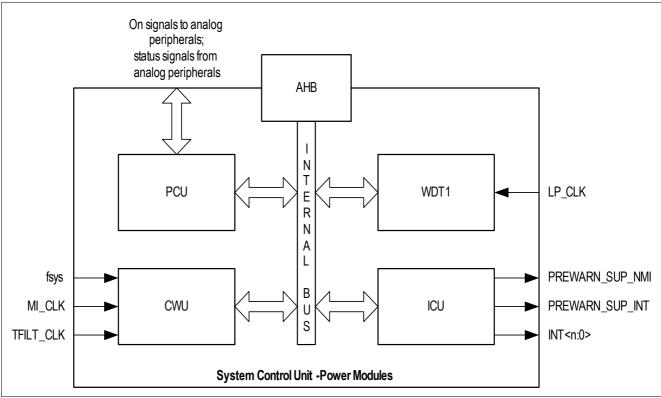

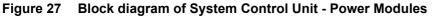

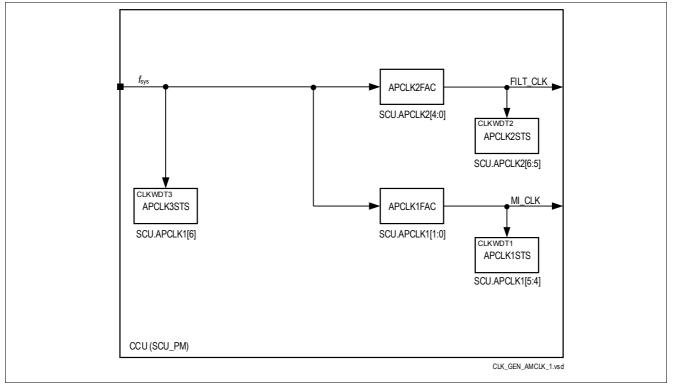

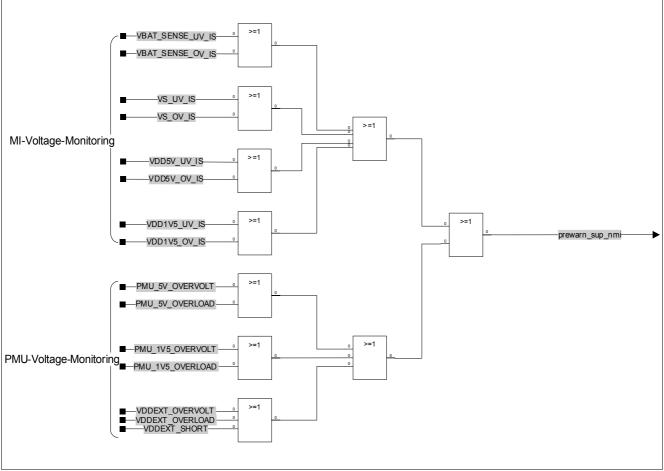

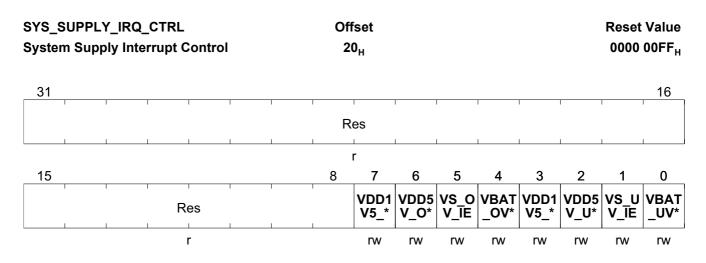

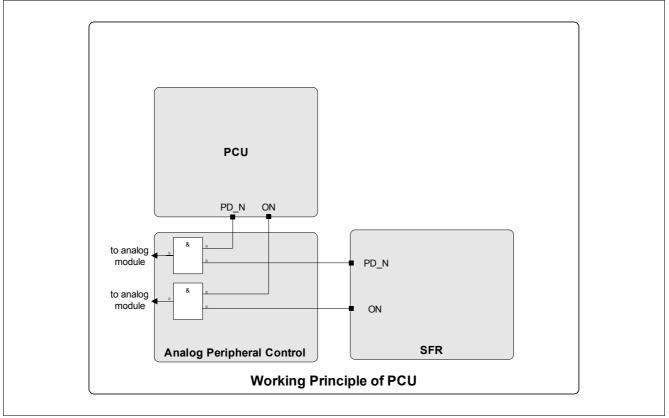

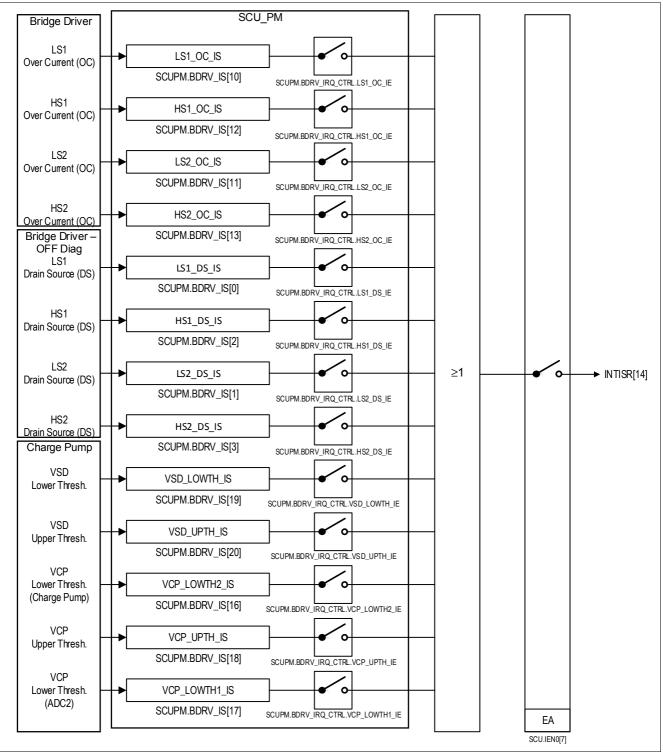

| <ul> <li>8.1</li> <li>8.2</li> <li>8.2.1</li> <li>8.3</li> <li>8.3.1</li> <li>8.3.1.1</li> <li>8.3.2</li> <li>8.4</li> <li>8.4.1</li> <li>8.4.2</li> <li>8.4.2.1</li> </ul> | System Control Ont - Power Modules (SCO-PM)         Features         Introduction         Block Diagram         Clock Watchdog Unit (CWU)         Fail Safe Functionality of Clock Generation Unit (Clock Watchdog)         Functional Description of Clock Watchdog Module         Clock Generation Unit Register         Interrupt Control Unit (ICU)         Structure of PREWARN_SUP_NMI         Interrupt Control Unit Status Register         Interrupt Control Unit Status Overview Register | 152<br>152<br>153<br>153<br>154<br>155<br>158<br>158<br>158                                                                     |

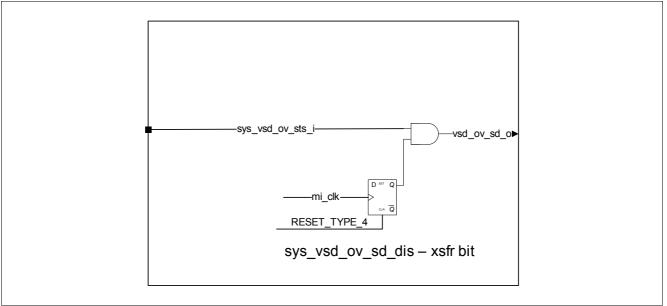

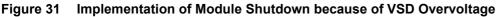

| 8.4.2.2<br>8.5<br>8.5.1<br>8.5.2<br>8.5.3<br>8.6<br>8.6.1<br>8.6.1.1                                                                                                        | Interrupt Control Unit - Interrupt Enable Register<br>Power Control Unit for Power Modules (PCU_PM)<br>VSD-Overvoltage System Shutdown<br>Overtemperature System Shutdown<br>Power Control Unit Register<br>MISC Control<br>Bus Faults<br>Bus Fault Control Register                                                                                                                                                                                                                                | 178<br>179<br>180<br>181<br>182<br>182<br>182                                                                                   |

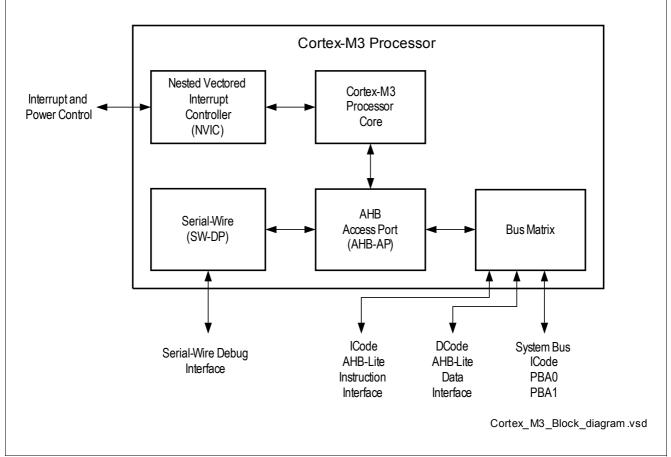

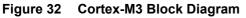

| <b>9</b><br>9.1<br>9.2<br>9.2.1<br>9.3<br>9.3.1<br>9.3.1.1<br>9.3.1.2<br>9.4<br>9.5                                                                                         | ARM Cortex-M3 Core         Features         Introduction         Block Diagram         Functional Description         Registers         General-Purpose Registers         Special-Purpose Program Status Registers (xPSR)         Summary of Processor Registers         Instruction Set Summary                                                                                                                                                                                                    | 188<br>189<br>189<br>189<br>190<br>190<br>191<br>192                                                                            |

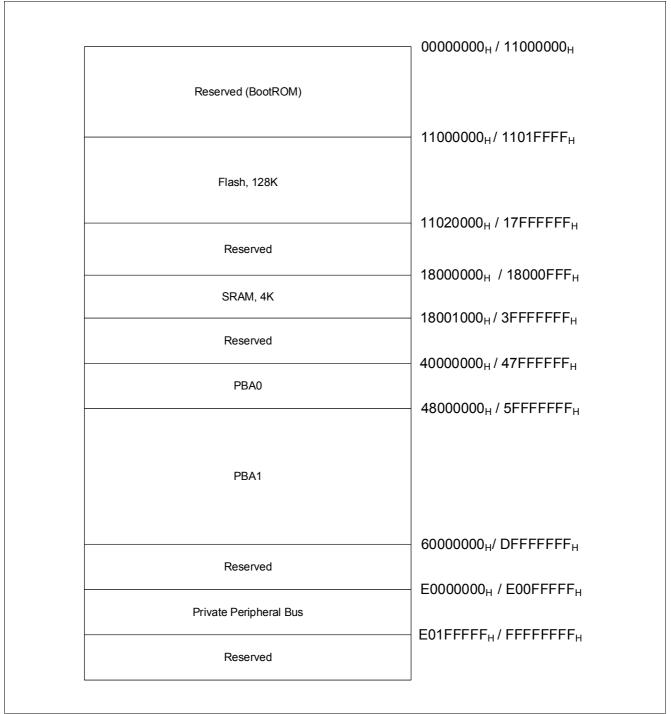

| 10        | Address Space Organization                            | 236 |

|-----------|-------------------------------------------------------|-----|

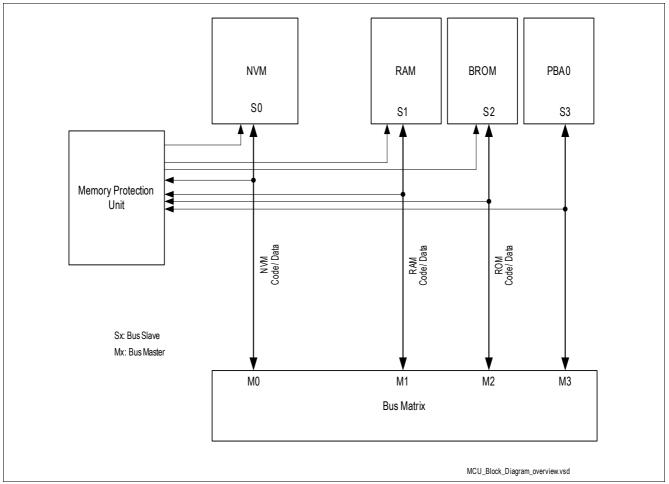

| 11        | Memory Control Unit                                   | 241 |

| 11.1      | Features                                              |     |

| 11.2      | Introduction                                          | 241 |

| 11.2.1    | Block Diagram                                         | 241 |

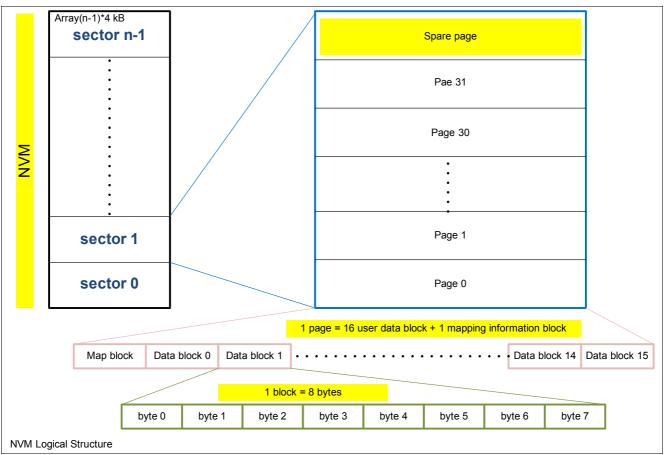

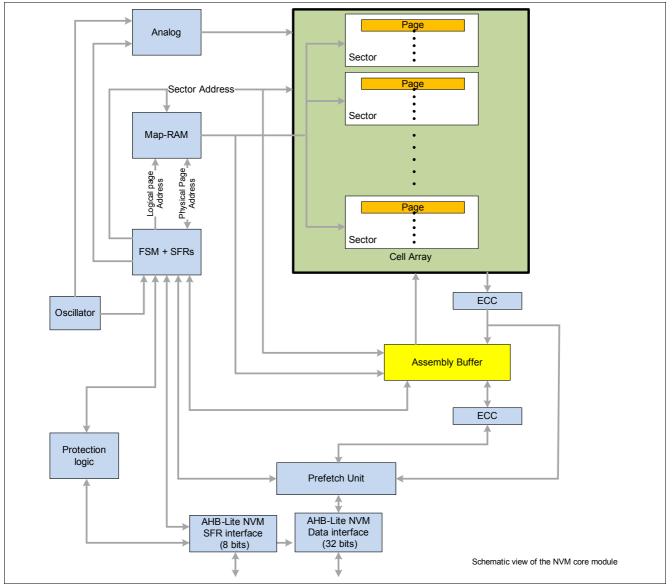

| 11.3      | NVM Module (Flash Memory)                             | 243 |

| 11.3.1    | Definitions                                           | 243 |

| 11.3.1.1  | General Definitions                                   | 243 |

| 11.3.2    | Functional Description                                | 246 |

| 11.3.2.1  | Basic Block Functions                                 | 246 |

| 11.3.2.2  | Memory Cell Array                                     | 247 |

| 11.3.2.3  | SFR Accesses                                          | 248 |

| 11.3.2.4  | Memory Read                                           | 248 |

| 11.3.2.5  | Memory Write                                          | 248 |

| 11.3.2.6  | Timing                                                | 249 |

| 11.3.2.7  | Verify                                                | 249 |

| 11.3.2.8  | Tearing-Safe programming                              | 249 |

| 11.3.2.9  | Disturb handling                                      | 249 |

| 11.3.2.10 | ECC and EDC                                           | 249 |

| 11.3.2.11 | Resume from disturbed Program/Erase operation         | 250 |

| 11.3.2.12 | 2 Code and Data Access through the AHB-Lite Interface | 250 |

| 11.3.2.13 | B Prefetch Unit                                       | 250 |

| 11.4      | BootROM Module                                        | 251 |

| 11.4.1    | BootROM addressing                                    | 251 |

| 11.4.2    | BootROM firmware program structure                    | 251 |

| 11.5      | RAM Module                                            | 251 |

| 11.5.1    | RAM Addressing                                        | 251 |

| 11.6      | Memory Protection Unit (MPU)                          | 252 |

| 12        | Interrupt System                                      |     |

| 12.1      | Features                                              |     |

| 12.2      | Introduction                                          |     |

| 12.2.1    | Overview                                              |     |

| 12.3      | Functional Description                                |     |

| 12.3.1    | Interrupt Node Assignment                             |     |

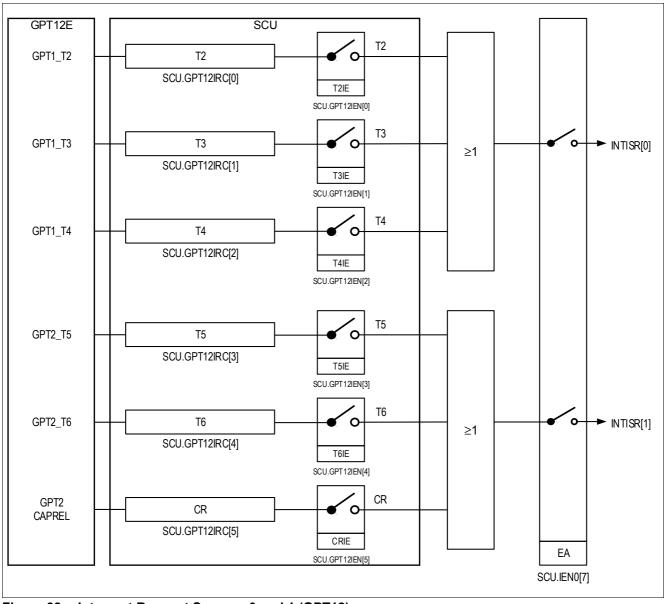

| 12.3.1.1  | Interrupt Node 0 and 1 - GPT12 Timer Module           |     |

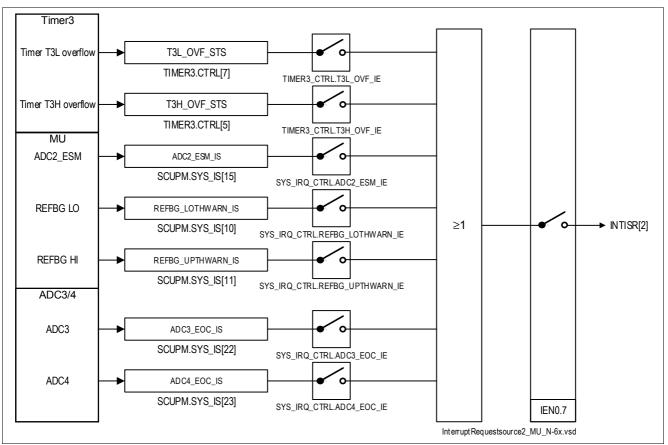

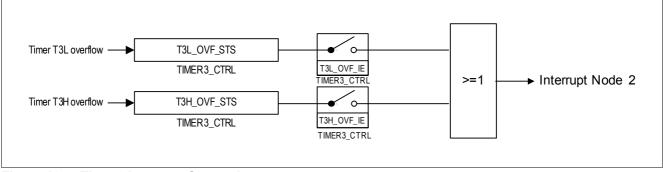

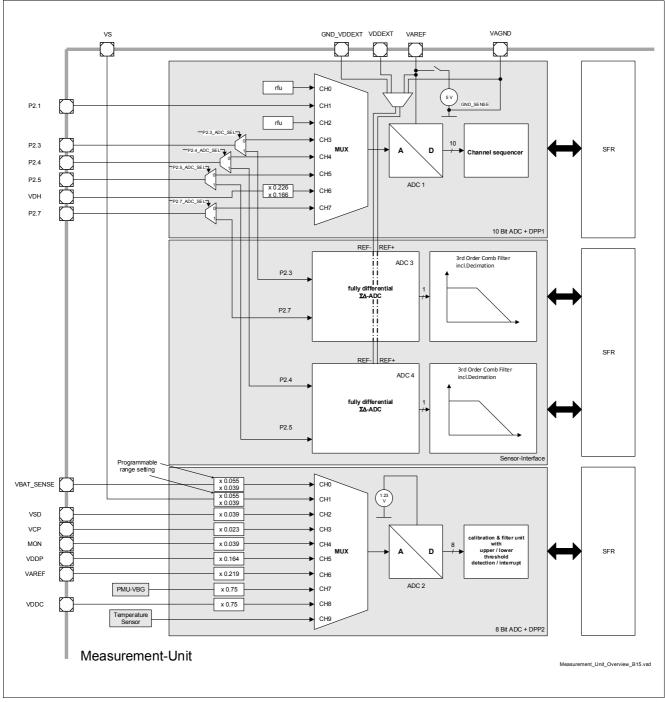

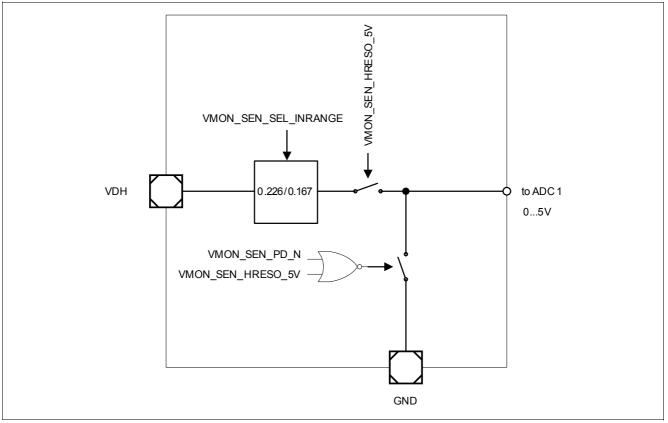

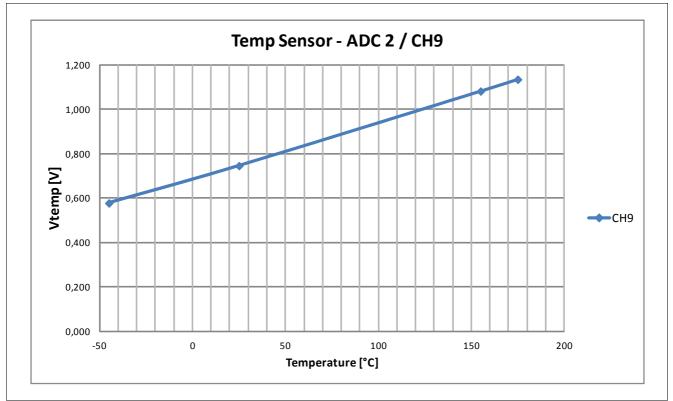

| 12.3.1.2  | Interrupt Node 2 - Measurement Unit                   |     |

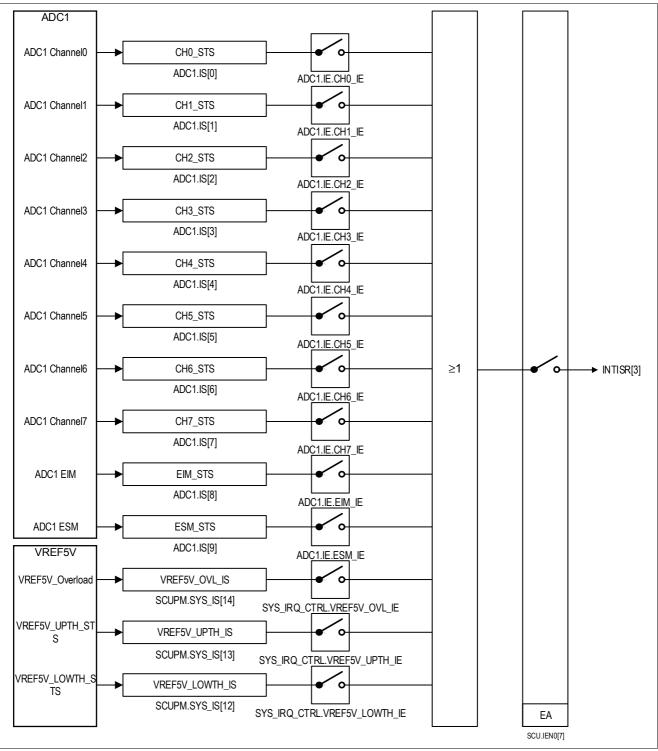

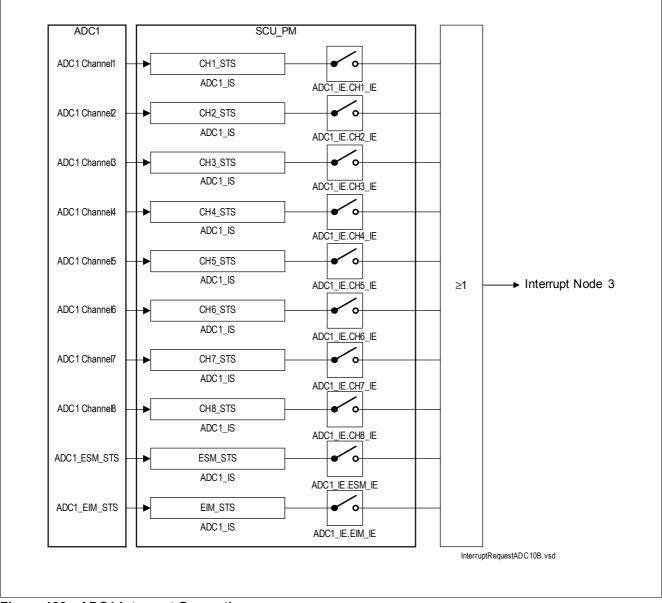

| 12.3.1.3  | Interrupt Node 3 - 10 Bit ADC (ADC1)                  |     |

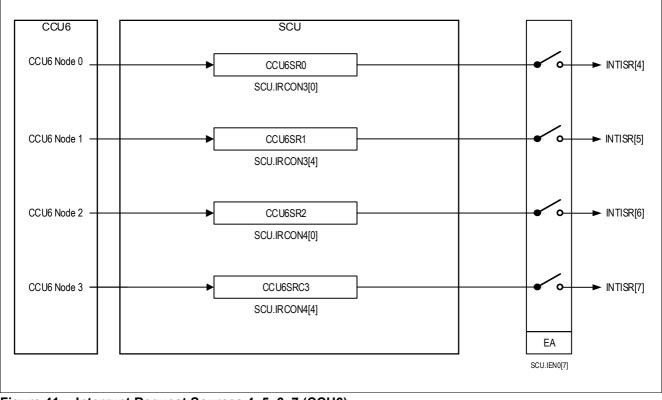

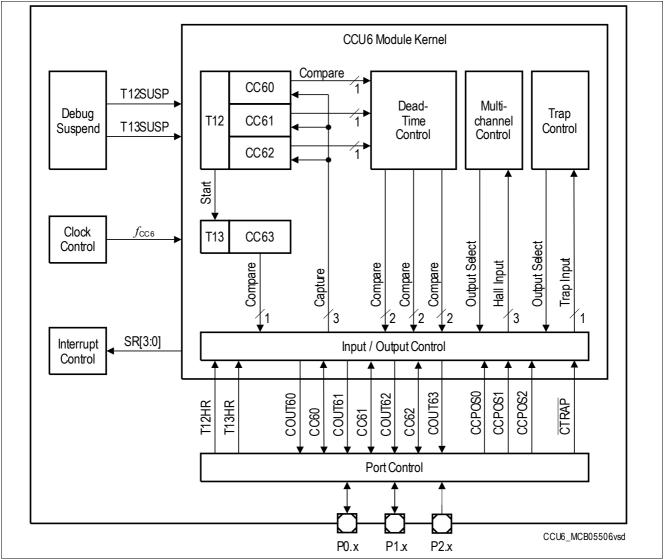

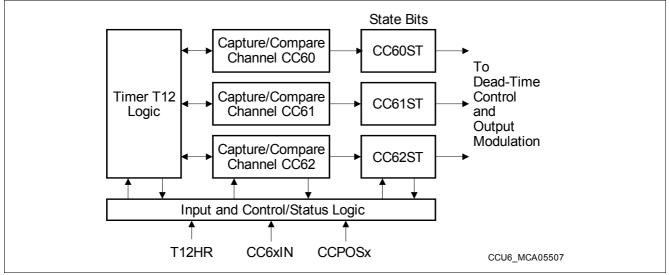

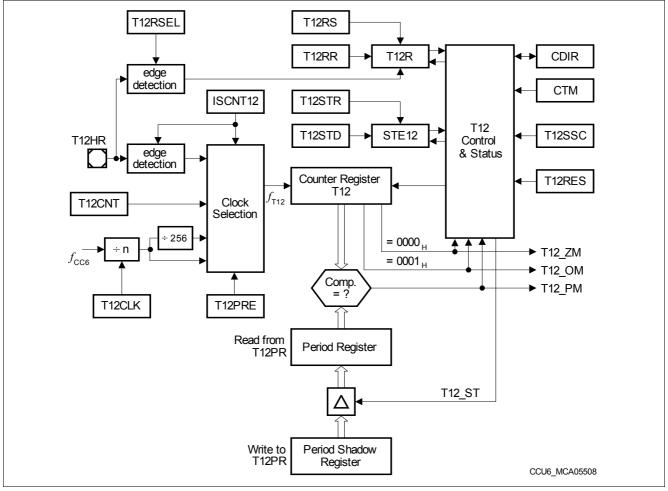

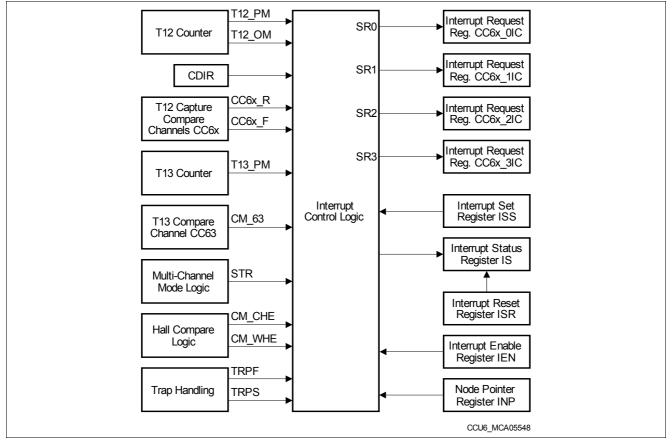

| 12.3.1.4  | Interrupt Nodes 4/5/6/7 - Capture Compare Unit (CCU6) |     |

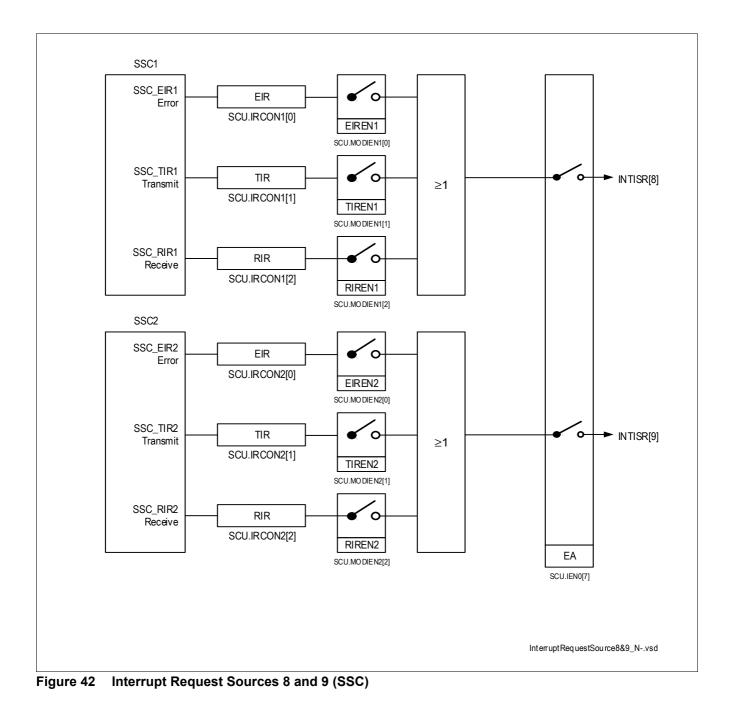

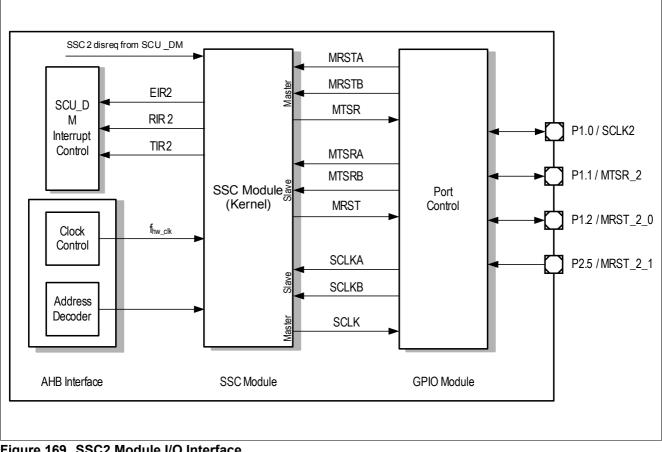

| 12.3.1.5  | Interrupt Node 8 and 9 - SSC1/SSC2                    |     |

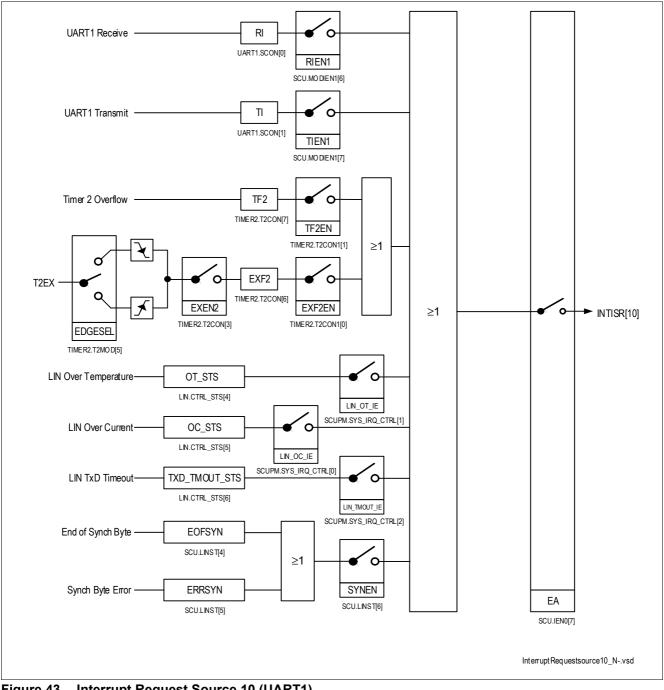

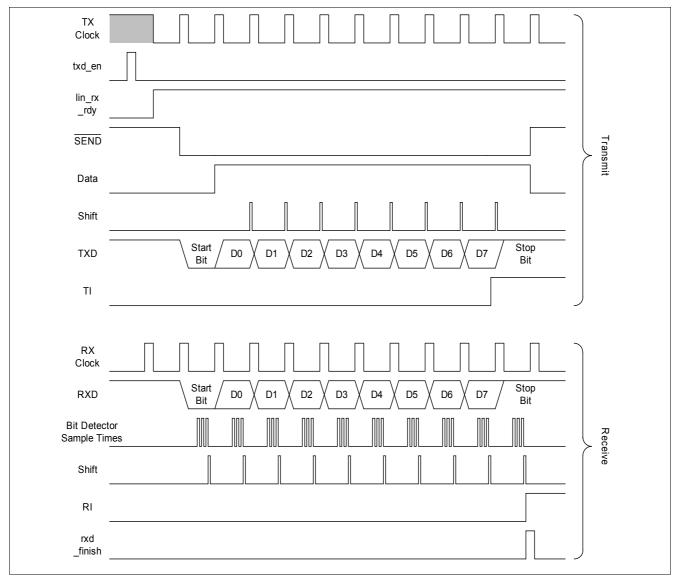

| 12.3.1.6  | Interrupt Node 10 - UART1/LIN Transceiver             |     |

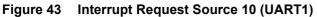

| 12.3.1.7  | Interrupt Node 11 - UART2                             |     |

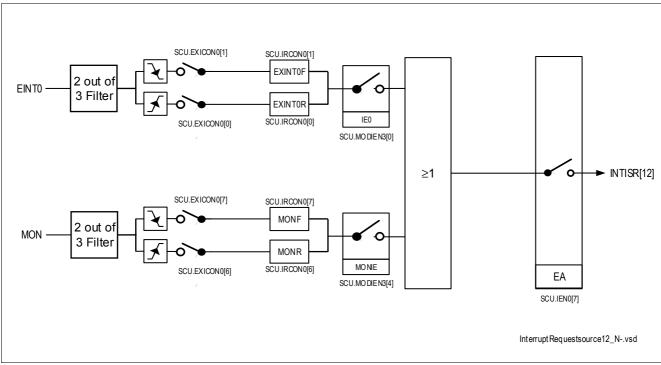

| 12.3.1.8  | Interrupt Node 12 - External Interrupt 0/MON          |     |

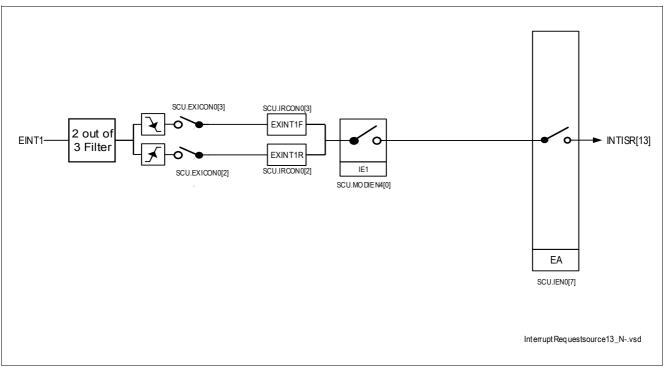

| 12.3.1.9  | Interrupt Node 13 - External Interrupt 1              |     |

| 12.3.1.10 |                                                       |     |

| 12.3.1.11 |                                                       |     |

| 12.3.1.12 |                                                       |     |

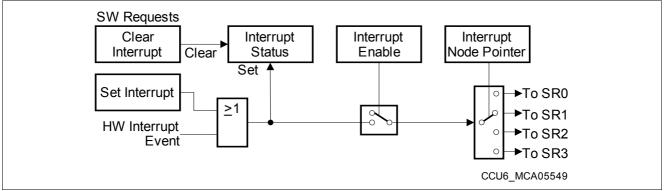

| 12.3.2    | Interrupt Structure                                   |     |

| 12.3.2.1  | Interrupt Structure 1                                 |     |

| 12.3.3    | Interrupt Source and Vector                           |     |

| 12.3.4    | Interrupt Priority                                    | 274 |

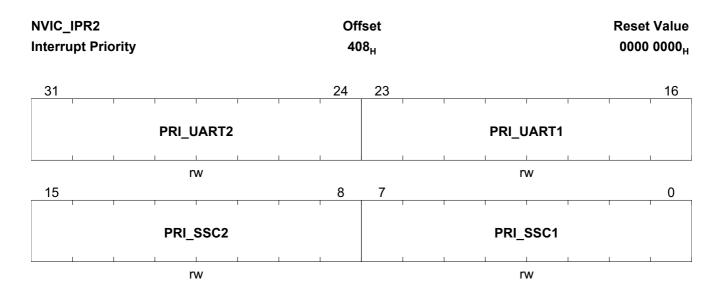

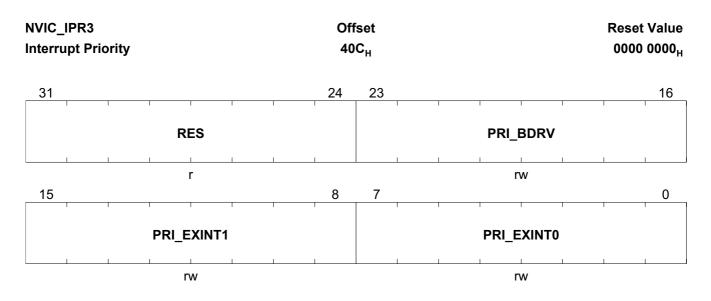

| 12.4<br>12.5<br>12.5.1<br>12.5.2<br>12.5.3<br>12.6 | Interrupt Handling<br>Register Definition<br>Interrupt Node Enable Registers<br>External Interrupt Control Registers<br>Interrupt Flag Registers<br>Interrupt Priority Registers | 276<br>276<br>278<br>280<br>290 |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

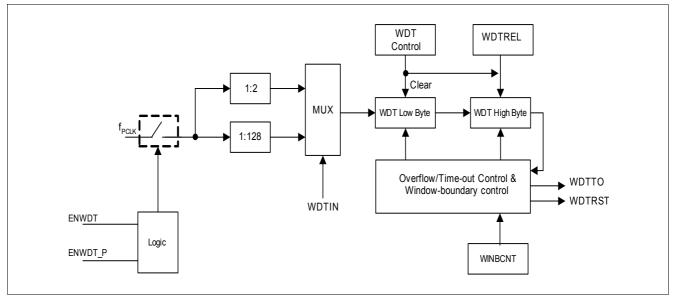

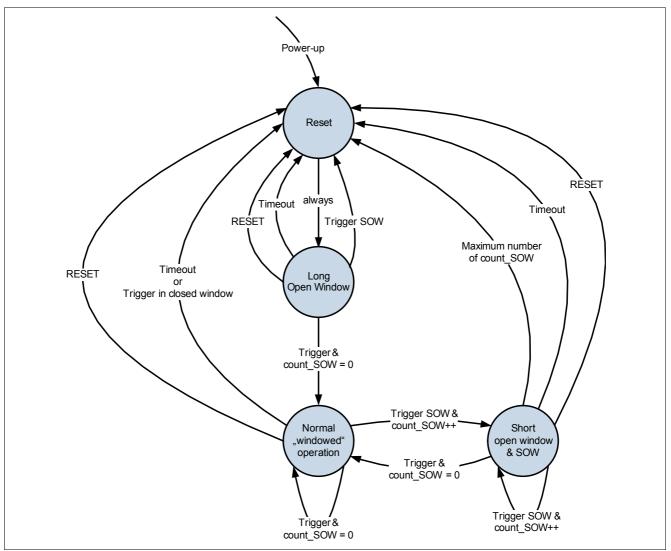

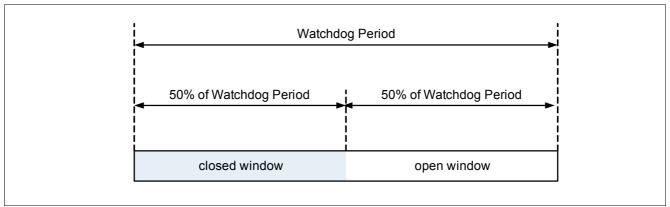

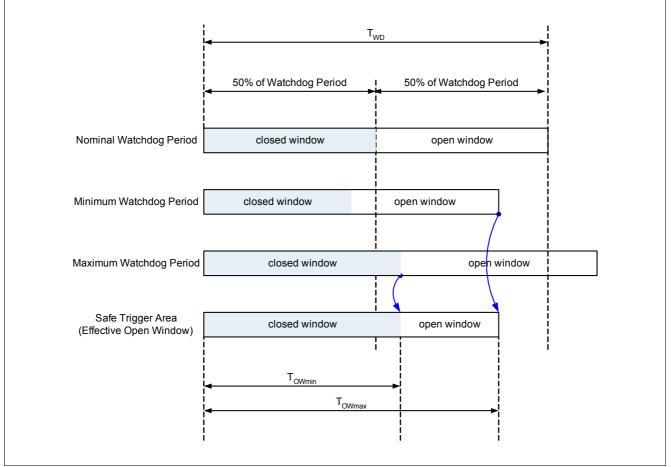

| 13                                                 | Watchdog Timer (WDT1)                                                                                                                                                            |                                 |

| 13.1                                               | Features                                                                                                                                                                         |                                 |

| 13.2                                               |                                                                                                                                                                                  |                                 |

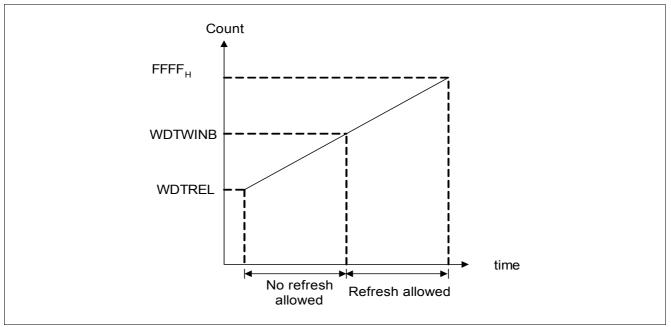

| 13.3                                               | Functional Description                                                                                                                                                           |                                 |

| 13.3.1                                             | Modes of Operation                                                                                                                                                               |                                 |

| 13.3.2                                             | Normal Operation                                                                                                                                                                 |                                 |

| 13.4                                               | Register Definition                                                                                                                                                              |                                 |

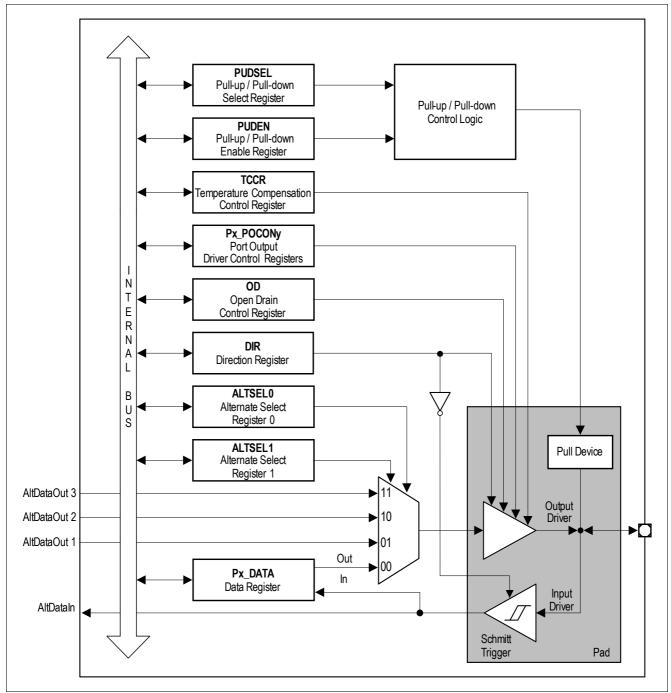

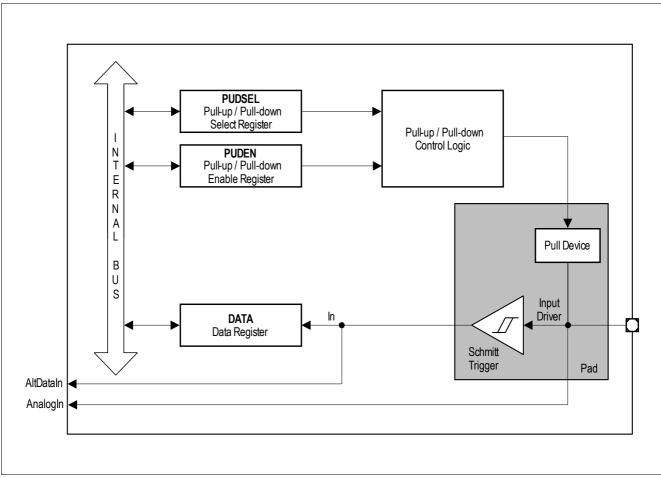

| 14                                                 | GPIO Ports and Peripheral I/O                                                                                                                                                    |                                 |

| 14.1                                               | Features                                                                                                                                                                         |                                 |

| 14.2                                               | Introduction                                                                                                                                                                     |                                 |

| 14.2.1                                             | Port 0 and Port 1                                                                                                                                                                |                                 |

| 14.2.2                                             | Port 2                                                                                                                                                                           |                                 |

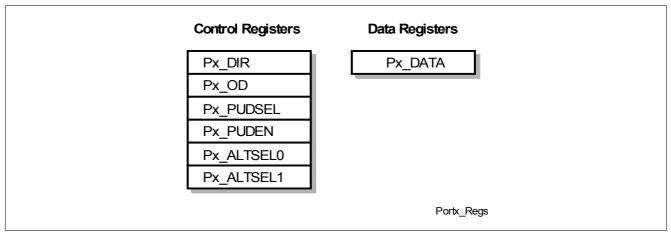

| 14.3<br>14.3.0.1                                   | General Port Register Description                                                                                                                                                |                                 |

| 14.3.0.1                                           | Port Data Register                                                                                                                                                               |                                 |

| 14.3.1                                             | Open Drain Control Register                                                                                                                                                      |                                 |

| 14.3.3                                             | Pull-Up/Pull-Down Device Register                                                                                                                                                |                                 |

| 14.3.3.1                                           | Alternate Input Functions                                                                                                                                                        |                                 |

| 14.3.4                                             | Alternate Output Functions                                                                                                                                                       |                                 |

| 14.3.5                                             | Register Map                                                                                                                                                                     |                                 |

| 14.4                                               | TLE9868QXB20 Port Module                                                                                                                                                         |                                 |

| 14.4.1                                             | Port 0                                                                                                                                                                           | 308                             |

| 14.4.1.1                                           | Overview                                                                                                                                                                         | 308                             |

| 14.4.1.2                                           | Port 0 Functions                                                                                                                                                                 | 308                             |

| 14.4.1.3                                           | Port 0 Register Description                                                                                                                                                      | 311                             |

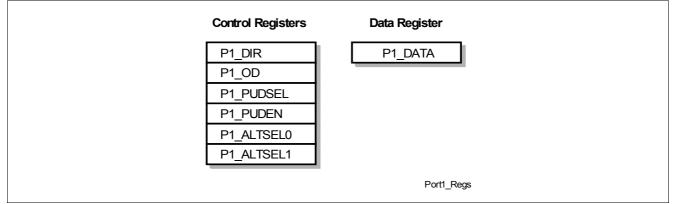

| 14.4.2                                             | Port 1                                                                                                                                                                           |                                 |

| 14.4.2.1                                           | Overview                                                                                                                                                                         |                                 |

| 14.4.2.2                                           | Port 1 Functions                                                                                                                                                                 | 314                             |

| 14.4.2.3                                           | Port 1 Register Description                                                                                                                                                      |                                 |

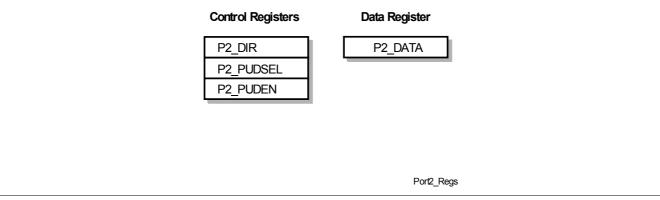

| 14.4.3<br>14.4.3.1                                 | Port 2 Overview                                                                                                                                                                  |                                 |

| 14.4.3.1                                           | Port 2 Functions                                                                                                                                                                 |                                 |

| 14.4.3.3                                           | Port 2 Register Description                                                                                                                                                      |                                 |

| 14.5                                               | Alternate Function Map                                                                                                                                                           |                                 |

|                                                    |                                                                                                                                                                                  |                                 |

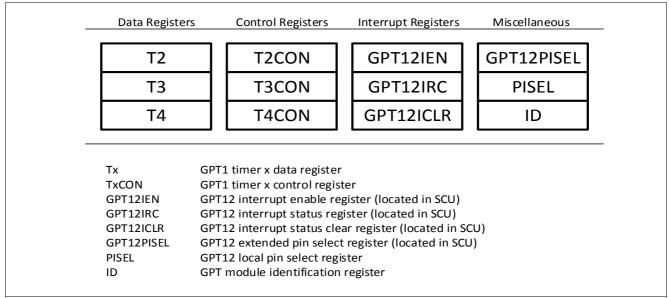

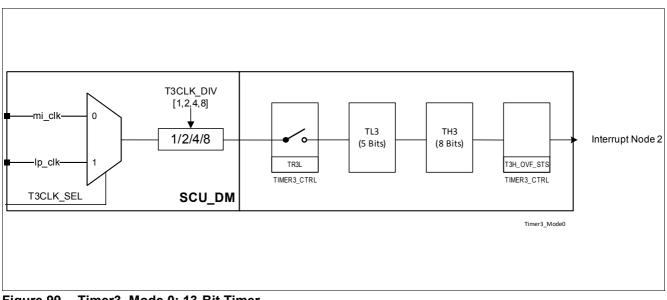

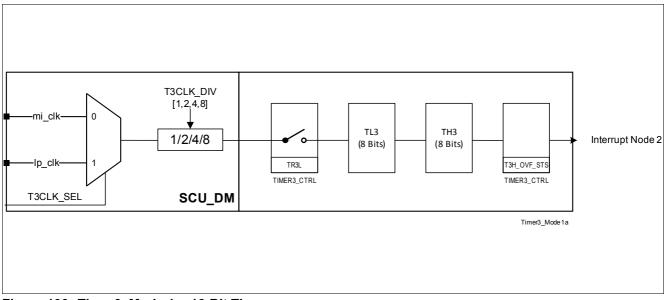

| 15                                                 | General Purpose Timer Units (GPT12)                                                                                                                                              |                                 |

| 15.1<br>15.1.1                                     | Features                                                                                                                                                                         |                                 |

| 15.1.2                                             | Features Block GPT2                                                                                                                                                              |                                 |

| 15.1.2                                             |                                                                                                                                                                                  |                                 |

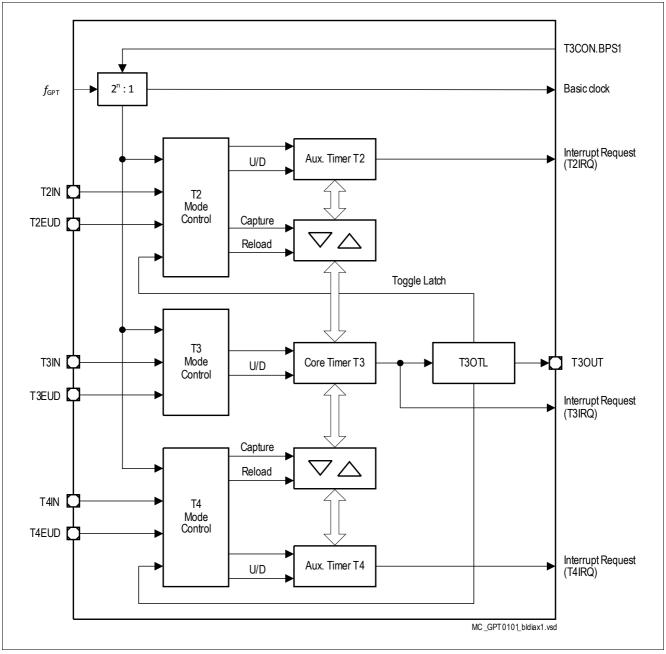

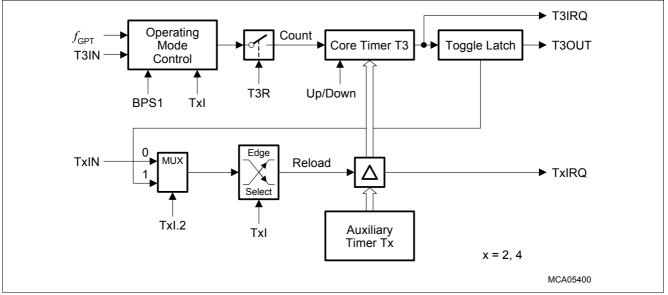

| 15.2.1                                             | Block Diagram GPT1                                                                                                                                                               |                                 |

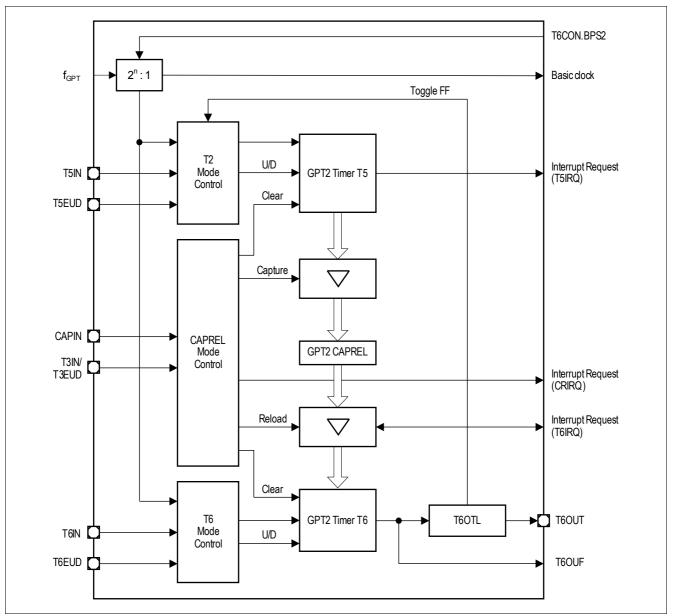

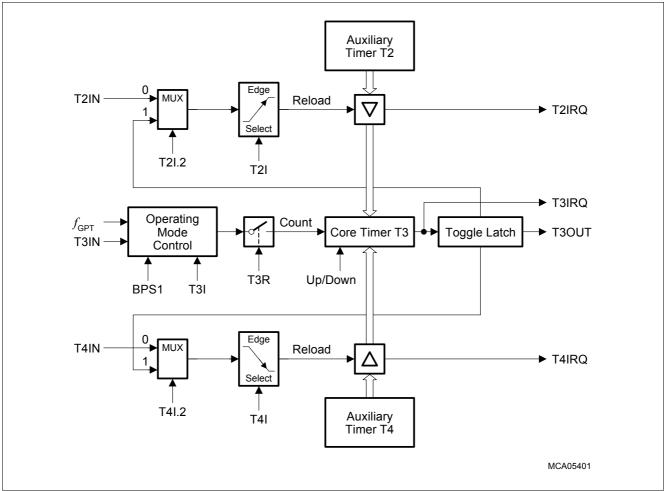

| 15.2.2                                             | Block Diagram GPT2                                                                                                                                                               | 328                             |

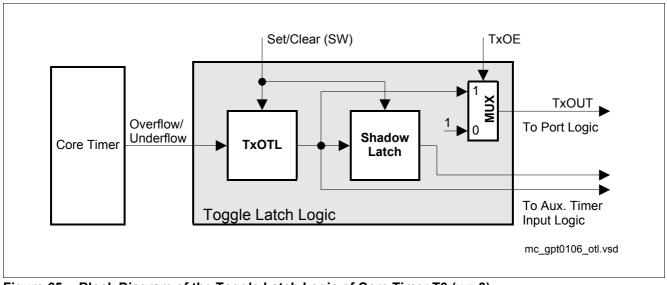

| 15.3                                               | Timer Block GPT1                                                                                                                                                                 |                                 |

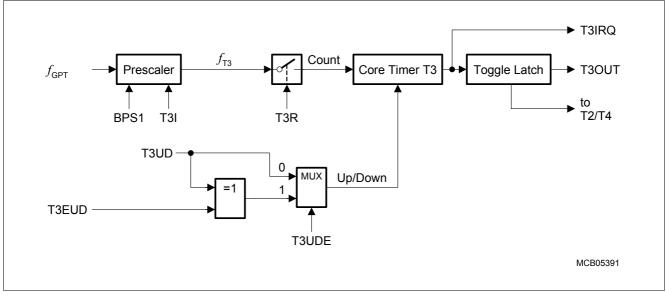

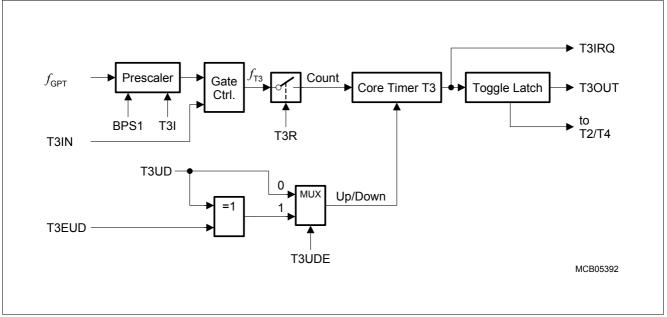

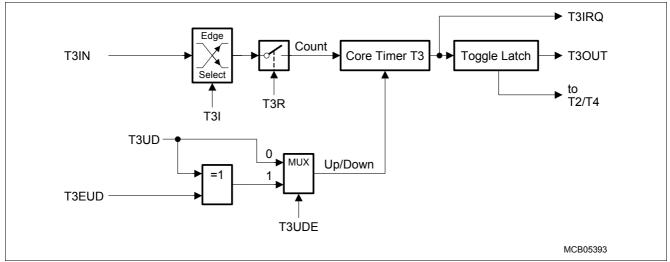

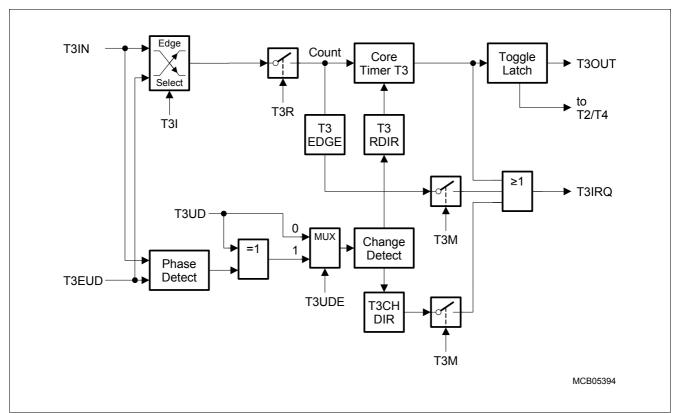

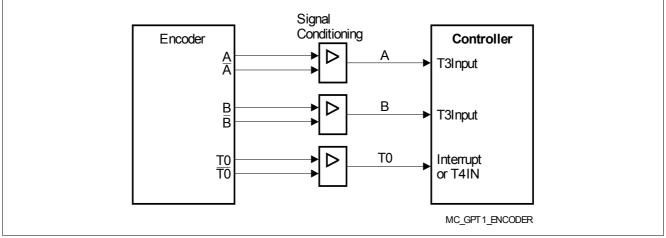

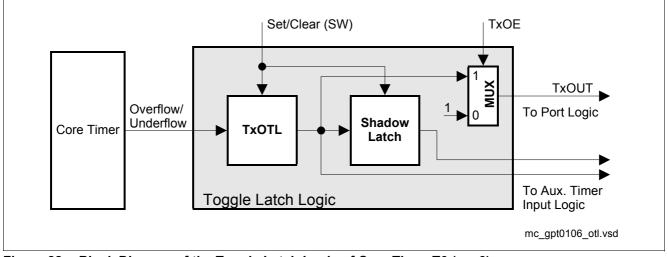

| 15.3.1                                             | GPT1 Core Timer T3 Control                                                                                                                                                       |                                 |

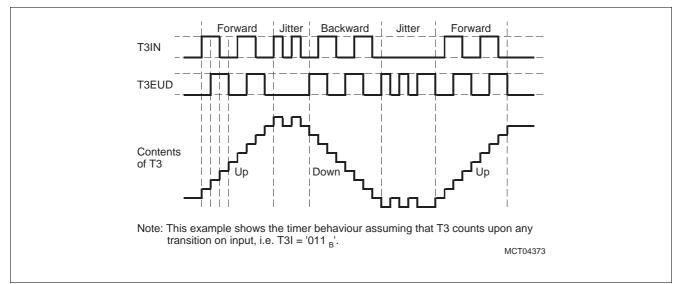

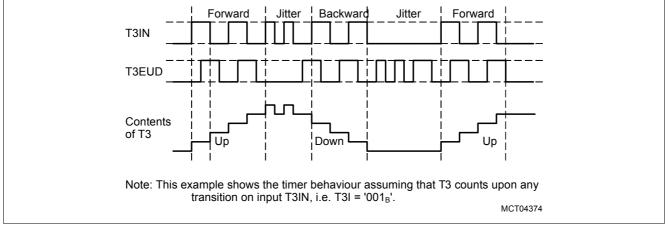

| 15.3.2                                             | GPT1 Core Timer T3 Operating Modes                                                                                                                                               |                                 |

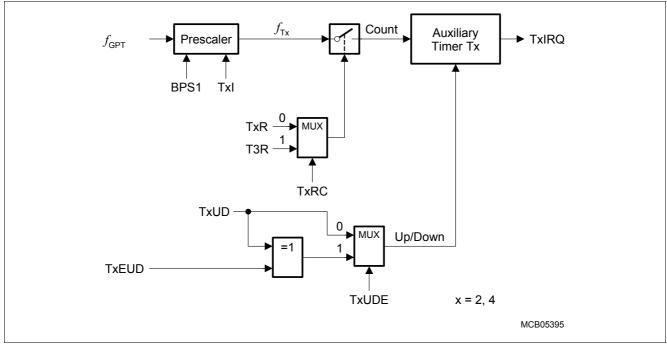

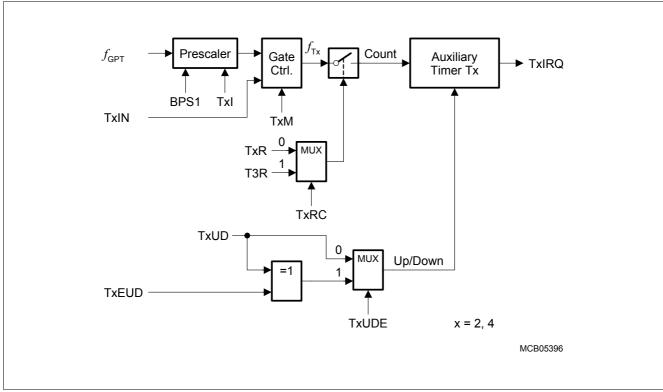

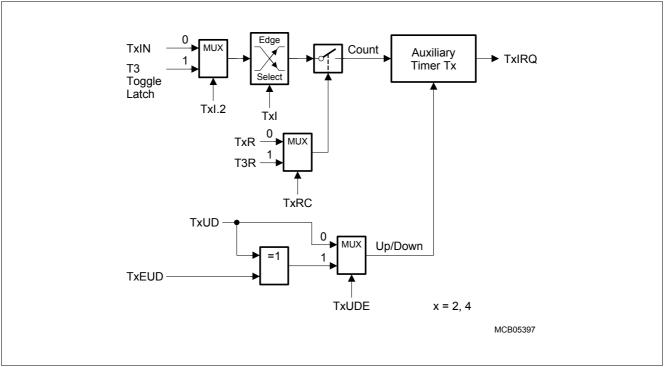

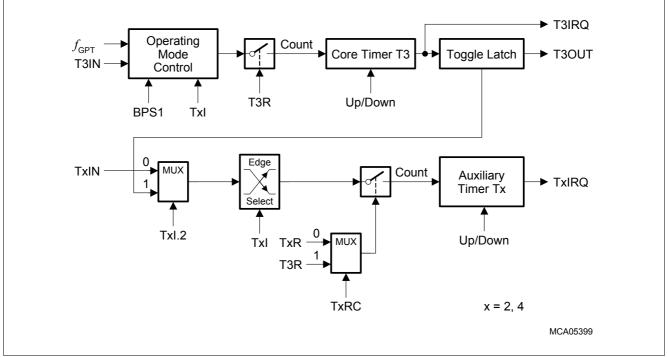

| 15.3.3                                                                                                                                                                                                                                | GPT1 Auxiliary Timers T2/T4 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

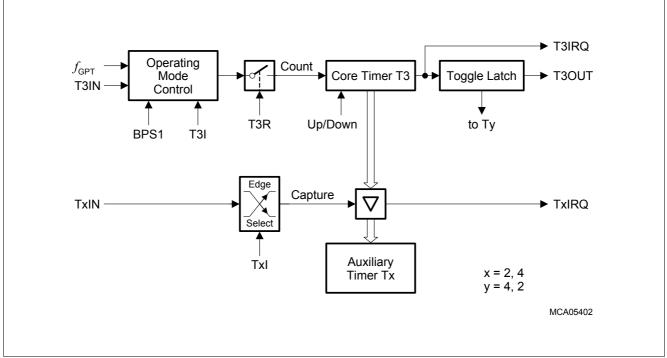

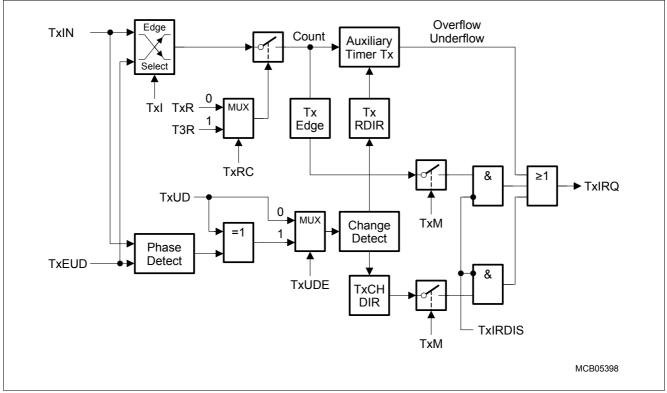

| 15.3.4                                                                                                                                                                                                                                | GPT1 Auxiliary Timers T2/T4 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |                                                                                                                                                               |

| 15.3.5                                                                                                                                                                                                                                | GPT1 Clock Signal Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                                                                                                                                               |

| 15.3.6                                                                                                                                                                                                                                | Interrupt Control for GPT1 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |                                                                                                                                                               |

| 15.3.7                                                                                                                                                                                                                                | GPT1 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |                                                                                                                                                               |

| 15.3.7.1                                                                                                                                                                                                                              | GPT1 Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |                                                                                                                                                               |

| 15.3.7.2                                                                                                                                                                                                                              | GPT1 Timer Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |                                                                                                                                                               |

| 15.3.7.3                                                                                                                                                                                                                              | GPT1 Timer Interrupt Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |                                                                                                                                                               |

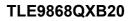

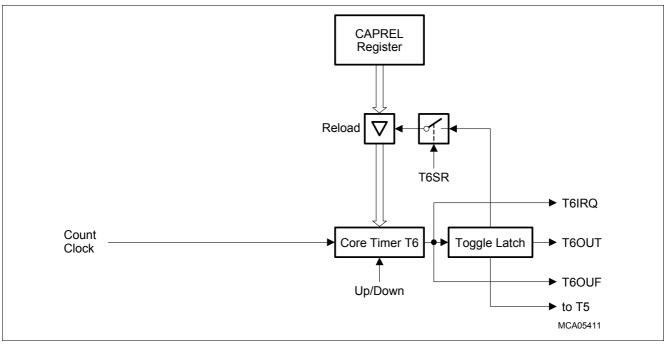

| 15.4                                                                                                                                                                                                                                  | Timer Block GPT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |                                                                                                                                                               |

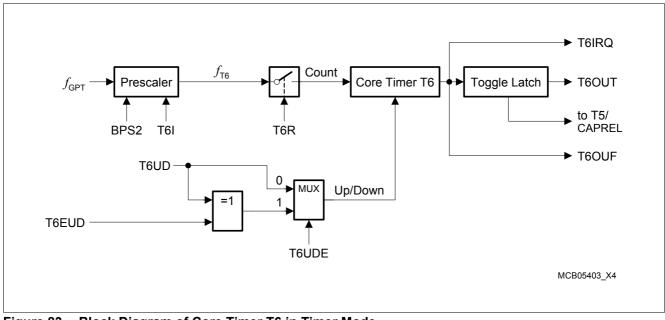

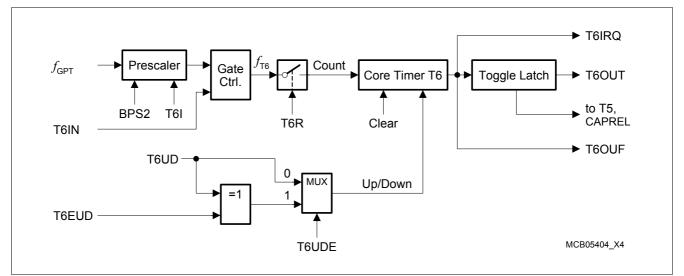

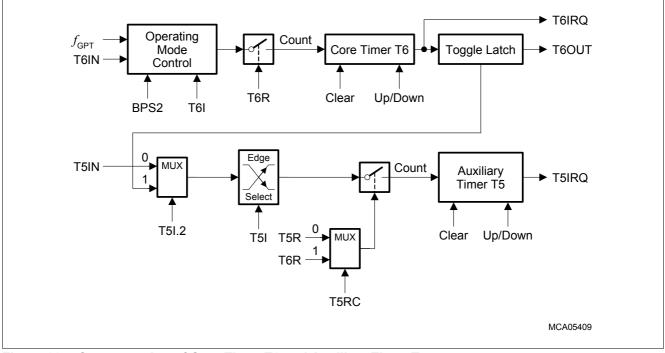

| 15.4.1                                                                                                                                                                                                                                | GPT2 Core Timer T6 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |                                                                                                                                                               |

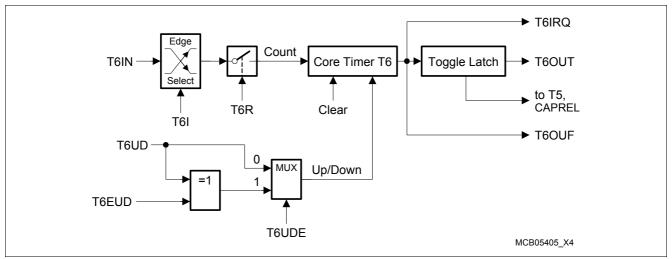

| 15.4.2                                                                                                                                                                                                                                | GPT2 Core Timer T6 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                                                                                                                                                               |

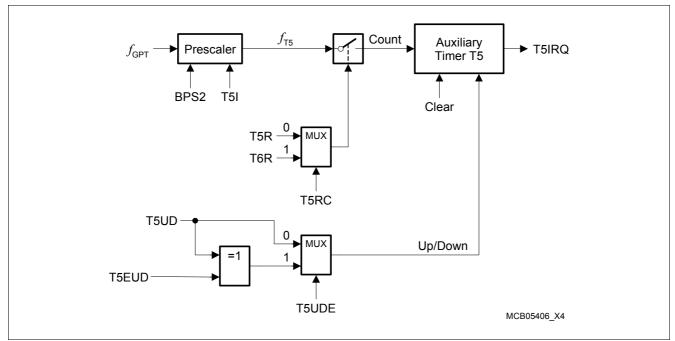

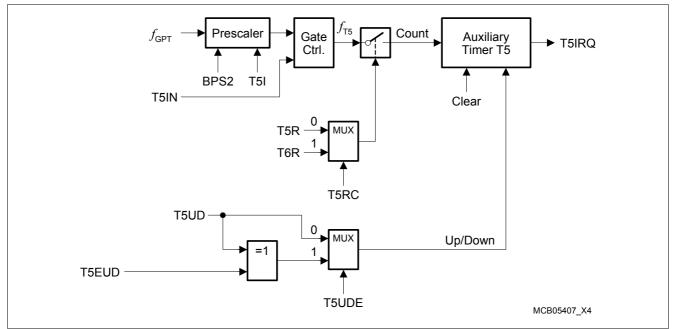

| 15.4.3                                                                                                                                                                                                                                | GPT2 Auxiliary Timer T5 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                                                                                                                                               |

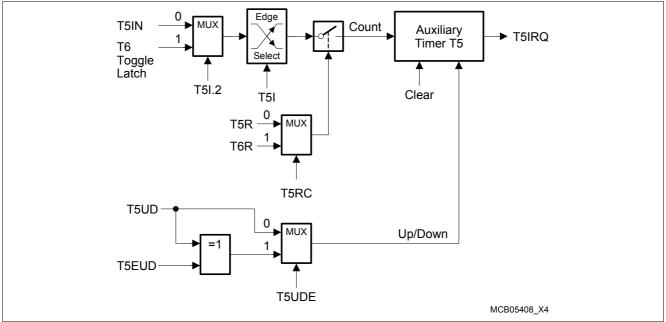

| 15.4.4                                                                                                                                                                                                                                | GPT2 Auxiliary Timer T5 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                                                                                                                                                               |

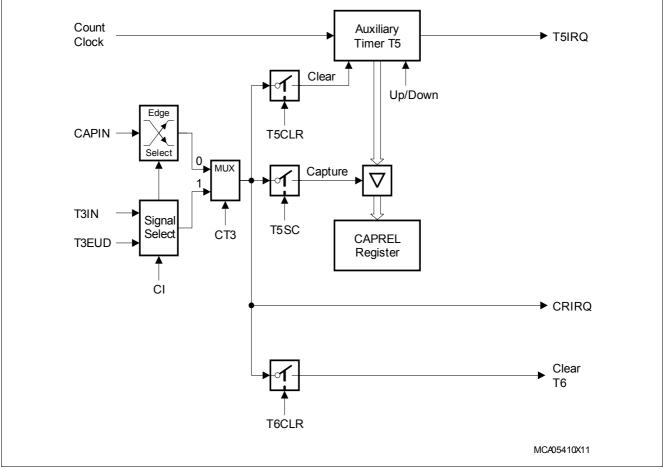

| 15.4.5                                                                                                                                                                                                                                | GPT2 Register CAPREL Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |                                                                                                                                                               |

| 15.4.6                                                                                                                                                                                                                                | GPT2 Clock Signal Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                                                                                                                                               |

| 15.4.7                                                                                                                                                                                                                                | Interrupt Control for GPT2 Timers and CAPREL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     | 378                                                                                                                                                           |

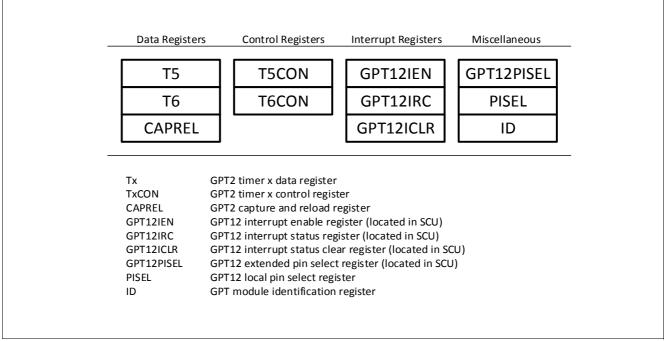

| 15.4.8                                                                                                                                                                                                                                | GPT2 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     | 379                                                                                                                                                           |

| 15.4.8.1                                                                                                                                                                                                                              | GPT2 Timer Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     | 379                                                                                                                                                           |

| 15.4.8.2                                                                                                                                                                                                                              | GPT2 Timer Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     | 380                                                                                                                                                           |

| 15.4.8.3                                                                                                                                                                                                                              | GPT2 Timer and CAPREL Interrupt Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     | 385                                                                                                                                                           |

| 15.5                                                                                                                                                                                                                                  | Miscellaneous GPT12 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     | 386                                                                                                                                                           |

| 15.6                                                                                                                                                                                                                                  | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     | 389                                                                                                                                                           |

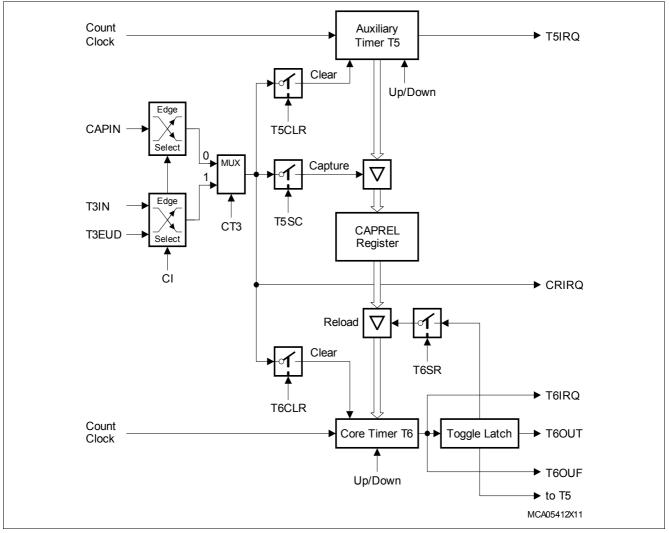

| 15.7                                                                                                                                                                                                                                  | Implementation of the GPT12 Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | 390                                                                                                                                                           |

| 15.7.1                                                                                                                                                                                                                                | Module Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | 390                                                                                                                                                           |

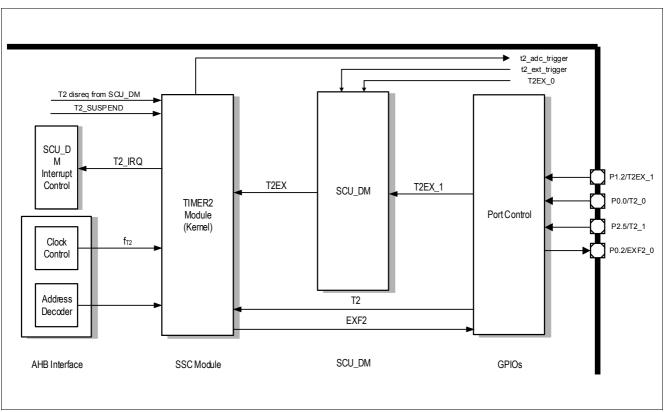

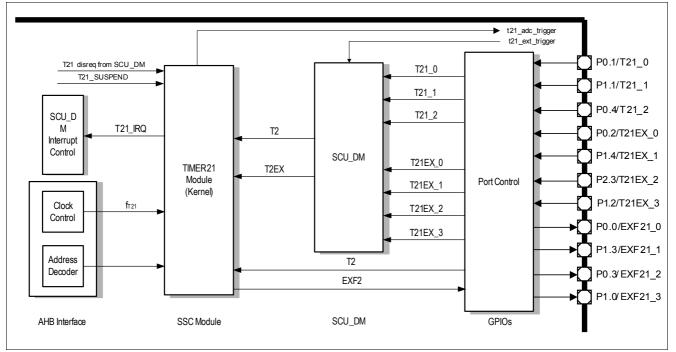

| 16                                                                                                                                                                                                                                    | Timer2 and Timer21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | 203                                                                                                                                                           |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                                                                                                                                               |

|                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |                                                                                                                                                               |

| 16.1                                                                                                                                                                                                                                  | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | 393                                                                                                                                                           |

| 16.1<br>16.2                                                                                                                                                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br>                                                | 393<br>393                                                                                                                                                    |

| 16.1<br>16.2<br>16.2.1                                                                                                                                                                                                                | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br><br>                                            | 393<br>393<br>393                                                                                                                                             |

| 16.1<br>16.2<br>16.2.1<br>16.3                                                                                                                                                                                                        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <br><br>                                            | 393<br>393<br>393<br>394                                                                                                                                      |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1                                                                                                                                                                                              | Features         Introduction         Timer2 and Timer21 Modes Overview         Functional Description         Auto-Reload Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <br><br><br>                                        | 393<br>393<br>393<br>394<br>394                                                                                                                               |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1                                                                                                                                                                                  | Features<br>Introduction<br>Timer2 and Timer21 Modes Overview<br>Functional Description<br>Auto-Reload Mode<br>Up/Down Count Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <br><br><br>                                        | 393<br>393<br>393<br>394<br>394<br>394                                                                                                                        |

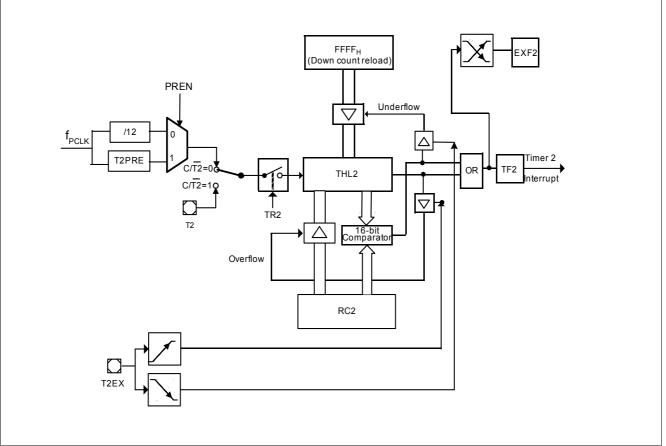

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2                                                                                                                                                                      | Features<br>Introduction .<br>Timer2 and Timer21 Modes Overview .<br>Functional Description .<br>Auto-Reload Mode .<br>Up/Down Count Disabled .<br>Up/Down Count Enabled .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | · · · ·<br>· · · ·<br>· · · ·                       | 393<br>393<br>393<br>394<br>394<br>394<br>394                                                                                                                 |

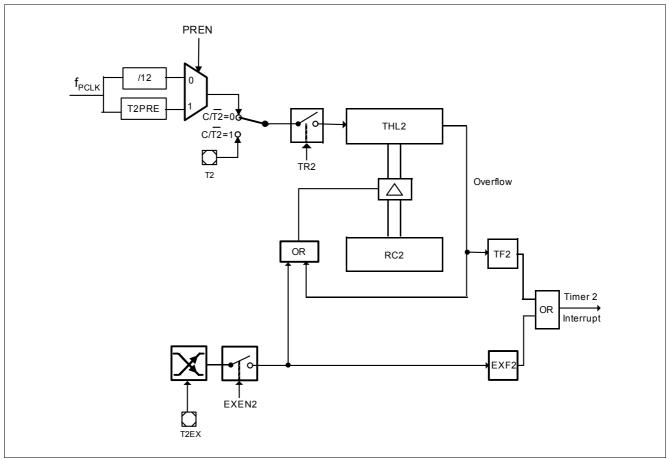

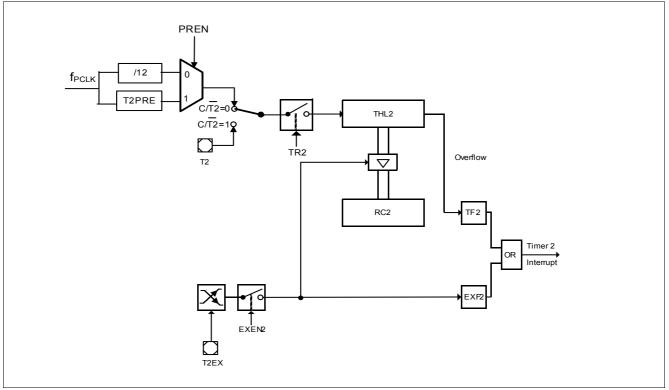

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2                                                                                                                                                            | Features .<br>Introduction .<br>Timer2 and Timer21 Modes Overview .<br>Functional Description .<br>Auto-Reload Mode .<br>Up/Down Count Disabled .<br>Up/Down Count Enabled .<br>Capture Mode .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · · · ·<br>· · · ·<br>· · · ·<br>· · · ·            | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397                                                                                                          |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3                                                                                                                                                  | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · · · ·<br>· · · ·<br>· · · ·<br>· · · ·            | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397<br>397                                                                                                   |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4                                                                                                                                          | Features<br>Introduction<br>Timer2 and Timer21 Modes Overview<br>Functional Description<br>Auto-Reload Mode<br>Up/Down Count Disabled<br>Up/Down Count Enabled<br>Capture Mode<br>Count Clock<br>Module Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                               | · · · ·<br>· · · ·<br>· · · ·<br>· · · ·<br>· · · · | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397<br>397<br>399                                                                                            |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1                                                                                                                                | Features<br>Introduction<br>Timer2 and Timer21 Modes Overview<br>Functional Description<br>Auto-Reload Mode<br>Up/Down Count Disabled<br>Up/Down Count Enabled<br>Capture Mode<br>Count Clock<br>Module Interfaces<br>Interfaces of the Timer2 and Timer21                                                                                                                                                                                                                                                                                                                                                                                                       | · · · · · · · · · · · · · · · · · · ·               | 393<br>393<br>394<br>394<br>394<br>396<br>397<br>397<br>399<br>399                                                                                            |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1<br>16.5                                                                                                                        | Features         Introduction         Timer2 and Timer21 Modes Overview         Functional Description         Auto-Reload Mode         Up/Down Count Disabled         Up/Down Count Enabled         Capture Mode         Count Clock         Module Interfaces         Interfaces of the Timer2 and Timer21                                                                                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · ·               | 393<br>393<br>394<br>394<br>394<br>396<br>397<br>397<br>399<br>399<br>400                                                                                     |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1<br>16.5<br>16.6                                                                                                                | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397<br>397<br>399<br>399<br>400<br>401                                                                       |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1<br>16.5<br>16.6<br>16.6.1                                                                                                      | Features .<br>Introduction .<br>Timer2 and Timer21 Modes Overview .<br>Functional Description .<br>Auto-Reload Mode .<br>Up/Down Count Disabled .<br>Up/Down Count Enabled .<br>Capture Mode .<br>Count Clock .<br>Module Interfaces .<br>Interfaces of the Timer2 and Timer21 .<br>Interrupt Generation .<br>Register Definition .<br>Timer 2 Registers .                                                                                                                                                                                                                                                                                                       |                                                     | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397<br>399<br>399<br>400<br>401<br>401                                                                       |

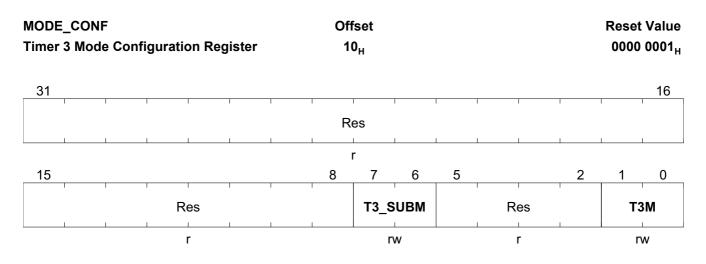

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1<br>16.5<br>16.6<br>16.6.1<br>16.6.1.1                                                                                          | Features .<br>Introduction .<br>Timer2 and Timer21 Modes Overview .<br>Functional Description .<br>Auto-Reload Mode .<br>Up/Down Count Disabled .<br>Up/Down Count Enabled .<br>Capture Mode .<br>Count Clock .<br>Module Interfaces .<br>Interfaces of the Timer2 and Timer21 .<br>Interrupt Generation .<br>Register Definition .<br>Timer 2 Registers .<br>Mode Register .                                                                                                                                                                                                                                                                                    |                                                     | 393<br>393<br>394<br>394<br>394<br>396<br>397<br>399<br>399<br>400<br>401<br>401<br>401                                                                       |

| 16.1<br>16.2<br>16.2.1<br>16.3<br>16.3.1<br>16.3.1.1<br>16.3.1.2<br>16.3.2<br>16.3.3<br>16.4<br>16.4.1<br>16.5<br>16.6<br>16.6.1<br>16.6.1.1<br>16.6.1.2                                                                              | Features<br>Introduction<br>Timer2 and Timer21 Modes Overview<br>Functional Description<br>Auto-Reload Mode<br>Up/Down Count Disabled<br>Up/Down Count Enabled<br>Capture Mode<br>Count Clock<br>Module Interfaces<br>Interfaces of the Timer2 and Timer21<br>Interrupt Generation<br>Register Definition<br>Timer 2 Registers<br>Mode Register<br>Control Register                                                                                                                                                                                                                                                                                              |                                                     | 393<br>393<br>394<br>394<br>394<br>394<br>397<br>397<br>399<br>399<br>400<br>401<br>401<br>401<br>402                                                         |

| $\begin{array}{c} 16.1 \\ 16.2 \\ 16.2.1 \\ 16.3 \\ 16.3.1 \\ 16.3.1.1 \\ 16.3.1.2 \\ 16.3.2 \\ 16.3.2 \\ 16.3.3 \\ 16.4 \\ 16.4.1 \\ 16.5 \\ 16.6 \\ 16.6.1 \\ 16.6.1.1 \\ 16.6.1.2 \\ 16.6.1.3 \end{array}$                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | 393<br>393<br>394<br>394<br>394<br>394<br>396<br>397<br>399<br>399<br>400<br>401<br>401<br>401<br>401<br>402<br>404                                           |