SGUS011D - APRIL 1991 - REVISED SEPTEMBER 2004

- Class B High-Reliability Processing

- 1-μm CMOS Technology

- Military Operating Temperature Range

-55°C to 125°C

- SMJ34020A-32/40 125/100-ns Instruction Cycle Time

- Fully Programmable 32-Bit General-Purpose Processor With 512-Megabyte Linear Address Range (Bit Addressable)

- Second-Generation Graphics System Processor

- Object-Code Compatible With the SMJ34010

- Enhanced Instruction Set

- Optimized Graphics Instructions

- Coprocessor Interface

- Pixel Processing, XY Addressing, and Window Checking Built Into the Instruction Set

- Programmable 1-, 2-, 4-, 8-, 16-, or 32-Bit Pixel Size With 16 Boolean and Six Arithmetic Pixel Processing Options (Raster Ops)

- 512-Byte LRU On-Chip Instruction Cache

- Optimized DRAM/VRAM Interface

- Page-Mode for Burst Memory Operations

- Dynamic Bus Sizing (16-Bit and 32-Bit Transfers)

- Byte-Oriented CAS Strobes

- Flexible Host Processor Interface

- Supports Host Transfers

- Direct Access to All of the SMJ34020A Address Space

- Implicit Addressing

- Prefetch for Enhanced Read Access

- Programmable CRT Control

- Composite Sync Mode

- Separate Sync Mode

- Synchronization to External Sync

- Direct Support for Special Features of 1M VRAMs

- Load Write Mask

- Load Color Mask

- Block Write

- Write Using the Write Mask

- Flexible Multi-Processor Interface

- Packaging Options

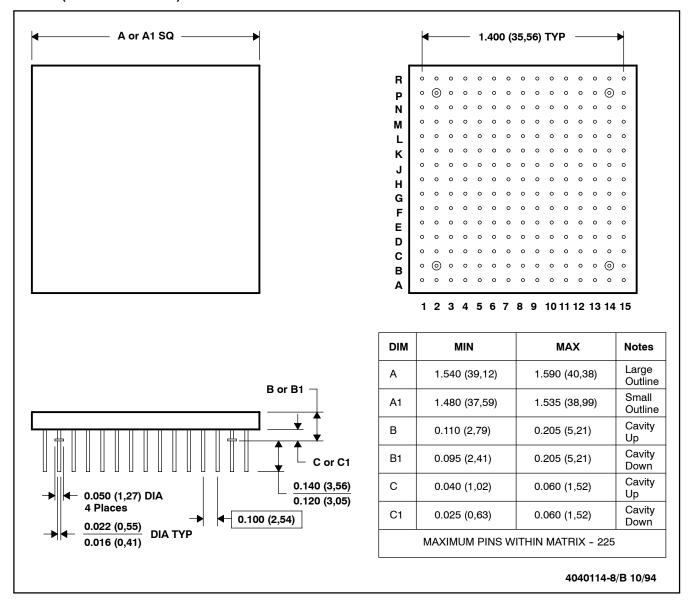

- 145-Pin Grid Array Ceramic Package (GB Suffix)

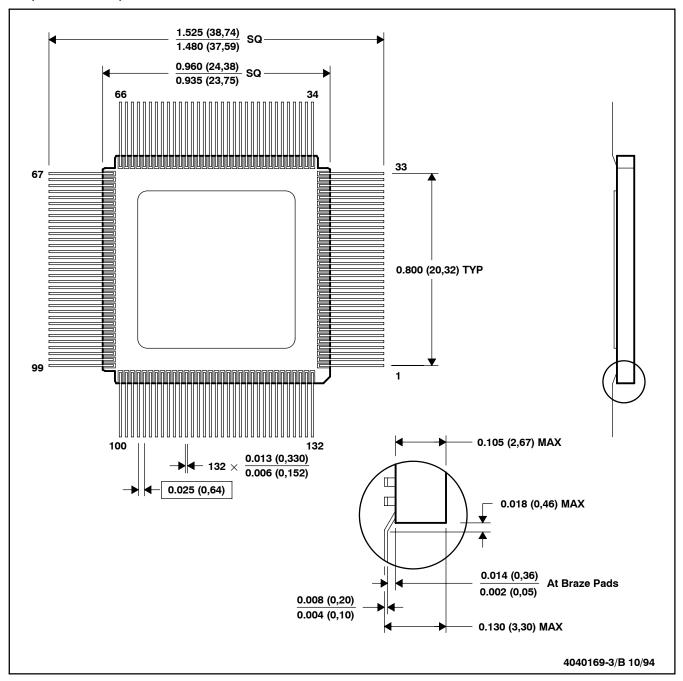

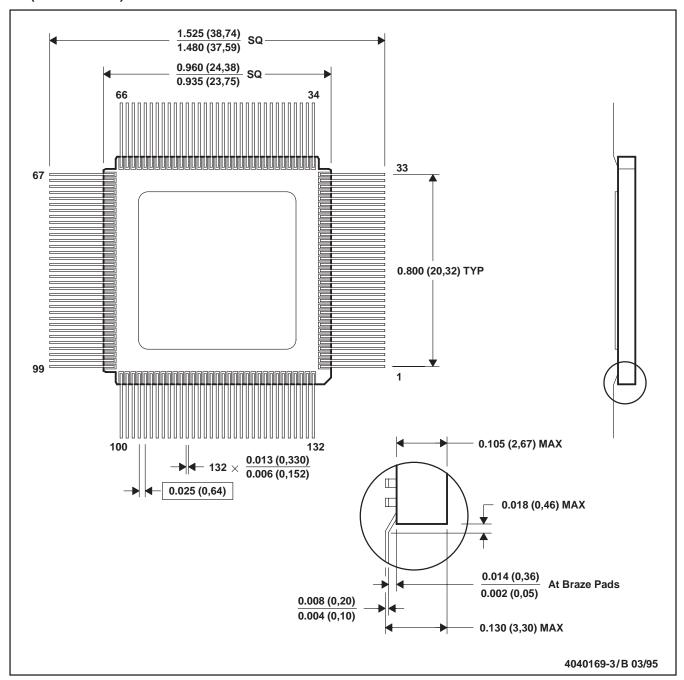

- 132-Pin Ceramic Quad Flat Pack (Unformed Lead) (HT Suffix)

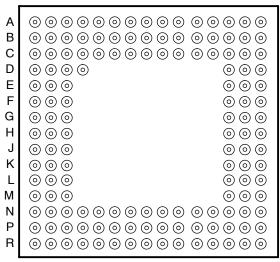

# 145-PIN GRID ARRAY PACKAGE (TOP VIEW)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

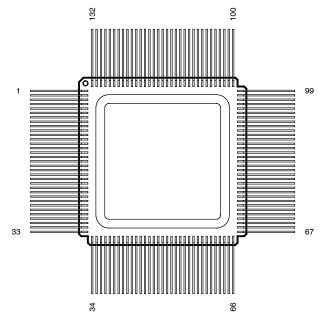

#### 132-PIN QUAD FLATPACK (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SGUS011D - APRIL 1991 - REVISED SEPTEMBER 2004

#### description

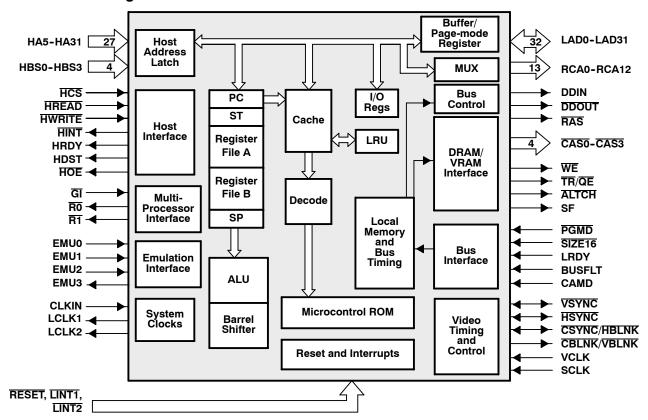

The SMJ34020A graphics system processor (GSP) is the second generation of an advanced high-performance CMOS 32-bit microprocessor optimized for graphics display systems. With a built-in instruction cache, the ability to simultaneously access memory and registers, and an instruction set designed to expedite raster graphics operations, the SMJ34020A provides user-programmable control of the CRT interface as well as the memory interface (both standard DRAM and multiport video RAM). The 4-gigabit (512-megabyte) physical address space is addressable on bit boundaries using variable width data fields (1 to 32 bits). Additional graphics addressing modes support 1-, 2-, 4-, 8-, 16- and 32-bit wide pixels.

#### architecture

The SMJ34020A is a CMOS 32-bit processor with hardware support for graphics operations such as pixel block transfers (PIXBLTS) during raster operations and curve-drawing algorithms. Also included is a complete set of general-purpose instructions with addressing modes tuned to support high-level languages. In addition to its ability to address a large external memory range, the SMJ34020A contains 30 general-purpose 32-bit registers, a hardware stack pointer, and a 512-byte instruction cache. On-chip functions include 64 programmable I/O registers that control CRT timing, input/output control, and parameters required by some instructions. The SMJ34020A directly interfaces to DRAMs and VRAMs and generates raster control signals. The SMJ34020A can be configured to operate as a standalone processor, or it can be used as a graphics engine with a host system. The host interface provides a generalized communication port for any standard host processor. The SMJ34020A also accommodates a multiprocessing or direct memory access (DMA) environment through the request/grant interface protocols. Virtual memory systems are supported through bus-fault detection and instruction continuation.

The SMJ34020A provides single-cycle execution of general-purpose instructions and most common integer arithmetic and Boolean operations from its instruction cache. Additionally, the SMJ34020A incorporates a hardware barrel shifter that provides a single-state bidirectional shift-and-rotate function for 1 to 32 bits.

The local-memory controller is designed to optimize memory access operations. It also supports pipeline memory write operations of variable-sized fields and allows memory access and instruction execution in parallel.

The SMJ34020A graphics-processing hardware supports pixel and pixel-array processing capabilities for both monochrome and color systems at a variety of pixel sizes. The hardware incorporates two-operand and three-operand raster operations with Boolean and arithmetic operations, XY addressing, window clipping, window-checking operations, 1 to *n* bits-per-pixel transforms, transparency, and plane masking. The architecture further supports operations on single pixel transfer (PIXT) instructions or on two-dimensional arrays of arbitrary size (PIXBLTS).

The SMJ34020A's flexible graphics-processing capabilities allow software-based graphics algorithms without sacrificing performance. These algorithms include clipping to arbitrary window size, custom incremental-curve drawing, two-operand raster operations, and masked two-operand raster operations.

The SMJ34020A provides for extensions to the basic architecture through the coprocessor interface. Special instructions and cycle timings are included to enhance data flow to coprocessors without requiring the coprocessor to decode the instruction stream, generate system addresses, or move data for the coprocessor through the SMJ34020A.

# Pin Assignments - 145-Pin Grid Array Package

|        | PIN             | PI              | N               | PI     | N               | PIN    |                 |  |

|--------|-----------------|-----------------|-----------------|--------|-----------------|--------|-----------------|--|

| NUMBER | NAME            | NUMBER          | NAME            | NUMBER | NAME            | NUMBER | NAME            |  |

| A1     | V <sub>SS</sub> | C9              | RCA8            | J1     | EMU0            | N15    | LAD17           |  |

| A2     | ALTCH           | C10             | RCA12           | J2     | GI              | P1     | V <sub>CC</sub> |  |

| A3     | CBLNK/VBLNK     | C11             | LAD30           | J3     | EMU1            | P2     | HWRITE          |  |

| A4     | HSYNC           | C12             | V <sub>SS</sub> | J13    | LAD4            | P3     | HCS             |  |

| A5     | TR/QE           | C13             | V <sub>SS</sub> | J14    | V <sub>CC</sub> | P4     | HA30            |  |

| A6     | RCA2            | C14             | V <sub>CC</sub> | J15    | LAD5            | P5     | HA27            |  |

| A7     | RCA3            | C15             | LAD26           | K1     | EMU2            | P6     | HA24            |  |

| A8     | V <sub>CC</sub> | D1              | RAS             | K2     | RESET           | P7     | HA22            |  |

| A9     | RCA6            | D2              | CAS2            | КЗ     | LINT2           | P8     | HA18            |  |

| A10    | RCA7            | D3              | V <sub>SS</sub> | K13    | V <sub>SS</sub> | P9     | HA14            |  |

| A11    | RCA10           | D4 <sup>†</sup> | NU <sup>†</sup> | K14    | LAD3            | P10    | HA13            |  |

| A12    | SCLK            | D13             | LAD28           | K15    | LAD20           | P11    | HA10            |  |

| A13    | LAD15           | D14             | LAD11           | L1     | LINT1           | P12    | HA7             |  |

| A14    | LAD29           | D15             | LAD10           | L2     | CAMD            | P13    | HA5             |  |

| A15    | V <sub>SS</sub> | E1              | R1              | L3     | LRDY            | P14    | HBS0            |  |

| B1     | CAS3            | E2              | V <sub>CC</sub> | L13    | LAD1            | P15    | LAD0            |  |

| B2     | WE              | E3              | CAS1            | L14    | LAD2            | R1     | HREAD           |  |

| В3     | V <sub>SS</sub> | E13             | LAD27           | L15    | LAD19           | R2     | HA31            |  |

| B4     | CSYNC/HBLNK     | E14             | LAD25           | M1     | BUSFLT          | R3     | HA28            |  |

| B5     | VSYNC           | E15             | LAD9            | M2     | PGMD            | R4     | HA26            |  |

| B6     | RCA0            | F1              | HRDY            | МЗ     | VCLK            | R5     | HA23            |  |

| B7     | RCA1            | F2              | R0              | M13    | V <sub>SS</sub> | R6     | HA20            |  |

| B8     | RCA5            | F3              | V <sub>SS</sub> | M14    | LAD16           | R7     | HA19            |  |

| В9     | RCA9            | F13             | LAD24           | M15    | LAD18           | R8     | HA17            |  |

| B10    | RCA11           | F14             | LAD8            | N1     | SIZE16          | R9     | HA16            |  |

| B11    | LAD31           | F15             | V <sub>SS</sub> | N2     | V <sub>CC</sub> | R10    | HA15            |  |

| B12    | LAD14           | G1              | HINT            | N3     | CLKIN           | R11    | HA11            |  |

| B13    | V <sub>CC</sub> | G2              | HOE             | N4     | V <sub>SS</sub> | R12    | HA9             |  |

| B14    | LAD13           | G3              | HDST            | N5     | HA29            | R13    | HA8             |  |

| B15    | LAD12           | G13             | LAD7            | N6     | HA25            | R14    | HBS3            |  |

| C1     | CAS0            | G14             | V <sub>SS</sub> | N7     | HA21            | R15    | V <sub>SS</sub> |  |

| C2     | V <sub>CC</sub> | G15             | LAD23           | N8     | V <sub>SS</sub> |        |                 |  |

| C3     | DDOUT           | H1              | LCLK1           | N9     | V <sub>SS</sub> |        |                 |  |

| C4     | DDIN            | H2              | EMU3            | N10    | HA12            |        |                 |  |

| C5     | V <sub>SS</sub> | H3              | LCLK2           | N11    | HA6             |        |                 |  |

| C6     | SF              | H13             | LAD22           | N12    | HBS2            |        |                 |  |

| C7     | RCA4            | H14             | LAD21           | N13    | HBS1            |        |                 |  |

| C8     | V <sub>SS</sub> | H15             | LAD6            | N14    | V <sub>CC</sub> |        |                 |  |

This pin is provided for device orientation purpose only. Make no external connection.

# SMJ34020A GRAPHICS SYSTEM PROCESSOR

SGUS011D - APRIL 1991 - REVISED SEPTEMBER 2004

# Pin Assignments - 132-Pin Ceramic Quad Flatpack Package

| NUMBER   NAME   NUMBER   NAME   NAME   NAME   NAME   NAME   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Р      | IN              | PII    | N        | PI     | N               |        | PIN             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|--------|----------|--------|-----------------|--------|-----------------|

| 2         CAS2         35         HA31         68         LAD16         101         LAD14           3         CAST         36         HA30         69         LAD1         102         LAD30           4         CAST         36         HA29         70         LAD17         103         LAD15           5         VCC         38         HA28         71         LAD2         104         LAD31           6         RAS         39         HA27         72         LAD18         105         SCLK           7         VSS         40         HA26         73         VSS         106         RCA12           8         RO         41         HA26         73         VSS         106         RCA12           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         VCC         109         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA                                                                                                                                                          | NUMBER | NAME            | NUMBER | NAME     | NUMBER | NAME            | NUMBER | NAME            |

| 3         CAST         36         HA30         69         LAD1         102         LAD30           4         CASS         37         HA29         70         LAD17         103         LAD15           5         V <sub>CC</sub> 38         HA28         71         LAD2         104         LAD31           6         RAS         39         HA27         72         LAD18         105         SCLK           7         VSS         40         HA26         73         VSS         106         RCA12           8         RO         41         HA25         74         LAD3         107         RCA11           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA6           14         EMU3         47         HA19         80         LAD21         113         <                                                                                                                                                   | 1      | CAS3            | 34     | HCS      | 67     | LAD0            | 100    | LAD29           |

| 4         CASO         37         HA29         70         LAD17         103         LAD15           5         V <sub>CC</sub> 38         HA28         71         LAD2         104         LAD31           6         RAS         39         HA27         72         LAD18         105         SCLK           7         V <sub>SS</sub> 40         HA26         73         V <sub>SS</sub> 106         RCA12           8         RG         41         HA26         73         V <sub>SS</sub> 106         RCA12           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           11         HOST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA6           13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113                                                                                                                                                  | 2      | CAS2            | 35     | HA31     | 68     | 68 LAD16        |        | LAD14           |

| 5         V <sub>CC</sub> 38         HA28         71         LAD2         104         LAD31           6         RAS         39         HA27         72         LAD18         105         SCLK           7         VSS         40         HA26         73         VSS         106         RCA12           8         RO         41         HA26         73         VSS         106         RCA12           8         RO         41         HA26         74         LAD3         107         RCA11           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA9           12         HRDY         45         HA21         78         LAD20         111         RCA                                                                                                                                                      | 3      | CAS1            | 36     | HA30     | 69     | LAD1            | 102    | LAD30           |

| 6 RAS 39 HA27 72 LAD18 105 SCLK 7 V <sub>SS</sub> 40 HA26 73 V <sub>SS</sub> 106 RCA12 8 R\( \overline{\text{R}} \) 41 HA25 74 LAD3 107 RCA11 9 R\( \overline{\text{T}} \) 42 HA24 75 LAD19 108 RCA9 110 HOE 43 HA23 76 V <sub>CC</sub> 109 RCA9 111 HDST 44 HA22 77 LAD4 110 RCA8 12 HRDY 45 HA21 78 LAD20 111 RCA7 13 HINT 46 HA20 79 LAD5 112 RCA6 14 EMU3 47 HA19 80 LAD21 113 RCA5 15 LCLK1 48 HA18 81 LAD6 114 V <sub>CC</sub> 16 LCLK2 49 HA17 82 LAD22 115 V <sub>SS</sub> 17 EMU1 50 V <sub>SS</sub> 83 LAD7 116 RCA4 18 EMU0 51 HA16 84 LAD23 117 RCA3 19 EMU2 52 HA15 85 V <sub>SS</sub> 118 RCA2 20 GI 53 HA14 86 V <sub>SS</sub> 119 RCA1 21 RESET 54 HA13 87 LAD8 120 RCA1 21 RESET 54 HA13 87 LAD8 120 RCA1 22 LINT2 55 HA12 88 LAD24 121 SF 23 LINT1 56 HA11 89 LAD9 122 TR/QE 24 CAMD 57 HA10 90 LAD25 123 VSYNC 25 BUSFLT 58 HA9 91 LAD10 124 HSYNC 26 SIZE16 59 HA8 92 LAD26 125 CEINK/VELNK 27 PGMD 60 HA7 93 LAD11 126 CSYNC/PELNK 28 LRDY 61 HA6 94 LAD27 127 V <sub>SS</sub> 30 VCLK 63 HBS3 96 LAD12 129 ALTCH 31 CLKIN 64 HBS2 97 LAD28 130 DDIN 32 HWRITE 65 HBS1 98 V <sub>SS</sub> 131 DDOUT                                                                                                                                                | 4      | CAS0            | 37     | HA29     | 70     | LAD17           | 103    | LAD15           |

| 7         V <sub>SS</sub> 40         HA26         73         V <sub>SS</sub> 106         RCA12           8         R0         41         HA25         74         LAD3         107         RCA11           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           111         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115                                                                                                                                                 | 5      | V <sub>CC</sub> | 38     | HA28     | 71     | LAD2            | 104    | LAD31           |

| 8         R0         41         HA25         74         LAD3         107         RCA11           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA6           13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117                                                                                                                                                     | 6      | RAS             | 39     | HA27     | 72     | LAD18           | 105    | SCLK            |

| 8         R0         41         HA25         74         LAD3         107         RCA11           9         RT         42         HA24         75         LAD19         108         RCA10           10         HOE         43         HA23         76         V <sub>CC</sub> 109         RCA9           11         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA6           13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117                                                                                                                                                     | 7      | $V_{SS}$        | 40     | HA26     | 73     | $V_{SS}$        | 106    | RCA12           |

| 10   HOE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8      |                 | 41     | HA25     | 74     |                 | 107    | RCA11           |

| 11         HDST         44         HA22         77         LAD4         110         RCA8           12         HRDY         45         HA21         78         LAD20         111         RCA7           13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         Gl         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120 <td>9</td> <td>R1</td> <td>42</td> <td>HA24</td> <td>75</td> <td>LAD19</td> <td>108</td> <td>RCA10</td>                                       | 9      | R1              | 42     | HA24     | 75     | LAD19           | 108    | RCA10           |

| 12         HRDY         45         HA21         78         LAD20         111         RCA7           13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121 </td <td>10</td> <td>HOE</td> <td>43</td> <td>HA23</td> <td>76</td> <td>V<sub>CC</sub></td> <td>109</td> <td>RCA9</td>                      | 10     | HOE             | 43     | HA23     | 76     | V <sub>CC</sub> | 109    | RCA9            |

| 13         HINT         46         HA20         79         LAD5         112         RCA6           14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122 <td>11</td> <td>HDST</td> <td>44</td> <td>HA22</td> <td>77</td> <td>LAD4</td> <td>110</td> <td>RCA8</td>                                      | 11     | HDST            | 44     | HA22     | 77     | LAD4            | 110    | RCA8            |

| 14         EMU3         47         HA19         80         LAD21         113         RCA5           15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINTZ         55         HA12         88         LAD24         121         SF           23         LINTT         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123 </td <td>12</td> <td>HRDY</td> <td>45</td> <td>HA21</td> <td>78</td> <td>LAD20</td> <td>111</td> <td>RCA7</td>                              | 12     | HRDY            | 45     | HA21     | 78     | LAD20           | 111    | RCA7            |

| 15         LCLK1         48         HA18         81         LAD6         114         V <sub>CC</sub> 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123 </td <td>13</td> <td>HINT</td> <td>46</td> <td>HA20</td> <td>79</td> <td>LAD5</td> <td>112</td> <td>RCA6</td>                               | 13     | HINT            | 46     | HA20     | 79     | LAD5            | 112    | RCA6            |

| 16         LCLK2         49         HA17         82         LAD22         115         V <sub>SS</sub> 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         12                                                                                                                                           | 14     | EMU3            | 47     | HA19     | 80     | LAD21           | 113    | RCA5            |

| 17         EMU1         50         V <sub>SS</sub> 83         LAD7         116         RCA4           18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11 <t< td=""><td>15</td><td>LCLK1</td><td>48</td><td>HA18</td><td>81</td><td>LAD6</td><td>114</td><td>V<sub>CC</sub></td></t<>                      | 15     | LCLK1           | 48     | HA18     | 81     | LAD6            | 114    | V <sub>CC</sub> |

| 18         EMU0         51         HA16         84         LAD23         117         RCA3           19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27                                                                                                                                              | 16     | LCLK2           | 49     | HA17     | 82     | LAD22           | 115    | V <sub>SS</sub> |

| 19         EMU2         52         HA15         85         V <sub>SS</sub> 118         RCA2           20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub>                                                                                                                                 | 17     | EMU1            | 50     | $V_{SS}$ | 83     | LAD7            | 116    | RCA4            |

| 20         GI         53         HA14         86         V <sub>SS</sub> 119         RCA1           21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12                                                                                                                                          | 18     | EMU0            | 51     | HA16     | 84     | LAD23           | 117    | RCA3            |

| 21         RESET         54         HA13         87         LAD8         120         RCA0           22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28 <td>19</td> <td>EMU2</td> <td>52</td> <td>HA15</td> <td>85</td> <td><math>V_{SS}</math></td> <td>118</td> <td>RCA2</td>                | 19     | EMU2            | 52     | HA15     | 85     | $V_{SS}$        | 118    | RCA2            |

| 22         LINT2         55         HA12         88         LAD24         121         SF           23         LINT1         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> </td <td>20</td> <td>GI</td> <td>53</td> <td>HA14</td> <td>86</td> <td><math>V_{SS}</math></td> <td>119</td> <td>RCA1</td> | 20     | GI              | 53     | HA14     | 86     | $V_{SS}$        | 119    | RCA1            |

| 23         LINTT         56         HA11         89         LAD9         122         TR/QE           24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                             | 21     | RESET           | 54     | HA13     | 87     | LAD8            | 120    | RCA0            |

| 24         CAMD         57         HA10         90         LAD25         123         VSYNC           25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                  | 22     | LINT2           | 55     | HA12     | 88     | LAD24           | 121    | SF              |

| 25         BUSFLT         58         HA9         91         LAD10         124         HSYNC           26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                       | 23     | LINT1           | 56     | HA11     | 89     | LAD9            | 122    | TR/QE           |

| 26         SIZE16         59         HA8         92         LAD26         125         CBLNK/VBLNK           27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24     | CAMD            | 57     | HA10     | 90     | LAD25           | 123    | VSYNC           |

| 27         PGMD         60         HA7         93         LAD11         126         CSYNC/HBLNK           28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25     | BUSFLT          | 58     | HA9      | 91     | LAD10           | 124    | HSYNC           |

| 28         LRDY         61         HA6         94         LAD27         127         V <sub>SS</sub> 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26     | SIZE16          | 59     | HA8      | 92     | LAD26           | 125    | CBLNK/VBLNK     |

| 29         V <sub>CC</sub> 62         HA5         95         V <sub>CC</sub> 128         V <sub>SS</sub> 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27     | PGMD            | 60     | HA7      | 93     | LAD11           | 126    | CSYNC/HBLNK     |

| 30         VCLK         63         HBS3         96         LAD12         129         ALTCH           31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28     | LRDY            | 61     | HA6      | 94     | LAD27           | 127    | V <sub>SS</sub> |

| 31         CLKIN         64         HBS2         97         LAD28         130         DDIN           32         HWRITE         65         HBS1         98         V <sub>SS</sub> 131         DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29     | V <sub>CC</sub> | 62     | HA5      | 95     | V <sub>CC</sub> | 128    | V <sub>SS</sub> |

| 32 HWRITE 65 HBS1 98 V <sub>SS</sub> 131 DDOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30     | VCLK            | 63     | HBS3     | 96     | LAD12           | 129    | ALTCH           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31     | CLKIN           | 64     | HBS2     | 97     | LAD28           | 130    | DDIN            |

| 33 HREAD 66 HBS0 99 LAD13 132 WE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32     | HWRITE          | 65     | HBS1     | 98     | V <sub>SS</sub> | 131    | DDOUT           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33     | HREAD           | 66     | HBS0     | 99     |                 | 132    | WE              |

# **Terminal Functions**

| TERMIN     | AL                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | TYPE <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |                   | LOCAL MEMORY INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ALTCH      | О                 | Address latch. The high-to-low transitions of ALTCH can be used to capture the address and status available on LAD. A transparent latch (such as a 54ALS373) maintains the current address and status as long as ALTCH remains low.                                                                                                                                                                                                                                                                                                                |

| BUSFLT     | I                 | Bus fault. External logic asserts BUSFLT high to the SMJ34020A to indicate that an error or fault has occurred on the current bus cycle. BUSFLT is also used with LRDY to generate externally requested bus cycle retries so that the entire memory address is presented again on LAD.                                                                                                                                                                                                                                                             |

|            |                   | In the emulation mode, BUSFLT is used for write protecting mapped memory (by disabling CAS outputs for the current cycle).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DDIN       | 0                 | Data bus direction in enable. DDIN is used to drive the active-high output enables on bidirectional transceivers (such as the 54ALS623). The transceivers buffer data input and output on LAD0-LAD31 when the SMJ34020A is interfaced to several memories.                                                                                                                                                                                                                                                                                         |

| DDOUT      | 0                 | Data bus direction output enable. DDOUT drives the active-low output enables on bidirectional transceivers (such as the 54ALS623). The transceivers buffer data input and output on LAD0-LAD31.                                                                                                                                                                                                                                                                                                                                                    |

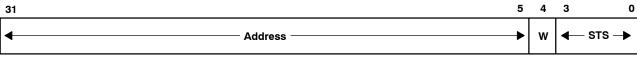

| LAD0-LAD31 | I/O               | 32-bit multiplexed local address/data bus. At the beginning of a memory cycle, the word address is output on LAD4-LAD31 and the cycle status is output on LAD0-LAD3. After the address is presented, LAD0-LAD31 are used for transferring data within the SMJ34020A system. LAD0 is the LSB and LAD31 is the MSB.                                                                                                                                                                                                                                  |

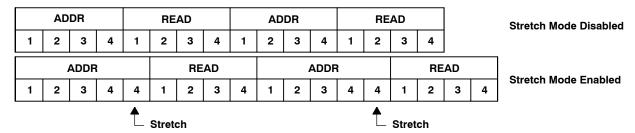

| LRDY       | I                 | Local ready. External circuitry drives LRDY low to inhibit the SMJ34020A from completing a local-memory cycle it has initiated. While LRDY remains low, the SMJ34020A waits unless the SMJ34020A loses bus priority or is given an external RETRY request (through BUSFLT). Wait states are generated in increments of one full LCLK1 cycle. LRDY can be driven low to extend local memory-read and memory-write cycles, VRAM serial-data-register-transfer cycles, and DRAM-refresh cycles. During internal cycles, the SMJ34020A ignores LRDY.   |

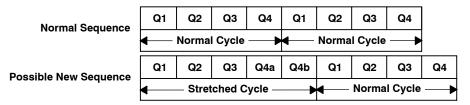

| PGMD       | I                 | Page mode. The memory-decode logic asserts PGMD low if the currently addressed memory supports burst (page mode) accesses. Burst accesses occur as a series of CAS cycles for a single RAS cycle to memory. LRDY is used with BUSFLT to describe the cycle termination status for a memory cycle.                                                                                                                                                                                                                                                  |

|            |                   | PGMD is also used in emulation mode for mapping memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SIZE16     | I                 | Bus size. The memory-decode logic can pull SIZE16 low if the currently addressed memory or port supports only 16-bit transfers. SIZE16 can also be used to determine which 16 bits of the data bus are used for a data transfer.                                                                                                                                                                                                                                                                                                                   |

|            |                   | In the emulation mode, SIZE16 is used to select the size of mapped memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            |                   | DRAM AND VRAM CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CAMD       | 1                 | Column-address mode. CAMD dynamically shifts the column address on the RCA0-RCA12 bus to allow the mixing of DRAM and VRAM address matrices using the same multiplexed address RCA0-RCA12 signals.                                                                                                                                                                                                                                                                                                                                                 |

| CAS0-CAS3  | 0                 | Four column-address strobes. CAS outputs drive the CAS inputs of DRAMs and VRAMs. CASO-CAS3 strobe the column address on RCA0-RCA12 to the memory. The four CAS strobes provide byte write-access to the memory.                                                                                                                                                                                                                                                                                                                                   |

| RAS        | 0                 | Row-address strobe. RAS output drives the RAS inputs of DRAMs and VRAMs. RAS strobes the row address on RCA0-RCA12 to memory.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RCA0-RCA12 | 0                 | Thirteen multiplexed row-address/column-address signals. At the beginning of a memory-access cycle, the row address for DRAMs is present on RCA0-RCA12. The row address contains the most significant address bits for the memory. As the cycle progresses, the memory column address is placed on RCA0-RCA12. The addresses that are actually output during row and column times depend on the memory configuration (set by RCM0 and RCM1 in the CONFIG register) and the state of CAMD during the access. RCA0 is the LSB, and RCA12 is the MSB. |

| SF         | 0                 | Special function pin. SF is the special-function signal to 1M VRAMs that allows the use of block write, load write mask, load color mask, and write using write mask. SF is also used to differentiate instructions and addresses for the coprocessor as part of the coprocessor interface.                                                                                                                                                                                                                                                        |

| TR/QE      | 0                 | Transfer/output-enable. TR/QE drives the TR/QE input of VRAMs. During a local memory-read cycle, TR/QE functions as an active-low output enable to gate from memory to LAD0-LAD31. During special VRAM function cycles, TR/QE controls the type of cycle that is performed.                                                                                                                                                                                                                                                                        |

<sup>†</sup> I = input, O = output

# **Terminal Functions (Continued)**

| TERMINA      | AL                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| NAME         | TYPE <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|              |                   | DRAM AND VRAM CONTROL (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| WE           | 0                 | Write enable. The active low WE drives the WE inputs of DRAMs and VRAMs. WE can also be used as the act low write enable to static memories and other devices connected to the SMJ34020A local interface. During local-memory read cycle, WE remains inactive high while CAS is strobed active low. During a local-memory w cycle, WE is strobed active low before CAS. During VRAM serial-data-register transfer cycles, the state of WE the falling edge of RAS controls the direction of the transfer.                                                                                                                                       |  |  |  |  |  |  |  |

|              |                   | HOST INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| HA5-HA31     | I                 | Twenty-seven host address input signals. A host can access a long word by placing the address on these lines. HA5-HA31 correspond to LAD5-LAD31 that output the address to the local memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| HBS0-HBS3    | I                 | Four host byte selects. HBS0-HBS3 identify which bytes within the long word are being selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

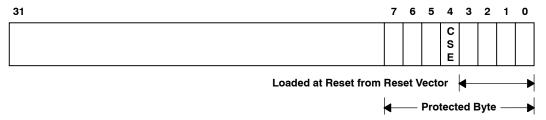

| HCS          | I                 | Host chip select. A host drives HCS low to latch the current host address present on HA5-HA31 and the host byte selects on HBS0-HBS3. HCS also enables host access cycles to the SMJ34020A I/O registers or local memory. During the low-to-high transition of RESET, the level on HCS determines whether the SMJ34020A is halted (HCS is high for host-present mode) or whether it begins executing its reset service routine (HCS is low for self-bootstrap mode).                                                                                                                                                                            |  |  |  |  |  |  |  |

| HDST         | 0                 | Host data-latch strobe. The rising edge of HDST latches data from the SMJ34020A local address space to the external host data latch on host read accesses. HDST can be used in conjunction with HRDY to indicate that data is valid in the external data latch.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

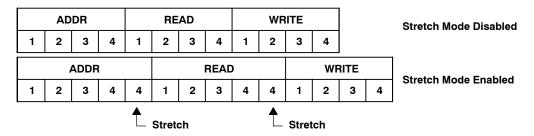

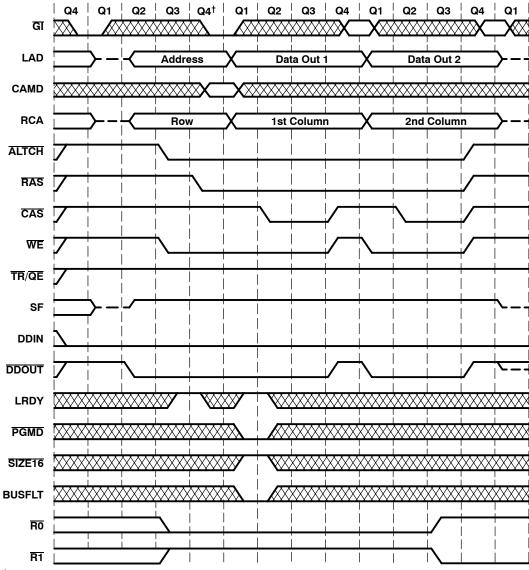

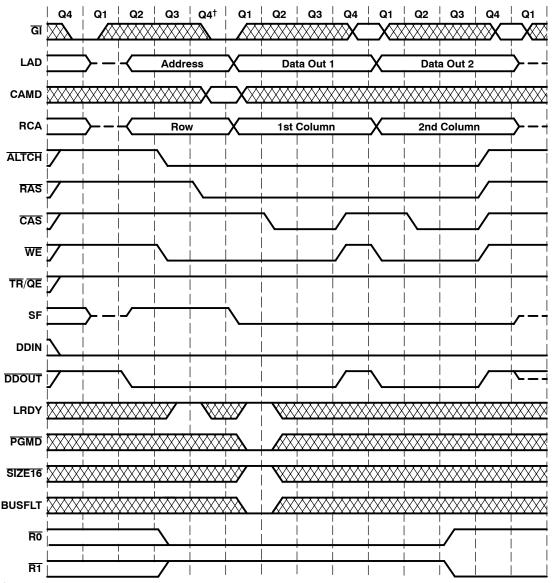

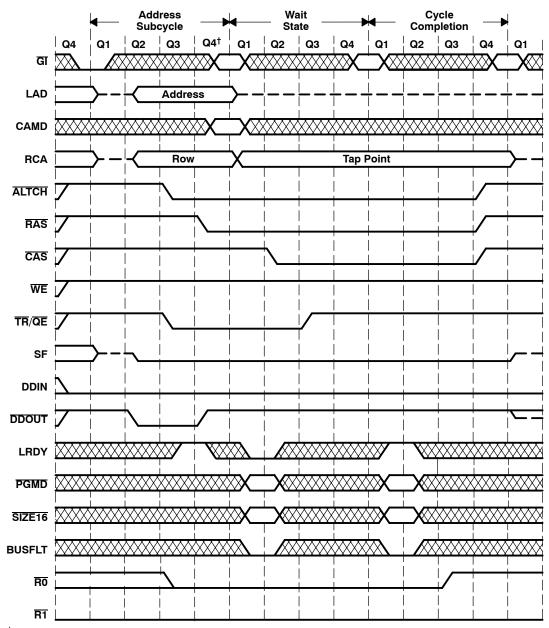

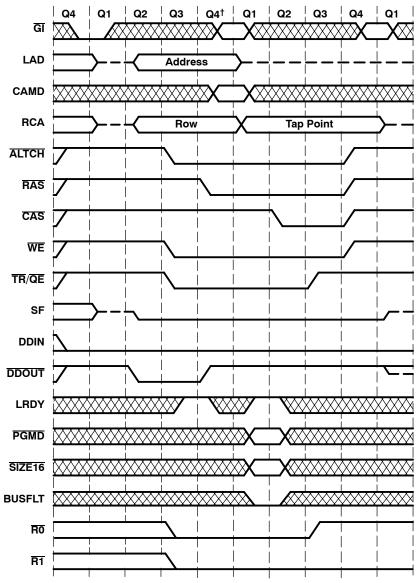

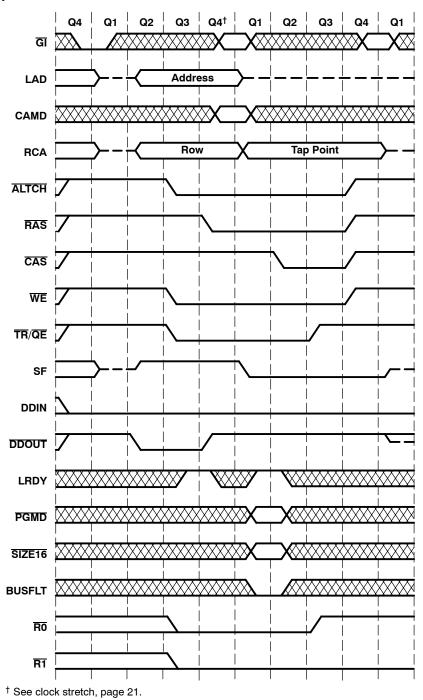

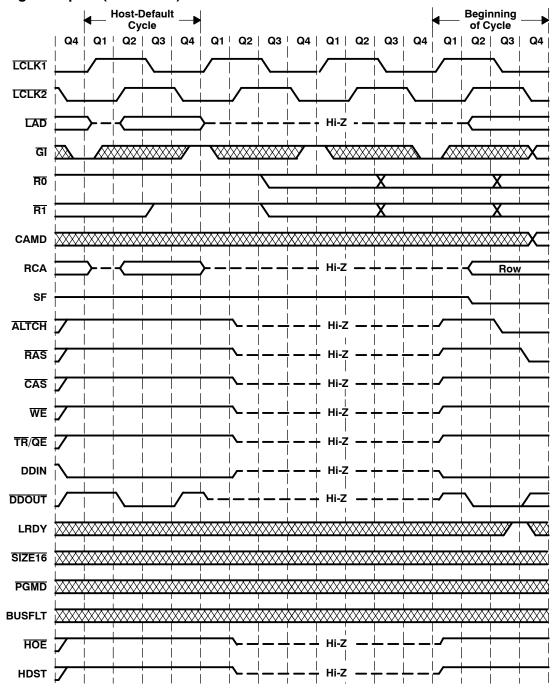

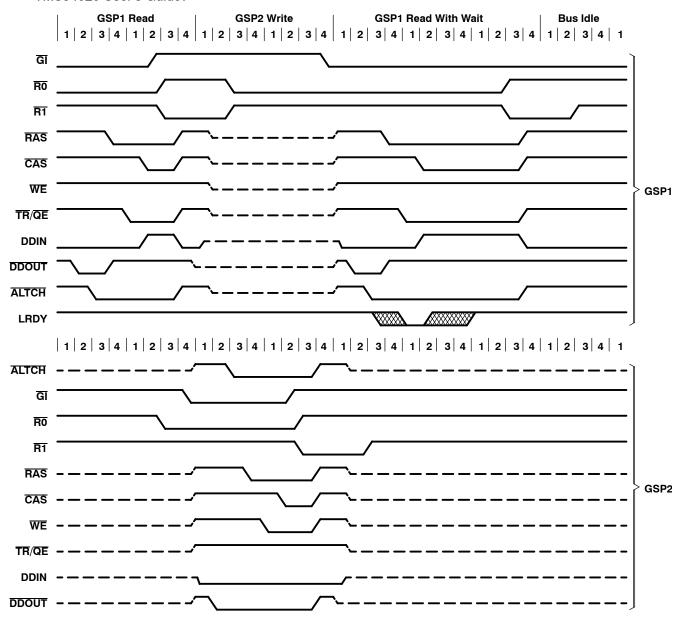

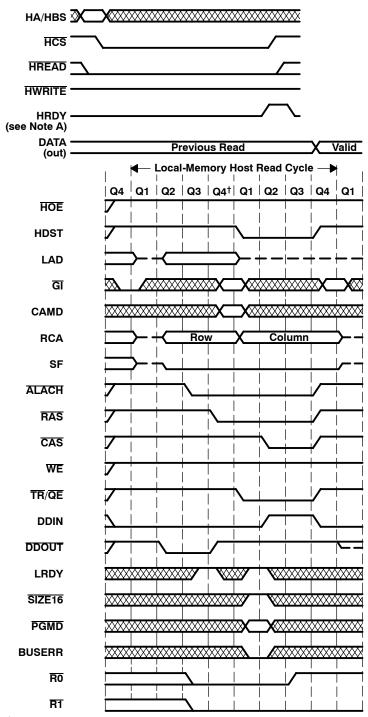

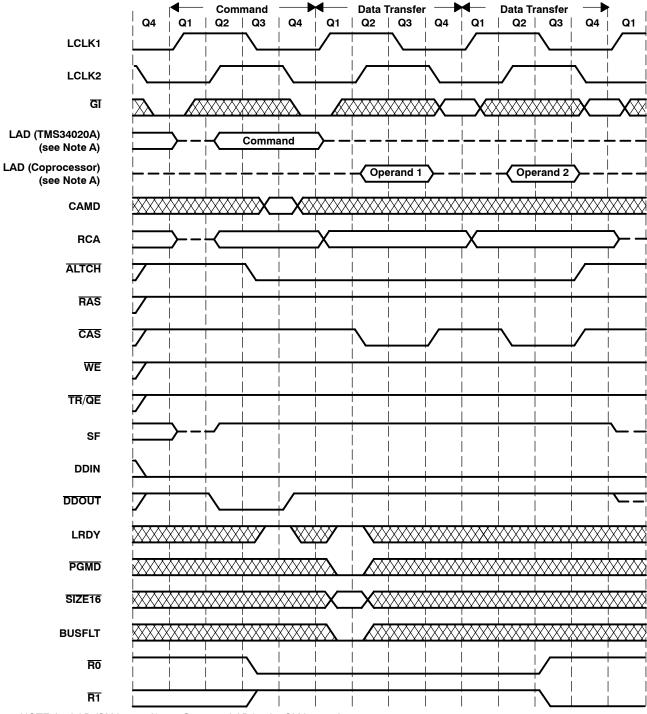

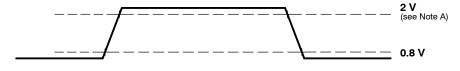

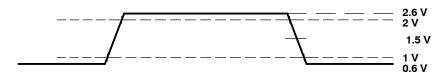

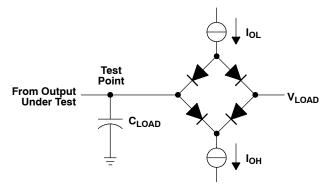

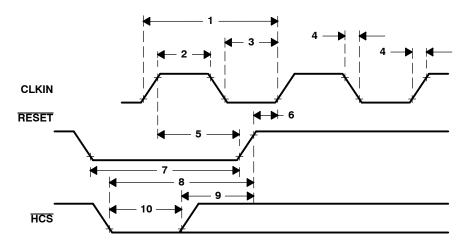

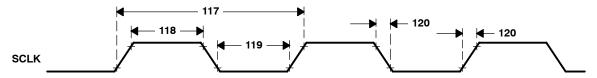

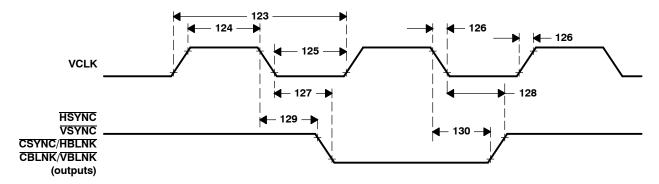

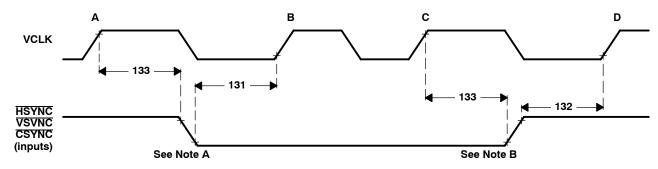

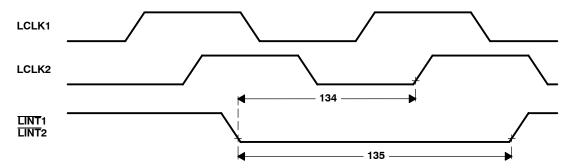

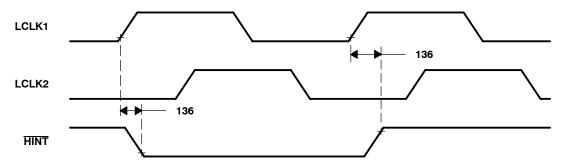

| HINT         | 0                 | Host Interrupt. HINT allows the SMJ34020A to interrupt a host by setting the INTOUT bit in the HSTCTLL I/O register. HINT can also be used to interrupt the host if a BUSFLT or RETRY occurs due to a host access cycle.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |