## GENERAL DESCRIPTION

The 8430B-71 is a general purpose, dual output Crystal/LVCMOS-to-3.3V Differential LVPECL High Frequency Synthesizer and a member of the HiPerClockS™ family of High Performance Clock Solutions from ICS. The 8430B-71 has a selectable crystal oscillator interface or LVCMOS TEST\_CLK. The VCO operates at a frequency range of 250MHz to 700MHz. With the output configured to divide the VCO frequency by 2, output frequency steps as small as 2MHz can be achieved using a 16MHz crystal or test clock. Output frequencies up to 700MHz can be programmed using the serial or parallel interfaces to the configuration logic. The low jitter and frequency range of the 8430B-71 make it an ideal clock generator for most clock tree applications.

## **F**EATURES

- Dual differential 3.3V LVPECL outputs

- Selectable crystal oscillator interface or LVCMOS TEST\_CLK

- Output frequency up to 700MHz

- Crystal input frequency range: 12MHz to 27MHz

- VCO range: 250MHz to 700MHz

- Parallel or serial interface for programming counter and output dividers

- RMS period jitter: 9ps (maximum)

- Cycle-to-cycle jitter: 25ps (maximum)

- 3.3V supply voltage

- 0°C to 70°C ambient operating temperature

- Replaces 8430-71

- Available in lead-free (RoHS 6) package

## **BLOCK DIAGRAM**

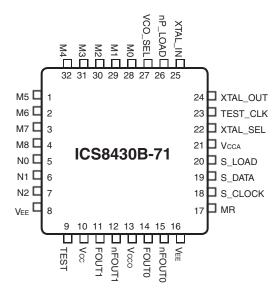

## PIN ASSIGNMENT

**32-Lead LQFP**7mm x 7mm x 1.4mm package body **Y Package**Top View

#### FUNCTIONAL DESCRIPTION

NOTE: The functional description that follows describes operation using a 16MHz crystal. Valid PLL loop divider values for different crystal or input frequencies are defined in the Input Frequency Characteristics, Table 5, NOTE 1.

The 8430B-71 features a fully integrated PLL and therefore requires no external components for setting the loop bandwidth. A parallel-resonant, fundamental crystal is used as the input to the on-chip oscillator. The output of the oscillator is divided by 16 prior to the phase detector. With a 16MHz crystal, this provides a 1MHz reference frequency. The VCO of the PLL operates over a range of 250MHz to 700MHz. The output of the M divider is also applied to the phase detector.

The phase detector and the M divider force the VCO output frequency to be 2M times the reference frequency by adjusting the VCO control voltage. Note that for some values of M (either too high or too low), the PLL will not achieve lock. The output of the VCO is scaled by a divider prior to being sent to each of the LVPECL output buffers. The divider provides a 50% output duty cycle.

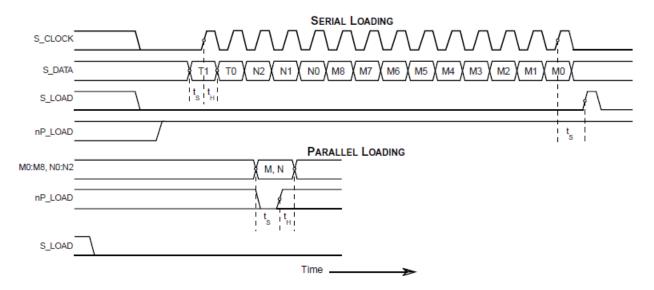

The programmable features of the 8430B-71 support two input modes to program the M divider and N output divider. The two input operational modes are parallel and serial. *Figure 1* shows the timing diagram for each mode. In parallel mode, the nP\_LOAD input is initially LOW. The data on inputs M0 through M8 and N0 through N2 is passed directly to the M divider and N output divider. On the LOW-to-HIGH transition of the nP\_LOAD input, the data is latched and the M divider remains loaded until the next LOW transition on nP\_LOAD or until a serial event occurs. As a result, the M and N bits can be hardwired to set the M divider and N output divider to a specific default state that will

automatically occur during power-up. The TEST output is LOW when operating in the parallel input mode. The relationship between the VCO frequency, the crystal frequency and the M divider is defined as follows:

$fVCO = \frac{fxtal}{16} \times 2M$

The M value and the required values of M0 through M8 are shown in Table 3B, Programmable VCO Frequency Function Table. Valid M values for which the PLL will achieve lock for a 16MHz reference are defined as  $125 \leq M \leq 350$ . The frequency out is defined as follows:

fout =

$$\frac{\text{fVCO}}{\text{N}} = \frac{\text{fxtal}}{16} \times \frac{2\text{M}}{\text{N}}$$

Serial operation occurs when nP\_LOAD is HIGH and S\_LOAD is LOW. The shift register is loaded by sampling the S\_DATA bits with the rising edge of S\_CLOCK. The contents of the shift register are loaded into the M divider and N output divider when S\_LOAD transitions from LOW-to-HIGH. The M divide and N output divide values are latched on the HIGH-to-LOW transition of S\_LOAD. If S\_LOAD is held HIGH, data at the S\_DATA input is passed directly to the M divider and N output divider on each rising edge of S\_CLOCK. The serial mode can be used to program the M and N bits and test bits T1 and T0. The internal registers T0 and T1 determine the state of the TEST output as follows:

| <u>T1</u> | T0 | TEST Output                  |

|-----------|----|------------------------------|

| 0         | 0  | LOW                          |

| 0         | 1  | S_Data clocked into register |

| 1         | 0  | Output of M divider          |

| 1         | 1  | CMOS Fout                    |

FIGURE 1. PARALLEL & SERIAL LOAD OPERATIONS

TABLE 1. PIN DESCRIPTIONS

| Number                           | Name                                       | Ту     | ре                 | Description                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|--------------------------------------------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3,<br>28, 29, 30<br>31, 32 | M5, M6, M7,<br>M0, M1, M2, M3,<br>M4<br>M8 | Input  | Pulldown<br>Pullup | M divider inputs. Data latched on LOW-to-HIGH transition of nP_LOAD input. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                        |

| 5, 6                             | N0, N1                                     | Input  | Pulldown           | Determines output divider value as defined in Table 3C                                                                                                                                                                                                                                                                             |

| 7                                | N2                                         | Input  | Pullup             | Function Table. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                                                                   |

| 8, 16                            | V                                          | Power  | Тапар              | Negative supply pins.                                                                                                                                                                                                                                                                                                              |

| 9                                | TEST                                       | Output |                    | Test output which is ACTIVE in the serial mode of operation. Output driven LOW in parallel mode. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                    |

| 10                               | V <sub>cc</sub>                            | Power  |                    | Core power supply pin.                                                                                                                                                                                                                                                                                                             |

| 11, 12                           | FOUT1, nFOUT1                              | Output |                    | Differential output for the synthesizer. 3.3V LVPECL interface levels.                                                                                                                                                                                                                                                             |

| 13                               | V <sub>cco</sub>                           | Power  |                    | Output supply pin.                                                                                                                                                                                                                                                                                                                 |

| 14, 15                           | FOUT0, nFOUT0                              | Output |                    | Differential output for the synthesizer. 3.3V LVPECL interface levels.                                                                                                                                                                                                                                                             |

| 17                               | MR                                         | Input  | Pulldown           | Active High Master reset. When logic HIGH, the internal dividers are reset causing the true outputs (FOUTx) to go low and the inverted outputs (nFOUTx) to go high. When Logic LOW, the internal dividers and the outputs are enabled. Assertion of MR does not affect loaded M, N, and T values. LVCMOS / LVTTL interface levels. |

| 18                               | S_CLOCK                                    | Input  | Pulldown           | Clocks in serial data present at S_DATA input into the shift register on the rising edge of S_CLOCK. LVCMOS / LVTTL interface levels.                                                                                                                                                                                              |

| 19                               | S_DATA                                     | Input  | Pulldown           | Shift register serial input. Data sampled on the rising edge of S_CLOCK. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                          |

| 20                               | S_LOAD                                     | Input  | Pulldown           | Controls transition of data from shift register into the dividers. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                |

| 21                               | V <sub>CCA</sub>                           | Power  |                    | Analog supply pin.                                                                                                                                                                                                                                                                                                                 |

| 22                               | XTAL_SEL                                   | Input  | Pullup             | Selects between the crystal oscillator or test clock as the PLL reference source. Selects XTAL inputs when HIGH. Selects TEST_CLK when LOW. LVCMOS / LVTTL interface levels.                                                                                                                                                       |

| 23                               | TEST_CLK                                   | Input  | Pulldown           | Test clock input. LVCMOS interface levels.                                                                                                                                                                                                                                                                                         |

| 24,<br>25                        | XTAL_OUT,<br>XTAL_IN                       | Input  |                    | Crystal oscillator interface. XTAL_IN is the input. XTAL_OUT is the output.                                                                                                                                                                                                                                                        |

| 26                               | nP_LOAD                                    | Input  | Pulldown           | Parallel load input. Determines when data present at M8:M0 is loaded into the M divider, and when data present at N2:N0 sets the N output divider value. LVCMOS / LVTTL interface levels.                                                                                                                                          |

| 27                               | VCO_SEL                                    | Input  | Pullup             | Determines whether synthesizer is in PLL or bypass mode. LVCMOS / LVTTL interface levels.                                                                                                                                                                                                                                          |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Table 2. Pin Characteristics

| Symbol | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|--------|-------------------------|-----------------|---------|---------|---------|-------|

| C      | Input Capacitance       |                 |         | 4       |         | pF    |

| R      | Input Pullup Resistor   |                 |         | 51      |         | kΩ    |

| R      | Input Pulldown Resistor |                 |         | 51      |         | kΩ    |

TABLE 3A. PARALLEL AND SERIAL MODE FUNCTION TABLE

|    |         |      | In   | puts     |         |        | Conditions                                                                                                        |

|----|---------|------|------|----------|---------|--------|-------------------------------------------------------------------------------------------------------------------|

| MR | nP_LOAD | М    | N    | S_LOAD   | S_CLOCK | S_DATA | Conditions                                                                                                        |

| Н  | Х       | Х    | Х    | Х        | Х       | Х      | Reset. Forces outputs LOW.                                                                                        |

| L  | L       | Data | Data | Х        | Х       | х      | Data on M and N inputs passed directly to the M divider and N output divider. TEST output forced LOW.             |

| L  | 1       | Data | Data | L        | Х       | Х      | Data is latched into input registers and remains loaded until next LOW transition or until a serial event occurs. |

| L  | Н       | Х    | Х    | L        | 1       | Data   | Serial input mode. Shift register is loaded with data on S_DATA on each rising edge of S_CLOCK.                   |

| L  | Н       | Х    | Х    | 1        | L       | Data   | Contents of the shift register are passed to the M divider and N output divider.                                  |

| L  | Н       | Х    | Х    | <b>\</b> | L       | Data   | M divider and N output divider values are latched.                                                                |

| L  | Н       | Х    | Х    | L        | Х       | Х      | Parallel or serial input do not affect shift registers.                                                           |

| L  | Н       | Х    | Х    | Н        | 1       | Data   | S_DATA passed directly to M divider as it is clocked.                                                             |

NOTE: L = LOW

H = HIGH

X = Don't care

↑ = Rising edge transition ↓ = Falling edge transition

TABLE 3B. PROGRAMMABLE VCO FREQUENCY FUNCTION TABLE (NOTE 1)

| VCO Frequency |          | 256 | 128 | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

|---------------|----------|-----|-----|----|----|----|----|----|----|----|

| (MHz)         | M Divide | M8  | M7  | М6 | M5 | M4 | М3 | M2 | M1 | МО |

| 250           | 125      | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 0  | 1  |

| 252           | 126      | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| 254           | 127      | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 256           | 128      | 0   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| •             | •        | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| •             | •        | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| 696           | 348      | 1   | 0   | 1  | 0  | 1  | 1  | 1  | 0  | 0  |

| 698           | 349      | 1   | 0   | 1  | 0  | 1  | 1  | 1  | 0  | 1  |

| 700           | 350      | 1   | 0   | 1  | 0  | 1  | 1  | 1  | 1  | 0  |

NOTE 1: These M divide values and the resulting frequencies correspond to crystal or TEST\_CLK input frequency of 16MHz.

TABLE 3C. PROGRAMMABLE OUTPUT DIVIDER FUNCTION TABLE

|    | Inputs |    | N Divider Value | FOUT0, nFOUT0 Output Frequency (MHz) |         |  |  |

|----|--------|----|-----------------|--------------------------------------|---------|--|--|

| N2 | N1     | N0 |                 | Minimum                              | Maximum |  |  |

| 0  | 0      | 0  | 2               | 125                                  | 350     |  |  |

| 0  | 0      | 1  | 4               | 62.5                                 | 175     |  |  |

| 0  | 1      | 0  | 8               | 31.25                                | 87.5    |  |  |

| 0  | 1      | 1  | 16              | 15.625                               | 43.75   |  |  |

| 1  | 0      | 0  | 1               | 250                                  | 700     |  |  |

| 1  | 0      | 1  | 2               | 125                                  | 350     |  |  |

| 1  | 1      | 0  | 4               | 62.5                                 | 175     |  |  |

| 1  | 1      | 1  | 8               | 31.25                                | 87.5    |  |  |

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V<sub>cc</sub> 4.6V

Inputs,  $V_{cc}$  -0.5V to  $V_{cc}$  + 0.5V

Outputs, I

Continuous Current 50mA Surge Current 100mA

Package Thermal Impedance,  $\theta_{_{\rm JA}}$  47.9°C/W (0 lfpm) Storage Temperature, T $_{_{\rm STG}}$  -65°C to 150°C

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

**Table 4A. Power Supply DC Characteristics,**  $V_{cc} = V_{cca} = V_{cco} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol           | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|-----------------|---------|---------|---------|-------|

| V <sub>cc</sub>  | Core Supply Voltage   |                 | 3.135   | 3.3     | 3.465   | V     |

| V                | Analog Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>cco</sub> | Output Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| <br> EE          | Power Supply Current  |                 |         |         | 140     | mA    |

| I <sub>CCA</sub> | Analog Supply Current |                 |         |         | 15      | mA    |

Table 4B. LVCMOS/LVTTL DC Characteristics,  $V_{CC} = V_{CCA} = V_{CCA} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol          | Parameter              |                                                                             | Test Conditions                            | Minimum | Typical | Maximum               | Units |

|-----------------|------------------------|-----------------------------------------------------------------------------|--------------------------------------------|---------|---------|-----------------------|-------|

|                 |                        | TEST_CLK; NOTE 1                                                            |                                            | 2.35    |         | V <sub>cc</sub> + 0.3 | V     |

| V <sub>IH</sub> | Input<br>High Voltage  | VCO_SEL, S_LOAD, S_DATA,<br>S_CLOCK, nP_LOAD, MR,<br>M0:M8, N0:N2, XTAL_SEL |                                            | 2       |         | V <sub>cc</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Volt         | age                                                                         |                                            | -0.3    |         | 0.8                   | V     |

| 15              | Input<br>High Current  | M0-M7, N0, N1, MR, nP_LOAD, S_CLOCK, S_DATA, S_LOAD                         | V <sub>cc</sub> = V <sub>IN</sub> = 3.465V |         |         | 150                   | μA    |

| IH IH           |                        | M8, N2, XTAL_SEL, VCO_SEL                                                   | V <sub>cc</sub> = V <sub>IN</sub> = 3.465V |         |         | 5                     | μA    |

|                 |                        | TEST_CLK                                                                    | $V_{cc} = V_{IN} = 3.465V$                 |         |         | 200                   | μΑ    |

|                 | Input                  | M0-M7, N0, N1, MR, nP_LOAD,<br>S_CLOCK, S_DATA, S_LOAD                      | $V_{CC} = 3.465V,$<br>$V_{IN} = 0V$        | -5      |         |                       | μΑ    |

| I IL            | Low Current            | TEST_CLK, M8, N2, XTAL_SEL, VCO_SEL                                         | $V_{CC} = 3.465V,$<br>$V_{IN} = 0V$        | -150    |         |                       | μΑ    |

| V <sub>OH</sub> | Output<br>High Voltage | TEST; NOTE 2                                                                |                                            | 2.6     |         |                       | V     |

| V <sub>oL</sub> | Output<br>Low Voltage  | TEST; NOTE 2                                                                |                                            |         |         | 0.5                   | V     |

NOTE 1: Characterized with 1ns input edge rate.

NOTE 2: Outputs terminated with  $50\Omega$  to  $V_{cco}/2$ .

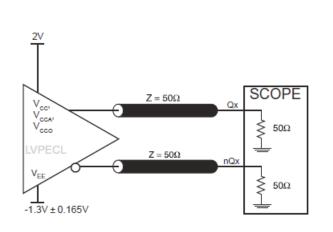

Table 4C. LVPECL DC Characteristics,  $V_{CC} = V_{CCA} = V_{CCCA} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol             | Parameter                         | Test Conditions | Minimum               | Typical | Maximum               | Units |

|--------------------|-----------------------------------|-----------------|-----------------------|---------|-----------------------|-------|

| V <sub>OH</sub>    | Output High Voltage; NOTE 1       |                 | V <sub>cc</sub> - 1.4 |         | V <sub>cc</sub> - 0.9 | V     |

| V <sub>OL</sub>    | Output Low Voltage; NOTE 1        |                 | V <sub>cc</sub> - 2.0 |         | V <sub>cc</sub> - 1.7 | V     |

| V <sub>swing</sub> | Peak-to-Peak Output Voltage Swing |                 | 0.6                   |         | 1.0                   | V     |

NOTE 1: Outputs terminated with 50W to V<sub>cco</sub> - 2V. See "Parameter Measurement Information" section, "3.3V Output Load Test Circuit" figure.

Table 5. Input Characteristics,  $V_{cc} = V_{cca} = V_{cco} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol               | Parameter       |                              | Test Conditions | Minimum | Typical | Maximum | Units |

|----------------------|-----------------|------------------------------|-----------------|---------|---------|---------|-------|

| f <sub>IN</sub> Inpo |                 | TEST_CLK; NOTE 1             |                 | 12      |         | 27      | MHz   |

|                      | Input Frequency | XTAL_IN, XTAL_OUT;<br>NOTE 1 |                 | 12      |         | 27      | MHz   |

|                      |                 | S_CLOCK                      |                 |         |         | 50      | MHz   |

| t<br>r_input         | Input Rise Time | TEST_CLK                     |                 |         |         | 5       | ns    |

NOTE 1: For the input crystal and reference frequency range, the M value must be set for the VCO to operate within the 250MHz to 700MHz range. Using the minimum input frequency of 12MHz, valid values of M are  $167 \le M \le 466$ . Using the maximum frequency of 27MHz, valid values of M are  $75 \le M \le 207$ .

## TABLE 6. CRYSTAL CHARACTERISTICS

| Parameter                          | Test Conditions | Minimum     | Typical | Maximum | Units |

|------------------------------------|-----------------|-------------|---------|---------|-------|

| Mode of Oscillation                |                 | Fundamental |         |         |       |

| Frequency                          |                 | 12          |         | 27      | MHz   |

| Equivalent Series Resistance (ESR) |                 |             |         | 50      | Ω     |

| Shunt Capacitance                  |                 |             |         | 7       | pF    |

| Drive Level                        |                 |             |         | 1       | mW    |

**Table 7. AC Characteristics,**  $V_{cc} = V_{cca} = V_{cco} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol                          | Parameter      |                       | Test Conditions                       | Minimum | Typical | Maximum | Units |

|---------------------------------|----------------|-----------------------|---------------------------------------|---------|---------|---------|-------|

| F <sub>MAX</sub>                | Output Frequ   | uency                 |                                       |         |         | 700     | MHz   |

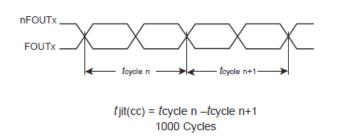

|                                 | Cycle to Cyc   | No littor: NOTE 1 2   | fOUT > 87.5MHz                        |         |         | 25      | ps    |

| tjit(cc)                        | Cycle-to-cyc   | cle Jitter; NOTE 1, 3 | fOUT ≤ 87.5MHz                        |         |         | 45      | ps    |

| tjit(per)                       | Period Jitter, | RMS; NOTE 1           |                                       |         |         | 9       | ps    |

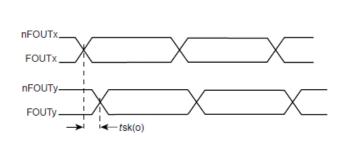

| tsk(o)                          | Output Skew    | r; NOTE 2, 3          |                                       |         |         | 15      | ps    |

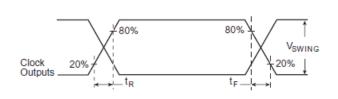

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/   | Fall Time             | 20% to 80%                            | 200     |         | 700     | ps    |

|                                 | Setup Time     | M, N to nP_LOAD       |                                       | 5       |         |         | ns    |

| ts                              |                | S_DATA to S_CLOCK     |                                       | 5       |         |         | ns    |

|                                 |                | S_CLOCK to S_LOAD     |                                       | 5       |         |         | ns    |

|                                 |                | M, N to nP_LOAD       |                                       | 5       |         |         | ns    |

| t <sub>H</sub>                  | Hold Time      | S_DATA to S_CLOCK     |                                       | 5       |         |         | ns    |

|                                 |                | S_CLOCK to S_LOAD     |                                       | 5       |         |         | ns    |

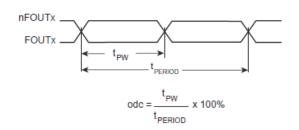

|                                 |                |                       | N ≠ div-by-1                          | 48      |         | 52      | %     |

| odc                             | Output Duty    | Cycle                 | N = div-by-1, fOUT ≤ 400MHz           | 45      |         | 55      | %     |

|                                 | Carpar Bary    | Cycle                 | N = div-by-1,<br>400MHz < fOUT 630MHz | 40      |         | 60      | %     |

| t <sub>LOCK</sub>               | PLL Lock Tir   | ne                    |                                       |         |         | 1       | ms    |

See Parameter Measurement Information section.

NOTE 1: Jitter performance using XTAL inputs.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

# PARAMETER MEASUREMENT INFORMATION

#### 3.3V OUTPUT LOAD ACTEST CIRCUIT

#### **OUTPUT SKEW**

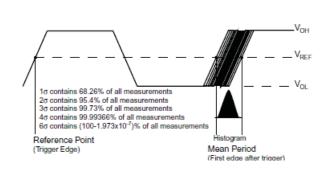

#### PERIOD JITTER

## Cycle-to-Cycle Jitter

November 30, 2015

## OUTPUT RISE/FALL TIME

### OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

## **APPLICATION INFORMATION**

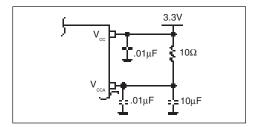

#### Power Supply Filtering Techniques

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. The 8430B-71 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{\rm cc}$ ,  $V_{\rm cca}$ , and  $V_{\rm cco}$  should be individually connected to the power supply plane through vias, and bypass capacitors should be used for each pin. To achieve optimum jitter performance, power supply isolation is required. Figure 1 illustrates how a  $10\Omega$  resistor along with a  $10\mu F$  and a  $.01\mu F$  bypass capacitor should be connected to each  $V_{\rm cca}$  pin.

FIGURE 1. POWER SUPPLY FILTERING

#### RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

## INPUTS:

#### CRYSTAL INPUT:

For applications not requiring the use of the crystal oscillator input, both XTAL\_IN and XTAL\_OUT can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from XTAL\_IN to ground.

#### TEST\_CLK INPUT:

For applications not requiring the use of the test clock, it can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from the TEST\_CLK to ground.

#### LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **OUTPUTS:**

#### LVPECL OUTPUT

All unused LVPECL outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.

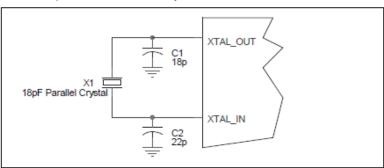

#### CRYSTAL INPUT INTERFACE

A crystal can be characterized for either series or parallel mode operation. The 8430B-71 has a built-in crystal oscillator circuit. This interface can accept either a series or parallel crystal without additional components and generate frequencies with accuracy

suitable for most applications. Additional accuracy can be achieved by adding two small capacitors C1 and C2 as shown in *Figure 2*.

FIGURE 2. CRYSTAL INPUT INTERFACE

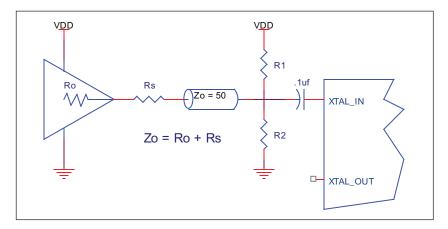

#### LVCMOS TO XTAL INTERFACE

The XTAL\_IN input can accept a single-ended LVCMOS signal through an AC coupling capacitor. A general interface diagram is shown in *Figure 3*. The XTAL\_OUT pin can be left floating. The input edge rate can be as slow as 10ns. For LVCMOS inputs, it is recommended that the amplitude be reduced from full swing to half swing in order to prevent signal interference with the power rail and to reduce noise. This configuration requires that the output

impedance of the driver (Ro) plus the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This can be done in one of two ways. First, R1 and R2 in parallel should equal the transmission line impedance. For most  $50\Omega$  applications, R1 and R2 can be  $100\Omega.$  This can also be accomplished by removing R1 and making R2  $50\Omega.$

FIGURE 3. GENERAL DIAGRAM FOR LVCMOS DRIVER TO XTAL INPUT INTERFACE

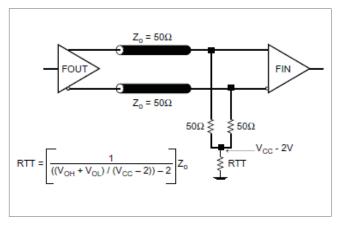

#### TERMINATION FOR LVPECL OUTPUTS

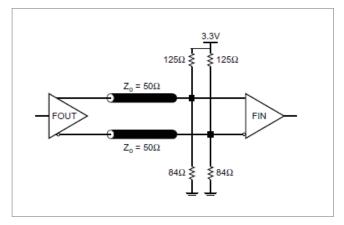

The clock layout topology shown below is a typical termination for LVPECL outputs. The two different layouts mentioned are recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that generate ECL/LVPECL compatible outputs. Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to drive  $50\Omega$  transmission

lines. Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion. There are a few simple termination schemes. *Figures 4A and 4B* show two different layouts which are recommended only as guidelines. Other suitable clock layouts may exist and it would be recommended that the board designers simulate to guarantee compatibility across all printed circuit and clock component process variations.

FIGURE 4A. LVPECL OUTPUT TERMINATION

FIGURE 4B. LVPECL OUTPUT TERMINATION

### LAYOUT GUIDELINE

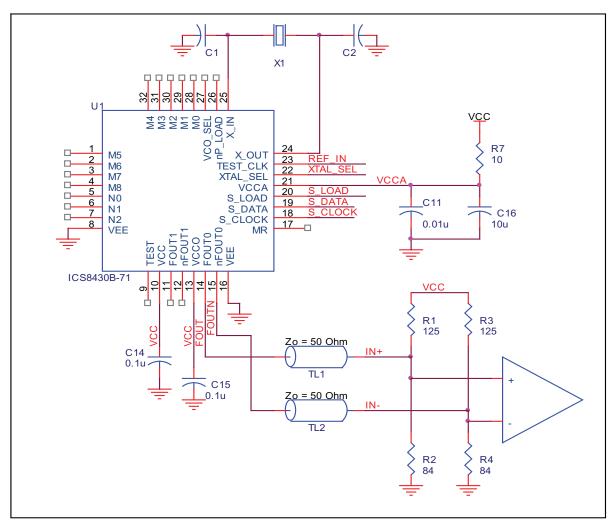

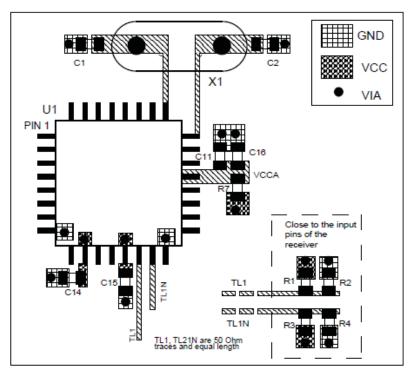

The schematic of the 8430B-71 layout example used in this layout guideline is shown in *Figure 5A*. The 8430B-71 recommended PCB board layout for this example is shown in *Figure 5B*. This layout example is used as a general guideline. The layout in the actual

system will depend on the selected component types, the density of the components, the density of the traces, and the stack up of the P.C. board.

FIGURE 5A. SCHEMATIC OF RECOMMENDED LAYOUT

The following component footprints are used in this layout example: All the resistors and capacitors are size 0603.

#### POWER AND GROUNDING

Place the decoupling capacitors C14 and C15 as close as possible to the power pins. If space allows, placing the decoupling capacitor at the component side is preferred. This can reduce unwanted inductance between the decoupling capacitor and the power pin generated by the via.

Maximize the pad size of the power (ground) at the decoupling capacitor. Maximize the number of vias between power (ground) and the pads. This can reduce the inductance between the power (ground) plane and the component power (ground) pins.

If V  $_{_{CCA}}$  shares the same power supply with V  $_{_{CC}}$ , insert the RC filter R7, C11, and C16 in between. Place this RC filter as close to the V  $_{_{CCA}}$  as possible.

#### **CLOCK TRACES AND TERMINATION**

The component placements, locations and orientations should be arranged to achieve the best clock signal quality. Poor clock signal quality can degrade the system performance or cause system failure. In the synchronous high-speed digital system, the clock signal is less tolerable to poor signal quality than other signals. Any ringing on the rising or falling edge or excessive ring back can cause system failure. The trace shape and the trace delay might be restricted by the available space on the board and the component location. While routing the traces, the clock signal traces should be routed first and should be locked prior to routing other signal traces.

- The traces with 50Ω transmission lines TL1 and TL2 at FOUT and nFOUT should have equal delay and run adjacent to each other. Avoid sharp angles on the clock trace. Sharp angle turns cause the characteristic impedance to change on the transmission lines.

- Keep the clock trace on the same layer. Whenever possible, avoid any vias on the clock traces. Any via on the trace can affect the trace characteristic impedance and hence degrade signal quality.

- To prevent cross talk, avoid routing other signal traces in parallel with the clock traces. If running parallel traces is unavoidable, allow more space between the clock trace and the other signal trace.

- Make sure no other signal trace is routed between the clock trace pair.

The matching termination resistors R1, R2, R3 and R4 should be located as close to the receiver input pins as possible. Other termination schemes can also be used but are not shown in this example.

#### CRYSTAL

The crystal X1 should be located as close as possible to the pins 24 (XTAL\_OUT) and 25 (XTAL\_IN). The trace length between the X1 and U1 should be kept to a minimum to avoid unwanted parasitic inductance and capacitance. Other signal traces should not be routed near the crystal traces.

FIGURE 5B. PCB BOARD LAYOUT FOR 8430B-71

## POWER CONSIDERATIONS

This section provides information on power dissipation and junction temperature for the 8430B-71. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the 8430B-71 is the sum of the core power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{cc} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

Power (core)<sub>MAX</sub> =

$$V_{CC,MAX} * I_{EE,MAX} = 3.465V * 140mA = 485mW$$

Power (outputs) = 30mW/Loaded Output pair

If all outputs are loaded, the total power is 2 \* 30mW = 60mW

**Total Power**  $_{\text{MAX}}$  (3.465V, with all outputs switching) = 485mW + 60mW = **545mW**

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for HiPerClockS™ devices is 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{\text{JA}}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming a moderate air flow of 200 linear feet per minute and a multi-layer board, the appropriate value is 42.1°C/W per Table 8 below.

Therefore, Tj for an ambient temperature of 70°C with all outputs switching is:

$70^{\circ}\text{C} + 0.545\Omega * 42.1^{\circ}\text{C/W} = 93^{\circ}\text{C}$ . This is well below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow, and the type of board (single layer or multi-layer).

Table 8. Thermal Resistance  $\theta_{\text{JA}}$  for 32-pin LQFP, Forced Convection

## $\theta_{\mbox{\tiny JA}}$ by Velocity (Linear Feet per Minute)

|                                              | 0        | 200      | 500      |

|----------------------------------------------|----------|----------|----------|

| Single-Layer PCB, JEDEC Standard Test Boards | 67.8°C/W | 55.9°C/W | 50.1°C/W |

| Multi-Layer PCB, JEDEC Standard Test Boards  | 47.9°C/W | 42.1°C/W | 39.4°C/W |

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

#### 3. Calculations and Equations.

The purpose of this section is to derive the power dissipated into the load.

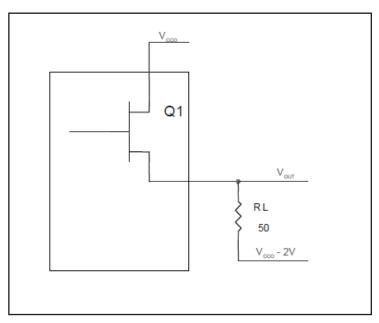

LVPECL output driver circuit and termination are shown in Figure 6.

FIGURE 6. LVPECL DRIVER CIRCUIT AND TERMINATION

To calculate worst case power dissipation into the load, use the following equations which assume a  $50\Omega$  load, and a termination voltage of  $V_{cco}$ - 2V.

• For logic high,

$$V_{OUT} = V_{OH, MAX} = V_{CCO, MAX} - 0.9V$$

$$(V_{CCO MAX} - V_{OH MAX}) = 0.9V$$

• For logic low,  $V_{OUT} = V_{OL MAX} = V_{CCO MAX} - 1.7V$

$$(V_{CCO MAX} - V_{OL MAX}) = 1.7V$$

Pd\_H is power dissipation when the output drives high.

Pd\_L is the power dissipation when the output drives low.

$$Pd_{-}H = [(V_{OH\_MAX} - (V_{CCO\_MAX} - 2V))/R_{L}] * (V_{CCO\_MAX} - V_{OH\_MAX}) = [(2V - (V_{CCO\_MAX} - V_{OH\_MAX}))/R_{L}] * (V_{CCO\_MAX} - V_{OH\_MAX}) = [(2V - 0.9V)/50\Omega] * 0.9V = 19.8mW$$

$$Pd\_L = [(V_{\text{ol_MAX}} - (V_{\text{cco\_MAX}} - 2V))/R_{\text{L}}] * (V_{\text{cco\_MAX}} - V_{\text{ol_MAX}}) = [(2V - (V_{\text{cco\_MAX}} - V_{\text{ol_MAX}}))/R_{\text{L}}] * (V_{\text{cco\_MAX}} - V_{\text{ol_MAX}}) = [(2V - 1.7V)/50\Omega] * 1.7V = 10.2mW$$

Total Power Dissipation per output pair = Pd\_H + Pd\_L = **30mW**

## RELIABILITY INFORMATION

# Table 9. $\theta_{_{JA}}vs.$ Air Flow Table for 32 Lead LQFP

## $\theta_{\mbox{\tiny JA}}$ by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

67.8°C/W

55.9°C/W

50.1°C/W

Multi-Layer PCB, JEDEC Standard Test Boards

47.9°C/W

42.1°C/W

39.4°C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

### TRANSISTOR COUNT

The transistor count for 8430B-71 is: 3948

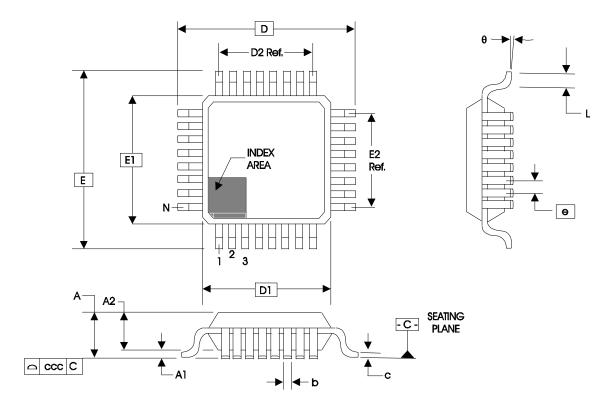

## PACKAGE OUTLINE - Y SUFFIX FOR 32 LEAD LQFP

TABLE 10. PACKAGE DIMENSIONS

| JEDEC VARIATION ALL DIMENSIONS IN MILLIMETERS |         |            |         |  |  |

|-----------------------------------------------|---------|------------|---------|--|--|

| OVALDOL                                       | ВВА     |            |         |  |  |

| SYMBOL                                        | МІМІМИМ | NOMINAL    | MAXIMUM |  |  |

| N                                             |         | 32         |         |  |  |

| A                                             |         |            | 1.60    |  |  |

| A1                                            | 0.05    |            | 0.15    |  |  |

| A2                                            | 1.35    | 1.40       | 1.45    |  |  |

| b                                             | 0.30    | 0.37       | 0.45    |  |  |

| С                                             | 0.09    |            | 0.20    |  |  |

| D                                             |         | 9.00 BASIC |         |  |  |

| D1                                            |         | 7.00 BASIC |         |  |  |

| D2                                            |         | 5.60       |         |  |  |

| E                                             |         | 9.00 BASIC |         |  |  |

| E1                                            |         | 7.00 BASIC |         |  |  |

| E2                                            |         | 5.60       |         |  |  |

| е                                             |         | 0.80 BASIC |         |  |  |

| L                                             | 0.45    | 0.60       | 0.75    |  |  |

| θ                                             | 0°      |            | 7°      |  |  |

| ccc                                           |         |            | 0.10    |  |  |

Reference Document: JEDEC Publication 95, MS-026

## TABLE 11. ORDERING INFORMATION

| Part/Order Number | Marking      | Package                  | Shipping Packaging | Temperature  |

|-------------------|--------------|--------------------------|--------------------|--------------|

| 8430BY-71LF       | ICS8430BY71L | 32 lead "Lead Free" LQFP | Tray               | 0°C to +70°C |

| 8430BY-71LFT      | ICS8430BY71L | 32 lead "Lead Free" LQFP | Tape and Reel      | 0°C to +70°C |

| REVISION HISTORY SHEET               |     |      |                                                             |          |

|--------------------------------------|-----|------|-------------------------------------------------------------|----------|

| Rev Table Page Description of Change |     | Date |                                                             |          |

| Α                                    | T11 | 17   | Ordering Information Table - corrected "Temperature" column | 11/20/06 |

| Α                                    |     |      | Updated data sheet format.                                  | 11/30/15 |

|                                      |     |      |                                                             |          |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/