## ATWINC15x0

# ATWINC15x0 Wi-Fi® Network Controller Software Design Guide

## Introduction

Microchip's SmartConnect ATWINC15x0 is an IEEE<sup>®</sup> 802.11 b/g/n network controller SoC for Internet of Things (IoT) applications. It is an ideal add-on to the existing microcontroller (MCU) solutions bringing Wi-Fi and network capabilities through an SPI-to-Wi-Fi interface. The ATWINC15x0 connects to any Microchip AVR<sup>®</sup> or Microchip SMART<sup>™</sup> MCU with minimal resource requirements.

## **Features**

- Wi-Fi IEEE 802.11 b/g/n STA, and AP modes

- Wi-Fi Protected Setup (WPS)

- Support of WEP, WPA/WPA2 Personal, and WPA/WPA2 Enterprise Security

- EAP-TLS

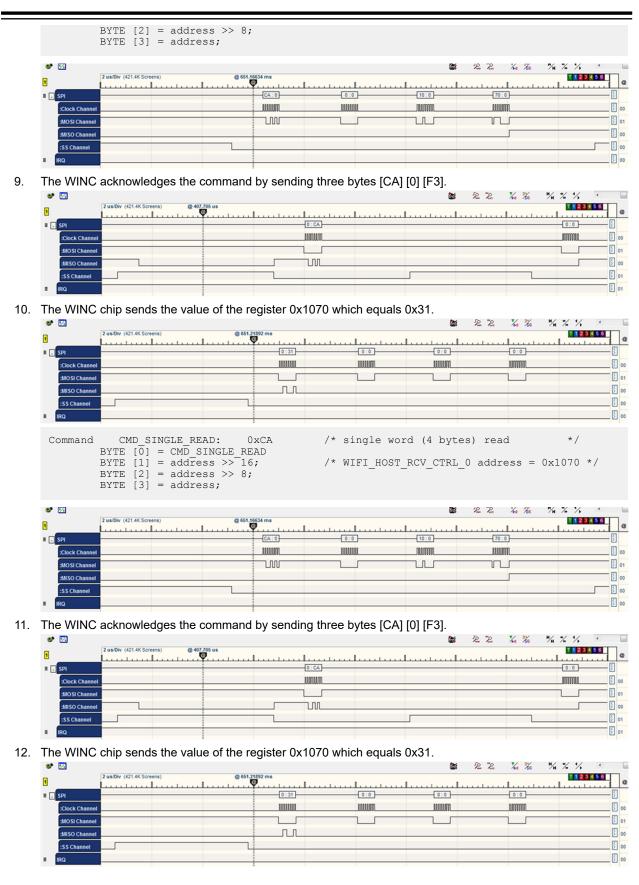

- EAP-PEAPv0/1 with TLS

- EAP-TTLSv0 with MSCHAPv2

- EAP-PEAPv0/1 with MSCHAPv2

- Embedded network stack protocols to offload work from the MCU (minimize the host CPU requirements). This

allows the Wi-Fi Network Controller (WINC) to operate with a wide range of MCUs including low-end MCUs.

- Embedded uIP TCP/IP stack with BSD-Style socket API

- · Embedded network protocols

- DHCP client/server

- DNS resolver client

- SNTP client for UTC time synchronization

- Embedded TLS security abstracted behind BSD-style socket API

- HTTP server for provisioning over AP mode

- Ultra-low C IEEE 802.11 b/g/n RF/PH/MAC SoC

- Fast boot from On-Chip boot ROM

- 8 Mb (WINC1510) and 4 Mb (WINC1500) internal Flash memory with Over-the-Air (OTA) firmware upgrade

- · WINC1510 support Host File Download feature which can be used for host MCU over the air firmware update

- · Low-power consumption with different Power Save modes

- · Low footprint host driver with the following capabilities:

- Can run on 8-, 16-, and 32-bit MCU using SPI interface

- Little- and big-endian support

## **Table of Contents**

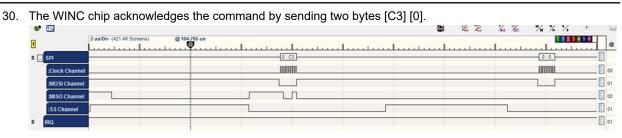

| Intr | oductic                        | on                                              | 1  |  |  |  |  |  |  |  |

|------|--------------------------------|-------------------------------------------------|----|--|--|--|--|--|--|--|

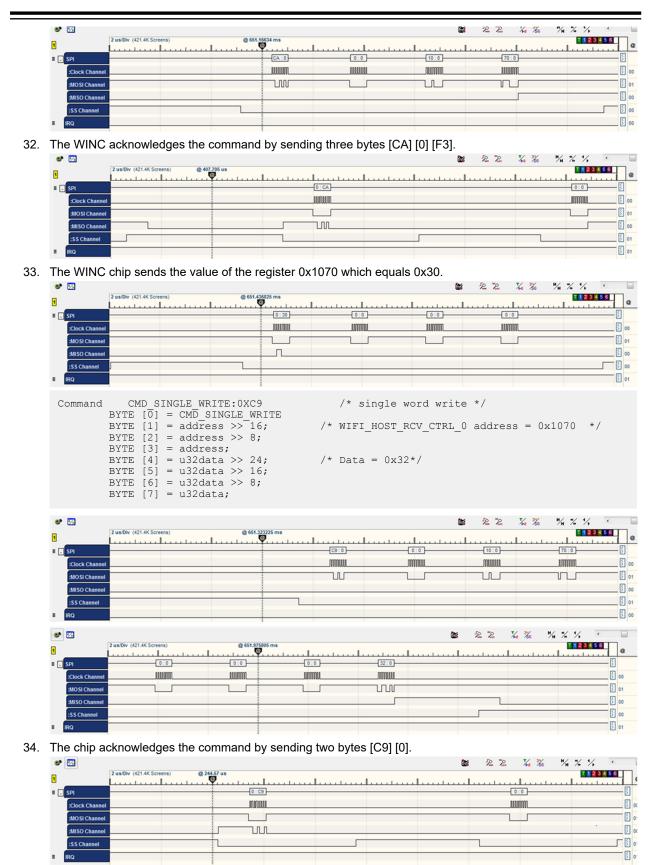

| Fea  | atures                         |                                                 | 1  |  |  |  |  |  |  |  |

| 1.   | Host I                         | Driver Architecture                             | 5  |  |  |  |  |  |  |  |

|      | 1.1.                           | WLAN API                                        | 5  |  |  |  |  |  |  |  |

|      | 1.2.                           | Socket API                                      | 5  |  |  |  |  |  |  |  |

|      | 1.3.                           | Host Interface (HIF)                            | 6  |  |  |  |  |  |  |  |

|      | 1.4.                           | Board Support Package (BSP)                     | 6  |  |  |  |  |  |  |  |

|      | 1.5.                           | Serial Bus Interface                            | 6  |  |  |  |  |  |  |  |

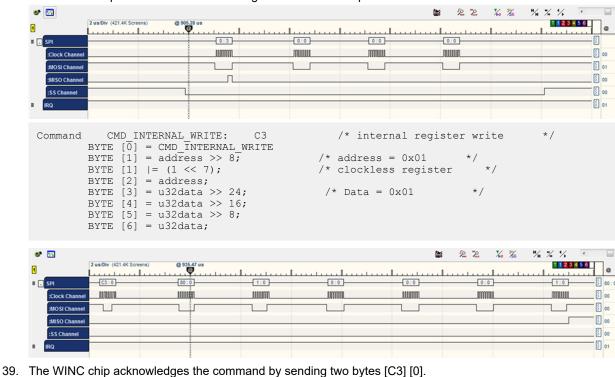

| 2.   | ATWINC15x0 System Architecture |                                                 |    |  |  |  |  |  |  |  |

|      | 2.1.                           | Bus Interface                                   | 7  |  |  |  |  |  |  |  |

|      | 2.2.                           | Nonvolatile Storage                             | 8  |  |  |  |  |  |  |  |

|      | 2.3.                           | CPU                                             | 8  |  |  |  |  |  |  |  |

|      | 2.4.                           | IEEE 802.11 MAC Hardware                        | 8  |  |  |  |  |  |  |  |

|      | 2.5.                           | Program Memory                                  | 8  |  |  |  |  |  |  |  |

|      | 2.6.                           | Data Memory                                     | 8  |  |  |  |  |  |  |  |

|      | 2.7.                           | Shared Packet Memory                            | 8  |  |  |  |  |  |  |  |

|      | 2.8.                           | IEEE 802.11 MAC Firmware                        | 8  |  |  |  |  |  |  |  |

|      | 2.9.                           | Memory Manager                                  | 8  |  |  |  |  |  |  |  |

|      | 2.10.                          | Power Management                                | 8  |  |  |  |  |  |  |  |

|      | 2.11.                          | WINC RTOS                                       | 9  |  |  |  |  |  |  |  |

|      | 2.12.                          | WINC IoT Library                                | 9  |  |  |  |  |  |  |  |

| 3.   | WINC                           | Initialization and Simple Application           | 11 |  |  |  |  |  |  |  |

|      | 3.1.                           | BSP Initialization                              | 11 |  |  |  |  |  |  |  |

|      | 3.2.                           | WINC Host Driver Initialization                 | 11 |  |  |  |  |  |  |  |

|      | 3.3.                           | Socket Layer Initialization                     | 11 |  |  |  |  |  |  |  |

|      | 3.4.                           | WINC Event Handling                             | 11 |  |  |  |  |  |  |  |

|      | 3.5.                           | Example Code                                    | 13 |  |  |  |  |  |  |  |

| 4.   | ATWI                           | NC15x0 Configuration                            | 14 |  |  |  |  |  |  |  |

|      | 4.1.                           | Device Parameters                               | 14 |  |  |  |  |  |  |  |

|      | 4.2.                           | WINC Modes of Operation                         | 14 |  |  |  |  |  |  |  |

|      | 4.3.                           | Network Parameters                              | 15 |  |  |  |  |  |  |  |

|      | 4.4.                           | Power Save Modes                                | 16 |  |  |  |  |  |  |  |

|      | 4.5.                           | Configuring Listen Interval and DTIM Monitoring | 18 |  |  |  |  |  |  |  |

| 5.   | Wi-Fi                          | Station Mode                                    | 19 |  |  |  |  |  |  |  |

|      | 5.1.                           | Scan Configuration Parameters                   | 19 |  |  |  |  |  |  |  |

|      | 5.2.                           | Wi-Fi Scan                                      | 19 |  |  |  |  |  |  |  |

|      | 5.3.                           | Wi-Fi Security                                  | 20 |  |  |  |  |  |  |  |

|      | 5.4.                           | On Demand Wi-Fi Connection                      | 21 |  |  |  |  |  |  |  |

|      | 5.5.                           | Default Connection                              | 24 |  |  |  |  |  |  |  |

|      | 5.6.                           | Encrypted Credential Storage                    | 25 |  |  |  |  |  |  |  |

|      | 5.7.                           | Simple Roaming                                  | 26 |  |  |  |  |  |  |  |

|     | 5.8.<br>5.9.                  | Multiple Gain Table Host File Download                        |    |  |  |  |  |  |  |

|-----|-------------------------------|---------------------------------------------------------------|----|--|--|--|--|--|--|

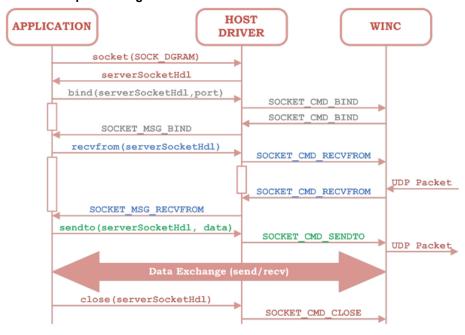

| 6.  | Socke                         | et Programming                                                | 36 |  |  |  |  |  |  |

|     | 6.1.                          | Overview                                                      | 36 |  |  |  |  |  |  |

|     | 6.2.                          | Sockets API                                                   | 36 |  |  |  |  |  |  |

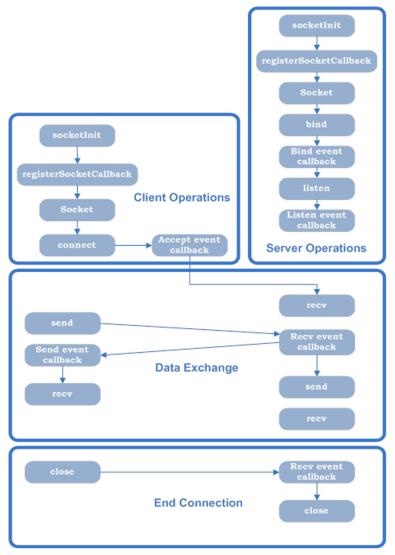

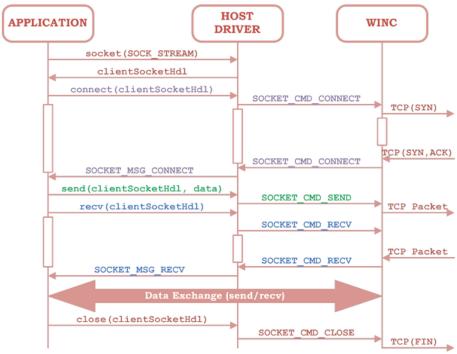

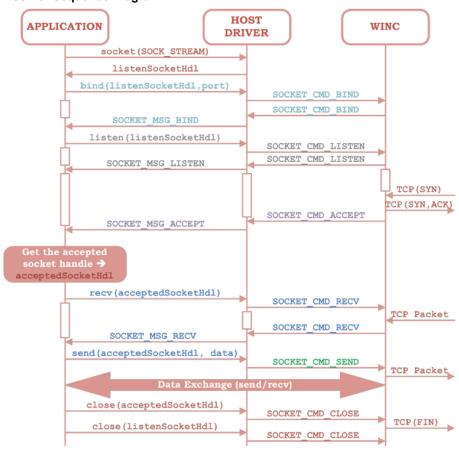

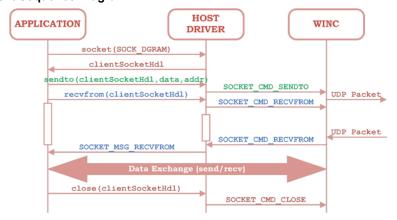

|     | 6.3.                          | Socket Connection Flow.                                       | 43 |  |  |  |  |  |  |

|     | 6.4.                          | Example Code                                                  | 48 |  |  |  |  |  |  |

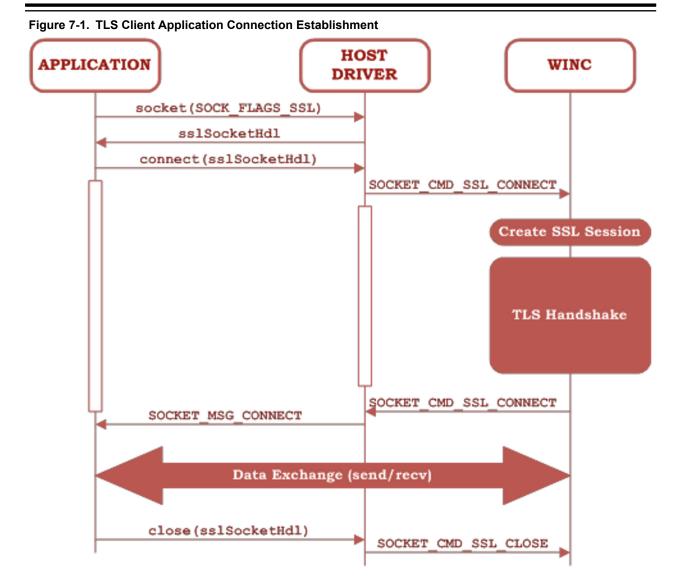

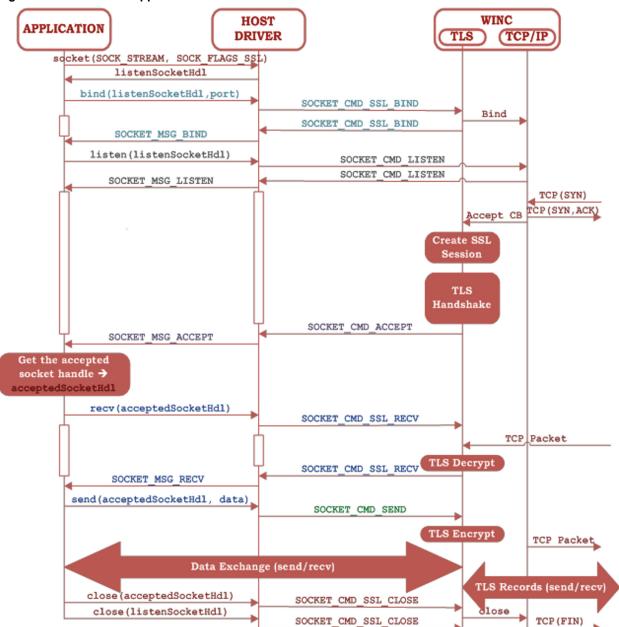

| 7.  | Trans                         | port Layer Security (TLS)                                     | 53 |  |  |  |  |  |  |

|     | 7.1.                          | TLS Overview                                                  | 53 |  |  |  |  |  |  |

|     | 7.2.                          | TLS Connection Establishment                                  | 53 |  |  |  |  |  |  |

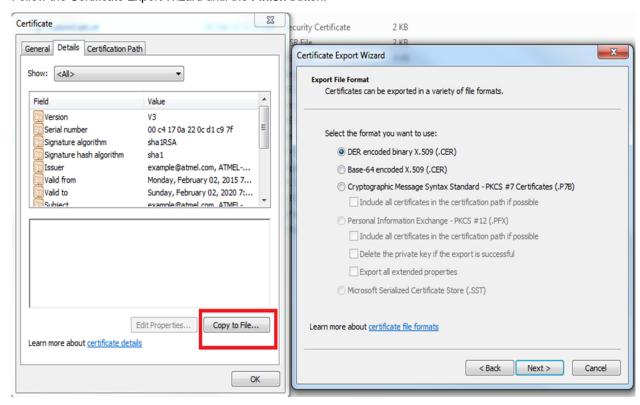

|     | 7.3.                          | Server Certificate Installation                               | 55 |  |  |  |  |  |  |

|     | 7.4.                          | WINC TLS Limitations                                          | 56 |  |  |  |  |  |  |

|     | 7.5.                          | SSL Client Code Example                                       | 57 |  |  |  |  |  |  |

| 8.  | Wi-Fi                         | AP Mode                                                       | 59 |  |  |  |  |  |  |

|     | 8.1.                          | Overview                                                      | 59 |  |  |  |  |  |  |

|     | 8.2.                          | Setting the WINC AP Mode                                      | 59 |  |  |  |  |  |  |

|     | 8.3.                          | Limitations                                                   | 59 |  |  |  |  |  |  |

|     | 8.4.                          | Sequence Diagram                                              | 59 |  |  |  |  |  |  |

|     | 8.5.                          | AP Mode Code Example                                          | 60 |  |  |  |  |  |  |

| 9.  | Provis                        | sioning                                                       | 62 |  |  |  |  |  |  |

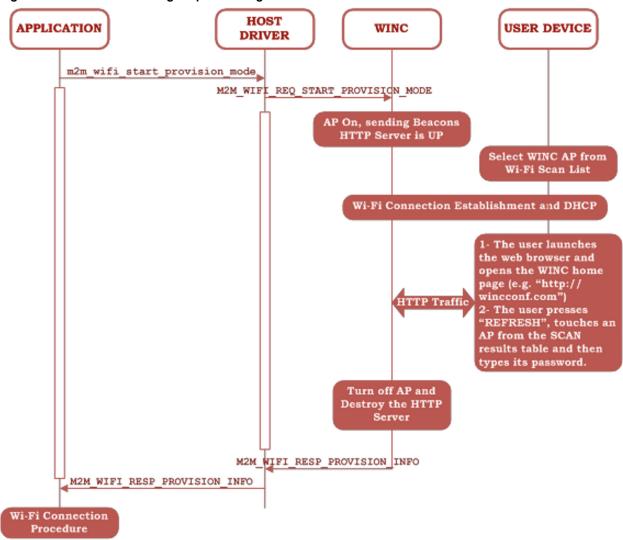

| 9.  | 9.1.                          | HTTP Provisioning                                             | 62 |  |  |  |  |  |  |

|     | 9.2.                          | Limitations                                                   | 65 |  |  |  |  |  |  |

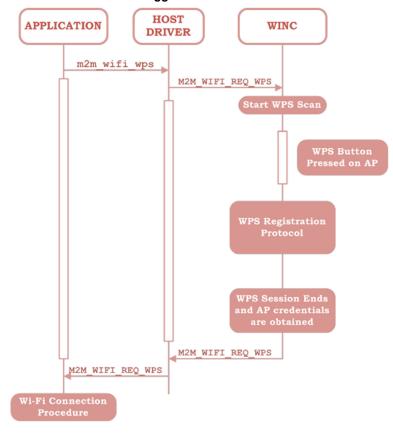

|     | 9.3.                          | Wi-Fi Protected Setup (WPS)                                   | 65 |  |  |  |  |  |  |

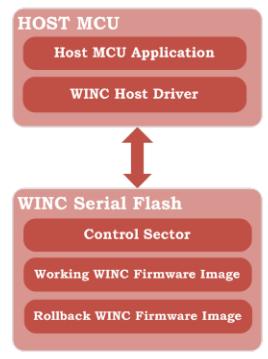

| 10. | Over-                         | The-Air Upgrade                                               | 68 |  |  |  |  |  |  |

|     |                               | Overview                                                      |    |  |  |  |  |  |  |

|     | 10.2.                         | OTA Image Architecture                                        | 68 |  |  |  |  |  |  |

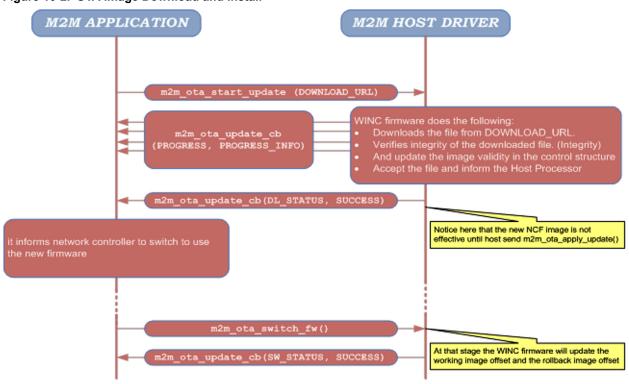

|     |                               | OTA Download Sequence Diagram                                 |    |  |  |  |  |  |  |

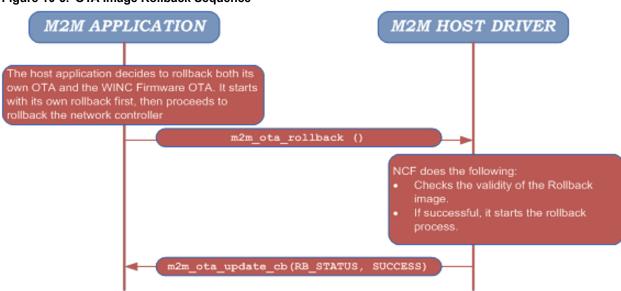

|     |                               | OTA Firmware Rollback                                         |    |  |  |  |  |  |  |

|     |                               | OTA Limitations                                               |    |  |  |  |  |  |  |

|     | 10.6.                         | OTA Code Example                                              | 70 |  |  |  |  |  |  |

| 11. |                               | ast Sockets                                                   |    |  |  |  |  |  |  |

|     |                               | Overview                                                      |    |  |  |  |  |  |  |

|     |                               | How to Use Filters                                            |    |  |  |  |  |  |  |

|     | 11.3.                         | Multicast Socket Code Example                                 | 71 |  |  |  |  |  |  |

| 12. |                               | Serial Flash Memory                                           |    |  |  |  |  |  |  |

|     |                               | Overview and Features                                         |    |  |  |  |  |  |  |

|     |                               | Accessing to Serial Flash                                     |    |  |  |  |  |  |  |

|     | 12.3.                         | Read/Write/Erase Operations                                   | 75 |  |  |  |  |  |  |

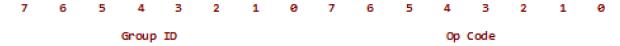

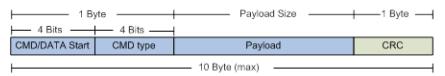

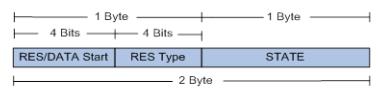

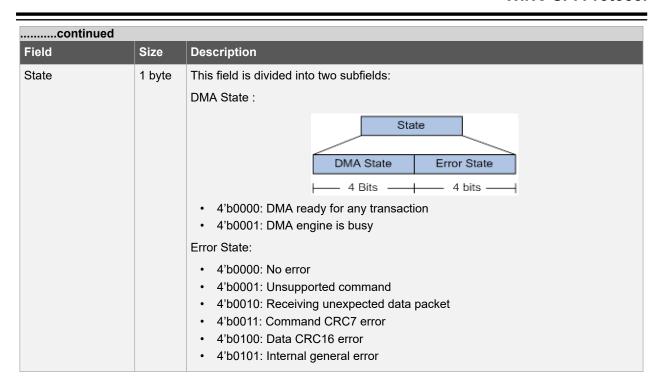

| 13. | Host Interface (HIF) Protocol |                                                               |    |  |  |  |  |  |  |

|     |                               | Transfer Sequence Between the HIF Layer and the WINC Firmware |    |  |  |  |  |  |  |

|     |                               | HIF Message Header Structure                                  |    |  |  |  |  |  |  |

|     | 13.3.                         | HIF Layer APIs                                                | 81 |  |  |  |  |  |  |

|     | 13.4.    | Scan Code Example                              | 82    |

|-----|----------|------------------------------------------------|-------|

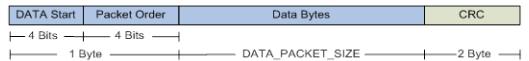

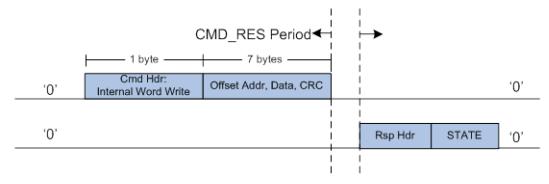

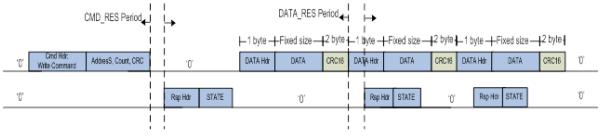

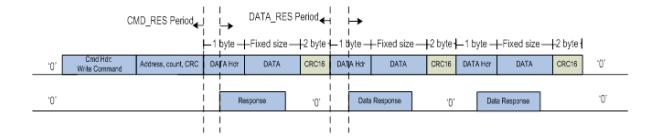

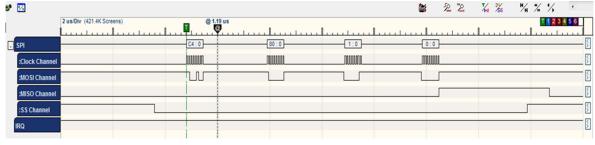

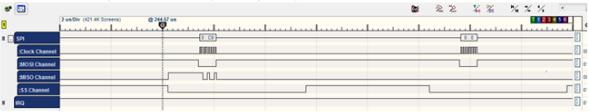

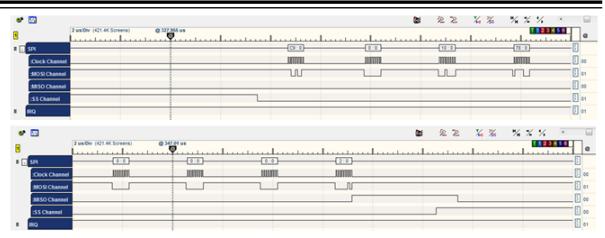

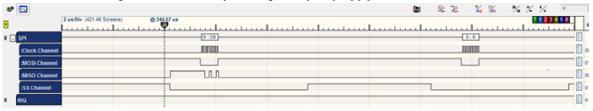

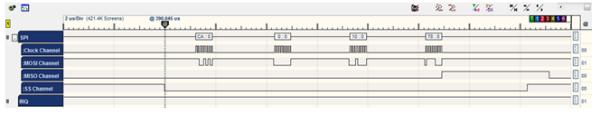

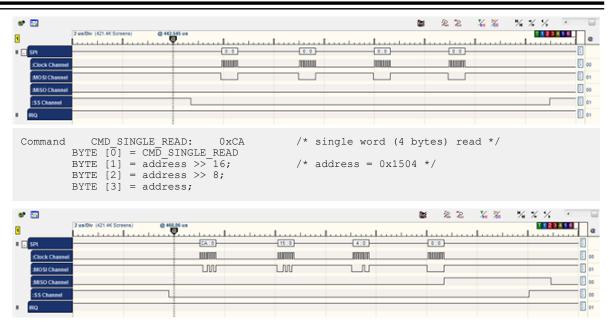

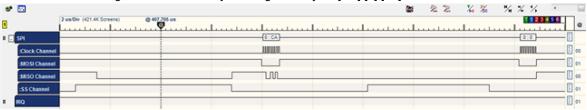

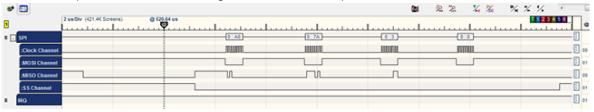

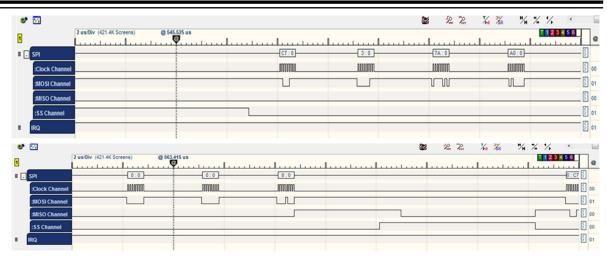

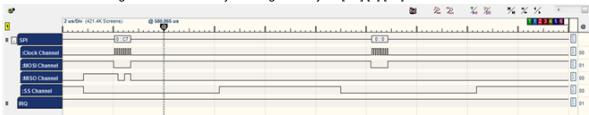

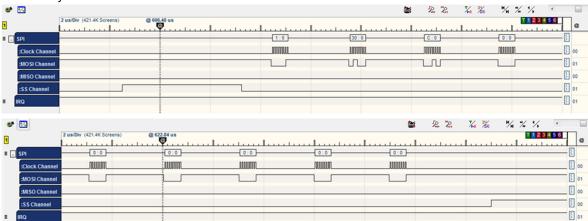

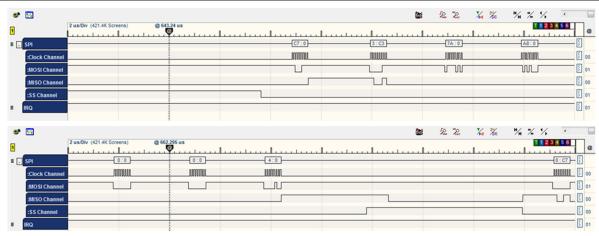

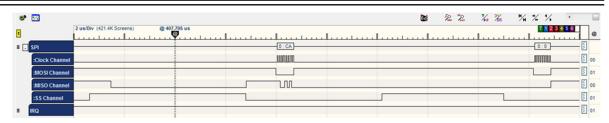

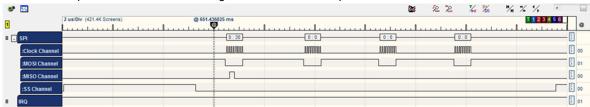

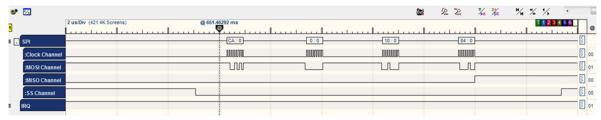

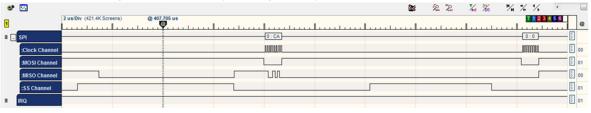

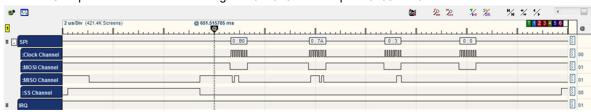

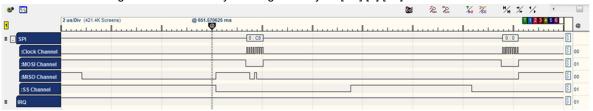

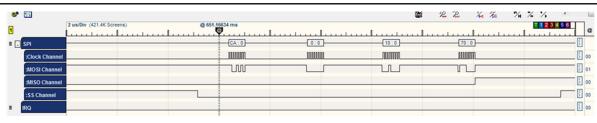

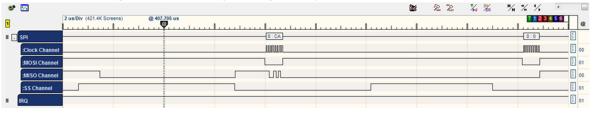

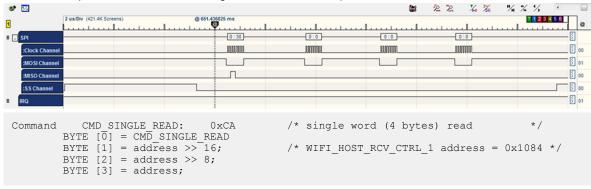

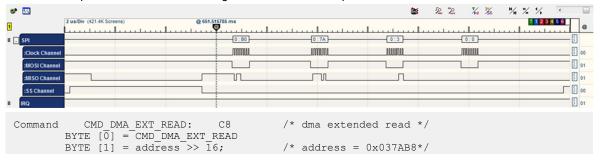

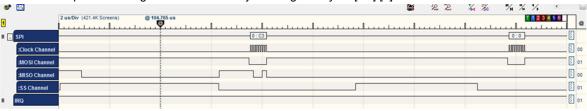

| 14. | WINC     | SPI Protocol                                   | 87    |

|     | 14.1.    | Introduction                                   | 87    |

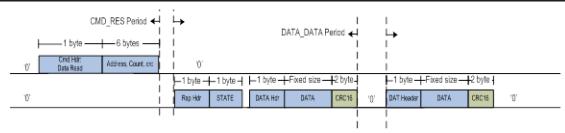

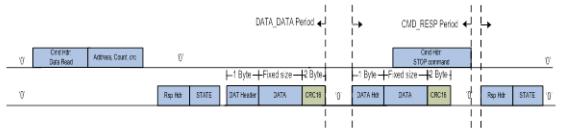

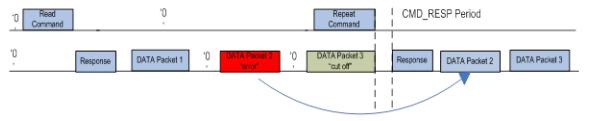

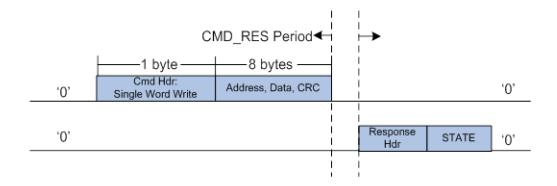

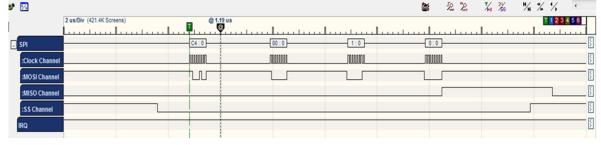

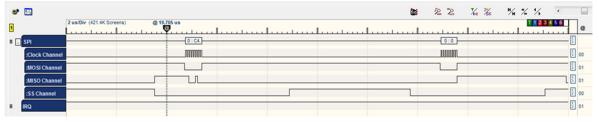

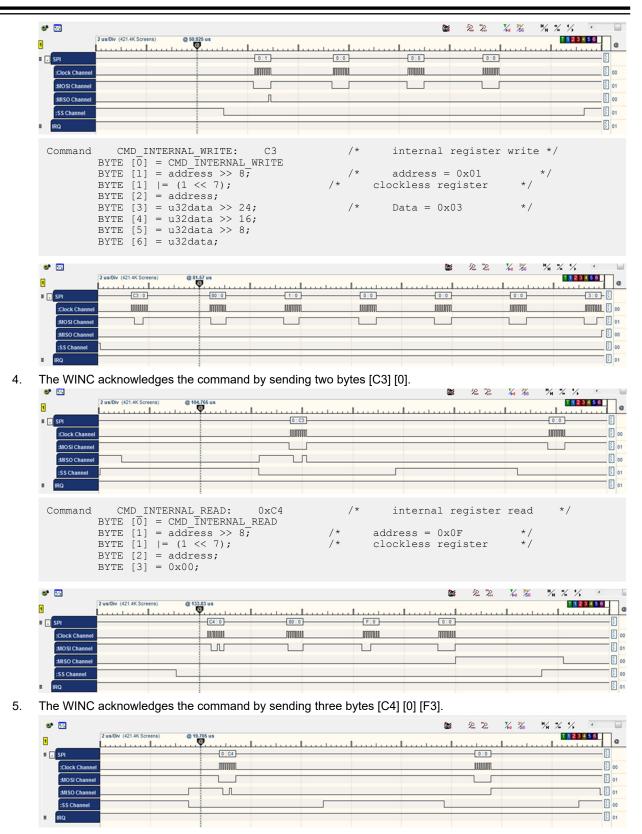

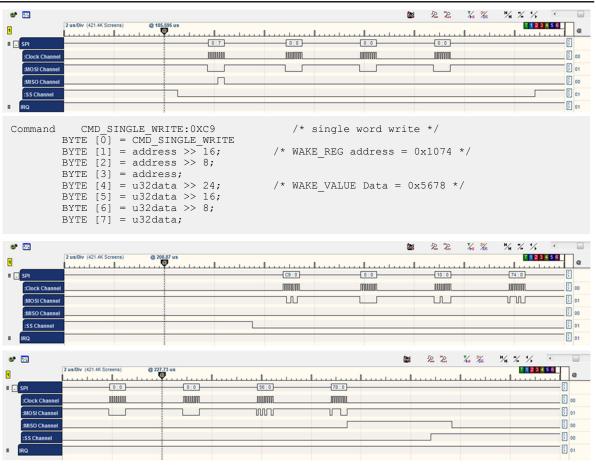

|     | 14.2.    | Message Flow for Basic Transactions            | 98    |

|     | 14.3.    | SPI Level Protocol Example                     | .101  |

| 15. | Apper    | dix A. How to Generate Certificates            | .123  |

|     | 15.1.    | Introduction                                   | .123  |

|     | 15.2.    | Steps                                          | . 123 |

|     | 15.3.    | Limitations                                    | . 123 |

| 16. | Apper    | dix B. X.509 Certificate Format and Conversion | .124  |

|     | 16.1.    | Introduction                                   | .124  |

|     | 16.2.    | Conversion Between Different Formats           | 124   |

| 17. | Refere   | ences                                          | .125  |

| 18. | Docur    | nent Revision History                          | .126  |

| The | Micro    | chip Website                                   | .127  |

| Pro | duct C   | nange Notification Service                     | .127  |

| Cus | tomer    | Support                                        | . 127 |

| Mic | rochip   | Devices Code Protection Feature                | . 127 |

| Leg | al Noti  | pe                                             | 128   |

| Tra | demark   | s                                              | 128   |

| Qua | ality Ma | nagement System                                | . 129 |

| Wo  | rldwida  | Sales and Service                              | 130   |

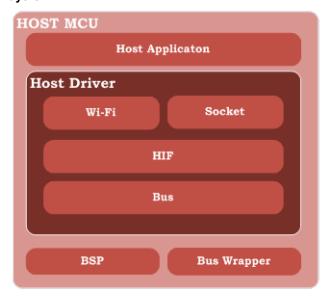

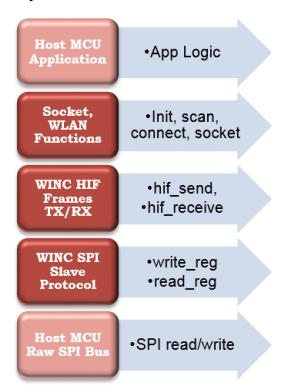

## 1. Host Driver Architecture

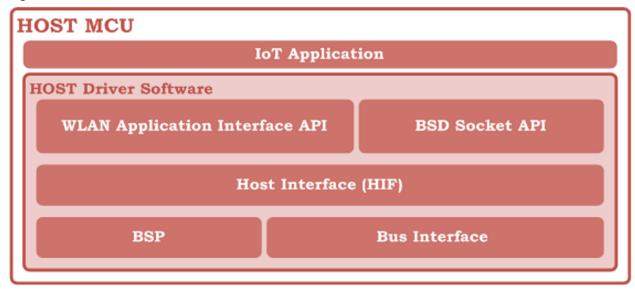

The following figure shows the architecture of the WINC host driver software, which runs on the host MCU.

Figure 1-1. Host Driver Software Architecture

The ATWINC15x0 host driver software is a C library, which provides the host MCU application with necessary APIs to perform necessary WLAN and socket operations. The components of the host driver are described in the following sub-sections.

### 1.1 WLAN API

This module provides an interface to the application for all Wi-Fi operations and any non-IP related operations.

This includes the following services:

- · Wi-Fi STA management operations

- Wi-Fi scan

- Wi-Fi connection management (connect, disconnect, connection status, and so on)

- WPS activation/deactivation

- · Wi-Fi AP enable/disable

- · Wi-Fi power save control API

This interface is defined in the  $m2m\_wifi.h$  file.

#### 1.2 Socket API

This module provides the socket communication APIs that are mostly compliant with the well-known BSD sockets to enable rapid application development. To comply with the nature of the MCU application environment, there are differences in API prototypes and in usage of some APIs between the WINC sockets and BSD sockets.

This interface is defined in the socket.h file.

The detailed description of the socket operations is provided in Socket Programming.

## 1.3 Host Interface (HIF)

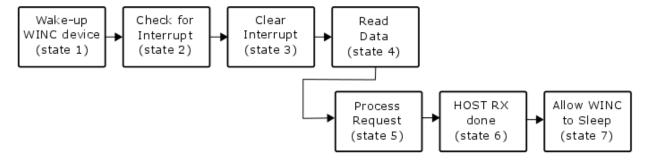

The HIF is responsible for handling the communication between the host driver and the WINC firmware. This includes interrupt handling, DMA and HIF command/response management. The host driver communicates with the firmware in the form of commands and responses formatted by the HIF layer.

The interface is defined in the m2m hif.h file.

The detailed description of the HIF design is provided in Host Interface Protocol.

## 1.4 Board Support Package (BSP)

The Board Support Package abstracts the functionality of a specific host MCU platform. This allows the driver to be portable to a wide range of hardware and hosts. Abstraction includes: pin assignment, power on/off sequence, reset sequence and peripheral definitions (Push buttons, LEDs, and so on).

The minimum required BSP functionality is defined in the nm bsp.h file.

#### 1.5 Serial Bus Interface

The Serial Bus Interface module abstracts the hardware associated with implementing the bus between the Host and the WINC. The serial bus interface abstracts I2C, SPI, or UART bus (Currently, host driver supports only SPI bus interface). The basic bus access operations (Read and Write) are implemented in this module as appropriate for the interface type and the specific hardware.

The bus interface APIs are defined in the nm\_bus\_wrapper.h file.

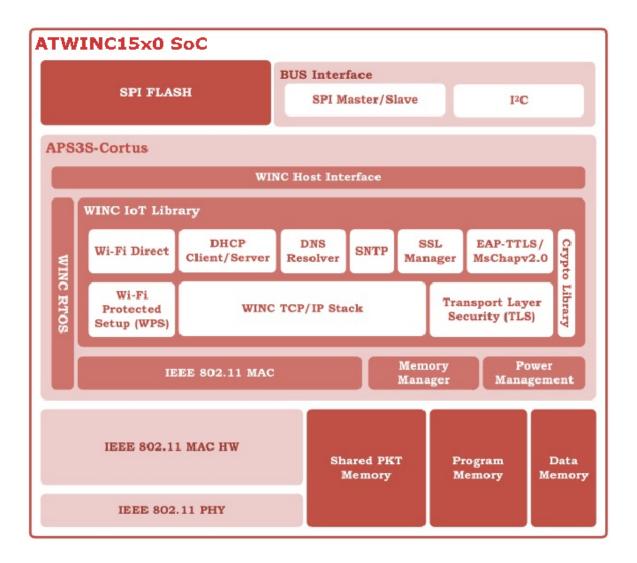

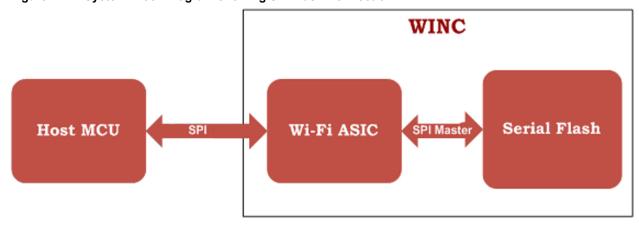

## 2. ATWINC15x0 System Architecture

The following figure shows the ATWINC15x0 system architecture. In addition to its built-in Wi-Fi IEEE-802.11 physical layer and RF front end, the WINC ASIC contains an embedded APS3S-Cortus 32-bit CPU to run the WINC firmware. The firmware comprises the Wi-Fi IEEE-802.11 MAC layer and embedded protocol stacks which offload the host MCU. The components of the system are described in the following sub-sections.

Figure 2-1. ATWINC15x0 System Architecture

## 2.1 Bus Interface

Hardware logic for the supported bus types for the ATWINC15x0 communications.

Note: SPI is currently the bus interface supported by the Host Driver.

## 2.2 Nonvolatile Storage

The ATWINC1510 has an integrated 8 Mb and the ATWINC1500 has an integrated 4 Mb serial Flash inside the WINC package (SIP). This stores the WINC firmware image and can store a second image to support OTA. It also stores information used by the WINC firmware in the run-time.

The detailed description of the serial Flash is provided in WINC Serial Flash Memory.

## 2.3 CPU

The SoC contains an APS3S-Cortus 32-bit CPU running at 40 MHz clock speed which executes the embedded WINC firmware.

### 2.4 IEEE 802.11 MAC Hardware

The SoC contains a hardware accelerator to ensure fast and compliant implementation of the IEEE 802.11 MAC layer and associated timing. It offloads IEEE 802.11 MAC functionality from firmware to improve performance and boost the MAC throughput. The accelerator includes hardware encryption/decryption of Wi-Fi traffic and traffic filtering mechanisms to avoid unnecessary processing in software.

### 2.5 Program Memory

128 KB Instruction RAM is provided for execution of the ATWINC15x0 firmware code.

## 2.6 Data Memory

64 KB RAM is provided for the ATWINC15x0 firmware data storage.

## 2.7 Shared Packet Memory

128 KB memory is provided for TX/RX packet management. It is shared between the MAC hardware and the CPU. This memory is managed by the Memory Manager SW component.

#### 2.8 IEEE 802.11 MAC Firmware

The system supports IEEE 802.11 b/g/n Wi-Fi MAC including WEP and WPA/WPA2 security supplicant. Between the MAC hardware and the firmware, a full range of IEEE 802.11 features are implemented and supported including beacon generation and reception, control packet generation and reception, and packet aggregation and deaggregation.

## 2.9 Memory Manager

The memory manager is responsible for the allocation and de-allocation of memory chunks in both shared packet memory and data memory.

## 2.10 Power Management

The Power Management module is responsible for handling different Power Save modes supported by the WINC and coordinating these modes with the Wi-Fi transceiver.

#### 2.11 WINC RTOS

The firmware includes a low-footprint real-time scheduler which allows concurrent multi-tasking on the ATWINC15x0 CPU. The ATWINC15x0 RTOS provides semaphores and timer functionality.

## 2.12 WINC IoT Library

The WINC IoT library provides a set of networking protocols in the WINC firmware. It offloads the host MCU from networking and transport layer protocols. The following sections describe the components of the WINC IoT library.

#### 2.12.1 WINC TCP/IP STACK

The WINC TCP/IP is an IPv4.0 stack based on the uIP (pronounced micro IP) TCP/IP stack.

uIP is a low footprint TCP/IP stack which has the ability to run on a memory-constrained microcontroller platform. It was originally developed by Adam Dunkels, licensed under a BSD style license, and further developed by a wide group of developers. The WINC TCP/IP stack is a customized version of the original uIP implementation which has several enhancements to boost TCP and UDP throughput.

#### 2.12.2 DHCP CLIENT/SERVER

A DHCP client is embedded in the WINC firmware that can automatically obtain an IP configuration after connecting to a Wi-Fi network.

The WINC firmware provides an instance of a DHCP server that automatically starts when the WINC AP mode is enabled. When the host MCU application activates the AP mode, it is allowed to configure the DHCP Server IP address pool range within the AP configuration parameters.

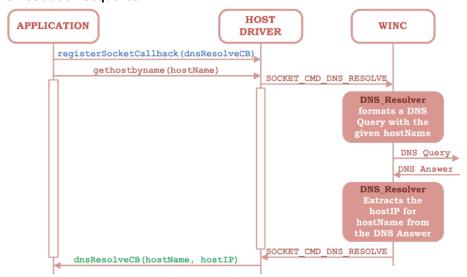

#### 2.12.3 DNS RESOLVER

The WINC firmware contains an instance of an embedded DNS resolver. This module can return an IP address by resolving the host domain names supplied with the socket API call gethostbyname.

#### 2.12.4 SNTP

The SNTP (Simple Network Time Protocol) module implements an SNTP client used to synchronize the WINC internal clock to the UTC clock.

#### 2.12.5 Enterprise Security

The Enterprise Security module implements the following authentication protocols for establishing a Wi-Fi connection with an AP by WPA/WPA2-Enterprise Security.

- · EAP with TLS

- EAP-PEAPv0/v1 with MSCHAPV2

- EAP-TTLSv0 with MSCHAPv2

- EAP-PEAPv0/v1 with MSCHAPv2

#### 2.12.6 TRANSPORT LAYER SECURITY

For TLS implementation, refer to Section 7 "Transport Layer Security (TLS)" for details.

#### 2.12.7 WI-FI PROTECTED SETUP

For WPS protocol implementation, refer to Section 10.3 "Wi-Fi Protected Setup (WPS)" for details.

#### 2.12.8 CRYPTO LIBRARY

The Crypto Library contains a set of cryptographic algorithms used by the common security protocols. This library has an implementation of the following algorithms:

- MD4 Hash algorithm (used only for MsChapv2.0 digest calculation)

- · MD5 Hash algorithm

## ATWINC15x0 System Architecture

- SHA-1 Hash algorithm

- SHA-256 Hash algorithm

- DES Encryption (used only for MsChapv2.0 digest calculation)

- MS-CHAPv2.0 (used as the EAP-TTLS inner authentication algorithm)

- MS-CHAPv2.0 (used as the EAP-PEAP and EAP-TTLS inner authentication algorithm)

- AES-128, AES-256 Encryption (used for securing WPS and TLS traffic)

- BigInt module for large integer arithmetic (for Public Key Cryptographic computations)

- RSA Public Key cryptography algorithms (includes RSA Signature and RSA Encryption algorithms)

## 3. WINC Initialization and Simple Application

After powering-up the WINC device, a set of synchronous initialization sequences must be executed, for the correct operation of the Wi-Fi functions. This chapter aims to explain the different steps required during the initialization phase of the system. After initialization, the host MCU application is required to call the WINC driver entry point to handle events from the WINC firmware.

- · BSP Initialization

- · WINC Host Driver Initialization

- · Socket Layer Initialization

- · Call WINC Driver Entry Point

Note: The initialization sequence must be completed to successfully operate the WINC start-up procedure.

#### 3.1 BSP Initialization

The BSP is initialized by calling the nm bsp init API. The BSP initialization routine performs the following steps:

- Resets the WINC<sup>1</sup> using the corresponding host MCU control GPIOs.

- Initializes the host MCU GPIO which connects to the WINC interrupt line. It configures the GPIO as an interrupt source to the host MCU. During runtime, the WINC interrupts the host to notify the application of events and data pending inside the WINC firmware.

- Initializes the host MCU delay function used within nm bsp sleep implementation.

#### 3.2 WINC Host Driver Initialization

The WINC host driver is initialized by calling the m2m\_wifi\_init API. The host driver initialization routine performs the following steps:

- Initializes the bus wrapper and SPI peripheral. The compilation flag CONF\_WINC\_USE\_SPI must be enabled in conf\_winc.h (bus interfaces CONF\_WINC\_USE\_UART and CONF\_WINC\_USE\_I2C are currently not supported).

- Registers an application-defined Wi-Fi event handler.

- · Initializes the driver and ensures compatibility between the WINC firmware version and the driver version.

- · Initializes the host interface and the Wi-Fi layer and registers the BSP Interrupt.

Note: A Wi-Fi event handler is required for the correct operation of any WINC application.

## 3.3 Socket Layer Initialization

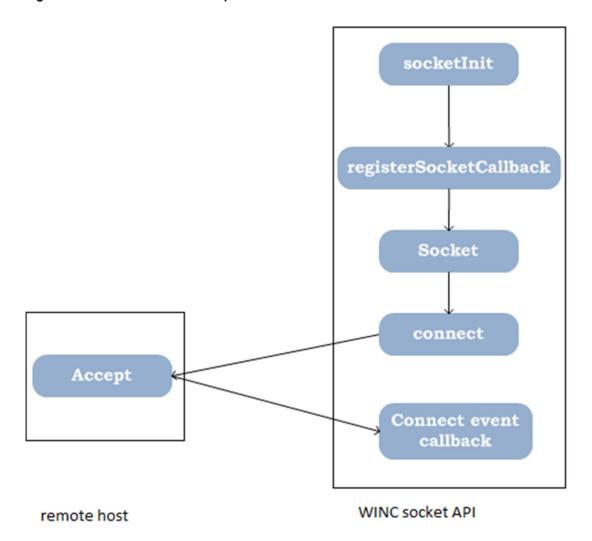

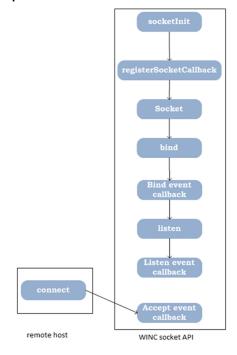

Socket layer initialization is carried out by calling the <code>socketInit</code> API. It must be called prior to any socket activity. For more information about socket initialization and programming, refer to WINC Sockets API.

## 3.4 WINC Event Handling

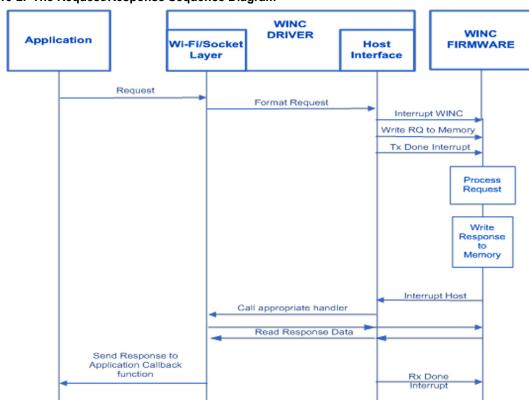

The WINC host driver API allows the host MCU application to interact with the WINC firmware. To facilitate interaction, the WINC driver implements the Host Interface (HIF) Protocol as described in **Section 15** "Host Interface (HIF) Protocol". The HIF protocol defines how to serialize and de-serialize API requests and response callbacks over the serial bus interface SPI (I2C and UART are currently not supported).

Refer to the ATWINC15x0-MR210xB Data Sheet (DS70005304) for more information about the hardware power-up/down sequence.

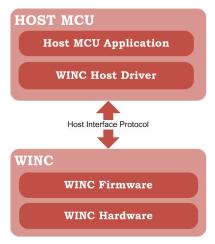

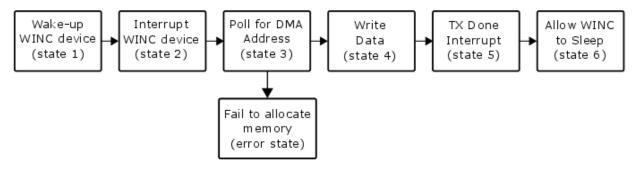

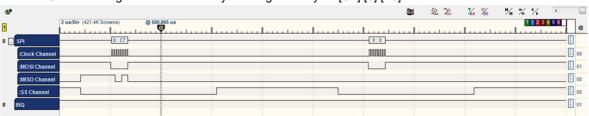

Figure 3-1. WINC System Architecture

The WINC host driver API provides services to the host MCU applications that are mainly divided in two major categories: Wi-Fi control services and Socket services. The Wi-Fi control services allow actions such as channel scanning, network identification, connection and disconnection. The Socket control services allow application data transfer once a Wi-Fi connection is established.

#### 3.4.1 Asynchronous Events

Some APIs in the ATWINC15x0 host driver are synchronous function calls, where the result is ready by the return of the function. However, most API functions in the ATWINC15x0 host driver are asynchronous. This means that when the application calls an API to request a service, the call is non-blocking and returns immediately, before the requested action is completed. When completed, a notification is provided in the form of a HIF protocol message from the WINC firmware to the host which, in turn, is delivered to the application via a callback<sup>2</sup> function. Asynchronous operation is essential when the requested service such as Wi-Fi connection may take significant time to complete. In general, the ATWINC15x0 firmware uses asynchronous events to signal the host driver about status change or pending data.

The HIF uses push architecture where the data and events are pushed from the ATWINC15x0 firmware to the host MCU in a First-Come First-Served (FCFS) manner. For instance, the host MCU application has two open sockets: socket 1 and socket 2. If the ATWINC15x0 receives socket 1 data followed by socket 2 data, then HIF delivers socket data in two HIF protocol messages in the order in which it is received. HIF does not allow reading socket 2 data before socket 1 data.

### 3.4.2 Interrupt Handling

The HIF interrupts the host MCU when one or more events are pending in the ATWINC15x0 firmware. The host MCU application is a big state machine which processes received data and events when the ATWINC15x0 driver calls the event callback function(s). To receive event callbacks, the host MCU application is required to call the  $m2m\_wifi\_handle\_events$  API to let the host driver retrieve and process the pending events from the ATWINC15x0 firmware. It is recommended to call this function if any of the following events occur:

- The host MCU application polls the API in main loop or a dedicated task

- When the host MCU receives an interrupt from the ATWINC15x0 firmware

Note: All the application-defined event callback functions registered with the ATWINC15x0 driver run in the context  $m2m\_wifi\_handle\_events$  API.

The above HIF architecture allows the ATWINC15x0 host driver to be flexible to run in the following configurations:

• Host MCU with no operating system configuration – the MCU main loop is responsible to handle deferred work from the interrupt handler

<sup>&</sup>lt;sup>2</sup> The callback is C function which contains an application-defined logic. The callback is registered using the ATWINC15x0 host driver registration API to handle the result of the requested service.

Host MCU with operating system configuration – a dedicated task or thread is required to call m2m wifi handle events to handle deferred work from the interrupt handler

#### Notes:

- 1. Host driver entry point m2m\_wifi\_handle\_events is **non-reentrant**. In the operating system configuration, it is required to protect the host driver from reentrance by a synchronization object.

- 2. When the host MCU is polling m2m\_wifi\_handle\_events, the API checks for pending unhandled interrupt from the ATWINC15x0. If no interrupt is pending, it returns immediately. If an interrupt is pending, m2m\_wifi\_handle\_events sequentially reads all the pending HIF messages and dispatches the HIF message content to the respective registered callback. If a callback is not registered to handle the type of message, the HIF message content is discarded.

## 3.5 Example Code

The following example code shows the initialization flow, as described in the previous sections.

```

static void wifi_cb(uint8_t u8MsgType, void *pvMsg)

{

int main (void)

{

tstrWifiInitParam param;

nm_bsp_init();

m2m_memset((uint8*)&param, 0, sizeof(param));

param.pfAppWifiCb = wifi_cb;

/*intilize the WINC Driver*/

ret = m2m_wifi_init(&param);

if (M2M_SUCCESS != ret) {

M2M_ERR("Driver Init Failed <%d>\n",ret);

while(1);

}

while(1) {

/* Handle the app state machine plus the WINC event handler */

while(m2m_wifi_handle_events(NULL) != M2M_SUCCESS) {

}

}

}

```

## 4. ATWINC15x0 Configuration

The ATWINC15x0 firmware offers a set of configurable parameters that control its behavior. There is a set of APIs provided to the host MCU application to configure these parameters. The configuration APIs are categorized according to their functionality, into device, network and power saving parameters.

Any parameters left unset by the host MCU application use their default values assigned during the initialization of the ATWINC15x0 firmware. A host MCU application needs to configure its parameters when coming out of cold boot or when a specific configuration change is required.

#### 4.1 Device Parameters

## 4.1.1 System Time

It is important to set the WINC system to UTC time to ensure a proper validity check of the X509 certificate expiration date. Since the WINC does not contain a built-in Real-Time Clock (RTC), there are two ways to obtain UTC time:

- Using the internal SNTP client this is enabled by default in the WINC firmware at start-up. The SNTP client synchronizes the WINC system clock to the UTC time from the time servers. The NTP server that the SNTP client uses can be configured using the API m2m\_wifi\_configure\_sntp. The default NTP server used by the WINC is time.nist.gov. The SNTP client uses a default update cycle of one day.

- In case there is no response from the default NTP server time-c.nist.gov, a secondary NTP server pool.ntp.org is used by the WINC.

- From the host MCU RTC if the host MCU has an RTC, the application may disable the SNTP client by calling m2m\_wifi\_enable\_sntp(0) (by passing zero as the argument) after the WINC initialization. The application provisions the WINC system time by calling m2m\_wifi\_get\_sytem\_time() API which returns the locally stored (internal clock value) time.

- When the SNTP Client running on the ATWINC15x0 synchronizes the time, the ATWINC15x0 will post the M2M WIFI RESP GET SYS TIME event to the host.

#### 4.1.2 Firmware and Driver Version

During initialization (m2m\_wifi\_init), the host driver checks the compatibility between the driver and the WINC firmware. The relevant parameters are:

- M2M HIF MAJOR VALUE

- M2M HIF MINOR VALUE

Note: These parameters are stated in release note version information as "Host Interface Level: X.Y".

If the driver and the WINC firmware have the same values of M2M\_HIF\_MAJOR\_VALUE, then they are deemed compatible and m2m wifi init returns with M2M SUCCESS.

If the driver and the WINC firmware have different values of M2M\_HIF\_MAJOR\_VALUE, then they are deemed incompatible and m2m\_wifi\_init returns with M2M\_ERR\_FW\_VER\_MISMATCH. In this case, communication is limited; the only permitted communication is for the driver to request the WINC firmware to switch to the WINC firmware image in the inactive partition of WINC flash, via m2m\_wifi\_check\_ota\_rb and m2m ota switch firmware.

Example code to handle this situation is available in the driver file m2m ota.h.

#### 4.2 WINC Modes of Operation

The WINC firmware supports the following modes of operation:

- · Idle mode

- Wi-Fi STA mode

- Wi-Fi Hotspot (AP)

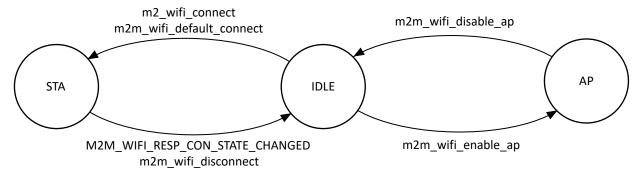

Figure 4-1. WINC Modes of Operation

#### 4.2.1 Idle Mode

After the host MCU application calls the ATWINC15x0 driver initialization <code>m2m\_wifi\_init</code> API, the ATWINC15x0 remains in Idle mode waiting for any command to change the mode or to update the configuration parameters. In this mode, the ATWINC15x0 enters into Power Save mode which disables the IEEE 802.11 radio and all unneeded peripherals and suspends the ATWINC15x0 CPU. If the ATWINC15x0 receives any configuration commands from the host MCU, it updates the configuration, sends back the response to the host MCU, and then returns to the Power Save mode.

#### 4.2.2 Wi-Fi Station Mode

The ATWINC15x0 enters Station (STA) mode when the host MCU requests connection to an AP using the m2m wifi connect or m2m wifi default connect APIs.

Note: m2m wifi connect is deprecated from v19.6.1 and above. For more details, see 5.3 Wi-Fi Security.

The ATWINC15x0 exits STA mode when it receives a disconnect request from the Wi-Fi AP conveyed to the host MCU application via the event callback M2M\_WIFI\_RESP\_CON\_STATE\_CHANGED or when the host MCU application decides to terminate the connection via m2m wifi disconnect API.

**Note:** The supported API functions in this mode use the HIF command types: tenuM2mConfigCmd and tenuM2mStaCmd. See the full list of commands in the m2m types.h header file.

For more information about STA mode, refer to Wi-Fi Station Mode.

## 4.2.3 Wi-Fi Hotspot (AP) Mode

In AP mode, the WINC allows Wi-Fi stations to connect and obtain the IP address from the WINC DHCP server. To enter AP mode, the host MCU application calls  $m2m\_wifi\_enable\_ap$  API. To exit AP mode, the application calls  $m2m\_wifi\_enable\_ap$  API.

The supported API functions in this mode use the HIF command types: tenuM2mApCmd and tenuM2mConfigCmd. See the full list of commands in the m2m types.h header file.

For more information about this mode, refer to Wi-Fi AP Mode.

#### 4.3 Network Parameters

#### 4.3.1 Wi-Fi MAC Address

The WINC firmware provides two methods to assign the WINC MAC address:

- Assignment from the host MCU this method occurs when the host MCU application calls the m2m wifi set mac address API after initialization using m2m wifi init API.

- Assignment from the WINC OTP (One-Time-Programmable) memory the WINC supports an internal MAC

address assignment method through a built-in OTP memory. If MAC address is programmed in the WINC OTP

memory, the WINC working MAC address defaults to the OTP MAC address unless the host MCU application

programmatically sets a different MAC address after initialization using the API m2m wifi set mac address.

#### Notes:

- OTP MAC address is programmed in the WINC OTP memory at the time of manufacturing.

- Use m2m\_wifi\_get\_otp\_mac\_address API to check if there is a valid programmed MAC address in the

WINC OTP memory. The host MCU application can also use the same API to read the OTP MAC address

octets. m2m\_wifi\_get\_otp\_mac\_address API not to be confused with the m2m\_wifi\_get\_mac\_address

API which reads the working WINC MAC address in the WINC firmware regardless from whether it is assigned

from the host MCU or from the WINC OTP.

- For more details on API, refer to the Atmel Software Framework for ATWINC1500 (Wi-Fi).

#### 4.3.2 IP Address

The ATWINC15x0 firmware uses the embedded DHCP client to automatically obtain an IP configuration after a successful Wi-Fi connection. DHCP is the preferred method and therefore it is used as a default method. After the IP configuration is obtained, the host MCU application is notified by the asynchronous event M2M\_WIFI\_REQ\_DHCP\_CONF.

Alternatively, the host MCU application can set a static IP configuration by calling the m2m\_wifi\_set\_static\_ip API. Before setting a static IP address, it is recommended to disable DHCP using the API m2m wifi enable dhcp(0) and then set the static IP as shown below.

```

In Main(), disable dhop after m2m wifi_init as shown below /* Initialize Wi-Fi driver with data and status callbacks. */

param.pfAppWifiCb = wifi cb;

ret = m2m wifi init(&param);

if (M2M SUCCESS != ret)

printf("main: m2m_wifi_init call error!(%d)\r\n", ret);

while (1)

{ }

m2m wifi enable dhcp(0);

Set Static IP when WINC is connected to AP as shown below.

static void wifi cb(uint8 t u8MsgType, void *pvMsg)

switch (u8MsgType) {

case M2M WIFI RESP CON STATE CHANGED:

tstrM2mWifiStateChanged *pstrWifiState = (tstrM2mWifiStateChanged *)pvMsg;

if (pstrWifiState->u8CurrState == M2M WIFI CONNECTED) {

printf("Wi-Fi connected\r\n");

tstrM2MIPConfig ip client;

ip client.u32StaticIP = htonl(0xc0a80167);

// Provide the required Static

ΤP

ip client.u32DNS = htonl(0xc0a80101);

// Provide DNS server details

ip client.u32SubnetMask = htonl(0xFFFFFF00);

// Provide the SubnetMask for

the currently connected AP

ip client.u32Gateway = htonl(0xc0a80101);

// Provide the GAteway IP for

the AP

printf("Wi-Fi setting static ip\r\n");

m2m wifi set static ip(&ip client);

```

## 4.4 Power Save Modes

The WINC firmware supports multiple Power Save modes which provide flexibility to the host MCU application to tweak the system power consumption. The host MCU can configure the WINC Power Saving policy using the m2m wifi set sleep mode and m2m wifi set lsn int APIs.

The WINC supports the following Power Save modes:

M2M PS MANUAL

- M2M\_PS\_DEEP\_AUTOMATIC

- M2M PS AUTOMATIC (deprecated, not be used in new implementations)

- M2M PS H AUTOMATIC (deprecated, not be used in new implementations)

Note: M2M PS DEEP AUTOMATIC mode recommended for most applications.

#### 4.4.1 M2M PS MANUAL

This is a fully host-driven Power Save mode.

- The WINC sleeps when the host uses the m2m\_wifi\_request\_sleep API. During this period, the host MCU can also sleep for extended durations.

- The WINC wakes up when the host MCU application requests services from the WINC by calling any host driver API function, for example, Wi-Fi or socket operation.

**Note:** In M2M\_PS\_MANUAL mode, when the WINC sleeps due to m2m\_wifi\_request\_sleep API, the WINC does not wake up to receive and monitor AP beacon. Beacon monitoring is resumed when the host MCU application wakes up the WINC.

For an active Wi-Fi connection, the AP may exit the connection if the WINC is unavailable due to long sleep time. If connection is dropped, the WINC detects the disconnection on the next wake-up cycle and notifies the host to reconnect to the AP again. To maintain an active Wi-Fi connection for extended durations, the host MCU application must periodically wake up the WINC in order to send a keep-alive Wi-Fi frame to the AP. The host must carefully choose the sleep period to satisfy the tradeoff between keeping the Wi-Fi connection uninterrupted and minimizing the system power consumption.

This mode is useful for applications which send notifications very rarely due to a certain trigger. It also fits applications which periodically send notifications with a very long spacing between notifications. Careful power planning is required when using this mode. If the host MCU decides to sleep for a longer period, it may use M2M\_PS\_MANUAL or may power off the WINC³. The advantage of this mode compared to powering off the WINC is that M2M\_PS\_MANUAL saves the time required for the WINC firmware to boot since the firmware is always loaded in the WINC memory. The real advantage and disadvantage depend on the nature of the application. In some applications, the sleep duration can be long enough to be a power-efficient decision to power off the WINC and then power it on again and reconnect to the AP when the host MCU wakes up. In other situations, a latency-sensitive application may choose to use M2M\_PS\_MANUAL to avoid the WINC firmware boot latency on the expense of slightly increased power consumption.

During the WINC Sleep mode, the WINC in M2M\_PS\_MANUAL mode saves more power than M2M\_PS\_DEEP\_AUTOMATIC mode. In M2M\_PS\_MANUAL mode, the WINC skips beacon monitoring whereas in M2M\_PS\_DEEP\_AUTOMATIC mode, it wakes up to receive beacons. The comparison also includes the effect of the host MCU sleep duration: if the host MCU sleeps for a longer period, the Wi-Fi connection may frequently drop and the power advantage of the M2M\_PS\_MANUAL mode is lost due to the power consumed in the Wi-Fi reconnection. In contrast, the M2M\_PS\_DEEP\_AUTOMATIC mode can keep the Wi-Fi connection for long durations at the expense of waking up the WINC to monitor the AP beacon.

#### 4.4.2 M2M PS AUTOMATIC

This mode is deprecated and kept for backward compatibility and development reasons. It is not recommended to use in new implementations.

#### 4.4.3 M2M PS H AUTOMATIC

This mode is deprecated and kept for backward compatibility and development reasons. It is not recommended to use in new implementations.

#### 4.4.4 M2M PS DEEP AUTOMATIC

This mode implements the Wi-Fi standard power-saving method in the WINC module. The WINC sleeps and periodically wakes up to monitor AP beacons. The AP is required to buffer data while stations are in Power Save mode and transmit data when stations wake-up. The AP periodically transmits a beacon frame to synchronize with a

Refer to the ATWINC15x0-MR210xB Data Sheet (DS70005304) for more information about the hardware power-up/down sequence.

## ATWINC15x0 Configuration

network for every beacon period. A station, which is in Power Save mode, periodically wakes up to receive the beacon. The beacon conveys information to the station about pending unicast data, which are buffered inside the AP while the station was in Sleep mode. The beacon also provides information about the broadcast/multicast data.

In this mode, the WINC module enters into Sleep state by turning off the IEEE 802.11 radio, MAC, and system clock. Prior to entering the Sleep mode, the ATWINC15x0 programs a hardware timer (running on an internal low-power oscillator) with a sleep period determined by the WINC firmware power management module.

Any of the following events can wake-up the WINC module from Sleep state:

- · Expiry of the hardware sleep timer. The WINC wakes up to receive the upcoming beacon from AP.

- The WINC wakes up<sup>4</sup> when the host MCU application requests services from the WINC by calling any host driver API function, for example, Wi-Fi or socket operation.

## 4.5 Configuring Listen Interval and DTIM Monitoring

The WINC allows the host MCU application to tweak system power consumption by configuring beacon monitoring parameters. The AP periodically send beacons for every *DTIM period* (for example, 100 ms). The beacon contains a *TIM element* which informs the station about the unicast data for the station that are buffered in the AP. The station negotiates with the AP for a *listen interval*. The listen interval tells the AP for how many beacon periods the station will sleep before it wakes up to receive data buffered in the AP. Some APs might drop buffered data after Listen Interval elapses if the data is not retrieved by the station.

The WINC driver allows the host MCU application to configure beacon monitoring parameters as follows:

- Configure DTIM monitoring that is to enable or disable reception of broadcast/multicast data using the following API:

- m2m\_wifi\_set\_sleep\_mode(desired\_mode, 1) to receive broadcast data

m2m wifi set sleep mode(desired mode, 0) to ignore broadcast data

- Configure the listen interval using the m2m wifi set lsn int API

**Note:** The listen interval value provided to the m2m\_wifi\_set\_lsn\_int API is expressed in the unit of beacon period. Also, the host application cannot fetch the DTIM period received by the WINC from the AP.

<sup>&</sup>lt;sup>4</sup> The wake-up sequence is internally handled in the WINC host driver by the hif\_chip\_wake API. Refer to Section 15 "Host Interface Protocol" for more information.

## 5. Wi-Fi Station Mode

This chapter provides information about the WINC Wi-Fi Station (STA) mode as described in Wi-Fi Station Mode. The STA mode involves a scan operation; association to an AP using parameters (SSID and credentials) provided by the host MCU or using AP parameters stored in the WINC nonvolatile storage (default connection). The chapter also provides information about supported security modes along with code examples.

## 5.1 Scan Configuration Parameters

#### 5.1.1 Scan Region

The number of RF channels supported varies by geographical region. For example, 13 channels are supported in Asia while 11 channels are supported in North America. By default, the WINC initial region configuration is equal to 14 channels, but this can be changed by setting the scan region using the m2m\_wifi\_set\_scan\_region API. The scan region can be selected from the enum tenuM2mScanRegion.

## 5.1.2 Scan Options

During Wi-Fi scan operation, the WINC sends probe request Wi-Fi frames and waits for the scan wait time to receive probe response frames in the current Wi-Fi channel. After the scan wait time, the WINC switches to the next channel. Increasing the scan wait time increases the possibility to detect more number of access points during scan operation but this leads to more power consumption and overall scan duration. The WINC firmware default scan wait time is optimized to provide the tradeoff between the power consumption and scan accuracy. The WINC firmware provides flexible configuration options to allow the host MCU application to set the scan time. For more details, refer to the m2m wifi set scan options API.

#### 5.2 Wi-Fi Scan

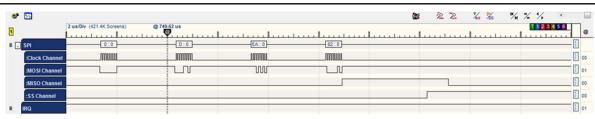

A Wi-Fi scan operation can be initiated by calling the m2m\_wifi\_request\_scan API. The scan can be performed on all 2.4GHz Wi-Fi channels or on a specific requested channel.

The scan response time depends on the scan options which can be set by calling  $m2m\_wifi\_set\_scan\_options$  (tstrM2MScanOption\* ptstrM2MScanOption). For instance, if the host MCU application requests to scan all channels, the scan time is equal to NoOfChannels (13) \*ptstrM2MScanOption->u8NumOfSlot\*ptstrM2MScanOption->u8SlotTime.

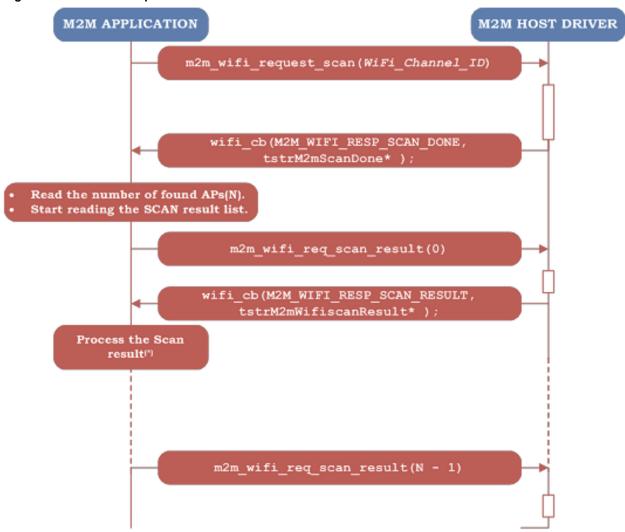

The scan operation is illustrated in the following figure.

Figure 5-1. Wi-Fi Scan Operation

## 5.3 Wi-Fi Security

The following types of security are supported in the WINC Wi-Fi STA mode.

- OPEN

- WEP (Wired Equivalent Protocol)

- WPA/WPA2 (Wi-Fi Protected Access Personal Security mode that is Passphrase)

- 802.1X (WPA/WPA2-Enterprise security)

For 802.1X Enterprise Security, the following authentication methods are supported from ATWINC1500 firmware version 19.6.1.

- EAP-TLS

- EAP-PEAPv0/TLS

- EAP-PEAPv1/TLS

- EAP-TTLSv0/MSCHAPv2

- EAP-PEAPv0/MSCHAPv2

- EAP-PEAPv1/MSCHAPv2

The m2m\_wifi\_connect is deprecated from v19.6.1 and above firmware. The legacy APIs m2m\_wifi\_connect and m2m\_wifi\_connect\_sc are available as wrappers for the new APIs. Functionally its behavior is unchanged from previously released drivers.

The recommended API for various security type such as OPEN, WEP, WPA/WPA2, 802.1X are summarized in the Table 5-1.

All new connect APIs, enable connection to a particular access point by specifying its BSSID and the SSID. To restrict connection to a specific access point, the application can specify the BSSID (in addition to SSID) in the argument tstrNetworkId -> pu8Bssid.

The application can instruct the WINC whether to store the credentials or not to store in Flash and also whether the saved credentials must be encrypted or not. This is done by configuring the <code>enum tenuCredStoreOption</code>.

For enterprise security, the application can configure WINC to send actual identity or use anonymous identity during phase 1 authentication. This can be done by setting or clearing bUnencryptedUserName in argument tstrAuth1xTls or tstrAuth1xMschap2.

For more details on usage of API m2m\_wifi\_connect\_1x\_tls, refer ASF (v3.42 or above) example "WINC1500 Connecting a EAP-TLS / PEAPv0 with TLS / PEAPv1 with TLS Secured AP Example".

For more details on usage of API m2m\_wifi\_connect\_1x\_mschap2, refer ASF (v3.42 or above) example "WINC1500 Connecting a EAP-TTLSv0 with MSCHAPv2 / EAP-PEAPv0 with MSCHAPv2 / EAP-PEAPv1 with MSCHAPv2 Secured AP Example".

#### 5.4 On Demand Wi-Fi Connection

The host MCU application may establish a Wi-Fi connection on demand when all the required connection parameters (SSID, security credentials, and so on.) are known to the application. To start a Wi-Fi connection on demand, the application calls the following APIs based on the security type.

Table 5-1. List of APIs based on Security Type

| Security Type        | API                         |

|----------------------|-----------------------------|

| Open                 | m2m_wifi_connect_open       |

| WEP                  | m2m_wifi_connect_wep        |

| WPA/WPA2             | m2m_wifi_connect_psk        |

| 802.1x with MSCHAPv2 | m2m_wifi_connect_1x_mschap2 |

| 802.1x with TLS      | m2m_wifi_connect_1x_tls     |

Alternatively, the application can call the API m2m\_wifi\_connect to connect with an access point which supports Open, WEP, WPA/WPA2 and 802.1x with MSCHAPv2. m2m\_wifi\_connect is deprecated in v19.6.1 and is kept for legacy purpose.

**Note:** Using the API in the Table 5-1 implies that the host MCU application has prior knowledge of the connection parameters. For instance, connection parameters can be stored on nonvolatile storage attached to the host MCU.

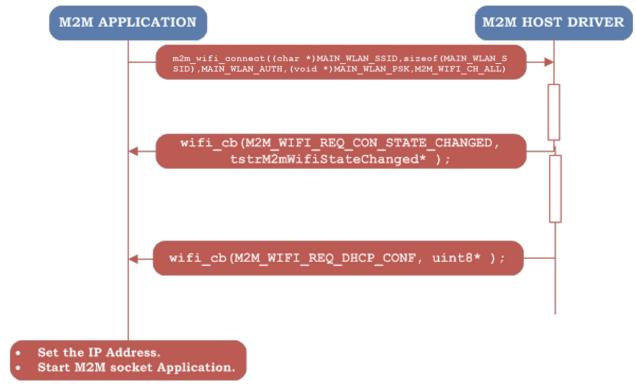

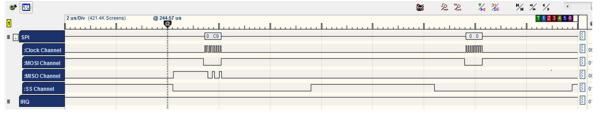

The Wi-Fi on demand connection operation is described in the following figure.

Figure 5-2. On-demand Wi-Fi Connection

#### 5.4.1 Example Code

## 5.4.1.1 Example Code for Connecting to Enterprise Network (PEAP and TTLSv0) with MSCHAPv2 as Phase2 Authentication

```

#define MAIN WLAN SSID

"WINC1500 ENTERPRISE" /**< Destination SSID */

#define MAIN WLAN 802 1X USR NAME

"DEMO USER" /**< RADIUS user account name */

#define MAIN_WLAN_802_1X_PWD

"DemoPassword" /**< RADIUS user account password */

int main(void)

int8 t ret;

tstr\overline{W}ifiInitParam\ param;

tstrNetworkId networkId;

tstrAuth1xMschap2 mschapv2 credential;

/* Initialize the board. */

system_init();

/* Initialize the UART console. */

configure console();

printf(STRING HEADER);

/* Initialize the BSP. */

nm_bsp_init();

/* Initialize Wi-Fi parameters structure. */

memset((uint8_t *)&param, 0, sizeof(tstrWifiInitParam));

/* Initialize Wi-Fi driver with data and status callbacks. */

param.pfAppWifiCb = wifi cb;

ret = m2m_wifi_init(&param);

if (M2M_SUCCESS != ret) {

printf("main: m2m wifi init call error!(%d)\r\n", ret);

while (1) {

}

```

```

networkId.pu8Bssid = NULL;

networkId.pu8Ssid = (uint8 *)MAIN WLAN SSID;

networkId.u8SsidLen = strlen(MAIN WLAN SSID);

networkId.enuChannel = M2M WIFI CH ALL;

mschapv2 credential.pu8Domain = NULL;

//mschapv2 credential.u16DomainLen = strlen(mschapv2 credential.pu8Domain);

mschapv2 credential.pu8UserName = (uint8 *)MAIN WLAN 802 1X USR NAME;

mschapv2_credential.pu8Password = (uint8 *)MAIN_WLAN_802_1X_PWD;

mschapv2 credential.u16UserNameLen = strlen(MAIN WLAN 802 1X USR NAME);

mschapv2 credential.u16PasswordLen = strlen(MAIN WLAN 802 1X PWD);

mschapv2_credential.bUnencryptedUserName = false;

mschapv2_credential.bPrependDomain = true;

printf("Connecting to %s\r\n\tUsername: %s\r\n", MAIN WLAN SSID,

MAIN WLAN 802 1X USR NAME);

m2m wifi connect 1x mschap2( WIFI CRED SAVE ENCRYPTED, &networkId, &mschapv2 credential);

/* Infinite loop to handle a event from the WINC1500. */

while (1) {

while (m2m wifi handle events(NULL) != M2M SUCCESS) {

return 0;

```

## 5.4.1.2 Example Code for Connecting to PEAP Enterprise Network with TLS as Phase2 Authentication and EAP- TLS

```

/** security information for Wi-Fi connection */

"WINC1500 ENTERPRISE" /**< Destination SSID */

#define MAIN WLAN SSID

"DEMO USER" /**< RADIUS user account name */

#define MAIN WLAN 802 1X USR NAME

const uint8 \bar{t} modulus\bar{t} = { \bar{t} private key modulus extracted from key file */ }; const uint8\bar{t} exponent[] = { \bar{t} private key exponent coefficient extracted from key file

*/ };

const uint8 t certificate[] = { /** certificate coefficient corresponding to Private Key

*/ };

int main (void)

int8 t ret;

tstrWifiInitParam param;

tstrNetworkId networkId;

tstrAuth1xTls tls credential;

/* Initialize the board. */

system init();

/* Initialize the UART console. */

configure console();

printf(STRING HEADER);

/* Initialize the BSP. */

nm_bsp_init();

/* Initialize Wi-Fi parameters structure. */

memset((uint8 t *)&param, 0, sizeof(tstrWifiInitParam));

/* Initialize Wi-Fi driver with data and status callbacks. */ param.pfAppWifiCb = wifi_cb;

ret = m2m wifi init(&param);

if (M2M S\overline{U}CCES\overline{S} != ret)

printf("main: m2m wifi init call error!(%d)\r\n", ret);

while (1) {

printf("Username:%s\r\n",MAIN WLAN 802 1X USR NAME);

/* Connect to the enterprise network. */

networkId.pu8Bssid = NULL;

networkId.pu8Ssid = (uint8 *)MAIN WLAN SSID;

networkId.u8SsidLen = strlen(MAIN WLAN SSID);

networkId.enuChannel = M2M WIFI CH ALL;

```

```

tls credential.pu8Domain = NULL;

tls credential.pu8UserName = (uint8 *)MAIN WLAN 802 1X USR NAME;

tls_credential.pu8PrivateKey_Mod = (uint8 *)modulus;

tls credential.pu8PrivateKey Exp = (uint8 *)exponent;

tls_credential.pu8Certificate = (uint8 *)certificate;

tls_credential.u16UserNameLen = strlen(MAIN_WLAN_802_1X_USR_NAME);

tls credential.u16PrivateKeyLen = sizeof(modulus);

tls_credential.u16CertificateLen = sizeof(certificate);

tls credential.bUnencryptedUserName = true;

tls credential.bPrependDomain = true;

printf("Connecting to %s...\r\n\t\tUsername:%s\r

\n", networkId.pu8Ssid, tls_credential.pu8UserName);

m2m wifi connect 1x tls(WIFI CRED SAVE ENCRYPTED, &networkId, &tls credential);

/* Infinite loop to handle a event from the WINC1500. */

while (1)

while (m2m wifi handle events(NULL) != M2M SUCCESS) {

}

return 0;

```

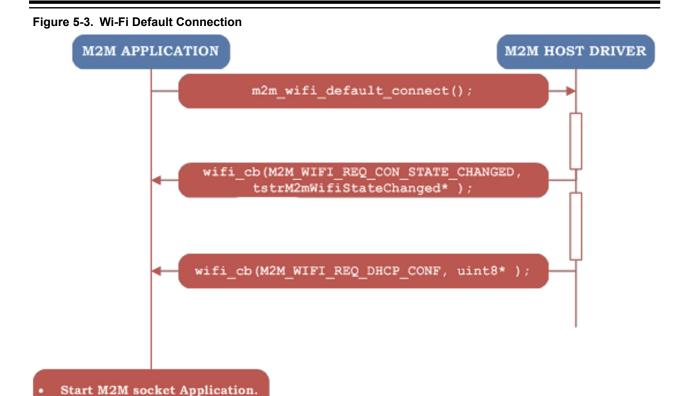

## 5.5 Default Connection

The host MCU application establishes the default connection based on the connection profile stored in the WINC serial Flash using the m2m\_wifi\_default\_connect API. This API does not require AP information to establish the connection.

**Note:** The connection profile information is automatically stored in the WINC Flash when on-demand Wi-Fi connection API is called (see Table 5-1). Saving of this connection profile is dependent on the <code>enumtenuCredStoreOption</code>.

The credentials such as passphrase of the AP or Enterprise certificate and other parameters like SSID, IP address, BSSID are encrypted using AES128-CBC before they are written into the serial Flash. This makes it difficult for an attacker to retrieve the sensitive information even if an attacker has physical access to the device. If there is no cached profile or if a connection cannot be established with any of the cached profile, an event of type M2M WIFI RESP DEFAULT CONNECT is delivered to the host driver indicating failure.

Upon successful default connection, the host application can read the current Wi-Fi connection status by calling  $m2m\_wifi\_get\_connection\_info$  API. The  $m2m\_wifi\_get\_connection\_info$  is an asynchronous API. The actual connection information is provided in the asynchronous event  $m2m\_wifi\_get\_connection\_info$  in Wi-Fi callback. The callback parameter of type tstrm2mConnInfo provides information about AP SSID, RSSI (AP received power level), security type, IP address obtained by DHCP.

**Note:** A connection profile is cached in the serial Flash if and only if the connection is successfully established with the target AP.

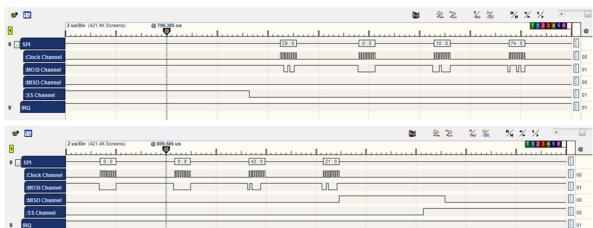

The Wi-Fi default connection operation is shown in the following figure.

## 5.6 Encrypted Credential Storage

In ATWINC15x0 firmware v19.6.1 and above, the credentials such as passphrase of the AP or Enterprise certificate and other parameters like SSID, IP address, BSSID are encrypted using AES128-CBC before they are written into the serial Flash. This makes it difficult for an attacker to retrieve the sensitive information inspite of having physical access to the device. The encryption provided by this feature must not be considered secure. The encryption is only intended to prevent credentials being revealed in plain text by an opportunistic read of ATWINC15x0 Flash. Therefore, other security practices must be followed where possible, such as changing passwords regularly and deleting credentials when they are no longer required.

When requesting for a connection to a network, the application can specify how the connection credentials must be stored in ATWINC15x0 Flash. The options are as follows:

- · Do not store credentials

- Store credentials unencrypted

- Store credentials encrypted

The credentials consist of:

- SSID

- BSSID (if provided)

- WEP key (for WEP connection)

- Passphrase and PSK (for WPA/WPA2 PSK connection)

- Domain, User name and Password (for WPA/WPA2 1x MSCHAPv2 connection)

- Domain, User name, Certificate and Private Key (for WPA/WPA2 1x TLS connection)

The credentials are stored in ATWINC15x0 Flash when connection succeeds, and only one set of credentials is stored at a time; if new credentials need to be stored then the old credentials are removed (overwritten with 0's).

If credentials are stored in ATWINC15x0 Flash, then the application can request subsequent connections without providing the credentials again, using m2m wifi default connect.

If roaming is enabled, roaming can take place regardless of whether the credentials are stored in ATWINC15x0 Flash. (They are stored in data memory for the duration of a connection.) The application can delete credentials from ATWINC15x0 Flash using  $m2m_wifi_delete_sc.$

**Notes:** Version 19.6.1 firmware implements a new format for the ATWINC15x0 Flash store for connection parameters. The effects of this are:

- During a firmware upgrade to v19.6.1, previously stored credentials are reformatted. After the first successful

connection to an access point, these stored credentials are encrypted.

- During a firmware upgrade to v19.6.1, previously stored IP address and Wi-Fi channel are deleted.

- After a firmware downgrade from v19.6.1 to previous firmware, credentials stored by v19.6.1 firmware are not readable by the previous firmware. The operation of the previous firmware is otherwise unaffected.

## 5.7 Simple Roaming

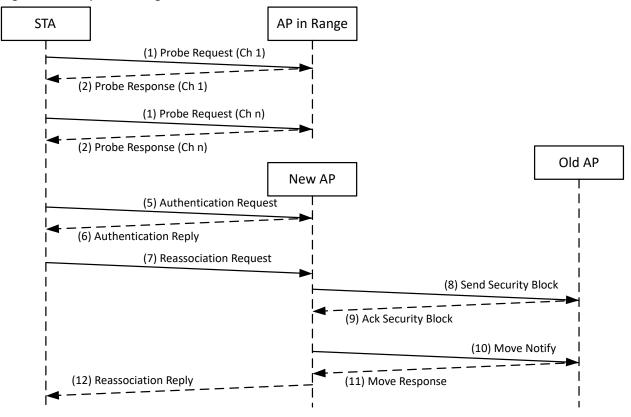

Simple Roaming is a custom feature which is supported by WINC firmware version 19.6.1 and above. With Simple Roaming feature enabled, the ATWINC1500 configured as station can move around in an ESS area with multiple access point. The WINC automatically switches to another AP which has the same SSID, authentication procedure and credentials with better signal strength. Roaming enables a station to change its AP while remaining connected to the network. The following figure explains the simple roaming feature.

Figure 5-4. Simple Roaming

In v19.6.1, the WINC roam occurs on link-loss detection with the existing AP, which is determined by tracking beacons and sending NULL frame keep-alive packets. ISO/OSI Layer 2 roaming occurs when the WINC roams from one AP to another AP, both of which are inside the same IP subnet. Layer 3 roaming occurs when the WINC roams from one AP to another AP which are in different subnets, whereby the WINC attempts to obtain a new IP address within the new subnet via DHCP. As a result of layer 3 roaming, any existing network connections is broken, and the upper layer protocols handle this IP address change if a continuous connection is required in layers 4 and above.

Roaming algorithm is internal to WINC firmware. The Host MCU can enable or disable the roaming functionality using the API's  $m2m\_wifi\_enable\_roaming$  and  $m2m\_wifi\_disable\_roaming$ . The roaming must be called after the WINC initialization.

When roaming is enabled, if the WINC successfully roamed to a new AP, then the M2M\_WIFI\_RESP\_CON\_STATE\_CHANGED message with state as M2M\_WIFI\_ROAMED is sent to host MCU. If the WINC is not able to find a new AP, then M2M\_WIFI\_RESP\_CON\_STATE\_CHANGED message with state as M2M WIFI DISCONNECTED is sent to the host MCU.

The API call m2m\_wifi\_enable\_roaming() sets the ATWINC15x0 to detect link-loss, and when link loss is detected with the existing access point, the following roaming steps are performed.

- · A precautionary de-authentication frame is sent to the old AP.

- · Scanning is performed to determine if there is an AP within the same ESS as the previous AP in the vicinity.

- If an AP is found, authentication and re-association messages are exchanged with the new AP, followed by a normal 4-way security handshake in the case of WPA/WPA2, or an EAPOL exchange in the case of 802.1x Enterprise security.

- A DHCP request is sent to the new AP to attempt to retain the same IP address. A notification event is sent to the host MCU of type M2M\_WIFI\_RESP\_CON\_STATE\_CHANGE with the state of M2M\_WIFI\_ROAMED.

Additionally, an M2M\_WIFI\_REQ\_DHCP\_CONF event conveying either the same or a new IP address is sent to the host MCU.

- If there is any problem with the connection, or DHCP fails, then a de-authentication message is sent to the AP, and an M2M\_WIFI\_RESP\_CON\_STATE\_CHANGED event is sent to the host MCU with the state set as M2M WIFI DISCONNECTED.

The bEnableDhcp parameter enables control of whether or not a DHCP request is sent after roaming to a new AP. The API call m2m wifi disable roaming is used to disable roaming.

## 5.8 Multiple Gain Table

There are restrictions regarding the maximum transmit power of a wireless device according to the regulatory agencies of the region. For Wi-Fi devices, the maximum transmit power is limited according the regulation of the region in which the Wi-Fi device is used. The gain table can be used to configure the transmission power in WINC. The digital gain (DG) that are used for different channels and different data rates are stored in ATWINC15x0 Flash as a table called Gain table. In ATWINC15x0, the Power Amplifier (PA) and Pre-power Amplifier (PPA) values are configured in the firmware directly.

The following figure shows the format of the gain table.

Figure 5-5. Gain Table

|       |      | 1        | 2         | 3  | 4        | 5        | 6  | 7        | 8  | 9  | 10       | 11         | 12  | 13       | 14 | <b>→</b> Channels |

|-------|------|----------|-----------|----|----------|----------|----|----------|----|----|----------|------------|-----|----------|----|-------------------|

|       | 1    | -10      | -9        | _  | 1        | -9       |    | -9       | -  | -9 | -        | -          | -9  | -        | -9 | )                 |

|       | 2    | -10      | _         |    | -        |          |    | -9       | _  |    | _        |            | _   | -        | -  |                   |

|       | 5.5  | -10      | _         |    | -        | -9       | _  | -9       | _  | _  | _        |            | _   | -        | -  |                   |

|       | 11   | -10      | -         | -  |          | -9       |    | -9       | -  |    | _        |            |     | -        | -9 |                   |

|       | 6    | -11      | -7        |    | -7       | -7       | -7 | -7       |    | -7 | -7       | -9         |     | -7       | -7 |                   |

|       | 9    | -11      | -7        | -7 |          | -7       | -7 | -7       | -7 | -7 | -7       | -9         |     |          |    |                   |

|       | 12   | -11      | -7        | -7 | -7       | -7       | -7 | -7       |    | -7 | -7       | -9         |     | -7       |    |                   |

|       | 18   | -11      | -7        | -7 |          | -7       | -7 | -7       |    | -7 |          | -9         |     | -        | •  |                   |

| Rates | 24   | -11      | -7        | -7 |          | -7       | -7 | -7       |    | -7 | -7       | -9         |     |          |    |                   |

| Rai   | 36   | -11      | -7        | -7 | -7       | -7       | -7 | -7       |    | -7 | -7       | -9         |     | -7       | -7 | Digital           |

| Data  | 48   | -11      | -8        | -  |          | -8       | -  | -8       | _  | -  | -        | -          | - 1 | -        | -  | Gain              |

| Δ     | 54   | -11      | -9        | _  | 1        | -8       |    | -8<br>-7 | -  | -  | _        | _          | - 1 | -        | -  |                   |

|       | mcs0 | -12      | -7        |    |          | -7       | -7 |          |    |    |          | -10        |     |          |    |                   |

|       | mcs1 | -12      |           | -7 |          | -7       | -7 | -7       |    | -7 | -7       | -10        |     |          |    |                   |

|       | mcs2 | -12      |           | -7 | -7       | -7<br>-7 | -7 | -7       | -7 | -7 | -7       | -10        |     | -7       | -7 |                   |

|       | mcs3 | -12      | -7        |    |          | -7<br>-7 | -7 | -7       |    | -7 |          | -10        |     |          |    |                   |

|       | mcs4 | -12      |           | -7 | -7<br>-7 | -7<br>-7 | -7 | -7<br>-7 | -7 | -7 | -7<br>-7 | -10<br>-10 |     | -7<br>-7 | -7 |                   |

|       | mcs5 | -12      | -8        |    |          |          |    |          |    |    |          |            |     |          | •  |                   |

|       | mcs6 | -12      | -9<br>-10 | -  |          | -8<br>-9 | -  | -8<br>-9 |    |    | -        | -          | - 1 | -        | -  |                   |

|       | mcs7 | -12<br>0 |           | -9 | -9       | -9       | -9 | -9       | -9 | -9 | -9       | -10        | -9  | -9       | -9 | <                 |

|       | 1e9c | 0        |           |    |          |          |    |          |    |    |          |            |     |          |    | Specific          |

|       | Teac | U        |           |    |          |          |    |          |    | l  | l        |            |     |          |    | Configuration     |

The Gain tables are provided as part of firmware update package in form of .csv file available at src/firmware/Tools/gain\_builder/gain\_sheets folder. The gain values are downloaded as part of complete download process. For more details, see "WINC Devices – Integrated Serial Flash Memory Download Procedure" document.

Prior to v19.6.1 only one gain table was supported in ATWINC15x0, with which the WINC can only operate in one regulatory region without requiring different Flash content.

The ATWINC15x0 firmware version 19.6.1 or above supports multiple gain table and the Flash can store up to four gain tables. The table can be selected by the Host MCU using the API m2m\_wifi\_set\_gain\_table\_idx. If the ATWINC15x0 has to operate in multiple region with maximum transmit power allowed in that region, multiple gain table feature can be used to select gain table (by Host MCU) based on the region in which the ATWINC15x0 is operated.

## 5.8.1 Writing the Gain Table to ATWINC15x0

The gain builder application uses multiple .csv files (up to a maximum of 4) and perform the necessary maths operations on the gain table to calculate the gain values and write them to the Flash:

```

gain_builder [-table <no_of_tables> <img_path1> <img_path2> <img_path3> <img_path4>]

[-index <gain_table_index>][-no_wait] [-port]

```

**Note:** The img\_path\* parameters specify the separate tables, and the index parameter specifies the default table to use on power up.

#### 5.8.2 Selecting a Specific Gain Table

Setting the specific gain table index is achieved using API m2m\_wifi\_set\_gain\_table\_idx. The m2m\_wifi\_set\_gain\_table\_idx must be called after the initialization and before any connection request. The corresponding gain tables must be available in the Flash.

Note: The ATWINC15x0 firmware release v19.6.1 contains only one gain table that can be used in all the region.

## 5.9 Host File Download

The Host File Download is a feature supported in the ATWINC15x0 firmware version 19.6.1 and above. This feature is supported only in the ATWINC1510 device which has 8 Mb Flash. The ATWINC1500 only has 4 Mbit of Flash memory and therefore this feature is not supported for the ATWINC1500. With Host file download feature, the Host MCU can instruct the ATWINC1510 to download a file and save it in the ATWINC1510 Flash. The ATWINC1510 can download the file from a HTTP or a HTTPS web server only. The maximum size of file that can be stored in the ATWINC1510 is 508 KB. This feature is ideal for updating the firmware of host MCU. However, the feature is not limited to MCU OTA only.

When performing MCU OTA updates, there is no enforced file format, so the Application Developer can choose a strategy to perform integrity check validation on the received file. The WINC does not perform any integrity check on the downloaded file and therefore, it is recommended that the Application do it instead.

The feature is designed for single file support and allows for a maximum size of 508 KB. The driver protects against invalid access to the file stored in the WINC's Flash by using file handlers to identify each file. If a new download starts or if the file is erased, access to the file partition is denied. Also, the application can request an explicit erase to delete the file from the ATWINC's Flash, destroying any potentially confidential data.

The API m2m\_ota\_host\_file\_get is used to download file from remote location and store it in ATWINC1500 Flash. The m2m\_ota\_host\_file\_get can be used to download only one file at a time. When the get file API is called again, the previously stored file is erased and new file download is initiated.

To retrieve the downloaded file from the ATWINC1510 Flash,  $m2m_ota_host_file_read_spi$  or  $m2m_ota_host_file_read_hif$  API can be used by the host MCU. The completion of file download is notified through the callback registered in  $m2m_ota_host_file_get$  API. The user can use the  $m2m_ota_host_file_read_spi$  or  $m2m_ota_host_file_read_hif$  API by passing required arguments to initiate the file read from the WINC Flash.

#### 5.9.1 Overview

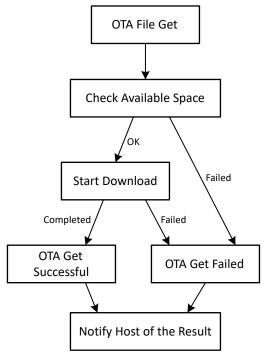

Whenever an application needs information which is stored in a file somewhere in a remote location, the application can use the Host File Download feature to retrieve the file from the remote location and temporarily store it in the WINC's Flash. When a download is successfully completed, a file handler is generated and stored in NVM in the WINC, therefore it is valid even after a WINC reset. After a handler is generated, access to the file is possible via the provided APIs and reading of a file is possible via two mechanisms, HIF and SPI. In either case, the read operation requires the file handler of the file which the application is trying to access, if the handler being requested and the handler internally stored match, then the access is granted. The same procedure is valid for erasing the file. The use of a file handler avoids access to invalid data, for example when trying to concurrently access the file. The following figure depicts the steps which the WINC follows when performing a Host File Download.

Figure 5-6. Host File Download Operation within the WINC

The download starts only if the space available in Flash is enough to store the file which is requested to be downloaded. If Host File Download is requested in the ATWINC1500 (4 Mb Flash), the download fails since there is no Host File partition in Flash and therefore no space to store the file.

The "Start Download" step causes any previously available valid file handler to be invalidated. When "OTA Get Successful" message is received, a new file handler is generated along with the status and the total size of the downloaded file, they are included in the Download completion notification sent to the host.

#### 5.9.2 OTA Initialization

To use the Host File Download feature, the WINC and the OTA driver must be initialized. The following is the procedure for OTA initialization:

- 1. m2m\_wifi\_init or m2m\_wifi\_reinit this API is required to initialize the WINC and to set up the callback for the HIF communication. After this step, the WINC can be configured to connect to a network and download a file. For more details to understand when to use each of these two options, see the API documentation.

- 2. m2m\_ota\_init this API registers the OTA callback, which is required to execute any callbacks configured through the Host File Download APIs and to notify the Application of file download status.

#### 5.9.3 Using Host File Download for MCU OTA

Host File Download allows an application to download a file from a remote location. The link to the file can be through a secure connection and once the file is downloaded, it is stored in the WINC's Flash and the Application is notified about it. The files to download can be of any kind and are not limited to MCU binaries, making this feature both flexible and powerful. One example would be the download of text files, which can hold, for instance, a file checksum,

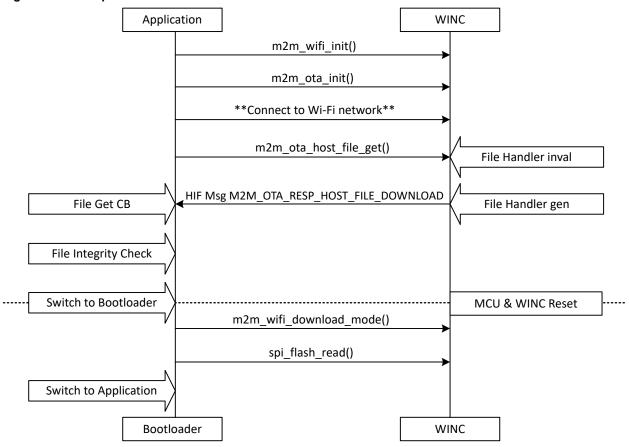

which can later be used by the Application to verify the integrity of the downloaded binary. An Host MCU OTA requires the following steps:

- Provide an http/https link to the file to tell WINC to download the file from a specific remote location, which can be done using API m2m\_ota\_host\_file\_get.

- Read the image from the WINC using <code>spi\_flash\_read</code>. Since there is a limitation currently in which the bootloader would also need to perform <code>m2m\_wifi\_init</code>, <code>m2m\_ota\_init</code> and only then it should do <code>m2m\_ota\_host\_file\_read\_spi</code> to read the image from WINC. <code>m2m\_ota\_host\_file\_read\_hif</code> and <code>m2m\_ota\_host\_file\_read\_spi</code> are not used in the ASF Example for MCU OTA to keep the driver footprint small while working around the limitation described above. However, this limitation is only present when the Application needs to be reset, or in this case switch to a bootloader, the WINC driver will lose track of the file handler and will have to load it again through the initialization process. If no reset or shutdown need to be performed and if no different Application needs to be loaded after downloading the file, these two APIs can be used.

Figure 5-7. Example Host File Download for MCU OTA

Other steps that must be considered by the Application Developer are:

- It is recommended to verify the integrity of the image using a checksum calculation and match it against a

previously known checksum. The user can design the validation mechanism since no predefined file format is

enforced for MCU OTA.

- There is an option to erase the file from Flash. Although this is not mandatory before requesting a new download, it can be useful for security purposes, ensuring that sensitive data is unavailable after its use.

Note: The WINC does not perform any integrity check of any of the downloaded files via Host File Download and that must be checked by the application.

#### 5.9.4 API Description

For a more detailed description of the APIs, refer to WINC1500 SW API.chm.

## 5.9.4.1 OTA File Get

```

NMI_API sint8 m2m_ota_host_file_get

(

unsigned char *pcDownloadUrl,

tpfFileGetCb pfHFDGetCb

);

```