# CarrierBoard Design Guide

SOM-3567

R101 2018'05'03

## **Contents**

| 1. Introduction                                               | 4   |

|---------------------------------------------------------------|-----|

| 1.1 About This Document                                       | 4   |

| 1.2 Signal Table Terminology                                  | 4   |

| 1.3 Terminology                                               | 4   |

| 1.4 Reference Documents                                       | 7   |

| 1.5 Revision History                                          | 8   |

| 1.6 SOM-3567 Block Diagram                                    |     |

| 2. Qseven Interfaces                                          |     |

| 2.1 Qseven Connector Layout                                   | 1 0 |

| 2.2 Qseven 2.1 Connector Pin-out                              |     |

| 2.3 PCI Express                                               | 1 7 |

| 2.3.1 COM Express A-B Connector and C-D Connector PCle Groups |     |

| 2.3.2 General Purpose PCIe Signal Definitions                 |     |

| 2.3.3 PCI Express* Trace Length Guidelines                    |     |

| 2.4 LAN Interface                                             |     |

| 2.4.1 LAN Signal Definitions                                  |     |

| 2.4.2 LAN Implementation Guidelines                           | 2 6 |

| 2.4.3 LAN Magnetics Modules                                   | 2 7 |

| 2.4.4 LAN Component Placement                                 | 2 7 |

| 2.4.5 LAN Ground Plane Separation                             | 2 7 |

| 2.4.6 LAN Link Activity and Speed LED                         | 2 8 |

| 2.4.7 LAN Trace Length Guidelines                             | 2 9 |

| 2.4.8 Reference Ground Isolation and Coupling                 | 3 0 |

| 2.5 SATA                                                      | 3 1 |

| 2.5.1 SATA Signal Definitions                                 | 3 1 |

| 2.5.2 SATA Routing Guidelines                                 | 3 3 |

| 2.5.2.1 General SATA Routing Guidelines                       | 3 3 |

| 2.5.3 SATA Trace Length Guidelines                            | 3 4 |

| 2.6 USB2.0 Ports                                              | 3 5 |

| 2.6.1 USB2.0 Signal Definitions                               | 3 6 |

|                                                               | 3 Q |

| 2.6.1.2 Powering USB devices during S5                         | 3 | 9 |

|----------------------------------------------------------------|---|---|

| 2.6.2 USB2.0 Routing Guidelines                                | 4 | 0 |

| 2.6.2.1 USB 2.0 General Design Considerations and Optimization | 4 | 0 |

| 2.6.2.2 USB 2.0 Port Power Delivery                            | 4 | 0 |

| 2.6.2.3 USB 2.0 Common Mode Chokes                             | 4 | 1 |

| 2.6.2.4 EMI / ESD Protection                                   | 4 | 2 |

| 2.6.2.5 USB Client Considerations                              | 4 | 3 |

| 2.6.3 USB2.0 Trace Length Guidelines                           | 4 | 4 |

| 2.7 USB3.0                                                     | 4 | 6 |

| 2.7.1 USB3.0 Signal Definitions                                | 4 | 6 |

| 2.7.1.1 USB Over-Current Protection (USB_x_y_OC#)              | 4 | 8 |

| 2.7.1.2 EMI / ESD Protection                                   | 4 | 9 |

| 2.7.2 USB3.0 Trace Length Guidelines                           | 4 | 9 |

| 2.8 SDIO Interface                                             | 5 | 0 |

| 2.8.1 SDIO Signal Definitions                                  | 5 | 0 |

| 2.8.2 SDIO Interface Routing Guidelines                        | 5 | 3 |

| 2.9 High Definition Audio / AC97 / I?S Audio Signals           | 5 | 4 |

| 2.9.1 Audio Codec Signal Descriptions                          | 5 | 4 |

| 2.9.2 Audio Routing Guidelines                                 | 5 | 5 |

| 2.9.3 Audio Trace Length Guidelines                            | 5 | 6 |

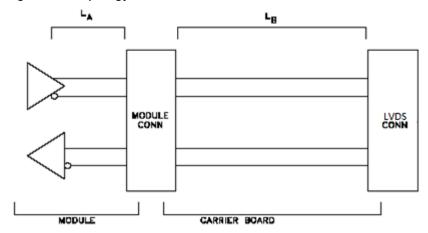

| 2.10 LVDS                                                      | 5 | 7 |

| 2.10.1 Signal Definitions                                      | 5 | 7 |

| 2.10.1.1 Display Timing Configuration                          | 6 | 1 |

| 2.10.1.2 Backlight Control                                     | 6 | 2 |

| 2.10.2 LVDS Routing Guidelines                                 | 6 | 2 |

| 2.10.3 LVDS Trace Length Guidelines                            | 6 | 3 |

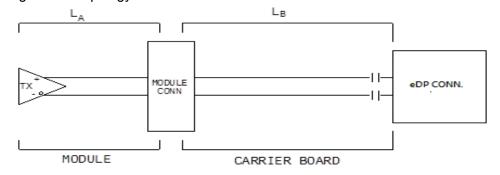

| 2.11 Embedded DisplayPort (eDP) *SOM-3567 is not support       | 6 | 4 |

| 2.11.1 eDP Signal Definitions                                  | 6 | 4 |

| 2.11.2 eDP Implementation Guidelines                           | 6 | 6 |

| 2.11.3 eDP Trace Length Guidelines                             | 6 | 6 |

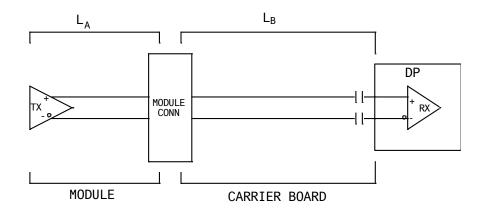

| 2.12 DisplayPort Interfaces                                    | 6 | 7 |

| 2.12.1 DisplayPort Interface Signals (from Module)             | 6 | 7 |

| 2.12.2 DisplayPort Interfaces Routing Guidelines               | 7 | 0 |

| 2.12.2.1 DisplayPort Routing Guidelines                        | 7 | 0 |

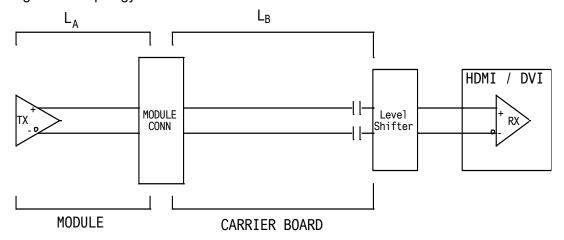

| 2.12.2.2 HDML/ DVI Routing Guidelines                          | 7 | 3 |

| 2.12.3 HDMI / DVI Level Shifter Requirements               | 4 |

|------------------------------------------------------------|---|

| 2.12.4 ESD Protection                                      | 5 |

| 2.13 LPC Bus – Low Pin Count Interface                     | 6 |

| 2.13.1 LPC Signal Definition                               | 7 |

| 2.13.2 LPC Routing Guidelines                              | 8 |

| 2.13.2.1 General Signals                                   | 8 |

| 2.13.2.2 Bus Clock Routing                                 | 8 |

| 2.13.3 LPC Trace Length Guidelines                         | 8 |

| 2.14. CAN Interface *SOM-3567 is not support CAN Interface | 0 |

| 2.14.1 CAN interface Signal Definitions                    | 0 |

| 2.14.2 CAN interface Routing Guidelines                    | 0 |

| 2.14.3 CAN interface Trace Length Guidelines               | 1 |

| 2.15 SPI – Serial Peripheral Interface Bus                 | 2 |

| 2.15.1 SPI Signal Definition                               | 2 |

| 2.15.2 SPI Routing Guidelines                              | 3 |

| 2.15.3 SPI Trace Length Guidelines                         | 3 |

| 2.16 General Purpose I2C Bus Interface                     | 4 |

| 2.16.1 Signal Definitions                                  | 5 |

| 2.16.2 I2C Routing Guidelines                              | 6 |

| 2.16.3 I2C Trace Length Guidelines                         | 6 |

| 2.16.4 Connectivity Considerations                         | 6 |

| 2.17 System Management Bus (SMBus)                         | 7 |

| 2.17.1 SMB Signal Definitions                              | 8 |

| 2.17.2 SMB Routing Guidelines                              | 8 |

| 2.17.3 SMB Trace Length Guidelines                         | 9 |

| 2.18 UART9                                                 | 0 |

| 2.18.1 UART interface Signal Definitions                   | 0 |

| 2.18.2 Serial interface Routing Guidelines                 | 0 |

| 2.18.3 Serial interface Trace Length Guidelines            | 0 |

| 2.19 Miscellaneous Signals                                 | 1 |

| 2.19.1 Miscellaneous Signals9                              | 1 |

| 2.19.1.1 Watchdog Control Signals9                         | 2 |

| 2.19.1.2 PC Speaker Output9                                | 3 |

| 2.19.2 Miscellaneous Signals Routing Guidelines            | 3 |

| 2.19.3 Miscellaneous Signals Trace Length Guidelines       | 3 |

| 2.20 Thermal Signals                               |   |

|----------------------------------------------------|---|

| 2.20.1 Thermal Interface                           |   |

| 2.20.2 Thermal Signals Routing Guidelines          |   |

| 2.20.3 Thermal Signals Trace Length Guidelines     |   |

| 2.21 Fan Control Implementation                    |   |

| 2.21.1 Fan Control Interface                       |   |

| 2.21.2 Fan Control Signals Routing Guidelines      |   |

| 2.21.3 Fan Control Signals Trace Length Guidelines |   |

| 3. Power                                           |   |

| 3.1 General Power requirements                     |   |

| 3.1.1 Power Management Signals                     |   |

| 3.2 Power Up Control                               |   |

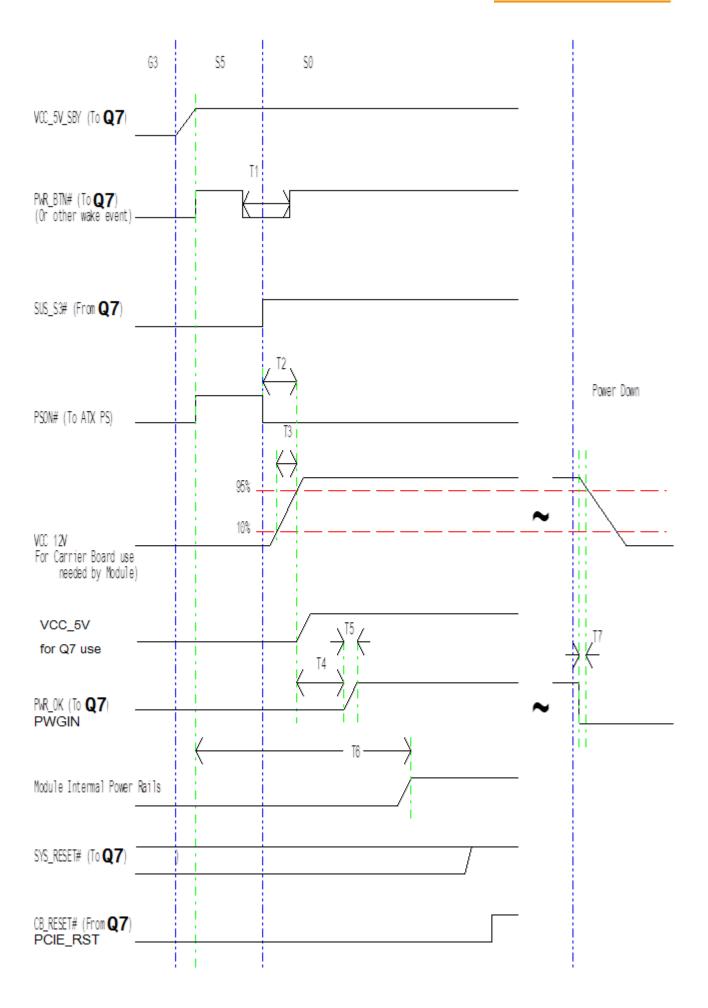

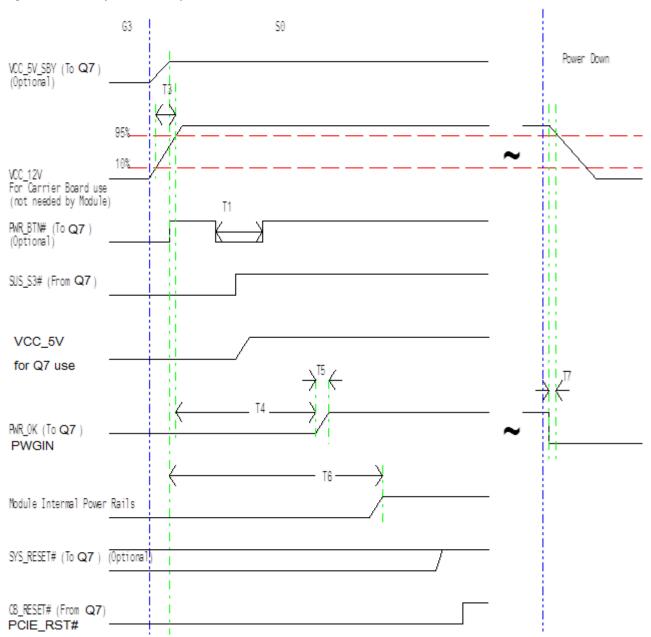

| 3.2.1 ATX and AT Power Sequencing Diagrams         | ) |

| 3.3 RTC Battery                                    | 3 |

| 3.3.1 RTC Battery Lifetime                         | 3 |

| 4. Electrical Characteristics                      | 4 |

| 4.1. Absolute Maximum Ratings                      | 4 |

| 4.2. DC Characteristics                            | 4 |

| 4.3. Inrush Current                                | 4 |

#### 1. Introduction

#### 1.1 About This Document

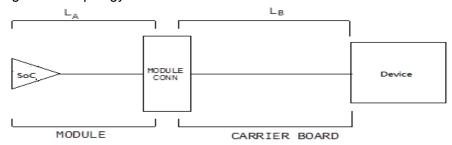

This document provides information for designing a custom system carrier board for Qseven modules. It includes Signal Descriptions, Routing Guidelines and Trace Length Guidelines. The main purpose is designing Carrier Board for helping customers fast and easy using the module of Advantech to be designed.

#### 1.2 Signal Table Terminology

Table 1 below describes the terminology used in this section for the Signal Description tables.

The "#" symbol at the end of the signal name indicates that the active or asserted state occurs when the signal is at a low voltage level. When "#" is not present, the signal is asserted when at a high voltage level.

The terms "Input" and "Output" and their abbreviations in Table 1 below refer to the Module's view, i.e. an input is an input for the Module and not for the Carrier-Board.

## 1.3 Terminology

Table 1: Conventions and Terminology

| Terminology        | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| X86                | The term x86 refers to a family of instruction set architectures  |

|                    | based on the Intel 8086.                                          |

| PCI Express (PCIe) | Peripheral Component Interface Express. Next-generation high      |

|                    | speed serialized I/O bus                                          |

| PCI Express Lane   | One PCI Express Lane is a set of 4 signals that contains two      |

|                    | differential lines for Transmitter and two differential lines for |

|            | Receiver. Clocking information is embedded into the data            |

|------------|---------------------------------------------------------------------|

|            | stream.                                                             |

| x1, x2, x4 | x1 refers to one PCI Express Lane of basic bandwidth; x2 to a       |

|            | collection of two PCI Express Lanes; etc Also referred to as x1,    |

|            | x2, x4 link.                                                        |

| DDC        | Display Data Channel is an I2C bus interface between a display      |

|            | and a graphics adapter.                                             |

| DVI        | Digital Visual Interface is a video interface standard developed    |

|            | by the Digital Display Working Group (DDWG).                        |

| GBE        | Gigabit Ethernet                                                    |

| USB        | Universal Serial Bus                                                |

| SATA       | Serial AT Attachment: serial interface standard for hard disks.     |

| HDA        | High Definition Audio                                               |

| I2S        | Integrated Interchip Sound (I2S) is an electrical serial bus        |

|            | interface standard used for connecting digital audio devices        |

|            | together.                                                           |

| HDMI       | High Definition Multimedia Interface. HDMI supports standard,       |

|            | enhanced, or                                                        |

|            | high-definition video, plus multi-channel digital audio on a single |

|            | cable.                                                              |

| TMDS       | Transition Minimized Differential Signaling. TMDS is a signaling    |

|            | interface defined by Silicon                                        |

|            | Image that is used for DVI and HDMI.                                |

| DP         | (embedded) DisplayPort (DP/eDP) is a digital display interface      |

| eDP        | developed by the Video Electronics Standards Association            |

|            | (VESA).                                                             |

| LPC        | Low Pin-Count Interface: a low speed interface used for             |

|            | peripheral circuits such as Super I/O controllers, which typically  |

|            | combine legacy-device support into a single IC.                     |

| CAN        | Controller Area Network                                             |

| SPI        | Serial Peripheral Interface                                         |

| SDIO       | Secure Digital Input Output                                         |

| SMB        | System Management Bus                                               |

| LVDS       | Low-Voltage Differential Signaling                                  |

| ACPI       | Advanced Control Programmable Interface                             |

| RoHS       | Restriction on Hazardous Substances: The Directive on the           |

|            | Restriction of the Use of Certain Hazardous Substances in           |

|               | Electrical and Electronic Equipment 2002/95/EC.                  |

|---------------|------------------------------------------------------------------|

| N.C.          | Not connected                                                    |

| N.A.          | Not available                                                    |

| T.B.D.        | To be determined                                                 |

| EDID          | Extended Display Identification Data                             |

| EDP           | Embedded DisplayPort (eDP) is a digital display interface        |

|               | standard produced by the Video Electronics Standards             |

|               | Association (VESA) for digital interconnect of Audio and Video.  |

| EEPROM        | Electrically Erasable Programmable Read-Only Memory              |

| EFT           | Electrical Fast Transient                                        |

| EMI           | Electromagnetic Interference                                     |

| ESD           | Electrostatic Discharge                                          |

| ExpressCard   | A PCMCIA standard built on the latest USB 2.0 and PCI            |

|               | Express buses.                                                   |

| FR4           | A type of fiber-glass laminate commonly used for printed circuit |

|               | boards.                                                          |

| GPI           | General Purpose Input                                            |

| GPIO          | General Purpose Input Output                                     |

| GPO           | General Purpose Output                                           |

| DE            | Integrated Device Electronics – parallel interface for hard disk |

|               | drives – also known as PATA                                      |

| Legacy Device | Relics from the PC-AT computer that are not in use in            |

|               | contemporary PC systems: primarily the ISA bus, UART-based       |

|               | serial ports, parallel printer ports, PS-2 keyboards, and mice.  |

|               | Definitions vary as to what constitutes a legacy device. Some    |

|               | definitions include IDE as a legacy device.                      |

| LS            | Least Significant                                                |

| PCB           | Printed Circuit Board                                            |

| PD            | Pull Down                                                        |

| PP            | Push Pull                                                        |

| I             | Input Pin                                                        |

| 0             | Output Pin                                                       |

| OD            | Open Drain                                                       |

| Р             | Power Pin                                                        |

| PHY           | Ethernet controller physical layer device                        |

| PEG           | PCI Express Graphics                                             |

| PS2           | "Personal System 2" - an IBM trademark term used to refer to     |

|               |                                                                  |

|                     | <del>-</del>                                                      |

|---------------------|-------------------------------------------------------------------|

| PS2 Keyboard        | Intel x86 based personal computers in the 1990s. The term         |

| PS2 Mouse           | survives as a reference to the style of mouse and keyboard        |

|                     | interface that were introduced with the PS2 system.               |

| RTC                 | Real Time Clock – battery backed circuit in PC-AT systems         |

|                     | that keeps system time and dateas well as certain system setup    |

|                     | parameters                                                        |

| S0, S1, S2, S3, S4, | Sleep States defined by the ACPI specificationS0 Full power, all  |

| S5                  | devices powered                                                   |

|                     | S1Sleep State, all context maintained                             |

|                     | S2 Sleep State, CPU and Cache context lost                        |

|                     | S3 Suspend to RAM System context stored in RAM; RAM is in         |

|                     | standby                                                           |

|                     | S4 Suspend to Disk System context stored on disk                  |

|                     | S5 Soft Off Main power rail off, only standby power rail present  |

| TMDS                | Transition Minimized Differential Signaling - a digital signaling |

|                     | protocol between the graphics subsystem and display. TMDS is      |

|                     | used for the DVI digital signals. DC coupled                      |

| TPM                 | Trusted Platform Module, chip to enhance the security features    |

|                     | of a computer system.                                             |

| VESA                | Video Electronics Standards Association                           |

| WDT                 | Watch Dog Timer                                                   |

| <u>I</u>            |                                                                   |

## 1.4 Reference Documents

| Document                                              |

|-------------------------------------------------------|

| Qseven Design Guide Rev. 2.0                          |

| Qseven Specification 2.0 and Qseven Specification 2.1 |

| Intel EDS Document                                    |

| Intel Layout Guide Document                           |

| ATX12V Power Supply Design Guide Rev. 2.01            |

# 1.5 Revision History

| Revision | Date         | РСВ    | Changes                              |

|----------|--------------|--------|--------------------------------------|

|          |              | Rev.   |                                      |

| 1.00     | Oct 14, 2015 | A101-2 | SOM-3567 design for Q7 R2.0          |

| 1.10     | May 03, 2018 | A101-2 | Update Table 18 LVDS impedance to 85 |

|          |              |        |                                      |

|          |              |        |                                      |

|          |              |        |                                      |

|          |              |        |                                      |

|          |              |        |                                      |

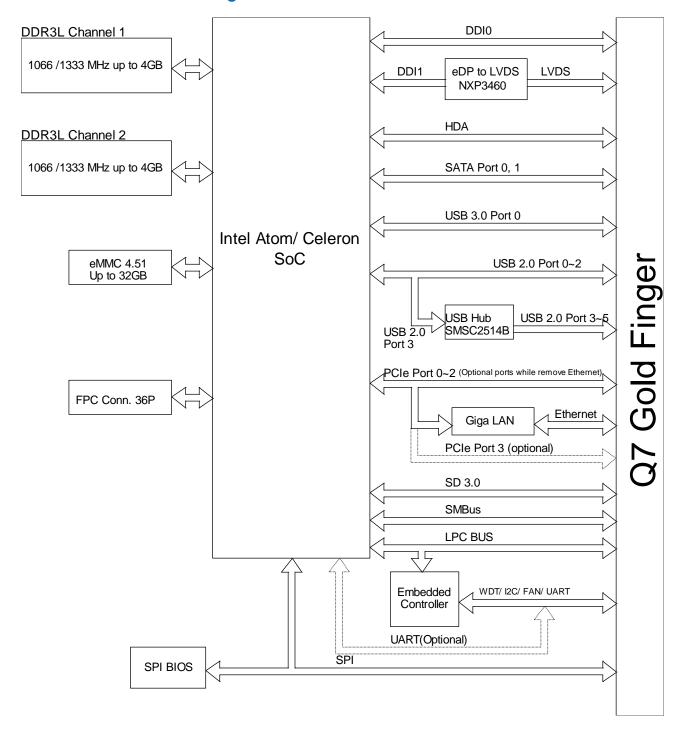

## 1.6 SOM-3567 Block Diagram

### 2. Qseven Interfaces

# 2.1 Qseven Connector Layout

Figure 1: Qseven Connector Layout

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | CN1A                     |                        |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|------------------------|-----|

| GBE_MDI3+   GBE0_MDI2-   GBE0_MDI2-   GBE_MDI3+   GBE0_MDI0-   GBE0_LINK1000#   GBE0_LINK1000#   GBE0_LINK1000#   GBE0_LINK1000#   GBE0_MDI0-   GB   |     | CND                      | OND                    | 2   |

| SBE_MDI3+   GBE_MDI0- -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3   |                          |                        | 4   |

| GBE_LINK100#   GBEO_LINK1000#   GBEO_MDIO-   GBE_MDIO-   GBEO_MDIO-   GBE_MDIO-   GBE_LINK#   GBEO_ACT#   GBE_CTREF   SUS_SS#   30   SUS_SS#   SUS   | 5   |                          |                        | 6   |

| GBE_MDI1+   GBE0_MDI0-   12   13   13   13   13   14   15   15   15   15   15   15   15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7   |                          |                        | 8   |

| The color of the   | 9   | _                        |                        |     |

| GBE_LINK#   GBE_ACT#   16   17   18   18   19   18   19   18   19   18   19   19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11  | _                        | _                      | 12  |

| OBSE_CTREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13  |                          |                        | 14  |

| WAKĒ#   SUS_S3#   20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15  |                          |                        | 16  |

| SUS_STAT#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17  |                          |                        | 18  |

| SLP_BTN#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19  |                          |                        | 20  |

| 25 GND PWGIN 28 SATAO_TX+ SATA1_TX+ 33 SATAO_TX+ SATA1_TX- 34 SATAO_TX+ SATA1_TX- 34 SATAO_RX+ SATA1_TX- 34 SATAO_RX+ SATA1_RX- GND 36 SATAO_RX+ SATA1_RX- GND 41 BIOS_DISABLE#/BOOT_ALT# SDIO_CLK# 44 SDIO_CLK# 44 SDIO_CMD SDIO_WP 48 SDIO_CMD SDIO_WP 48 SDIO_DAT3 SDIO_DAT3 SDIO_DAT3 SDIO_DAT4 SDIO_DAT4 SDIO_DAT5 SDIO_DAT5 SDIO_DAT5 SDIO_DAT6 SDIO_DAT6 SDIO_DAT6 SDIO_DAT7 SDIO_DAT7 SDIO_DAT7 SDIO_DAT7 SDIO_DAT6 SDIO_DAT6 SDIO_DAT6 SDIO_DAT7 SDIO_DAT8 SDIO | 21  |                          |                        | 22  |

| 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  |                          |                        | 24  |

| 27   GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | GND                      | GND                    | Т   |

| 27   GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25  |                          |                        | ے L |

| BATLOW#   SATAO_TX+   SATAI_TX+   330                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | GND                      | PWGIN                  |     |

| SAIAU_IX+   SAIAU_IX+   33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | BATLOW#                  | RSTBTN#                |     |

| SATAO_TX-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                          |                        |     |

| SATA_ACT#   SATA1_RX+   SATA   |     | _                        | _                      |     |

| SATAO RX+   SATA1 RX+   SATA1 RX+   SATA1 RX+   SATA0 RX-   SATA0 RX-   SATA0 RX-   SATA1 RX+   SATA1 RX-   SATA0 RX-   SATA   |     |                          | _                      |     |

| SATAO_RX-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | _                        |                        |     |

| SID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | <del>-</del>             | _                      |     |

| Horizon   Hori   |     | _                        |                        |     |

| SDIO_CD#   SDIO_LED   46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                          |                        |     |

| SDIO_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                          |                        |     |

| SDIO_DATO   SDIO_DAT3   SDIO_DAT3   SDIO_DAT5   SDIO_DAT5   SDIO_DAT5   SDIO_DAT5   SDIO_DAT5   SDIO_DAT6   SDIO_DAT7   SDIO_DAT6   SDIO_DAT7   SDIO_DAT7   SDIO_DAT6   SDIO_DAT7   SDIO_DAT7   SDIO_DAT7   SDIO_DAT7   SDIO_DAT7   SDIO_DAT7   SDIO_DAT7   SDIO_DAT6   SDIO_DAT7   SDIO   |     |                          |                        |     |

| SDIO_DATO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                          |                        |     |

| SDIO_DAT2   SDIO_DAT5   SDIO_DAT5   SDIO_DAT6   SDIO_DAT7   SDIO_DAT7   SDIO_DAT6   SDIO_DAT7   SDIO_DAT6   SDIO   |     |                          | _                      |     |

| SDIO_DAT4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                          | _                      |     |

| 557         SDIO_DAT6         USB_DRIVE_VBUS         58           59         GND         GND           61         HDA_SYNC/AC97_SYNC/I2S_WS         SMB_CLK/GP1_I2C_CLK         62           63         HDA_RST#/AC97_BCLK/I2S_CLK         SMB_ALERT#         64           65         HDA_BITCLK /AC97_BCLK/I2S_CLK         SMB_ALERT#         66           69         HDA_SDI/AC97_SDI/I2S_SDI         GPO_I2C_CLK         68           69         HDA_SDO/AC97_SDO/I2S_SDO         GPO_I2C_DAT         70           71         THRM#         WDTRIG#         72           73         THRMTRIP#         WDOUT         74           60         OND         GND         76           77         USBP7-/USB_SSTX0-         USBP6-/USB_SSRX0-         78           80         USBP7-/USB_SSTX1-         USBP6-/USB_SSRX1-         80           81         USBP5-/USB_SSTX1-         USBP4-/USB_SSRX1-         84           85         USBP3-         USBP3-         90           91         USBP3-         USBP2-         90           92         USBP3-         USBP3-         92           93         USBP4-/USB_SSTX1-         USBP2-         92           95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | _                        | _                      |     |

| SIND   GND   |     |                          | _                      |     |

| HDA_SYNC/AC97_SYNC/I2S_WS   SMB_CLK/GP1_I2C_CLK   62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                          |                        |     |

| HDA_RST#/AC97_RST#/I2S_RST# SMB_DAT/GP1_I2C_DAT   64   66   65   HDA_BITCLK /AC97_BCLK/I2S_CLK   SMB_ALERT#   66   66   67   HDA_SDI/AC97_SDI/I2S_SDI   GP0_I2C_CLK   68   HDA_SDI/AC97_SDI/I2S_SDI   GP0_I2C_CLK   68   HDA_SDI/AC97_SDI/I2S_SDO   GP0_I2C_DAT   70   71   THRM#   WDTRIG#   72   74   75   77   WDSP7-/USB_SSTX0-   USBP6-/USB_SSRX0-   USBP7-/USB_SSTX0+   USBP6-/USB_SSRX0-   USBP7-/USB_SSTX0+   USBP6-/USB_SSRX0-   80   82   USBP5-/USB_SSTX1+   USBP4-/USB_SSRX1-   USBP5-/USB_SSTX1+   USBP4-/USB_SSRX1-   USBP5-/USB_SSTX1+   USBP4-/USB_SSRX1-   USBP5-/USB_SSTX1+   USBP4-/USB_SSRX1-   USBP3-   USBP2-   90   USBP3-   USBP2-   90   USBP1-   USBP0-   91   USBP1-   USBP0-   92   92   92   92   93   USBP1-   USBP0-   96   98   99   99   101   103   eDP0_TX0-/LVDS_A0-   eDP1_TX0-/LVDS_B0-   102   eDP0_TX1-/LVDS_A1-   eDP0_TX1-/LVDS_A1-   eDP0_TX1-/LVDS_A1-   eDP0_TX1-/LVDS_B1-   eDP0_TX2-/LVDS_A2-   eDP1_TX2-/LVDS_B2-   104   eDP0_TX2-/LVDS_A3-   eDP1_TX2-/LVDS_B3-   116   eDP0_TX3-/LVDS_A3-   eDP1_TX3-/LVDS_B3-   116   eDP0_TX3-/LVDS_A3-   eDP1_TX3-/LVDS_B3-   117   eDP0_TX3-/LVDS_AC-   eDP1_TX3-/LVDS_B3-   118   118   120   eDP0_TX3-/LVDS_AC-   eDP1_TX3-/LVDS_B3-   118   120   eDP0_TX3-/LVDS_AC-   eDP1_TX3-/LVDS_B3   |     |                          |                        |     |

| HDA_BITCLK /AC97_BCLK/I2S_CLK   SMB_ALERT#   66   67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                          |                        |     |

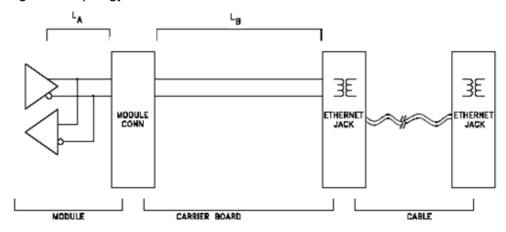

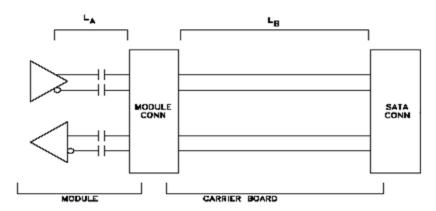

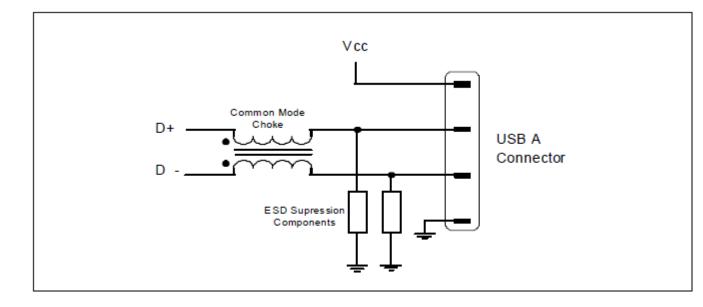

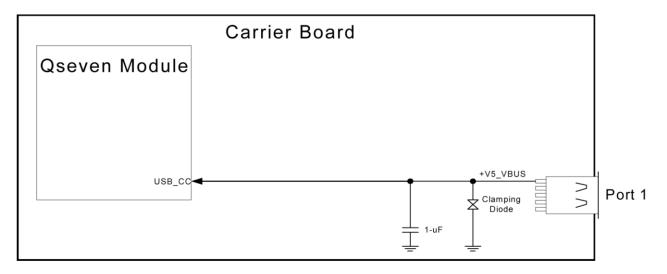

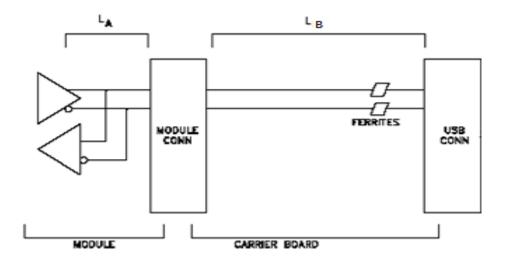

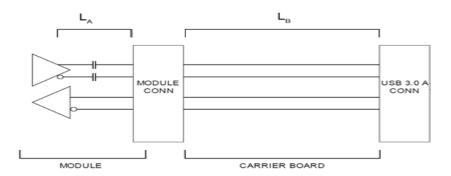

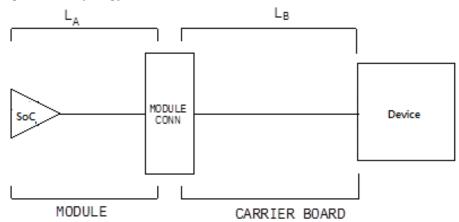

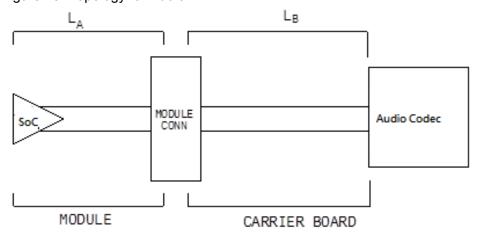

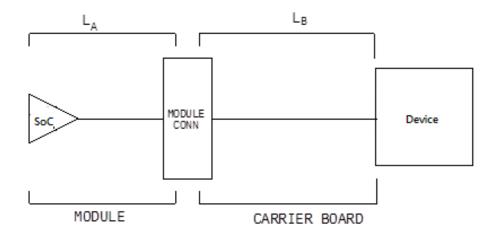

| 67         HDA_SDI/AC97_SDI/I2S_SDI         GP0_I2C_CLK         68           69         HDA_SDO/AC97_SDO/I2S_SDO         GP0_I2C_DAT         70           71         THRM#         WDTRIG#         72           73         THRMTRIP#         WDOUT         74           75         USBP7-/USB_SSTX0-         USBP6-/USB_SSRX0-         78           USBP7-/USB_SSTX0+         USBP6+/USB_SSRX0-         78           USBP5-/USB_SSTX1-         USBP4-/USB_SSRX1-         82           83         USBP5-/USB_SSTX1+         USBP4-/USB_SSRX1-           85         USBP3-         USBP2-           91         USBP3-         USBP2-           91         USBP3-         USBP2-           92         USBP1-         USBP0-           95         USBP1-         USBP0-           99         GND         GND           101         eDP0_TX0+/LVDS_A0-         eDP1_TX0+/LVDS_B0-           99         GND         eDP1_TX1-/LVDS_B1-           105         eDP0_TX1-/LVDS_A1-         eDP1_TX1-/LVDS_B2-           109         eDP0_TX2-/LVDS_A2-         eDP1_TX2-/LVDS_B2-           111         eDP0_TX2-/LVDS_A2-         eDP1_TX2-/LVDS_B3-           116         eDP0_TX3-/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                          |                        |     |