### **Mirror-Module Driver-IC**

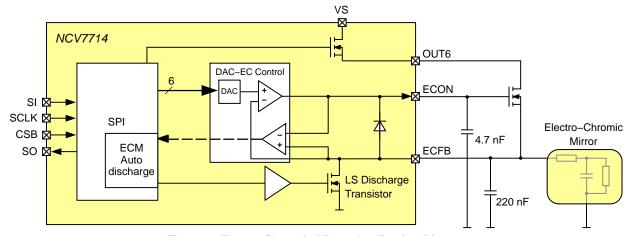

The NCV7704/NCV7714 is a powerful Driver–IC for automotive body control systems. The IC is designed to control several loads in the front door of a vehicle. The monolithic IC is able to control mirror functions like mirror positioning and heating. In addition, NCV7714 includes the electro–chromic mirror feature. The device features three high–side outputs to drive LEDs or incandescent bulbs (up to 10 W). To allow maximum flexibility, all lighting outputs can be PWM controlled thru PWM inputs (external signal source) or by an internal programmable PWM generator unit. The NCV7704/NCV7714 is controlled thru a 24 bit SPI interface with in–frame response.

#### **Features**

- Operating Range from 5.5 V to 28 V

- Three High–Side and Three Low–Side Drivers Connected as Half–Bridges

- 3 Half-bridges  $I_{load} = 0.75 \text{ A}$ ;  $R_{DS(on)} = 1.6 \Omega @ 25^{\circ}\text{C}$

- Three High-Side Lamp Drivers

- 2x LED;  $I_{load} = 0.3 \text{ A}$ ;  $R_{DS(on)} = 1.4 \Omega @ 25^{\circ}\text{C}$

- 1x 10 W; Configurable as LED Driver;  $I_{load} = 2.5 \text{ A}$ ;  $R_{DS(on)} = 300 \text{ m}\Omega$  @ 25°C

- One High–Side Driver for Mirror Heating;  $I_{load} = 6 \text{ A}$ ;  $R_{DS(on)} = 100 \text{ m}\Omega @ 25^{\circ}\text{C}$

- Electro Chromic Mirror Control (NCV7714 Only)

- ◆ 1x 6-Bit Selectable Output Voltage Controller

- 1x LS for EC Control;  $I_{load} = 0.75 \text{ A}$ ;  $R_{DS(on)} = 1.6 \Omega$  @ 25°C

- Independent PWM Functionality for All Outputs

- Integrated Programmable PWM Generator Unit for All Lamp Driver Outputs

- 7-bit / 9-bit Selectable Duty-cycle Setting Precision

- Programmable Soft-start Function to Drive Loads with Higher Inrush Currents as Current Limitation Value

- Multiplex Current Sense Analog Output for Advanced Load Monitoring

- Very Low Current Consumption in Standby Mode

- Charge Pump Output to Control an External Reverse Polarity Protection MOSFET

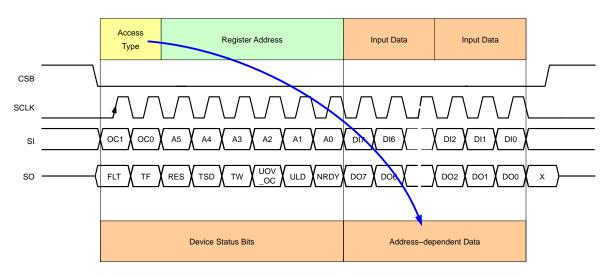

- 24-Bit SPI Interface for Output Control and Diagnostic

- Protection Against Short-circuit, Overvoltage and Over-temperature

- Downwards Pin-to-Pin and SPI Registers Compatible with NCV7707

- AEC-Q100 Qualified and PPAP Capable

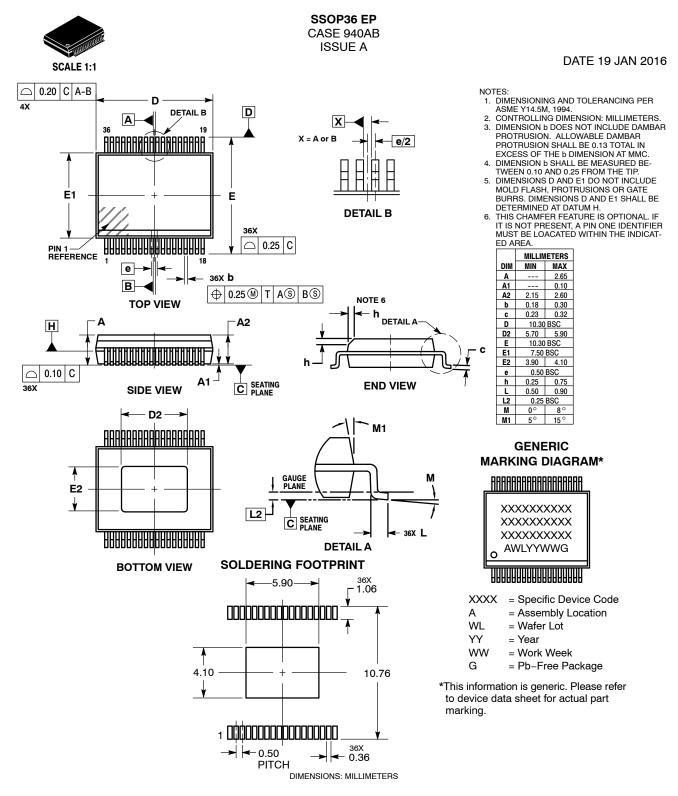

- SSOP36-EP Power Package

- This is a Pb-Free Device

#### ON Semiconductor®

www.onsemi.com

SSOP36 EP DQ SUFFIX CASE 940AB

#### **MARKING DIAGRAM**

#### NCV7704 or NCV7714

Specific Device CodeAssembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

vvvv = vvork vveek G = Pb–Free Package

#### ORDERING INFORMATION

| Device     |     | Package            | Shipping <sup>†</sup> |

|------------|-----|--------------------|-----------------------|

| NCV7704DQF | R2G | SSOP36-EP<br>GREEN | 1500 / Tape &         |

| NCV7714DQF | R2G | (Pb-Free)          | Reel                  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **Typical Applications**

- De-centralized Door Electronic Systems

- Body Control Units (BCUs)

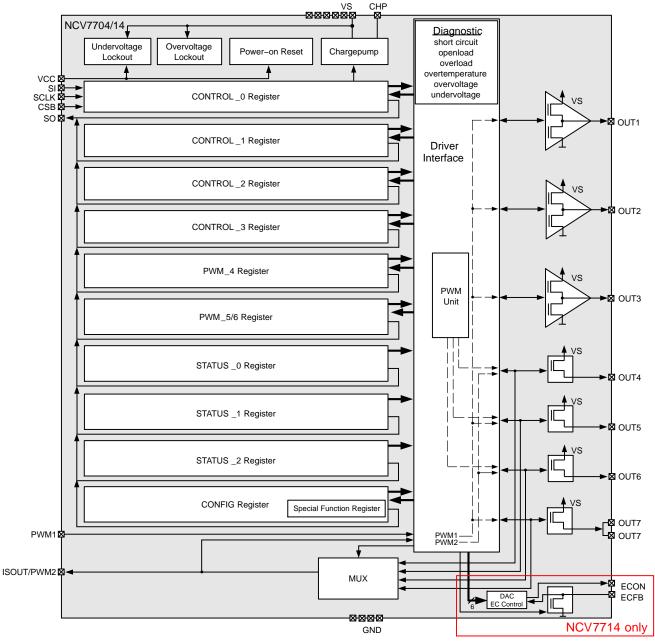

Figure 1. Block Diagram

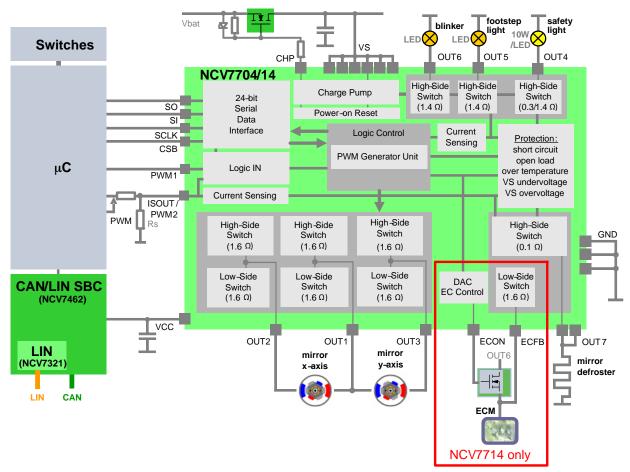

Figure 2. Application Diagram

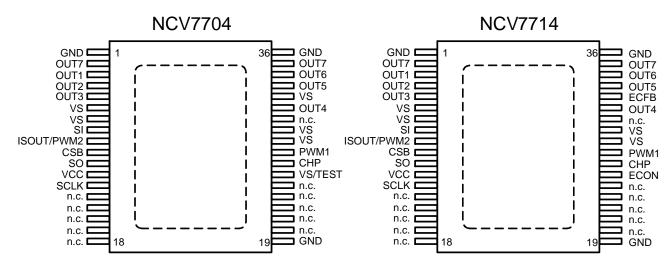

Figure 3. Pin Connections (Top View)

**Table 1. PIN FUNCTION DESCRIPTION**

|            | 1. PIN FUNCTIO            | N DESCRIPTION                    |                                                                                                                                                                                                                                                                                                  |

|------------|---------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Pin Name                  | Pin Type                         | Description                                                                                                                                                                                                                                                                                      |

| 1          | GND                       | Ground                           | Ground Supply (all GND pins have to be connected externally)                                                                                                                                                                                                                                     |

| 2          | OUT7                      | HS driver Output                 | Heater Output (has to be connected externally to pin 35)                                                                                                                                                                                                                                         |

| 3          | OUT1                      | Half bridge driver Output        | Mirror common Output                                                                                                                                                                                                                                                                             |

| 4          | OUT2                      | Half bridge driver Output        | Mirror x/y control Output                                                                                                                                                                                                                                                                        |

| 5          | OUT3                      | Half bridge driver Output        | Mirror x/y control Output                                                                                                                                                                                                                                                                        |

| 6          | VS                        | Supply                           | Battery Supply Input (all VS pins have to be connected externally)                                                                                                                                                                                                                               |

| 7          | VS                        | Supply                           | Battery Supply Input (all VS pins have to be connected externally)                                                                                                                                                                                                                               |

| 8          | SI                        | Digital Input                    | SPI interface Serial Data Input                                                                                                                                                                                                                                                                  |

| 9          | ISOUT/PWM2                | Digital Input /<br>Analog Output | PWM control Input / Current Sense Output. This pin is a bidirectional pin. Depending on the selected multiplexer bits, an image of the instant current of the corresponding HS stage can be read out.  This pin can also be used as PWM control input pin for OUT4 and OUT6.                     |

| 10         | CSB                       | Digital Input                    | SPI interface Chip Select                                                                                                                                                                                                                                                                        |

| 11         | SO                        | Digital Output                   | SPI interface Serial Data Output                                                                                                                                                                                                                                                                 |

| 12         | VCC                       | Supply                           | Logic Supply Input                                                                                                                                                                                                                                                                               |

| 13         | SCLK                      | Digital Input                    | SPI interface Shift Clock                                                                                                                                                                                                                                                                        |

| 14         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 15         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 16         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 17         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 18         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 19         | GND                       | Ground                           | Ground Supply (all GND pins have to be connected externally)                                                                                                                                                                                                                                     |

| 20         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 21         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 22         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 23         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 24         | n.c.                      |                                  | Not connected                                                                                                                                                                                                                                                                                    |

| 25         | VS/TEST<br>(NCV7704 only) | Supply                           | Test Input, has to be connected to VS in application                                                                                                                                                                                                                                             |

|            | ECON<br>(NCV7714 only)    | ECM driver Output                | Electrochromic mirror control DAC output. If the Electrochrome feature is selected, this output controls an external Mosfet, otherwise it remains in high–impedance state.  If the electrochrome feature is not used in the application and not selected via SPI the pin can be connected to VS. |

| 26         | CHP                       | Analog Output                    | Reverse Polarity FET Control Output                                                                                                                                                                                                                                                              |

| 27         | PWM1                      | Digital Input                    | PWM control Input for OUT1–3, OUT5 and OUT7                                                                                                                                                                                                                                                      |

| 28         | VS                        | Supply                           | Battery Supply Input (all VS pins have to be connected externally)                                                                                                                                                                                                                               |

| 29         | VS                        | Supply                           | Battery Supply Input (all VS pins have to be connected externally)                                                                                                                                                                                                                               |

| 30         | n.c.                      | 11-7                             | Not connected                                                                                                                                                                                                                                                                                    |

| 31         | OUT4                      | HS driver Output                 | LED / Bulb Output                                                                                                                                                                                                                                                                                |

| 32         | VS                        | Supply                           | Connect to VS pins externally (no power connection)                                                                                                                                                                                                                                              |

|            | (NCV7704 only)            |                                  |                                                                                                                                                                                                                                                                                                  |

|            | ECFB<br>(NCV7714 only)    | ECM Input / Output               | Electrochromic Mirror Feedback Input, Fast discharge transistor Output                                                                                                                                                                                                                           |

| 33         | OUT5                      | HS driver Output                 | LED Output                                                                                                                                                                                                                                                                                       |

| 34         | OUT6                      | HS driver Output                 | LED Output                                                                                                                                                                                                                                                                                       |

| 35         | OUT7                      | HS driver Output                 | Heater Output (has to be connected externally to pin 2)                                                                                                                                                                                                                                          |

| 36         | GND                       | Ground                           | Ground Supply (all GND pins have to be connected externally)                                                                                                                                                                                                                                     |

|            | Heat slug                 | Ground                           | Substrate; Heat slug has to be connected to all GND pins                                                                                                                                                                                                                                         |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol                         | Rating                                                                                                                                        | Min            | Max           | Unit |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|------|

| Vs                             | Power supply voltage  - Continuous supply voltage  - Transient supply voltage (t < 500 ms, "clamped load dump")                               | -0.3<br>-0.3   | 28<br>40      | V    |

| Vcc                            | Logic supply                                                                                                                                  | -0.3           | 5.5           | V    |

| Vdig                           | DC voltage at all logic pins (SO, SI, SCLK, CSB, PWM1)                                                                                        | -0.3           | Vcc + 0.3     | V    |

| Visout/pwm2                    | Current monitor output / PWM2 logic input                                                                                                     | -0.3           | Vcc + 0.3     | V    |

| Vchp                           | Charge pump output (the most stringent value is applied)                                                                                      | −25<br>Vs − 25 | 40<br>Vs + 15 | V    |

| Voutx, Vecon,<br>Vecfb         | Static output voltage (OUT1-7, ECON, ECFB)                                                                                                    | -0.3           | Vs + 0.3      | V    |

| lout1/2/3                      | OUT1/2/3 Output current  - Tj ≥ 25°C  - Tj < 25°C                                                                                             | -1.25<br>-1.35 | 1.25<br>1.35  | А    |

| lout4                          | OUT4 Output current  – DC  – Transient                                                                                                        | <b>-</b> 5     | 5             | А    |

| lout5/6                        | OUT5/6 Output current  – DC  – Transient                                                                                                      | -1.25          | 1.25          | А    |

| lout7                          | OUT7 Output current  – DC  – Transient                                                                                                        | -10            | 10            | А    |

| lout_ecfb<br>(NCV7714<br>only) | ECFB Output current                                                                                                                           |                | 1.25          | А    |

| ESD_HBM                        | ESD Voltage, HBM (Human Body Model); (100 pF, 1500 Ω) (Note 1)  – All pins  – Output pins OUT1–3 and ECFB to GND (all unzapped pins grounded) | -2<br>-4       | 2<br>4        | kV   |

| ESD_CDM                        | ESD according to CDM (Charge Device Model) (Note 1)  – All pins  – Corner pins                                                                | -500<br>-750   | 500<br>750    | V    |

| Tj                             | Operating junction temperature range                                                                                                          | -40            | 150           | °C   |

| Tstg                           | Storage temperature range                                                                                                                     | -55            | 150           | °C   |

| MSL                            | Moisture sensitivity level (Note 2)                                                                                                           | М              | SL3           |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality thould not be assumed, damage may occur and reliability may be affected.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

#### **Table 3. THERMAL CHARACTERISTICS**

| Symbol           | Rating                                                                                       | Value | Unit |

|------------------|----------------------------------------------------------------------------------------------|-------|------|

| $R_{\theta JA}$  | Thermal Characteristics, SSOP36–EP, 1–layer PCB Thermal Resistance, Junction–to–Air (Note 3) | 42    | °C/W |

| R <sub>θJA</sub> | Thermal Characteristics, SSOP36–EP, 4–layer PCB Thermal Resistance, Junction–to–Air (Note 4) | 19.5  | °C/W |

<sup>3.</sup> Values based on PCB of 76.2 x 114.3 mm, 72 µm copper thickness, 20% copper area coverage and FR4 PCB substrate.

ESD Charge Device Model tested per EIA/JES D22/C101, Field Induced Charge Model

2. For soldering information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

<sup>4.</sup> Values based on PCB of 76.2 x 114.3 mm, 72 / 36 μm copper thickness (signal layers / internal planes), 20 / 90% copper area coverage (signal layers / internal planes) and FR4 PCB substrate.

Table 4. ELECTRICAL CHARACTERISTICS 4.5 V < Vcc < 5.25 V, 8 V < Vs < 18 V, -40°C < Tj < 150°C; unless otherwise noted.

| Symbol       | Parameter                                    | Test Conditions                                                                                                                                                                                                                                    | Min      | Тур           | Max        | Unit |

|--------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|------------|------|

| PPLY         | •                                            |                                                                                                                                                                                                                                                    | •        |               |            | •    |

| Vs           | Supply voltage                               | Functional (see Vuv_vs / Vov_vs) Parameter specification                                                                                                                                                                                           | 5.5<br>8 |               | 28<br>18   | V    |

| Is(standby)  | Supply Current (VS), Standby mode            | Standby mode, $VS = 16 \text{ V}, 0 \text{ V} \leq \text{VCC} \leq 5.25 \text{ V}, \\ CSB = \text{VCC}, \text{OUTx/ECx} = \text{floating}, \\ SI = \text{SCLK} = 0 \text{ V}, \text{Tj} < 85^{\circ}\text{C} \\ (\text{Tj} = 150^{\circ}\text{C})$ |          | 3.5<br>(6.5)  | 12<br>(25) | μΑ   |

| Is(active)   | Supply current (VS), Active mode             | Active mode, VS = 16 V,<br>OUTx/ECx = floating                                                                                                                                                                                                     |          | 7.5           | 20         | mA   |

| Icc(standby) | Supply Current (VCC), Standby mode           | Standby mode,<br>VCC = 5.25 V,<br>SI = SCLK = 0 V, Tj < 85°C<br>(Tj = 150°C)                                                                                                                                                                       |          | 4.5<br>(11.5) | 6<br>(50)  | μΑ   |

| Icc(active)  | Supply current (VCC), Active mode            | Active mode, VS = 16 V,<br>OUTx/ECx = floating                                                                                                                                                                                                     |          | 5.5           | 8.4        | mA   |

| I(standby)   | Total Standby mode supply current (ls + lcc) | Standby mode,<br>VS = 16 V, Tj < 85°C,<br>CSB = VCC, OUTx/ECx = floating                                                                                                                                                                           |          | 8             | 18         | μΑ   |

| ERVOLTAGE AN | D UNDERVOLTAGE DETECTION                     |                                                                                                                                                                                                                                                    | •        |               |            |      |

| Vuv_vs(on)   | VS Undervoltage detection                    | VS increasing                                                                                                                                                                                                                                      | 5.6      |               | 6.2        | V    |

| Vuv_vs(off)  |                                              | VS decreasing                                                                                                                                                                                                                                      | 5.2      |               | 5.8        | V    |

| Vuv_vs(hys)  | VS Undervoltage hysteresis                   | Vuv_vs(on) - Vuv_vs(off)                                                                                                                                                                                                                           |          | 0.65          |            | V    |

| Vov_vs(off)  | VS Overvoltage detection                     | VS increasing                                                                                                                                                                                                                                      | 20       |               | 24.5       | V    |

| Vov_vs(on)   |                                              | VS decreasing                                                                                                                                                                                                                                      | 19       |               | 23.5       | V    |

| Vov_vs(hys)  | VS Overvoltage hysteresis                    | Vov_vs(off) - Vov_vs(on)                                                                                                                                                                                                                           |          | 2             |            | V    |

| Vuv_vcc(off) | VCC Undervoltage detection                   | VCC increasing                                                                                                                                                                                                                                     |          |               | 2.9        | V    |

| Vuv_vcc(on)  |                                              | VCC decreasing                                                                                                                                                                                                                                     | 2        |               |            | V    |

| Vuv_vcc(hys) | VCC Undervoltage hysteresis                  | Vuv_vcc(off) - Vuv_vcc(on)                                                                                                                                                                                                                         |          | 0.11          |            | V    |

| td_uv        | VS Undervoltage filter time                  | Time to set the power supply fail bit UOV_OC in the Global Status Byte                                                                                                                                                                             | 6        |               | 13         | μS   |

| td_ov        | VS Overvoltage filter time                   | Time to set the power supply fail bit UOV_OC in the Global Status Byte                                                                                                                                                                             | 50       |               | 100        | μS   |

| ARGE PUMP OU | TPUT CHP                                     |                                                                                                                                                                                                                                                    |          |               |            |      |

| Vchp8        | Chargepump Output Voltage                    | Vs = 8 V, Ichp = -60 μA                                                                                                                                                                                                                            | Vs + 6   | Vs + 9.5      | Vs + 13    | V    |

| Vchp10       | Chargepump Output Voltage                    | Vs = 10 V, Ichp = -80 μA                                                                                                                                                                                                                           | Vs + 8   | Vs + 11       | Vs + 13    | V    |

| Vchp12       | Chargepump Output Voltage                    | VS > 12 V, Ichp = -100 μA                                                                                                                                                                                                                          | Vs + 9.5 | Vs + 11       | Vs + 13    | V    |

| Ichp         | Chargepump Output current                    | VS = 13.5 V, Vchp = Vs + 10 V                                                                                                                                                                                                                      | -750     |               | -95        | μΑ   |

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ 4.5 \ \text{V} < \text{Vcc} < 5.25 \ \text{V}, \ 8 \ \text{V} < \text{Vs} < 18 \ \text{V}, \ -40^{\circ}\text{C} < \text{Tj} < 150^{\circ}\text{C}; \text{unless otherwise noted.}$

| Symbol              | Parameter                                                                       | Test Conditions                                                                                                                                                   | Min            | Тур | Max          | Unit     |

|---------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|--------------|----------|

| MIRROR x/y POSITIO  | NING OUTPUTS OUT1, OUT2, OUT                                                    | 3                                                                                                                                                                 |                |     | -            |          |

| Ron_out,12,3        | On-resistance HS or LS                                                          | Tj = 25°C, lout1,2,3 = ± 0.5 A                                                                                                                                    |                | 1.6 |              | Ω        |

|                     |                                                                                 | Tj = 125°C, lout1,2,3 = ± 0.5 A                                                                                                                                   |                |     | 3            | Ω        |

| loc1,2,3_hs         | Overcurrent threshold HS                                                        | Tj < 25°C<br>Tj ≥ 25°C                                                                                                                                            | -1.35<br>-1.25 |     | -0.75        | Α        |

| loc1,2,3_ls         | Overcurrent threshold LS                                                        | Tj < 25°C<br>Tj ≥ 25°C                                                                                                                                            | 0.75           |     | 1.35<br>1.25 | Α        |

| Vlim1,2,3           | Vds voltage limitation HS or LS                                                 |                                                                                                                                                                   | 2              |     | 3            | V        |

| luld1,2,3_hs        | Underload detection threshold HS                                                |                                                                                                                                                                   | -32            | -20 | -10          | mA       |

| luld1,2,3_ls        | Underload detection threshold LS                                                |                                                                                                                                                                   | 10             | 20  | 32           | mA       |

| td_HS1,2,3(on)      | Output delay time, HS Driver on                                                 | Time from CSB going high to                                                                                                                                       |                | 2.5 | 6            | μS       |

| td_HS1,2,3(off)     | Output delay time, HS Driver off                                                | V(OUT1,2,3) = 0.1·Vs / 0.9·Vs (on/off)                                                                                                                            |                | 3   | 6            | μS       |

| td_LS1,2,3(on)      | Output delay time, LS Driver on                                                 | Time from CSB going low to                                                                                                                                        |                | 1   | 6            | μS       |

| td_LS1,2,3(off)     | Output delay time, LS Driver off                                                | V(OUT1,2,3) = 0.9·Vs / 0.1·Vs (on/off)                                                                                                                            |                | 1   | 6            | μs       |

| tdLH1,2,3           | Cross conduction protection time, low-to-high transition including LS slew-rate |                                                                                                                                                                   |                | 0.5 | 22           | μS       |

| tdHL1,2,3           | Cross conduction protection time, high-to-low transition including HS slew-rate |                                                                                                                                                                   |                | 5.5 | 22           | μs       |

| lleak_act_hs1,2,3   | Output HS leakage current,<br>Active mode                                       | V(OUT1,2,3) = 0 V                                                                                                                                                 | -40            | -16 |              | μΑ       |

| Ileak_act_ls1,2,3   | Output pull-down current,<br>Active mode                                        | V(OUT1,2,3) = VS                                                                                                                                                  |                | 100 | 160          | μΑ       |

| Ileak_stdby_hs1,2,3 | Output HS leakage current,<br>Standby mode                                      | V(OUT1,2,3) = 0 V                                                                                                                                                 | <b>-</b> 5     |     |              | μΑ       |

| lleak_stdby_ls1,2,3 | Output pull-down current,<br>Standby mode                                       | $ \begin{array}{l} V(\text{OUT1,2,3}) = \text{VS, Tj}  \geq \times  25^{\circ}\text{C} \\ V(\text{OUT1,2,3}) = \text{VS, Tj}  <  25^{\circ}\text{C} \end{array} $ |                | 80  | 120<br>175   | μA<br>μA |

| td_uld1,2,3         | Underload blanking delay                                                        |                                                                                                                                                                   | 430            |     | 610          | μS       |

| tdb_old1,2,3        | Overload shutdown blanking delay                                                | Timer started after output activation                                                                                                                             | 16             |     | 25           | μs       |

| td_old1,2,3         | Overload shutdown filter time                                                   | Timer started after blanking delay elapsed                                                                                                                        | 16             |     | 50           | μS       |

| frec1,2,3L          | Recovery frequency, slow recovery mode                                          | CONTROL_3.OCRF = 0                                                                                                                                                | 1              |     | 4            | kHz      |

| frec1,2,3H          | Recovery frequency, fast recovery mode                                          | CONTROL_3.OCRF = 1                                                                                                                                                | 2              |     | 6            | kHz      |

| dVout1,2,3          | Slew rate of HS driver                                                          | Vs = 13.5 V, Rload = 64 $\Omega$ to GND                                                                                                                           | 1.5            | 2.5 | 3.5          | V/μs     |

Table 4. ELECTRICAL CHARACTERISTICS 4.5 V < Vcc < 5.25 V, 8 V < Vs < 18 V, -40°C < Tj < 150°C; unless otherwise noted.

| Symbol            | Parameter                                              | Test Conditions                                                 | Min          | Тур  | Max  | Unit |

|-------------------|--------------------------------------------------------|-----------------------------------------------------------------|--------------|------|------|------|

| BULB / LED DRIVER | OUTPUT OUT4                                            | •                                                               |              | •    |      |      |

| Ron_out4_ICB      | On–resistance to supply,                               | Tj = 25°C, lout4 = -1 A                                         |              | 0.3  |      | Ω    |

|                   | HS switch, Bulb mode                                   | Tj = 125°C, lout4 = -1 A                                        |              |      | 0.6  | Ω    |

| Ron_out4_LED      | On–resistance to supply,                               | Tj = 25°C, lout4 = -0.2 A                                       |              | 1.4  |      | Ω    |

|                   | HS switch, LED mode                                    | Tj = 125°C, lout4 = -0.2 A                                      |              |      | 3    | Ω    |

| Ilim4_ICB         | Output current limitation to GND, Bulb mode            | Tj < 25°C<br>Tj ≥ 25°C                                          | -3.9<br>-3.7 |      | -2.5 | А    |

| Ilim4_LED         | Overcurrent threshold,<br>LED mode                     |                                                                 | -1.1         |      | -0.5 | А    |

| Iuld4_ICB         | Underload detection threshold,<br>Bulb mode            |                                                                 | -70          |      | -5   | mA   |

| luld4_LED         | Underload detection threshold,<br>LED mode             |                                                                 | -15          |      | -5   | mA   |

| td_OUT4_ICB(on)   | Output delay time, Driver on, Bulb mode                | Time from CSB going high to V(OUT4) = 0.1·Vs / 0.9·Vs (on/off); |              | 15   | 48   | μS   |

| td_OUT4_ICB(off)  | Output delay time, Driver off, Bulb mode               | Rload = 16 $\Omega$                                             |              | 21   | 48   | μS   |

| td_OUT4_LED(on)   | Output delay time, Driver on, LED mode                 | Time from CSB going high to V(OUT4) = 0.1·Vs / 0.9·Vs (on/off); |              | 15   | 48   | μS   |

| td_OUT4_LED(off)  | Output delay time, Driver off, LED mode                | - Rload = 64 Ω                                                  |              | 21   | 48   | μS   |

| lleak_act4        | Output leakage current,<br>Active mode                 | V(OUT4) = 0 V                                                   | -15          |      |      | μΑ   |

| Ileak_stdby4      | Output leakage current,<br>Standby mode                | V(OUT4) = 0 V                                                   | -5           |      |      | μΑ   |

| Ileak_out_vs4     | Output leakage current                                 | V(OUT4) = VS                                                    |              |      | 1    | mA   |

| td_uld4_BULB      | Underload blanking delay<br>Bulb mode                  |                                                                 | 1350         |      | 1910 | μS   |

| td_uld4_LED       | Underload blanking delay<br>LED mode                   |                                                                 | 430          |      | 610  | μS   |

| tdb_old_ICB4      | Overload shutdown blanking delay, Bulb mode            | Timer started after output activation                           | 200          |      | 290  | μS   |

| td_old_ICB4       | Overload shutdown filter time,<br>Bulb mode            | Timer started after blanking delay elapsed                      | 100          |      | 160  | μS   |

| tdb_old_LED4      | Overload shutdown blanking delay, LED mode             | Timer started after output activation                           | 200          |      | 290  | μS   |

| td_old_LED4       | Overload shutdown filter time, LED mode only           | Timer started after blanking delay elapsed                      | 50           |      | 100  | μS   |

| frec4L            | Recovery frequency, slow recovery mode recovery        | CONTROL_3.OCRF = 0                                              | 1            |      | 2.1  | kH   |

| frec4H            | Recovery frequency, fast recovery mode (LED mode only) | CONTROL_3.OCRF = 1                                              | 2            |      | 6    | kHz  |

| dVout4_ICB        | Slew rate, Bulb mode                                   | Vs = 13.5 V, Rload = 16 $\Omega$                                |              | 0.22 |      | V/µ  |

| dVout4_LED        | Slew rate, LED mode                                    | Vs = 13.5 V, Rload = 64 $\Omega$                                |              | 0.22 |      | V/µ  |

| dVout4_ocr        | Slew rate in overcurrent recovery mode                 | Vs = 13.5 V, Rload = 16 $\Omega$                                | 1            | 2    | 3    | V/μ  |

Table 4. ELECTRICAL CHARACTERISTICS 4.5 V < Vcc < 5.25 V, 8 V < Vs < 18 V, -40°C < Tj < 150°C; unless otherwise noted.

| Symbol          | Parameter                               | Test Conditions                                            | Min  | Тур | Max  | Unit |

|-----------------|-----------------------------------------|------------------------------------------------------------|------|-----|------|------|

| ED DRIVER OUTPU | TS OUT5, OUT6                           |                                                            | •    |     |      |      |

| Ron_out5,6      | On-resistance to supply,                | Tj = 25°C, lout5,6 = -0.2 A                                |      | 1.4 |      | Ω    |

|                 | HS switch                               | Tj = 125°C, lout5,6 = -0.2 A                               |      |     | 3    | Ω    |

| loc5,6          | Overcurrent threshold                   |                                                            | -0.6 |     | -0.3 | Α    |

| luld5,6         | Underload detection threshold           |                                                            | -18  |     | -4   | mA   |

| td_OUT(on)5,6   | Output delay time, Driver on            | Time from CSB going high to                                |      | 18  | 48   | μs   |

| td_OUT(off)5,6  | Output delay time, Driver off           | $V(OUT5,6) = 0.1 \cdot Vs / 0.9 \cdot Vs \text{ (on/off)}$ |      | 23  | 48   | μs   |

| lleak_act5,6    | Output leakage current,<br>Active mode  | V(OUT5,6) = 0 V                                            | -10  |     |      | μΑ   |

| lleak_stdby5,6  | Output leakage current,<br>Standby mode | V(OUT5,6) = 0 V                                            | -5   |     |      | μΑ   |

| Ileak_out_vs5,6 | Output leakage current                  | V(OUT5,6) = VS                                             |      |     | 1    | mA   |

| td_uld5,6       | Underload blanking delay                |                                                            | 430  |     | 610  | μS   |

| tdb_old_OUT5,6  | Overload shutdown blanking delay        | Timer started after output activation                      | 200  |     | 290  | μS   |

| td_old_OUT5,6   | Overload shutdown filter time           | Timer started after blanking delay elapsed                 | 16   |     | 50   | μs   |

| frec5,6L        | Recovery frequency, slow recovery mode  | CONTROL_3.OCRF = 0                                         | 1    |     | 4    | kHz  |

| frec5,6H        | Recovery frequency, fast recovery mode  | CONTROL_3.OCRF = 1                                         | 2    |     | 6    | kHz  |

| dVout5,6        | Slew rate                               | Vs = 13.5 V, Rload = 64 Ω                                  |      | 0.2 |      | V/μs |

| IEATER OUTPUT O | UT7                                     |                                                            |      | I   | l    |      |

| Ron_out7        | On–resistance to supply,                | Tj = 25°C, lout7 = −3 A                                    |      | 0.1 |      | Ω    |

|                 | HS switch                               | Tj = 125°C, lout7 = -3 A                                   |      |     | 0.2  | Ω    |

| loc7            | Overcurrent threshold                   |                                                            | -10  |     | -6   | Α    |

| luld7           | Underload detection threshold           |                                                            | -300 |     | -30  | mA   |

| td_OUT7(on)     | Output delay time, Driver on            | Time from CSB going high to                                |      | 3   | 12   | μS   |

| td_OUT7(off)    | Output delay time, Driver off           | $V(OUT7) = 0.1 \cdot Vs / 0.9 \cdot Vs (on/off)$           |      | 3   | 12   | μS   |

| lleak_act7      | Output leakage current,<br>Active mode  | V(OUT7) = 0 V                                              | -10  |     |      | μΑ   |

| lleak_stdby7    | Output leakage current,<br>Standby mode | V(OUT7) = 0 V                                              | -5   |     |      | μΑ   |

| Ileak_out7_vs   | Output leakage current                  | V(OUT7) = VS                                               |      |     | 1    | mA   |

| td_uld7         | Underload blanking delay                |                                                            | 430  |     | 610  | μS   |

| tdb_old_OUT7    | Overload shutdown blanking delay        | Timer started after output activation                      | 30   |     | 48   | μS   |

| td_old_OUT7     | Overload shutdown filter time           | Timer started after blanking delay elapsed                 | 16   |     | 25   | μS   |

| frec7L          | Recovery frequency, slow recovery mode  | CONTROL_3.OCRF = 0                                         | 1    |     | 4    | kHz  |

| frec7H          | Recovery frequency, fast recovery mode  | CONTROL_3.OCRF = 1                                         | 2    |     | 6    | kHz  |

|                 |                                         |                                                            |      |     |      |      |

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ 4.5 \ \text{V} < \text{Vcc} < 5.25 \ \text{V}, \ 8 \ \text{V} < \text{Vs} < 18 \ \text{V}, \ -40 ^{\circ}\text{C} < \text{Tj} < 150 ^{\circ}\text{C}; \text{unless otherwise noted.}$

| Symbol            | Parameter                                                                     | Test Conditions                                                                          | Min           | Тур  | Max           | Uni             |

|-------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------|------|---------------|-----------------|

| LECTROCHROMIC     | MIRROR CONTROL (ECFB, ECON)                                                   | (NCV7714 ONLY)                                                                           |               |      |               |                 |

| Ron_ecfb          | On-resistance to GND, LS switch                                               | Tj = 25°C, lecfb = 0.5 A                                                                 |               | 1.6  |               | Ω               |

|                   |                                                                               | Tj = 125°C, lecfb = 0.5 A                                                                |               |      | 3             | Ω               |

| Ilim_ecfb_src     | Output current limitation to GND                                              | Vs = 13.5V, Vcc = 5 V                                                                    | 0.75          |      | 1.25          | Д               |

| Vlim_ecfb         | Vds voltage limitation                                                        | Output enabled                                                                           | 2             |      | 3             | ٧               |

| luld_ecfb         | Underload detection threshold                                                 | Vs = 13.5 V, Vcc = 5 V                                                                   | 10            | 20   | 35            | m               |

| td_ecfb(on)       | Output delay time, LS Driver on                                               | Vs = 13.5 V, Vcc = 5 V,                                                                  |               | 1    | 12            | μ               |

| td_ecfb(off)      | Output delay time, LS Driver off                                              | Rload = 64 $\Omega$ ,<br>V(ECFB) = 0.9·VS / 0.1·VS (on /off)                             |               | 2    | 12            | μ               |

| lleak_ecfb_stdby  | Output leakage current, LS off                                                | Vecfb = Vs, Standby mode                                                                 | -15           |      | 15            | μ               |

| lleak_ecfb_act    | -                                                                             | Vecfb = Vs, Active mode                                                                  | -10           |      | 10            | μ               |

| td_uld_ecfb       | Underload blanking delay                                                      |                                                                                          | 430           |      | 610           | μ               |

| tdb_old_ecfb      | Overload shutdown blanking delay                                              | Timer started after output activation                                                    | 30            |      | 48            | μ               |

| td_old_ecfb       | Overload shutdown blanking delay                                              | Timer started after blanking delay elapsed                                               | 16            |      | 50            | μ               |

| dVecfb/dt(on/off) | Slew rate of ECFB, LS switch                                                  | Vs = 13.5 V, Vcc = 5 V, Rload = 64 $\Omega$                                              |               | 5    |               | V/ <sub>!</sub> |

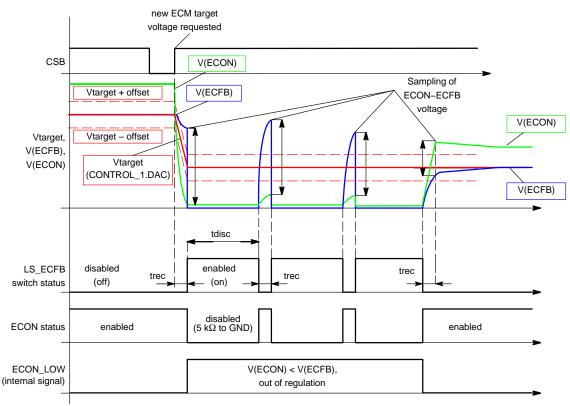

| Vctrl_max         | Maximum EC control voltage                                                    | CONTROL_2.FSR = 1                                                                        | 1.4           |      | 1.6           | \               |

|                   |                                                                               | CONTROL_2.FSR = 0                                                                        | 1.12          |      | 1.28          | ١               |

| DNL               | Differential non linearity                                                    | 1 LSB = 23.8 mV                                                                          | -1            |      | 1             | LS              |

| dV_ecfb           | Voltage deviation between target and ECFB                                     | dV_ecfb = Vtarget – Vecfb,<br>lecon < 1 μA                                               |               |      |               | m               |

|                   |                                                                               | gain<br>offset                                                                           | -5%<br>-1 LSB |      | +5%<br>+1 LSB |                 |

| dV_ecfb_lo        | Difference voltage between target and ECFB sets flag if Vecfb is below target | dV_ecfb = Vtarget - Vecfb,<br>Toggle bit STATUS_2.ECLO = 1                               |               | 120  |               | m               |

| dV_ecfb_hi        | Difference voltage between target and ECFB sets flag if Vecfb is above target | dV_ecfb = Vtarget - Vecfb,<br>Toggle bit STATUS_2.ECHI = 1                               |               | -120 |               | m               |

| Vecon_min_hi      | ECON output voltage range                                                     | lecon = −10 μA                                                                           | 4.5           |      | 5.5           | ١               |

| Vecon_max_lo      |                                                                               | lecon = 10 μA                                                                            | 0             |      | 0.7           | ١               |

| lecon             | ECON output current capability                                                | Vtarget > Vecfb + 500 mV,<br>Vecon = 3.5 V                                               | -100          |      | -10           | μ               |

|                   |                                                                               | Vtarget < Vecfb - 500 mV,<br>Vecon = 0.5 V, Vtarget = 1 LSB,<br>Vecfb = 0.5 V            | 10            |      | 100           | μ               |

| Recon_pd          | Pull-down resistance at ECON in fast discharge mode                           | Vecon = 0.7 V,<br>CONTROL_1.ECEN = 1,<br>CONTROL_1.LSECFB = 1,<br>CONTROL_1.DAC[5:0] = 0 |               |      | 5             | k               |

| Iq_econ           | ECON quiescent current                                                        | Vecon = Vs,<br>CONTROL_1.ECEN = 0                                                        |               |      | 1             | μ               |

| t_disc            | Auto-discharge pulse width                                                    | Config.LSPWM=1                                                                           | 230           | 300  | 360           | m               |

| t_rec             | Auto-discharge blanking time                                                  | Config.LSPWM=1                                                                           | 2.25          | 3    | 3.75          | m               |

| Vthdisc_abs       | PWM discharge threshold level V(ECON) (Note 5)                                | Config.LSPWM=1                                                                           | 350           | 400  | 450           | m               |

| Vthdisc_diff      | PWM discharge threshold level V(ECON) – V(ECFB) (Note 5)                      | Config.LSPWM=1                                                                           | -50           | 0    | 50            | m               |

<sup>5.</sup> If V(ECON) < Vthdisc\_abs or V(ECON)-V(ECFB) < Vthdisc\_diff then ECON\_LOW =1; see description in paragraph Controller for Electro-chromic Glass

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ 4.5 \ \text{V} < \text{Vcc} < 5.25 \ \text{V}, \ 8 \ \text{V} < \text{Vs} < 18 \ \text{V}, \ -40 ^{\circ}\text{C} < \text{Tj} < 150 ^{\circ}\text{C}; \text{unless otherwise noted.}$

| Symbol                  | Parameter                                                              | Test Conditions                                                                                 | Min            | Тур   | Max            | Unit |

|-------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------|-------|----------------|------|

| RENT SENSE              | MONITOR OUTPUT ISOUT/PWM2                                              |                                                                                                 | •              |       |                |      |

| Vis                     | Current Sense output functional voltage range                          | Vcc = 5 V, Vs = 8-20 V                                                                          | 0              |       | Vcc –<br>0.5   | V    |

| (Note 6) and mo         | Current Sense output ratio OUT7 and 4 (low on–resistance bulb mode)    | $ K = lout / lis, 0 V \le Vis \le 4.5 V, Vcc = 5 V $                                            |                | 10000 |                |      |

|                         | Current Sense output ratio OUT5/6 and 4 (high on-resistance LED mode)  |                                                                                                 |                | 2000  |                |      |

| lis,acc<br>(Notes 7, 8) | Current Sense output accuracy<br>OUT4 (low on–resistance bulb<br>mode) | 0.3 V ≤ Vis ≤ 4.5 V, Vcc = 5 V<br>lout4 = 0.5–1.3 A                                             | -2% -<br>6% FS |       | 23% –<br>4% FS |      |

|                         | Current Sense output accuracy<br>OUT4 (high on-resistance LED<br>mode) | 0.3 V ≤ Vis ≤ 4.5 V, Vcc = 5 V<br>lout4 = 0.1–0.28 A                                            | -6% -<br>4% FS |       | 21% –<br>4% FS |      |

|                         | Current Sense output accuracy OUT5/6                                   | 0.3 V ≤ Vis ≤ 4.5 V, Vcc = 5 V<br>lout5/6 = 0.1–0.4 A                                           | -3% -<br>6% FS |       | 17% –<br>3% FS |      |

|                         | Current Sense output accuracy OUT7                                     | $0.3 \text{ V} \le \text{Vis} \le 4.5 \text{ V}, \text{Vcc} = 5 \text{ V}$<br>lout7 = 0.5–5.9 A | –7% –<br>5% FS |       | 12% –<br>1% FS |      |

| tis_blank               | Current Sense blanking time                                            |                                                                                                 | 50             |       | 65             | μS   |

| tis                     | Current Sense settling time                                            | 0 V to FSR (full scale range)                                                                   |                | 230   | 264            | μS   |

<sup>6.</sup> Kis trimmed at 150°C to higher value of spec range to be more centered over temp range.

<sup>7.</sup> Current sense output accuracy = Isout–Isout\_ideal relative to Isout\_ideal 8. FS (Full scale) = Ioutmax/Kis

Table 4. ELECTRICAL CHARACTERISTICS 4.5 V < Vcc < 5.25 V, 8 V < Vs < 18 V, -40°C < Tj < 150°C; unless otherwise noted.

| Symbol            | Parameter                                           | Test Conditions                                                                             | Min     | Тур  | Max     | Unit |

|-------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------|---------|------|---------|------|

| IGITAL INPUTS CSI | B, SCLK, PWM1/2, SI                                 |                                                                                             |         |      | •       |      |

| Vinl              | Input low level                                     | Vcc = 5 V                                                                                   |         |      | 0.3·Vcc | V    |

| Vinh              | Input high level                                    | Vcc = 5 V                                                                                   | 0.7·Vcc |      |         | V    |

| Vin_hyst          | Input hysteresis                                    |                                                                                             | 500     |      |         | mV   |

| Rcsb_pu           | CSB pull-up resistor                                | Vcc = 5 V,<br>0 V < Vcsb < 0.7·Vcc                                                          | 30      | 120  | 250     | kΩ   |

| Rsclk_pd          | SCLK pull-down resistor                             | Vcc = 5 V,<br>Vsclk = 1.5 V                                                                 | 30      | 60   | 220     | kΩ   |

| Rsi_pd            | SI pull-down resistor                               | Vcc = 5 V,<br>Vsi = 1.5 V                                                                   | 30      | 60   | 220     | kΩ   |

| Rpwm1_pd          | PWM1 pull–down resistor                             | Vcc = 5 V,<br>Vpwm1 = 1.5 V                                                                 | 30      | 60   | 220     | kΩ   |

| Rpwm2_pd          | PWM2 pull-down resistor                             | Vcc = 5 V,<br>Vpwm2 = 1.5 V,<br>current sense disabled                                      | 30      | 60   | 220     | kΩ   |

| Ileak_isout       | Output leakage current                              | current sense enabled                                                                       | -2      |      | 2       | μΑ   |

| Ccsb/sclk/pwm1/2  | Pin capacitance                                     | 0 V < Vcc < 5.25 V (Note 9)                                                                 |         |      | 10      | pF   |

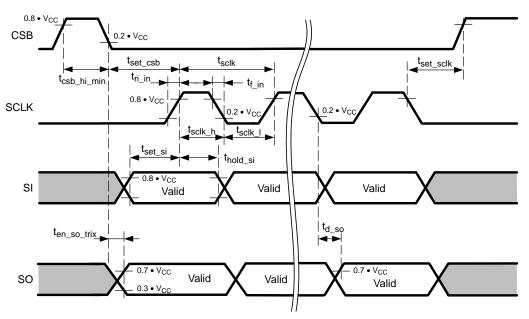

| IGITAL INPUTS CSI | B, SCLK, SI; TIMING                                 |                                                                                             |         |      |         |      |

| tsclk             | Clock period                                        | Vcc = 5 V                                                                                   |         | 1000 |         | ns   |

| tsclk_h           | Clock high time                                     |                                                                                             | 115     |      |         | ns   |

| tsclk_l           | Clock low time                                      |                                                                                             | 115     |      |         | ns   |

| tset_csb          | CSB setup time, CSB low before rising edge of SCLK  |                                                                                             | 400     |      |         | ns   |

| tset_sclk         | SCLK setup time, SCLK low before rising edge of CSB |                                                                                             | 400     |      |         | ns   |

| tset_si           | SI setup time                                       |                                                                                             | 200     |      |         | ns   |

| thold_si          | SI hold time                                        |                                                                                             | 200     |      |         | ns   |

| tr_in             | Rise time of input signal SI, SCLK, CSB             |                                                                                             |         |      | 100     | ns   |

| tf_in             | Fall time of input signal SI, SCLK, CSB             |                                                                                             |         |      | 100     | ns   |

| tcsb_hi_stdby     | Minimum CSB high time, switching from Standby mode  | Transfer of SPI–command to input register, valid before tsact mode transition delay expires |         | 5    | 10      | μS   |

| tcsb_hi_min       | Minimum CSB high time,<br>Active mode               |                                                                                             |         | 2    | 4       | μS   |

|                   |                                                     |                                                                                             |         |      |         |      |

<sup>9.</sup> Values based on design and/or characterization

Table 4. ELECTRICAL CHARACTERISTICS 4.5 V < Vcc < 5.25 V, 8 V < Vs < 18 V, -40°C < Tj < 150°C; unless otherwise noted.

| Symbol       | Parameter                                   | Test Conditions                                       | Min     | Тур | Max     | Unit |

|--------------|---------------------------------------------|-------------------------------------------------------|---------|-----|---------|------|

| TAL OUTPUT   | 50                                          |                                                       |         |     |         |      |

| Vsol         | Output low level                            | Iso = 5 mA                                            |         |     | 0.2·Vcc | V    |

| Vsoh         | Output high level                           | Iso = -5 mA                                           | 0.8·Vcc |     |         | V    |

| lleak_so     | Tristate leakage current                    | Vcsb = Vcc,<br>0 V < Vso < Vcc                        | -10     |     | 10      | μΑ   |

| Cso          | Tristate input capacitance                  | Vcsb = Vcc,<br>0 V < Vcc < 5.25 V (Note 10)           |         |     | 10      | pF   |

| TAL OUTPUT   | SO; TIMING                                  |                                                       |         |     |         |      |

| tr_so        | SO rise time                                | Cso = 100 pF                                          |         | 80  | 140     | ns   |

| tf_so        | SO fall time                                | Cso = 100 pF                                          |         | 50  | 100     | ns   |

| ten_so_tril  | SO enable time from tristate to low level   | Cso = 100 pF, Iload = 1 mA,<br>pull-up load to VCC    |         | 100 | 250     | ns   |

| tdis_so_ltri | SO disable time from low level to tristate  | Cso = 100 pF, Iload = 4 mA,<br>pull-up load to VCC    |         | 380 | 450     | ns   |

| ten_so_trih  | SO enable time from tristate to high level  | Cso = 100 pF, Iload = -1 mA, pull-down load to GND    |         | 100 | 250     | ns   |

| tdis_so_htri | SO disable time from high level to tristate | Cso = 100 pF, Iload = -4 mA,<br>pull-down load to GND |         | 380 | 450     | ns   |

| td_so        | SO delay time                               | Vso < 0.3·Vcc, or Vso > 0.7·Vcc,<br>Cso = 100 pF      |         | 50  | 250     | ns   |

<sup>10.</sup> Values based on design and/or characterization

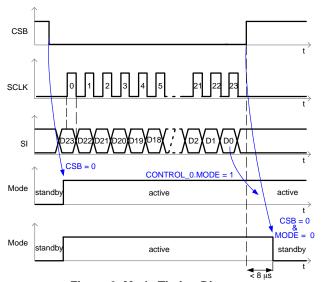

Figure 4. SPI Signals Timing Parameters

$\textbf{Table 4. ELECTRICAL CHARACTERISTICS} \ 4.5 \ \text{V} < \text{Vcc} < 5.25 \ \text{V}, \ 8 \ \text{V} < \text{Vs} < 18 \ \text{V}, \ -40 ^{\circ}\text{C} < \text{Tj} < 150 ^{\circ}\text{C}; \text{unless otherwise noted.}$

| Symbol         | Parameter                                                                   | Test Conditions                                                                       | Min | Тур | Max | Unit |

|----------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

| HERMAL PROTEC  | TION                                                                        |                                                                                       | •   | •   | •   | •    |

| Tjtw_on        | Temperature warning threshold                                               | Junction temperature                                                                  | 140 |     | 160 | °C   |

| Tjtw_hys       | Thermal warning hysteresis                                                  |                                                                                       |     | 5   |     | °C   |

| Tjsd_on        | Thermal shutdown threshold,<br>Tj increasing                                | Junction temperature                                                                  | 160 |     | 180 | °C   |

| Tjsd_off       | Thermal shutdown threshold,<br>Tj decreasing                                | Junction temperature                                                                  | 160 |     |     | °C   |

| Tjsd_hys       | Thermal shutdown hysteresis                                                 |                                                                                       |     | 5   |     | °C   |

| Tjsdtw_delta   | Temperature difference between warning and shutdown threshold               |                                                                                       |     | 20  |     | °C   |

| td_tx          | Filter time for thermal warning and shutdown                                | TW / TSD Global Status bits                                                           | 10  |     | 100 | μs   |

| PERATING MODE  | S TIMING                                                                    |                                                                                       |     |     |     |      |

| tact           | Time delay for mode change from<br>Unpowered mode into Standby<br>mode      | SPI communication ready after Vcc reached Vuv_vcc(off) threshold                      |     |     | 30  | μs   |

| tsact          | Time delay for mode change from<br>Standby mode into Active mode            | Time until output drivers are enabled after CSB going to high and CONTROL_0.MODE = 1  |     | 190 | 360 | μS   |

| tacts          | Time delay for mode change from<br>Active mode into Standby mode via<br>SPI | Time until output drivers are disabled after CSB going to high and CONTROL_0.MODE = 0 |     |     | 300 | μs   |

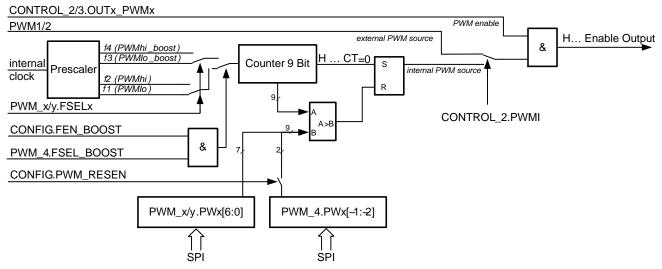

| NTERNAL PWM CO | ONTROL UNIT (OUT4 – OUT6)                                                   |                                                                                       |     |     |     |      |

| PWMIo          | PWM frequency, low selection                                                | CONTROL_2.PWMI=1,<br>PWMx.FSELx=0                                                     | 135 | 170 | 190 | Hz   |

| PWMhi          | PWM frequency, high selection                                               | CONTROL_2.PWMI=1,<br>PWMx.FSELx=1                                                     | 175 | 225 | 250 | Hz   |

| PWMIo_boost    | Boosted PWM frequency, low selection                                        | CONTROL_2.PWMI=1,<br>CONFIG.FEN_BOOST=1,<br>PWM_4.FSEL_BOOST=1,<br>PWMx.FSELx=0       | 360 | 440 | 500 | Hz   |

| PWMhi_boost    | Boosted PWM frequency, high selection                                       | CONTROL_2.PWMI=1,<br>CONFIG.FEN_BOOST=1,<br>PWM_4.FSEL_BOOST=1,<br>PWMx.FSELx=1       | 440 | 550 | 630 | Hz   |

#### DETAILED OPERATING AND PIN DESCRIPTION

#### General