## **Differential LVPECL** Voltage Controlled **Crystal Oscillator**

CVPD-920 Model 9×14 mm SMD, 3.3V, LVPECL

**Frequency Range: Frequency Pulling: Temperature Range:** (Option X)

Storage: Input Voltage: **Control Voltage:** Input Current: Output:

Aging:

Symmetry: Rise/Fall Time: Linearity: Logic:

Disable Time: Start-up Time: Phase Jitter: 12kHz to 80MHz Phase Noise: 10Hz 100Hz 1kHz 10kHz 100kHz

±20ppm APR Min 0°C to 70°C -40°C to 85°C -45°C to 90°C 3.3V ±0.3V 1.65V ±1.65V 88mA Max **Differential LVPECL** 45/55% Max @ zero crossing point 1ns Max (20% to 80%) ±10% Max Terminated to Vcc-2V into 50 ohms "0" = Vcc-1.85V Min, Vcc-1.62V Max "1" = Vcc-1.02V Min, Vcc-0.81V Max 200ns 1ms Typical, 2ms Max 0.5ps Typical, 1ps RMS Max -65 dBc/Hz Typical -98 dBc/Hz Typical -125 dBc/Hz Typical -140 dBc/Hz Typical -145 dBc/Hz Typical <3ppm 1<sup>st</sup> year, <1ppm every year thereafter

50 MHz to 125 MHz

Designed to meet today's requirements for 3.3V Differential LVPECL applications. The CVPD-920 is produced using our cost saving FR5 PCB and UM-1 overtone crystal technology. This design offers considerable cost savings over other HFF VCXO products when broad frequency pulling is not required. Also available in 14 pin dip fully hermetic package.

| C\              | /PD-9       | 20 X -        | 100.0 | 00 |

|-----------------|-------------|---------------|-------|----|

|                 |             | #2 #3         | #4    |    |

| #1 Crystek 9×1  | 4 SMD PEC   |               |       |    |

| #2 Model 920    |             | 2 10/10       |       |    |

| #3 Temp. Rang   |             |               |       |    |

| #4 Frequency in | n MHz: 3 or | 6 decimal pla | aces  |    |

| Enable/Disable Function                                                                                         |                              |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

| Pin 2                                                                                                           | Output Pin                   |  |  |  |

| Open<br>"0" level Vcc-1.620V Max<br>"1" level Vcc-1.025V Min                                                    | Active<br>Active<br>Disabled |  |  |  |

| Disabled State:<br>Pin 4 will assume a fixed level of logic "0"<br>Pin 5 will assume a fixed level of logic "1" |                              |  |  |  |

$\mathbf{RYS}$

CORPORATION

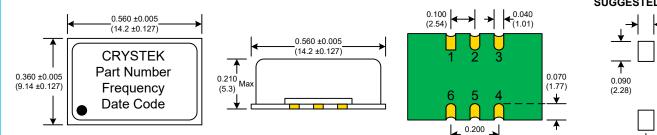

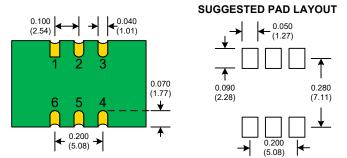

PAD FINISH: Immersion Gold (ENIG); 5 micro inches maximum

**RECOMMENDED REFLOW SOLDERING PROFILE** 900034 (See App Note listed on website) http://www.crystek.com/specification/reflow/900034.pdf

## NOT RECOMMENDED FOR NEW DESIGNS PLEASE USE CVPD-922 FAMILY

http://www.crystek.com/crystal/spec-sheets/vcxo/CVPD-922.pdf

| PIN | Function     |

|-----|--------------|

| 1   | Control Volt |

| 2   | E/D          |

| 3   | GND          |

| 4   | OUT          |

| 5   | COUT         |

| 6   | Vcc          |

Rev: N Date: 17-Jan-2023 Page 1 of 1

Crystek Corporation reserves the right to make changes to its products and/or information contained herein without notice. No liability is assumed as a result of its use or application.

16850 ORIGLE ROAD \* FORT MYERS, FLORIDA 33912 PHONE: 239-561-3311 • 800-237-3061 WWW.CRYSTEK.COM