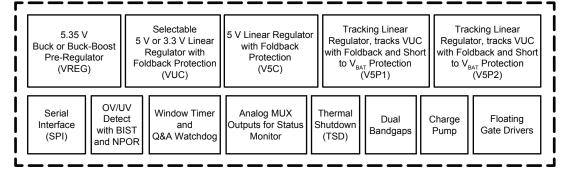

## Fully Integrated PMIC for Safety-Related Systems

with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

## FEATURES AND BENEFITS

- A<sup>2</sup>-SIL<sup>TM</sup> product—device features for safety-critical systems

- Automotive AEC-Q100 qualified

- Wide input voltage range, 3.8 to 36  $\rm V_{IN}$  operating range, 40  $\rm V_{IN}$  maximum

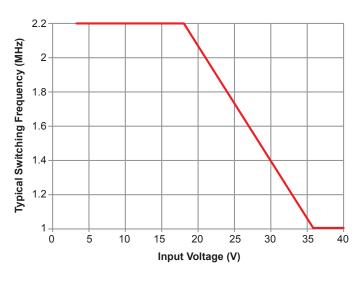

- 2.2 MHz buck or buck/boost pre-regulator (VREG: 5.35 V)

- Four internal linear regulators with foldback short-circuit protection

- □ VUC: selectable output (3.3 V / 5.0 V) regulator for microcontroller

- □ V5C: 5 V general purpose LDO regulator

- □ V5P1 and V5P2: two LDO regulators (track VUC voltage) with short-to-battery protection for remote sensors

- Q&A Watchdog and Window Watchdog timer

- Floating gate drivers with charge pump for external isolator NFET control

- Control and diagnostic reporting through a serial peripheral interface (SPI)

- Logic enable input (ENB) for microprocessor control

- Ignition enable input (ENBAT)

- Frequency dithering and controlled slew rate help reduce EMI/EMC

- Undervoltage protection for all output rails

- Thermal shutdown protection

- –40°C to 150°C junction temperature range

### **APPLICATIONS**

- Provides system power for (microcontroller/DSP, CAN, sensors, etc.) and high current isolation FET gate driver in automotive control modules, such as:

- □ Electronic power steering (EPS)

- □ Advanced braking systems (ABS)

- □ Other automotive applications

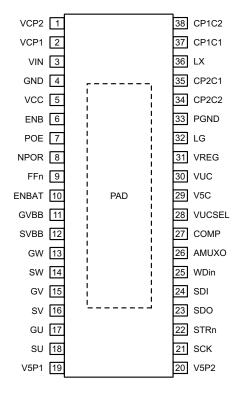

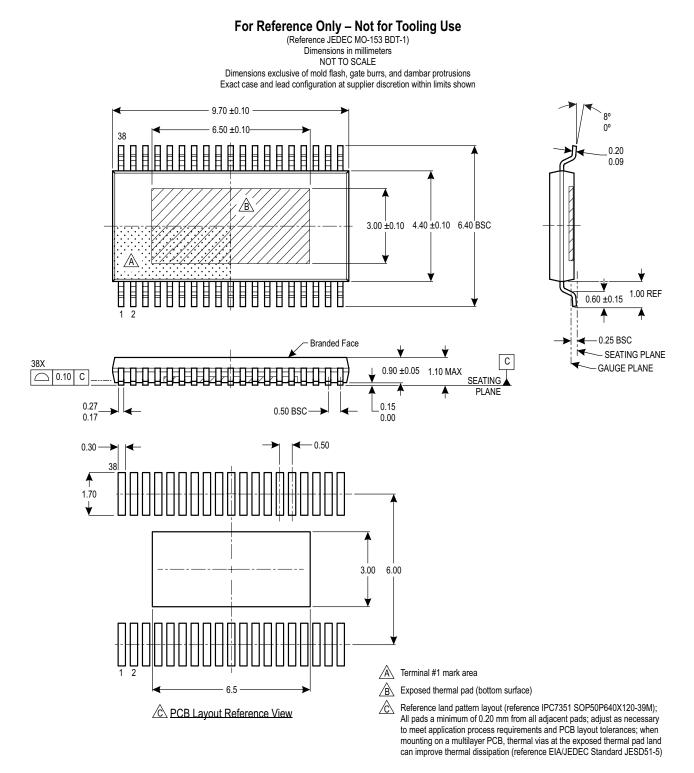

## PACKAGE: 38-Pin eTSSOP (suffix LV)

DESCRIPTION

The ARG82801-1 is a power management IC that integrates a buck or buck/boost pre-regulator, four LDOs, and four floating gate drivers. The pre-regulator uses a buck or buck/boost topology to efficiently convert automotive battery voltages into a tightly regulated intermediate voltage complete with control, diagnostics, and protections.

The output of the pre-regulator supplies a 3.3 V or 5.0 V selectable 350 mA linear regulator, a 5 V/115 mA linear regulator, and two 120 mA protected linear regulators which track VUC output. Designed to supply power for microprocessors, sensors, and CAN transceivers, the ARG82801-1 is ideal for underhood applications.

The independent floating gate drivers have the capability of controlling N-channel MOSFETs through SPI. These MOSFETs can be configured as phase or battery isolation devices in high current motor applications. An integrated charge pump allows the driver outputs to maintain the power MOSFETs in the on state over the full supply range with high phase-voltage slew rates.

Enable inputs to the ARG82801-1 include a logic level (ENB) and a high voltage (ENBAT). The ARG82801-1 also provides flexibility with disable function of the individual output rails through a serial peripheral interface (SPI).

Diagnostic outputs from the ARG82801-1 include a power-onreset output (NPOR) and a fault flag output (FFn) to alert the microprocessor that a fault has occurred. The microprocessor can read fault status through SPI. Dual bandgaps, one for regulation and one for fault checking, improve safety coverage and fault detection of the ARG82801-1.

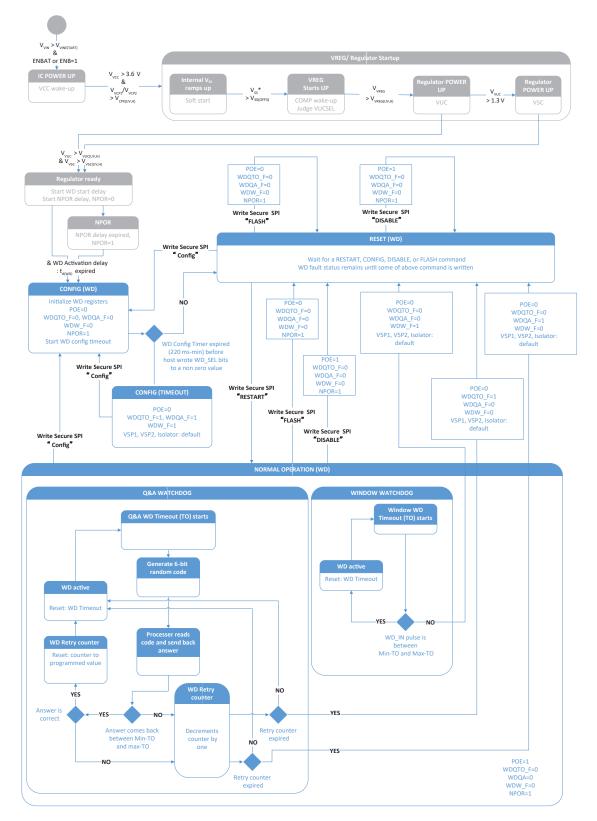

The ARG82801-1 contains two types of watchdog functions: Q&A and Window Watchdog timer. The watchdog timer is activated once it receives a valid SPI command from a processor. The watchdog can be put into flash mode or be reset via secure SPI commands.

The ARG82801-1 is supplied in a low-profile (1.2 mm maximum height) 38-lead eTSSOP package (suffix "LV") with exposed power pad.

ARG82801-1 Simplified Block Diagram

#### SELECTION GUIDE

| Part Number      | Package                        | Packing <sup>[1]</sup>      | Lead Frame     |  |

|------------------|--------------------------------|-----------------------------|----------------|--|

| ARG82801KLVATR-1 | 38-pin eTSSOP with thermal pad | 4000 pieces per 7-inch reel | 100% matte tin |  |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS<sup>[2]</sup>

| Characteristic            | Symbol                                                                  | Notes Rati                                    | ng Unit                   |

|---------------------------|-------------------------------------------------------------------------|-----------------------------------------------|---------------------------|

| VIN                       | V <sub>VIN</sub>                                                        | -0.3 to                                       | v 40 V                    |

|                           |                                                                         | With current limiting resistor [3] -13 to     | v 40 V                    |

| ENBAT                     | V <sub>ENBAT</sub>                                                      | -0.3 t                                        | o 8 V                     |

|                           | I <sub>ENBAT</sub>                                                      | ±75                                           | 5 mA                      |

| LX                        |                                                                         | -0.3 to V <sub>v</sub>                        | <sub>'IN</sub> + 0.3 V    |

|                           | V <sub>LX</sub>                                                         | t < 250 ns -1.                                | 5 V                       |

|                           |                                                                         | t < 50 ns V <sub>VIN</sub> .                  | + 3 V                     |

| GU, GV, GW, GVBB          | V <sub>GU</sub> , V <sub>GV</sub> , V <sub>GW</sub> , V <sub>GVBB</sub> | V <sub>SX</sub> – 0.3 to                      | V <sub>SX</sub> + 12 V    |

| SU, SV, SW, SVBB          |                                                                         | -6 to V <sub>v</sub>                          | <sub>'IN</sub> + 5 V      |

|                           | $V_{SU}, V_{SV}, V_{SW}, V_{SVBB}$                                      | Transient -18 to V                            | <sub>VIN</sub> + 5 V      |

| VCP1                      | V <sub>VCP1</sub>                                                       | V <sub>VIN</sub> - 0.3 to                     | V V <sub>VIN</sub> + 8 V  |

| VCP2                      | V <sub>VCP2</sub>                                                       | V <sub>VIN</sub> - 0.3 to                     | V <sub>VIN</sub> + 12 V   |

| CP1C1                     |                                                                         | $V_{VIN} \ge 12V$ $V_{VIN} - 12$ to           | V <sub>VIN</sub> + 0.3 V  |

| CPICI                     | V <sub>CP1C1</sub>                                                      | V <sub>VIN</sub> < 12V -0.3 to V <sub>V</sub> | <sub>'IN</sub> + 0.3 V    |

| CP2C1                     | V <sub>CP2C1</sub>                                                      | V <sub>VIN</sub> - 0.3 to <sup>v</sup>        | V <sub>VCP1</sub> + 0.3 V |

| CP1C2                     | V <sub>CP1C2</sub>                                                      | V <sub>VIN</sub> - 0.3 to <sup>v</sup>        | V <sub>VCP1</sub> + 0.3 V |

| CP2C2                     | V <sub>CP2C2</sub>                                                      | V <sub>CP1C2</sub> - 0.3 tc                   | V <sub>VCP2</sub> + 0.3 V |

| V5P1, V5P2                | V <sub>V5P1</sub> , V <sub>V5P2</sub>                                   | Independent of V <sub>VIN</sub> -1.0 to       | v 40 V                    |

| All other pins            |                                                                         | -0.3 t                                        | o 7 V                     |

| Junction Temperature      | TJ                                                                      | -40 to                                        | 150 °C                    |

| Storage Temperature Range | T <sub>stg</sub>                                                        | -40 to                                        | 150 °C                    |

[2] Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

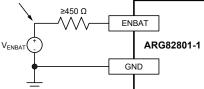

<sup>[3]</sup> The higher ENBAT ratings (-13 V and 40 V) are measured at node "A" in the following circuit configuration:

THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                         | Symbol                | Test Conditions <sup>[4]</sup> | Value | Unit |

|----------------------------------------|-----------------------|--------------------------------|-------|------|

| Junction to Ambient Thermal Resistance | $R_{	extsf{	heta}JA}$ | eTSSOP-38 (LV) package         | 30    | °C/W |

<sup>[4]</sup> Additional thermal information available on the Allegro website.

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

## **Table of Contents**

| Features and Benefits                  | 1  |

|----------------------------------------|----|

| Description                            | 1  |

| Applications                           | 1  |

| Package                                | 1  |

| Simplified Block Diagram               | 1  |

| Selection Guide                        | 2  |

| Absolute Maximum Ratings               | 2  |

| Thermal Characteristics                |    |

| Functional Block Diagram               | 4  |

| Pinout Diagram and Terminal List Table | 5  |

| Electrical Characteristics             | 6  |

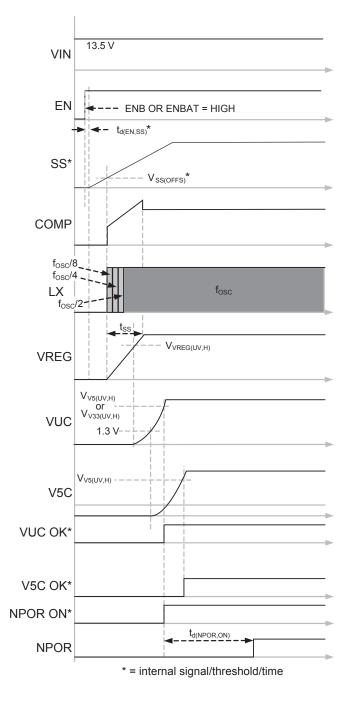

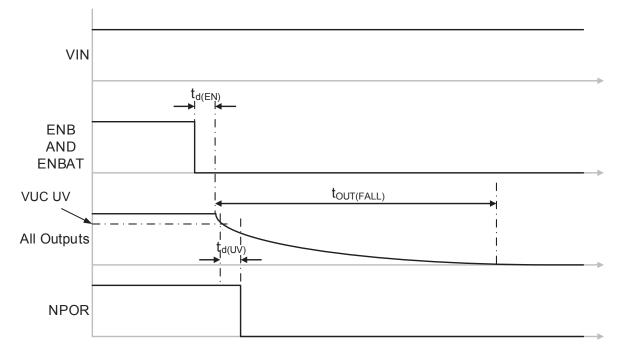

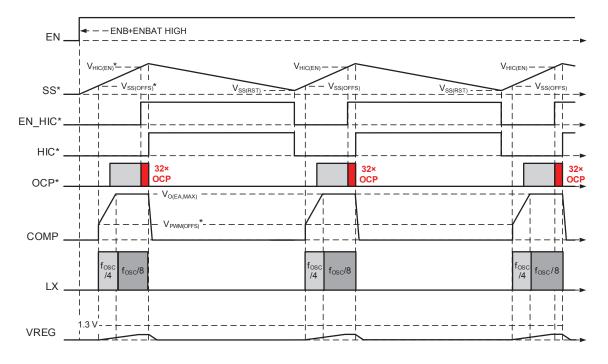

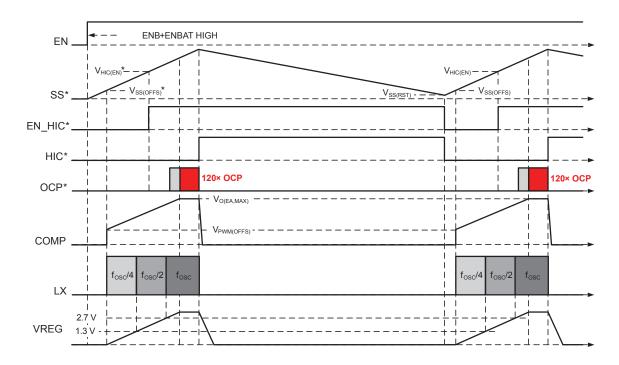

| Startup and Shutdown Logic             | 16 |

| Timing Diagrams                        |    |

| Summary of Fault Mode Operation        | 20 |

| Functional Description                 |    |

| Overview                               | 22 |

| Pre-Regulator                          | 22 |

| Bias Supply                            | 22 |

| Charge Pump                            |    |

| Bandgap                                |    |

| Enable                                 |    |

| Linear Regulators                      |    |

| Fault Detection and Reporting          |    |

| Startup Self-Test                      |    |

| Undervoltage Detect Self-Test          |    |

| Overvoltage Detect Self-Test           |    |

| -                                      |    |

| Overtemperature Shutdown Self-Test                                             | 23 |

|--------------------------------------------------------------------------------|----|

| Power-On Enable Self-Test                                                      | 23 |

| Watchdog Timer                                                                 | 23 |

| Analog Multiplexer Output                                                      | 24 |

| Floating MOSFET Gate Drivers                                                   | 24 |

| Serial Communication Interface                                                 | 27 |

| Register Mapping                                                               | 28 |

| Design and Component Selection                                                 | 38 |

| Setting Up the Pre-Regulator                                                   | 38 |

| Charge Pump Capacitors                                                         | 38 |

| PWM Switching Frequency                                                        | 38 |

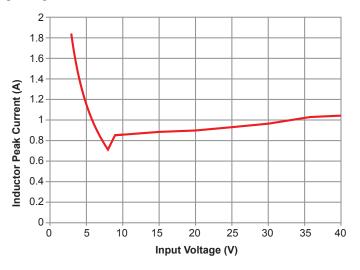

| Pre-Regulator Output Inductor                                                  | 38 |

| Pre-Regulator Output Capacitors                                                | 39 |

| Ceramic Input Capacitors                                                       | 39 |

| Buck-Boost Asynchronous Diode (D1)                                             | 40 |

| Boost MOSFET (Q1)                                                              | 40 |

| Boost Diode (D2)                                                               | 40 |

| Pre-Regulator Soft Start and Hiccup Mode (C <sub>SS1</sub> )                   | 40 |

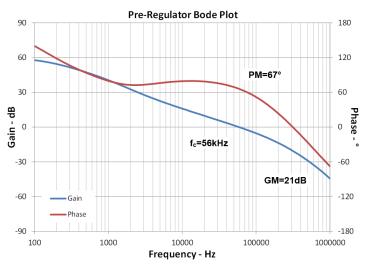

| Pre-Regulator Compensation (R <sub>Z</sub> , C <sub>Z</sub> , C <sub>P</sub> ) | 40 |

| Linear Regulators                                                              | 41 |

| Internal Bias (VCC)                                                            | 41 |

| Signal Pins (NPOR, FFn, POE)                                                   | 41 |

| PCB Layout Recommendations                                                     | 42 |

| Package Outline Drawing                                                        | 43 |

|                                                                                |    |

## Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

⊣H<sup>0.22 µF</sup> 2.2 µF Πh 1 μF ARG82801-1 VBAT Charge Pump1 Charge Pump2 VREG ¢ BG1\_UV VCP1 BG1 REMOVE D2 AND Q1 FOR BUCK ONLY MODE D2 ₽ L1 3G2\_UV 5.35 V LDC 50 V 1210 BUCK-BOOST PRE-REGULATOR (VREG) (w/ Hiccup Mode) ≭. D1 ΙI Ţ ž I I BG1 OSC2 CI K... 10 µF VREG ON VCP1 UV OP PWM CLK @ Fosc osc VRE KEY\_S VUCSEL state will be latched at start-up, don't care during operation Tie to VCC (5 Vout) SS OK Soft Start tss MASTER IC POR FOLDBAG TSD Tie to GND (3.3 Vout) ¥ TEMF 5/3.3V LDO BG1 5/3.3 V 350 mA LDOs C MDOE 2.2 µF FOL STARTUP/ SHUTDOWN SEQUENCE VREG ON 5V LDO ► 5 V 115 mA BG1 -LDOs ON LDOs ON 2.2 µF FALLIN DELAY V5 Short to VBAT FOLDBA ┢╾╏ Tracking LDO 5 V (VUCSEL=Hi) 120 mA Short to VBAT Protection 2.2 µF 1 1 İ Ī FOLDE 5 V (VUCSEL=Hi) 120 mA racking LDO μC ENABLE 2.2 µF RENB EN REN ENB Ī VBAT VCP2 Ĵ ON/OFF BG ENVBB SVBB UV RST ate-Driv ş ENV NPOF SVBB) GU (w.r.t. SU) GV (w.r.t. SV)  $\triangleleft$ MPC VUC ł OV/UV DETEC & NPOR & Fault Fla DE /CP2 /REG /UC /UC /5C /5P1 SU UV 3-Phase BLDC Motor 3-phase BLDC Motor Driver To SPI register Fit TSD Б CLK<sub>1MH</sub> MPOR WD\_F AMUXO VIN x Q&A VATCH TIME (QAD WD\_F ti ti POE Contl. SPI GND PGND

#### FUNCTIONAL BLOCK DIAGRAM

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

#### Package LV, 38-Pin eTSSOP Pinout Diagram

| Number   | Name   | Function                                                                                                                         |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 1        | VCP2   | Charge pump 2 reservoir capacitor connection                                                                                     |

| 2        | VCP1   | Charge pump 1 reservoir capacitor connection                                                                                     |

| 3        | VIN    | Input voltage pin                                                                                                                |

| 4        | GND    | Ground                                                                                                                           |

| 5        | VCC    | Internal voltage regulator bypass capacitor pin                                                                                  |

| 6        | ENB    | Logic enable input from a microcontroller or DSP                                                                                 |

| 7        | POE    | Gate drive enable signal, goes low if a watchdog fault is detected                                                               |

| 8        | NPOR   | Active low, open-drain regulator fault detection output                                                                          |

| 9        | FFn    | Fault Flag to microcontroller                                                                                                    |

| 10       | ENBAT  | Ignition enable input from the key/switch via a series resistor                                                                  |

| 11       | GVBB   | Battery line MOSFET gate drive                                                                                                   |

| 12       | SVBB   | Battery line MOSFET source reference                                                                                             |

| 13       | GW     | W phase MOSFET gate drive                                                                                                        |

| 14       | SW     | W phase MOSFET source reference                                                                                                  |

| 15       | GV     | V phase MOSFET gate drive                                                                                                        |

| 16       | SV     | V phase MOSFET source reference                                                                                                  |

| 17       | GU     | U phase MOSFET gate drive                                                                                                        |

| 18       | SU     | U phase MOSFET source reference                                                                                                  |

| 19       | V5P1   | 5 V protected regulator output which tracks VUC                                                                                  |

| 20       | V5P2   | 5 V protected regulator output which tracks VUC                                                                                  |

| 21       | SCK    | SPI clock input from the microcontroller                                                                                         |

| 22       | STRn   | SPI chip select input from the microcontroller                                                                                   |

| 23       | SDO    | SPI data output to the microcontroller                                                                                           |

| 24       | SDI    | SPI data input from the microcontroller                                                                                          |

| 25       | WDin   | Watchdog refresh input from a microcontroller or DSP                                                                             |

| 26       | AMUXO  | Analog Multiplexer output                                                                                                        |

| 27       | COMP   | Error amplifier compensation network pin for the buck/boost pre-regulator                                                        |

| 28       | VUCSEL | VUC output voltage selection pin:<br>1 (High: should be tied to VCC), $V_{VUC} = 5 V$<br>0 (Low: tied to GND), $V_{VUC} = 3.3 V$ |

| 29       | V5C    | 5 V regulator output                                                                                                             |

| 30       | VUC    | Selectable V <sub>OUT</sub> (5 V or 3.3 V by VUCSEL) regulator output                                                            |

| 31       | VREG   | Voltage feedback input of the pre-regulator and supply input of the linear regulators                                            |

| 32       | LG     | Boost gate drive output for the buck/boost pre-regulator                                                                         |

| 33       | PGND   | Power ground                                                                                                                     |

| 34       | CP2C2  | Charge pump 2 capacitor connection                                                                                               |

| 35       | CP2C1  | Charge pump 2 capacitor connection                                                                                               |

| 36       | LX     | Switching node for the buck/boost pre-regulator                                                                                  |

| 37       | CP1C1  | Charge pump 1 capacitor connection                                                                                               |

| 38       | CP1C2  | Charge pump 1 capacitor connection                                                                                               |

| <u> </u> | PAD    | Exposed thermal pad                                                                                                              |

## ELECTRICAL CHARACTERISTICS <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> ≤ V<sub>VIN</sub> ≤ 36 V, –40°C ≤ T<sub>J</sub> ≤ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                               | Symbol                       | Test Conditions                                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|----------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| GENERAL SPECIFICATIONS                       |                              | ·`                                                                                                                                                                                 |      |      |      |      |

| Operating Input Valtage [2]                  |                              | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> and VREG in regulating,<br>Buck-Boost Mode                                                                                        | 3.8  | 13.5 | 36   | V    |

| Operating Input Voltage <sup>[2]</sup>       | V <sub>VIN</sub>             | After $V_{VIN} > V_{VIN(START)}$ and VREG in regulating, Buck Mode                                                                                                                 | 5.5  | 13.5 | 36   | V    |

| VIN UVLO Start Voltage                       | V <sub>VIN(START)</sub>      | V <sub>VIN</sub> rising                                                                                                                                                            | 4.55 | 4.8  | 5.05 | V    |

| VIN UVLO Stop Voltage                        | V <sub>VIN(STOP)</sub>       | V <sub>VIN</sub> falling                                                                                                                                                           | 3.25 | 3.5  | 3.75 | V    |

| VIN UVLO Hysteresis                          | V <sub>VIN(HYS)</sub>        | V <sub>VIN(START)</sub> – V <sub>VIN(STOP)</sub>                                                                                                                                   | _    | 1.3  | _    | V    |

|                                              | ا <sub>م</sub>               | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.6 V (no PWM)                                                                                                                      | -    | 13   | -    | mA   |

| VIN Supply Quiescent Current [1]             | I <sub>Q(SLEEP)</sub>        | $V_{VIN}$ = 13.5 V,<br>V <sub>ENBAT</sub> = Low and V <sub>ENB</sub> = Low, T <sub>J</sub> = 25°C                                                                                  | _    | _    | 13   | μA   |

| PWM SWITCHING FREQUENC                       | Y AND DITHERI                | NG                                                                                                                                                                                 |      |      |      |      |

| Switching Frequency                          | f <sub>OSC</sub>             | Dithering off                                                                                                                                                                      | 2.0  | 2.2  | 2.4  | MHz  |

| Frequency Dithering                          | Δf <sub>OSC</sub>            | As a percent of f <sub>OSC</sub>                                                                                                                                                   | -    | ±10  | -    | %    |

|                                              | N                            | V <sub>VIN</sub> rising                                                                                                                                                            | 8.5  | 9.0  | 9.5  | V    |

| VIN Dithering Start Threshold <sup>[2]</sup> | V <sub>VIN(DITHER,ON)</sub>  | V <sub>VIN</sub> falling                                                                                                                                                           | -    | 17   | -    | V    |

| VIN Dithering Stop Threshold [2]             | V <sub>VIN(DITHER,OFF)</sub> | V <sub>VIN</sub> falling                                                                                                                                                           | 7.8  | 8.3  | 8.8  | V    |

|                                              |                              | V <sub>VIN</sub> rising                                                                                                                                                            | -    | 18   | -    | V    |

| CHARGE PUMP (VCP1 AND VC                     | P2)                          |                                                                                                                                                                                    |      |      |      |      |

|                                              | V <sub>VCP1</sub>            | $V_{VCP1} - V_{VIN}, V_{VIN} \ge 9 \text{ V}, I_{VCP1} > -5 \text{ mA},$<br>Buck Mode                                                                                              | 4.1  | 6.6  | _    | V    |

| VCP1 Output Voltage                          |                              | $V_{VCP1} - V_{VIN}$ , 5.5 V < $V_{VIN} \le 9$ V, $I_{VCP1} > -5$ mA, Buck Mode                                                                                                    | 3.6  | 4.4  | _    | V    |

|                                              |                              | $\label{eq:V_VCP1} \begin{array}{c} V_{VCP1} - V_{VIN}, \ 3.8 \ V < V_{VIN} \le 5.5 \ V, \\ V_{REG} = 5.35 \ V, \ I_{VCP1} > -5 \ \text{mA}, \ \text{Buck-Boost Mode} \end{array}$ | 3.0  | 3.8  | _    | V    |

|                                              |                              | $V_{VCP2} - V_{VIN}, V_{VIN} > 9 V, I_{VCP2} > -1 mA,$<br>Buck Mode                                                                                                                | 9    | 10   | _    | V    |

| VCP2 Output Voltage                          | V <sub>VCP2</sub>            | $V_{VCP2} - V_{VIN}, ~5.5~V < V_{VIN} \le 9~V,~I_{VCP2} > -1~mA,$ Buck Mode                                                                                                        | 8    | 10   | _    | V    |

|                                              |                              | $\label{eq:VVCP2} \begin{array}{l} V_{VCP2} - V_{VIN}, \ 3.8 \ V < V_{VIN} \leq 5.5 \ V, \ V_{VREG} = \\ 5.35 \ V, \ I_{VCP2} > -1 \ mA, \ Buck-Boost \ Mode \end{array}$          | 6.6  | 9.5  | _    | V    |

| Switching Frequency                          | f <sub>SW(CP)</sub>          |                                                                                                                                                                                    | -    | 65   | -    | kHz  |

| VCC PIN VOLTAGE                              |                              |                                                                                                                                                                                    |      |      |      |      |

| Output Voltage                               | V <sub>VCC</sub>             | V <sub>VREG</sub> = 5.35 V                                                                                                                                                         | -    | 4.4  | -    | V    |

| THERMAL PROTECTION                           |                              |                                                                                                                                                                                    |      |      |      |      |

| Thermal Shutdown Threshold [2]               | T <sub>TSD</sub>             | T <sub>J</sub> rising                                                                                                                                                              | 165  | _    | _    | °C   |

| Thermal Shutdown Hysteresis <sup>[2]</sup>   | T <sub>HYS</sub>             |                                                                                                                                                                                    | _    | 15   | _    | °C   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

$^{[3]}$  Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

#### ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                      | Symbol                    | Test Conditions                                                                                                                                                                                  | Min. | Тур. | Max. | Unit |

|-------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUTPUT VOLTAGE SPECIFICAT           | IONS                      |                                                                                                                                                                                                  | ·    |      |      |      |

| Pre-Regulator Output Voltage [2]    | V <sub>VREG</sub>         | V <sub>VIN</sub> = 13.5 V, 0.1 A < I <sub>VREG</sub> < 1.2 A                                                                                                                                     | 5.25 | 5.35 | 5.45 | V    |

| PULSE-WIDTH MODULATION (P           |                           | ·                                                                                                                                                                                                | ÷    |      |      |      |

| PWM Ramp Offset                     | V <sub>PWM(OFFS)</sub>    | V <sub>COMP</sub> for 0% duty cycle                                                                                                                                                              | -    | 480  | -    | mV   |

| LX Rising Slew Rate [2]             | SR <sub>LXRISE</sub>      | V <sub>VIN</sub> = 13.5 V, 10% to 90%, I <sub>VREG</sub> = 1 A                                                                                                                                   | -    | 1.4  | -    | V/ns |

| LX Falling Slew Rate <sup>[2]</sup> | SR <sub>LXFALL</sub>      | V <sub>VIN</sub> = 13.5 V, 90% to 10%, I <sub>VREG</sub> = 1 A                                                                                                                                   | -    | 1.5  | -    | V/ns |

| Buck Minimum On-Time                | t <sub>ON(BUCK,MIN)</sub> |                                                                                                                                                                                                  | -    | 85   | 160  | ns   |

| Buck Maximum Duty Cycle             | D <sub>BUCK(MAX)</sub>    | V <sub>VIN</sub> < 7.8 V                                                                                                                                                                         | -    | -    | 100  | %    |

| Boost Maximum Duty Cycle            | D <sub>BST(MAX)</sub>     | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> , and VREG in regulating, V <sub>VIN</sub> = 3.8 V                                                                                              | -    | 65   | _    | %    |

| COMP to LX Current Gain             | gm <sub>POWER</sub>       |                                                                                                                                                                                                  | -    | 4.57 | -    | A/V  |

| Slope Compensation [2]              | S <sub>E</sub>            |                                                                                                                                                                                                  | 1.1  | 1.62 | 2.15 | A/µs |

| INTERNAL MOSFET                     |                           |                                                                                                                                                                                                  | ·    |      | •    |      |

|                                     |                           | V <sub>VIN</sub> = 13.5 V, T <sub>J</sub> = -40°C <sup>[2]</sup> , I <sub>DS</sub> = 0.1 A                                                                                                       | -    | 60   | 90   | mΩ   |

| MOSFET On Resistance                | R <sub>DS(on)</sub>       | V <sub>VIN</sub> = 13.5 V, T <sub>J</sub> = 25°C <sup>[3]</sup> , I <sub>DS</sub> = 0.1 A                                                                                                        | -    | 95   | 115  | mΩ   |

|                                     |                           | V <sub>VIN</sub> = 13.5 V, T <sub>J</sub> = 150°C, I <sub>DS</sub> = 0.1 A                                                                                                                       | -    | 160  | 190  | mΩ   |

| MOOFFEE Laglaces Current            |                           | $V_{ENBAT} \le 2.2 \text{ V}, V_{ENB} = \text{Low}, V_{LX} = 0 \text{ V}, V_{VIN} = 16 \text{ V}, -40^{\circ}\text{C} < \text{T}_{J} < 85^{\circ}\text{C}$ <sup>[3]</sup>                        | -    | -    | 10   | μA   |

| MOSFET Leakage Current              | I <sub>FET(LKG)</sub>     | $V_{\text{ENBAT}} \le 2.2 \text{ V}, V_{\text{ENB}} \le \text{Low}, V_{\text{LX}} = 0 \text{ V}, V_{\text{VIN}} = 16 \text{ V}, -40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ | -    | 50   | 150  | μA   |

| ERROR AMPLIFIER                     |                           |                                                                                                                                                                                                  |      |      |      |      |

| Open Loop Voltage Gain              | A <sub>VOL</sub>          |                                                                                                                                                                                                  | -    | 60   | -    | dB   |

| Transconductance                    | c1722                     | V <sub>SS</sub> (internal signal) = 750 mV                                                                                                                                                       | 520  | 720  | 920  | μA/V |

| Transconductance                    | gm <sub>EA</sub>          | V <sub>SS</sub> (internal signal) = 500 mV                                                                                                                                                       | 260  | 360  | 460  | μA/V |

| Output Current                      | I <sub>O(EA)</sub>        |                                                                                                                                                                                                  | -    | ±75  | -    | μA   |

|                                     |                           | V <sub>VIN</sub> < 8.5 V                                                                                                                                                                         | 1.2  | 1.52 | 2.1  | V    |

| Maximum Output Voltage              | V <sub>O(EA,MAX)</sub>    | V <sub>VIN</sub> > 9.5 V                                                                                                                                                                         | 0.9  | 1.22 | 1.7  | V    |

| Minimum Output Voltage              | V <sub>O(EA,MIN)</sub>    |                                                                                                                                                                                                  | -    | _    | 300  | mV   |

| COMP Pull-Down Resistance           | R <sub>COMP</sub>         | HICCUP = 1 or FAULT = 1 or<br>V <sub>ENBAT</sub> = Low and V <sub>ENB</sub> = Low                                                                                                                | -    | 1    | _    | kΩ   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking). [2] Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                   | Symbol                    | Test Conditions                                                             | Min.   | Тур.                | Max. | Unit          |

|----------------------------------|---------------------------|-----------------------------------------------------------------------------|--------|---------------------|------|---------------|

| BOOST MOSFET (LG) GATE DR        | IVER                      | ·                                                                           |        |                     |      |               |

| LG High Output Voltage           | V <sub>LG(ON)</sub>       | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V                          | 4.6    | -                   | 5.35 | V             |

| LG Low Output Voltage            | V <sub>LG(OFF)</sub>      | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.35 V                       | -      | 0.2                 | 0.4  | V             |

| LG Source Current <sup>[1]</sup> | I <sub>LG(ON)</sub>       | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V   | -      | -300                | -    | mA            |

| LG Sink Current <sup>[1]</sup>   | I <sub>LG(OFF)</sub>      | V <sub>VIN</sub> =13.5 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V | -      | 150                 | -    | mA            |

| SOFT-START                       |                           |                                                                             |        | ·                   |      |               |

| SS Ramp Time <sup>[2]</sup>      | t <sub>ss</sub>           |                                                                             | -      | 900                 | -    | μs            |

| SS PWM Frequency Foldback        |                           | $0 \text{ V} \leq \text{V}_{\text{VREG}} < 0.67 \text{ V}$ typical          | -      | f <sub>OSC</sub> /8 | _    | -             |

|                                  | 4                         | $0.67 \text{ V} \le \text{V}_{\text{VREG}} < 1.34 \text{ V}$ typical        | -      | f <sub>OSC</sub> /4 | _    | -             |

|                                  | f <sub>SW(SS)</sub>       | 1.34 V ≤ V <sub>VREG</sub> < 2.68 V typical                                 | -      | f <sub>OSC</sub> /2 | _    | -             |

|                                  |                           | V <sub>VREG</sub> ≥ 2.68 V typical                                          | -      | f <sub>OSC</sub>    | -    | -             |

| HICCUP MODE                      | ,                         |                                                                             | ,<br>, | •                   |      | °             |

| Hiccup Enable Delay Time [2]     | t <sub>HIC(EN)</sub>      |                                                                             | -      | 230                 | _    | μs            |

| Hiccup Recovery Time [2]         | t <sub>HIC(REC)</sub>     |                                                                             | -      | 930                 | -    | μs            |

|                                  |                           | $V_{VREG}$ < 1.3 $V_{TYP}$ , $V_{COMP}$ = $V_{O(EA,MAX)}$                   | -      | 32                  | _    | PWM<br>cycles |

| Hiccup OCP PWM Counts            | thic(ocp)                 | $V_{VREG}$ > 1.3 $V_{TYP}$ , $V_{COMP}$ = $V_{O(EA,MAX)}$                   | -      | 120                 | _    | PWM<br>cycles |

| CURRENT PROTECTIONS              |                           |                                                                             |        |                     |      |               |

| Pulso by Pulso Current Limit     |                           | V <sub>VIN</sub> < 8.5 V                                                    | 3.83   | 4.2                 | 4.77 | A             |

| Pulse-by-Pulse Current Limit     | I <sub>LIM(ton,min)</sub> | V <sub>VIN</sub> > 9.5 V                                                    | 2.49   | 2.8                 | 3.11 | A             |

| LX Short-Circuit Current Limit   | I <sub>LIM(LX)</sub>      | Latched fault after 2 <sup>nd</sup> detection                               | 5.3    | 7.1                 | -    | A             |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

[4] The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                                          | Symbol                    | Test Conditions                                                              | Min.  | Тур.  | Max.                                   | Unit |

|---------------------------------------------------------|---------------------------|------------------------------------------------------------------------------|-------|-------|----------------------------------------|------|

| MISSING ASYNCHRONOUS DIODE                              | (D1) PROTE                | CTION                                                                        |       |       |                                        |      |

| Detection Level                                         | V <sub>D(OPEN)</sub>      |                                                                              | -1.9  | -1.4  | -1.0                                   | V    |

| Time Filtering <sup>[2]</sup>                           | t <sub>D(OPEN)</sub>      |                                                                              | 50    | _     | 250                                    | ns   |

| VUC, V5C, V5P1, V5P2 LINEAR REG                         | ULATORS                   |                                                                              | ·     | `     | `````````````````````````````````````` |      |

| VUC Accuracy and Load Regulation (5 V <sub>OUT</sub> )  | V <sub>VUC5</sub>         | 10 mA < I <sub>VUC</sub> < 350 mA, V <sub>VREG</sub> = 5.25 V,<br>VUCSEL = 1 | 4.9   | 5.0   | 5.1                                    | V    |

| VUC Accuracy and Load Regulation $(3.3 V_{OUT})^{[2]}$  | V <sub>VUC33</sub>        | 10 mA < I <sub>VUC</sub> < 350 mA, V <sub>VREG</sub> = 5.25 V,<br>VUCSEL = 0 | 3.23  | 3.30  | 3.37                                   | V    |

| VUC Output Capacitance Range <sup>[2]</sup>             | C <sub>OUT(VUC)</sub>     |                                                                              | 1.0   | _     | 15                                     | μF   |

| V5C Accuracy and Load Regulation                        | V <sub>V5C</sub>          | 5 mA < I <sub>V5C</sub> < 115 mA, V <sub>VREG</sub> = 5.25 V                 | 4.9   | 5.0   | 5.1                                    | V    |

| V5C Output Capacitance Range [2]                        | C <sub>OUT(V5C)</sub>     |                                                                              | 1.0   | -     | 15                                     | μF   |

| V5P1 Accuracy and Load Regulation (5 V <sub>OUT</sub> ) | V <sub>V5P1</sub>         | 5 mA < I <sub>V5P1</sub> < 120 mA, V <sub>VREG</sub> = 5.25 V,<br>VUCSEL = 1 | 4.9   | 5.0   | 5.1                                    | V    |

| V5P1 Output Capacitance Range [2]                       | C <sub>OUT(V5P1)</sub>    |                                                                              | 1.0   | _     | 15                                     | μF   |

| V5P2 Accuracy and Load Regulation (5 V <sub>OUT</sub> ) | V <sub>V5P2</sub>         | 5 mA < I <sub>V5P2</sub> < 120 mA, V <sub>VREG</sub> = 5.25 V,<br>VUCSEL = 1 | 4.9   | 5.0   | 5.1                                    | V    |

| V5P2 Output Capacitance Range [2]                       | C <sub>OUT(V5P2)</sub>    |                                                                              | 1.0   | _     | 15                                     | μF   |

| V5Px/VUC Tracking Ratio                                 | TRACK <sub>V5Px/VUC</sub> | V <sub>VUC</sub> = 3.3 V, V <sub>V5Px</sub> / V <sub>3V3</sub> , VUCSEL = 0  | 1.500 | 1.515 | 1.530                                  | V/V  |

| V5Px Tracking Accuracy, $V_{VUC}$ = 3.3 V               | TRACK <sub>33</sub>       | $I_{V5Px} = I_{VUC} = 60 \text{ mA}, \text{ VUCSEL} = 0$                     | -0.66 | _     | 0.66                                   | %    |

| V5Px Tracking Accuracy, $V_{VUC}$ = 5 V                 | V <sub>TRACK(5V)</sub>    | $I_{V5Px} = I_{VUC} = 60 \text{ mA}, \text{ VUCSEL} = 1$                     | -25   | _     | 25                                     | mV   |

| VUC OVERCURRENT PROTECTION                              | 1                         |                                                                              | ·     |       |                                        |      |

| VUC Current Limit <sup>[1]</sup>                        | I <sub>VUC(LIM)</sub>     |                                                                              | -360  | -570  | -800                                   | mA   |

| VUC Foldback Current <sup>[1]</sup>                     | I <sub>VUC(FBK)</sub>     | V <sub>VUC</sub> = 0 V                                                       | -60   | -170  | -250                                   | mA   |

| V5C OVERCURRENT PROTECTION                              |                           |                                                                              | ·     |       |                                        |      |

| V5C Current Limit <sup>[1]</sup>                        | I <sub>V5C(LIM)</sub>     |                                                                              | -120  | -180  | -250                                   | mA   |

| V5C Foldback Current <sup>[1]</sup>                     | I <sub>V5C(FBK)</sub>     | V <sub>V5C</sub> = 0 V                                                       | -15   | -60   | -125                                   | mA   |

| <b>V5P1 OVERCURRENT PROTECTIO</b>                       | N                         |                                                                              |       |       |                                        |      |

| V5P1 Current Limit <sup>[1]</sup>                       | I <sub>V5P1(LIM)</sub>    |                                                                              | -135  | -230  | -350                                   | mA   |

| V5P1 Foldback Current <sup>[1]</sup>                    | I <sub>V5P1(FBK)</sub>    | V <sub>V5P1</sub> = 0 V                                                      | -20   | -60   | -125                                   | mA   |

| V5P2 OVERCURRENT PROTECTIO                              |                           |                                                                              |       |       |                                        |      |

| V5P2 Current Limit <sup>[1]</sup>                       | I <sub>V5P2(LIM)</sub>    |                                                                              | -135  | -230  | -350                                   | mA   |

| V5P2 Foldback Current <sup>[1]</sup>                    | I <sub>V5P2(FBK)</sub>    | V <sub>V5P2</sub> = 0 V                                                      | -20   | -60   | -125                                   | mA   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                                                            | Symbol                    | Test Conditions                                                                      | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| VUC, V5C, V5P1, AND V5P2 STAR                                             | TUP TIMING                |                                                                                      |      | •    |      |      |

| VUC Startup Time (5 V <sub>OUT</sub> ) <sup>[2]</sup>                     | t <sub>VUC5(START)</sub>  | $C_{VUC} \le 2.9 \ \mu\text{F}$ , Load = 33 $\Omega \pm 5\%$ (152 mA),<br>VUCSEL = 1 | -    | -    | 1.0  | ms   |

| VUC Startup Time (3.3 V <sub>OUT</sub> ) <sup>[2]</sup>                   | t <sub>VUC33(START)</sub> | $C_{VUC} \le 2.9 \ \mu\text{F}$ , Load = 33 $\Omega \pm 5\%$ (100 mA),<br>VUCSEL = 0 | -    | _    | 1.0  | ms   |

| V5C Startup Time <sup>[2]</sup>                                           | t <sub>V5C(START)</sub>   | C <sub>V5C</sub> ≤ 2.9 μF, Load = 100 Ω ±5% (50 mA)                                  | -    | _    | 1.0  | ms   |

| V5P1 Startup Time <sup>[2]</sup>                                          | t <sub>V5P1(START)</sub>  | C <sub>V5P1</sub> ≤ 2.9 μF, Load = 100 Ω ±5%                                         | _    | _    | 1.0  | ms   |

| V5P2 Startup Time <sup>[2]</sup>                                          | t <sub>VP2(START)</sub>   | C <sub>V5P2</sub> ≤ 2.9 μF, Load = 100 Ω ±5%                                         | -    | _    | 1.0  | ms   |

| IGNITION ENABLE (ENBAT) INPU                                              |                           |                                                                                      |      | •    | ·    |      |

|                                                                           | V <sub>ENBAT(H)</sub>     | V <sub>ENBAT</sub> rising                                                            | 2.9  | 3.1  | 3.5  | V    |

| ENBAT Thresholds                                                          | V <sub>ENBAT(L)</sub>     | V <sub>ENBAT</sub> falling                                                           | 2.2  | 2.6  | 2.9  | V    |

| ENBAT Hysteresis                                                          | V <sub>ENBAT(HYS)</sub>   | V <sub>ENBAT(H)</sub> – V <sub>ENBAT(L)</sub>                                        | -    | 500  | _    | mV   |

| ENBAT Bias Current <sup>[1]</sup>                                         |                           | V <sub>ENBAT</sub> = 0.8 V via a 1 kΩ series resistor                                | -    | _    | 5    | μA   |

|                                                                           | I <sub>ENBAT(BIAS)</sub>  | $V_{ENBAT}$ = 5.5 V via a 1 kΩ series resistor                                       | -    | 50   | 100  | μA   |

|                                                                           |                           | V <sub>ENBAT</sub> = 20 V via a 1 kΩ series resistor                                 | -    | -    | 2    | mA   |

| ENBAT Pulldown Resistance                                                 | R <sub>ENBAT</sub>        | V <sub>ENBAT</sub> < 1.2 V                                                           | -    | 600  | _    | kΩ   |

| LOGIC ENABLE (ENB) INPUT                                                  |                           |                                                                                      |      |      |      |      |

|                                                                           | V <sub>ENB(H)</sub>       | V <sub>ENB</sub> rising                                                              | -    | _    | 2.0  | V    |

| ENB Thresholds                                                            | V <sub>ENB(L)</sub>       | V <sub>ENB</sub> falling                                                             | 0.8  | _    | _    | V    |

| ENB Bias Current <sup>[1]</sup>                                           | I <sub>ENB(IN)</sub>      | V <sub>ENB</sub> = 3.3 V                                                             | -    | _    | 175  | μA   |

| ENB Resistance                                                            | R <sub>ENB</sub>          |                                                                                      | -    | 60   | _    | kΩ   |

| ENB/ENBAT FILTER/DEGLITCH                                                 | ·                         |                                                                                      |      |      |      |      |

| Enable Filter/Deglitch Time                                               | t <sub>d(EN)</sub>        |                                                                                      | 10   | 15   | 20   | μs   |

| VUC, V5C, V5P1, AND V5P2 UNDE                                             | RVOLTAGE PR               | ROTECTION THRESHOLDS                                                                 |      |      |      |      |

| VUC (5 V <sub>OUT</sub> ), V5C, V5P1, and V5P2                            | V <sub>V5(UV,H)</sub>     | V <sub>V5</sub> rising, VUCSEL = 1                                                   | -    | 4.68 | _    | V    |

| Undervoltage Thresholds                                                   | V <sub>V5(UV,L)</sub>     | V <sub>V5</sub> falling, VUCSEL = 1                                                  | 4.50 | 4.65 | 4.80 | V    |

| VUC (3.3 V <sub>OUT</sub> ) Undervoltage                                  | V <sub>V33(UV,H)</sub>    | V <sub>V33</sub> rising, VUCSEL = 0                                                  | _    | 3.12 | _    | V    |

| Thresholds                                                                | V <sub>V33(UV,L)</sub>    | V <sub>V33</sub> falling, VUCSEL = 0                                                 | 2.8  | 3.1  | 3.19 | V    |

| VUC (5 V <sub>OUT</sub> ), V5C, V5P1, and V5P2<br>Undervoltage Hysteresis |                           | $V_{V5(UV,H)} - V_{V5(UV,L)}$                                                        | -    | 30   | _    | mV   |

| VUC (3.3 V <sub>OUT</sub> ) Undervoltage<br>Hysteresis                    | V <sub>V33(UV,HYS)</sub>  | $V_{V33(UV,H)} - V_{V33(UV,L)}$                                                      | -    | 20   | _    | mV   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                                                           | Symbol                    | Test Conditions                                                 | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------|------|------|------|------|

| VUC, V5C, V5P1, AND V5P2 OVER                                            | OLTAGE PRO                | TECTION THRESHOLDS                                              |      |      |      |      |

| VUC (5 V <sub>OUT</sub> ), V5C, V5P1, and V5P2                           | V <sub>V5(OV,H)</sub>     | V <sub>V5</sub> rising, VUCSEL = 1                              | 5.15 | 5.33 | 5.5  | V    |

| Overvoltage Thresholds                                                   | V <sub>V5(OV,L)</sub>     | V <sub>V5</sub> falling, VUCSEL = 1                             | -    | 5.30 | -    | V    |

| VUC (3.3 V <sub>OUT</sub> ) Overvoltage                                  | V <sub>V33(OV,H)</sub>    | V <sub>V33</sub> rising, VUCSEL = 0                             | 3.41 | 3.51 | 3.62 | V    |

| Thresholds                                                               | V <sub>V33(OV,L)</sub>    | V <sub>V33</sub> falling, VUCSEL = 0                            | _    | 3.49 | -    | V    |

| VUC (5 V <sub>OUT</sub> ), V5C, V5P1, and V5P2<br>Overvoltage Hysteresis | V <sub>V5(OV,HYS)</sub>   | $V_{V5(OV,H)} - V_{V5(OV,L)}$                                   | -    | 30   | _    | mV   |

| VUC (3.3 V <sub>OUT</sub> ) Overvoltage<br>Hysteresis                    | V <sub>V33(OV,HYS)</sub>  | V <sub>V33(OV,H)</sub> – V <sub>V33(OV,L)</sub>                 | -    | 20   | -    | mV   |

| V5Px Output Disconnect Threshold                                         | V <sub>V5PX(DISC)</sub>   | V <sub>V5PX</sub> rising                                        | -    | 7.2  | -    | V    |

| VREG, VCPX, AND BG THRESHOL                                              |                           |                                                                 |      |      |      |      |

| VREG Non-Latching Overvoltage                                            | V <sub>VREG(OV,H)</sub>   | V <sub>VREG</sub> rising, LX PWM disabled                       | 5.70 | 5.95 | 6.20 | V    |

| Threshold                                                                | V <sub>VREG(OV,L)</sub>   | V <sub>VREG</sub> falling, LX PWM enabled                       | -    | 5.85 | -    | V    |

| VREG Non-Latching Overvoltage<br>Hysteresis                              | V <sub>VREG(OV,HYS)</sub> | $V_{VREG(OV,H)} - V_{VREG(OV,L)}$                               | -    | 100  | -    | mV   |

| VREG Undervoltage Thresholds                                             | V <sub>VREG(UV,H)</sub>   | V <sub>VREG</sub> rising, triggers rise of VUC linear regulator | 4.14 | 4.38 | 4.62 | V    |

| 0                                                                        | V <sub>VREG(UV,L)</sub>   | V <sub>VREG</sub> falling                                       | _    | 4.28 | -    | V    |

| VREG Undervoltage Hysteresis                                             | V <sub>VREG(UV,HYS)</sub> | $V_{VREG(UV,H)} - V_{VREG(UV,L)}$                               | -    | 100  | -    | mV   |

| VCP1 Overvoltage Thresholds <sup>[2]</sup>                               | V <sub>VCP1(OV,H)</sub>   | V <sub>VCP1</sub> rising (w.r.t. V <sub>VIN</sub> )             | 11.0 | 12.5 | 14.0 | V    |

| VCD1 Undervoltage Thresholde                                             | V <sub>VCP1(UV,H)</sub>   | $V_{\text{VCP1}}$ rising, PWM enabled (w.r.t. $V_{\text{VIN}})$ | 2.9  | 3.1  | 3.35 | V    |

| VCP1 Undervoltage Thresholds                                             | V <sub>VCP1(UV,L)</sub>   | $V_{VCP1}$ falling, PWM disabled (w.r.t. $V_{VIN}$ )            | -    | 2.8  | -    | V    |

| VCP1 Undervoltage Hysteresis                                             | V <sub>VCP1(UV,HYS)</sub> | V <sub>VCP1(UV,H)</sub> - V <sub>VCP1(UV,L)</sub>               | -    | 400  | -    | mV   |

| VCP2 Undervoltage Thresholds                                             | V <sub>VCP2(UV,H)</sub>   | $V_{VCP2}$ rising, PWM enabled (w.r.t. $V_{VIN})$               | 5.95 | 6.3  | 6.65 | V    |

| VCF2 Undervoltage Thresholds                                             | V <sub>VCP2(UV,L)</sub>   | $V_{VCP2}$ falling, PWM disabled (w.r.t. $V_{VIN})$             | -    | 5.1  | -    | V    |

| VCP2 Undervoltage Hysteresis                                             | V <sub>VCP2(UV,HYS)</sub> | V <sub>VCP2(UV,H)</sub> - V <sub>VCP2(UV,L)</sub>               | -    | 1.2  | _    | V    |

| BG1 and BG2 Undervoltage<br>Thresholds <sup>[2]</sup>                    | V <sub>BGx(UV)</sub>      | $V_{BG1}$ or $V_{BG2}$ falling                                  | 1.00 | 1.05 | 1.10 | V    |

| OVERVOLTAGE FILTERING/DEGL                                               | ТСН ТІМЕ                  |                                                                 |      |      |      |      |

| Overvoltage Detection Delay <sup>[2]</sup>                               | t <sub>d(OV)</sub>        | Overvoltage detection delay time                                | 5    | _    | 25   | μs   |

| UNDERVOLTAGE FILTERING/DEG                                               | LITCH TIME                |                                                                 |      |      |      |      |

| Undervoltage Filter/Deglitch Times [2]                                   | t <sub>d(UV)</sub>        | Undervoltage detection delay time                               | 5    | _    | 25   | μs   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

### Fully Integrated PMIC for Safety-Related Systems with Buck or Buck-Boost Pre-Regulator, 4× Linear Regulators, 4× Gate Drivers, and SPI

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> ≤ V<sub>VIN</sub> ≤ 36 V, –40°C ≤ T<sub>J</sub> ≤ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                                       | Symbol                  | Test Conditions                                                              | Min.                      | Тур. | Max. | Unit |

|------------------------------------------------------|-------------------------|------------------------------------------------------------------------------|---------------------------|------|------|------|

| NPOR TURN-ON AND TURN-OFF                            | DELAYS                  | •                                                                            | ·                         |      |      |      |

| NPOR Turn-on Delay                                   | t <sub>d(NPOR,ON)</sub> | Time from when VUC and V5C are all in regulation to NPOR being asserted high | 15                        | 20   | 25   | ms   |

| NPOR OUTPUT VOLTAGES                                 |                         | ÷                                                                            | ·                         | ·    |      |      |

| NPOR Output Low Voltage                              | V <sub>NPOR(L)</sub>    | $V_{VIN} \ge 2.5 \text{ V}, \text{ I}_{NPOR} = 2 \text{ mA}$                 | -                         | 150  | 400  | mV   |

| NPOR Leakage Current <sup>[1]</sup>                  | I <sub>NPOR(LKG)</sub>  | V <sub>NPOR</sub> = 3.3 V                                                    | -                         | -    | 2    | μA   |

| FAULT FLAG OUTPUT VOLTAGE                            | S (FFn)                 |                                                                              |                           |      |      |      |

| FFn Output Voltage                                   | V <sub>FF(L)</sub>      | FFn is tripped, V <sub>VIN</sub> ≥ 2.5 V, I <sub>FF</sub> = 2 mA             | -                         | 150  | 400  | mV   |

| FFn Leakage Current                                  | I <sub>FF(LKG)</sub>    | V <sub>FF</sub> = 3.3 V                                                      | -                         | -    | 2    | μA   |

| WD <sub>IN</sub> VOLTAGE THRESHOLDS A                | ND CURRENT              |                                                                              |                           |      |      |      |

|                                                      | V <sub>WDIN(LO)</sub>   | V <sub>WDIN</sub> falling                                                    | 0.8                       | -    | _    | V    |

| WD <sub>IN</sub> Input Voltage Thresholds            | V <sub>WDIN(HI)</sub>   | V <sub>WDIN</sub> rising                                                     | -                         | -    | 2.0  | V    |

| WD <sub>IN</sub> Pull-Down Resistance <sup>[2]</sup> | R <sub>WDIN</sub>       |                                                                              | -                         | 50   | -    | kΩ   |

| WD <sub>IN</sub> TIMING SPECIFICATIONS               |                         |                                                                              |                           |      |      |      |

| WD <sub>IN</sub> Duty Cycle [2]                      | D <sub>WDIN</sub>       |                                                                              | -                         | 50   | -    | %    |

| Watchdog Activation Delay                            | t <sub>d(WD)</sub>      |                                                                              | -                         | 30   | -    | ms   |

| GATE DRIVE ENABLE (POE)                              |                         |                                                                              |                           |      |      |      |

|                                                      | V <sub>POE(L)</sub>     | I <sub>POE</sub> = 4 mA                                                      | -                         | 150  | 400  | mV   |

| POE Output Voltage                                   | V <sub>POE(H)</sub>     | I <sub>POE</sub> = -1.5 mA                                                   | 0.8 ×<br>V <sub>VUC</sub> | _    | _    | V    |

| VUCSEL LOGIC INPUT                                   |                         | ·                                                                            |                           |      |      |      |

| VUCSEL Thresholds                                    | V <sub>VUCSEL(H)</sub>  | V <sub>VUCSEL</sub> rising                                                   | _                         | _    | 2.0  | V    |

| VUCSEL INTESTIDIUS                                   | V <sub>VUCSEL(L)</sub>  | V <sub>VUCSEL</sub> falling                                                  | 0.8                       | _    | _    | V    |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

## ELECTRICAL CHARACTERISTICS (continued) <sup>[1]</sup>: Valid at 3.8 V <sup>[4]</sup> $\leq$ V<sub>VIN</sub> $\leq$ 36 V, -40°C $\leq$ T<sub>J</sub> $\leq$ 150°C, V<sub>ENB</sub> = High or V<sub>ENBAT</sub> = High, unless otherwise specified

| Characteristic                            | Symbol            | Test Conditions                       | Min.                      | Тур. | Max. | Unit |

|-------------------------------------------|-------------------|---------------------------------------|---------------------------|------|------|------|

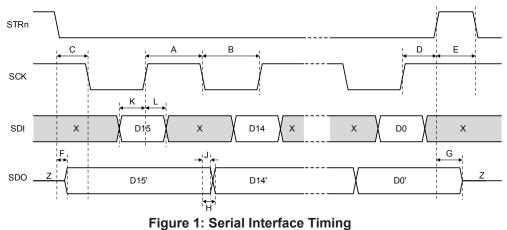

| SERIAL INTERFACE (STRn, SDI, SD           | 0, SCK)           |                                       |                           |      |      | •    |

| Input Low Voltage                         | V <sub>IL</sub>   |                                       | -                         | _    | 0.8  | V    |

| Input High Voltage                        | V <sub>IH</sub>   | All logic inputs                      | 2.0                       | -    | -    | V    |

| Input Hysteresis                          | V <sub>lhys</sub> | All logic inputs                      | 250                       | 550  | -    | mV   |

| Input Pull-Down SDI, SCK                  | R <sub>PDS</sub>  | 0 V < V <sub>VIN</sub> < 5 V          | -                         | 50   | -    | kΩ   |

| Input Pull-Up To VCC                      | I <sub>PU</sub>   | STRn                                  | -                         | 50   | -    | kΩ   |

| Output Low Voltage                        | V <sub>OL</sub>   | I <sub>OL</sub> = 1 mA <sup>[1]</sup> | -                         | _    | 0.4  | V    |

| Output High Voltage                       | V <sub>OH</sub>   | $I_{OL} = -1 \text{ mA}^{[1]}$        | 0.8 ×<br>V <sub>VUC</sub> | _    | _    | V    |

| Clock High Time                           | t <sub>SCKH</sub> | A in Figure 1                         | 50                        | -    | -    | ns   |

| Clock Low Time                            | t <sub>SCKL</sub> | B in Figure 1                         | 50                        | _    | -    | ns   |

| Strobe Lead Time                          | t <sub>STLD</sub> | C in Figure 1                         | 30                        | _    | -    | ns   |

| Strobe Lag Time                           | t <sub>STLG</sub> | D in Figure 1                         | 30                        | _    | -    | ns   |

| Strobe High Time                          | t <sub>STRH</sub> | E in Figure 1                         | 300                       | _    | -    | ns   |

| Data Out Enable Time                      | t <sub>SDOE</sub> | F in Figure 1                         | -                         | -    | 40   | ns   |

| Data Out Disable Time                     | t <sub>SDOD</sub> | G in Figure 1                         | -                         | -    | 30   | ns   |

| Data Out Valid Time From Clock<br>Falling | t <sub>SDOV</sub> | H in Figure 1                         | _                         | _    | 40   | ns   |

| Data Out Hold Time From Clock<br>Falling  | t <sub>SDOH</sub> | J in Figure 1                         | 5                         | _    | _    | ns   |

| Data In Setup Time To Clock Rising        | t <sub>SDIS</sub> | K in Figure 1                         | 15                        | _    | -    | ns   |

| Data In Hold Time From Clock Rising       | t <sub>SDIH</sub> | L in Figure 1                         | 10                        | _    | -    | ns   |

| Wake Up From Sleep                        | t <sub>EN</sub>   |                                       | -                         | _    | 2    | ms   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions V<sub>VIN</sub> > V<sub>VIN(START)</sub> and V<sub>VCP</sub> - V<sub>VIN</sub> > V<sub>VCP(UV,H)</sub> and V<sub>VREG</sub> in regulating are satisfied before V<sub>VIN</sub> is reduced.

X = do not exceed Watchdog Config timeout; Z = high-impedance (tri-state)