# CMX655D Ultra Low Power Voice Codec

Provisional

D/655/6 May 2022

#### **Features**

- Digital microphone support

- High efficiency Class-D amplifier

- Ultra Low power consumption

- 16 bit audio data

- Supports conventional telephony and HD voice (300Hz 3.4kHz and 50Hz -7kHz bandwidths)

- Supports audio bandwidths up to 21kHz

- Supports 8/16/32/48 ksps sample rates

- Flexible serial audio interface

- SPI<sup>™</sup>/TWI control interface<sup>1</sup>

- Small 24-lead VQFN Package

## **Applications**

- Security alarm panels

- Glass break detection

- Intercom and access systems

- Mobile radio and accessories

- Wired telephony

- Voice controlled equipment

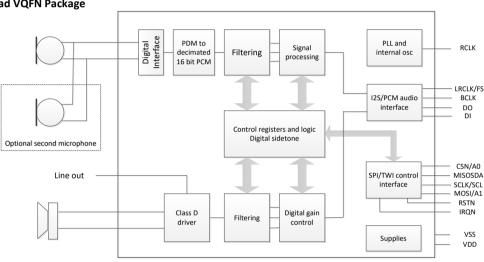

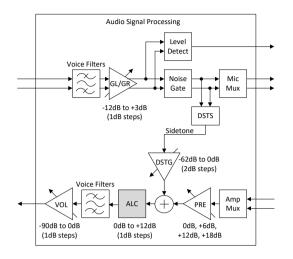

Figure 1 CMX655D Simplified Block Diagram

## 1 Brief Description

Traditionally audio codecs have interfaced to electret microphones and speakers providing A-to-D and D-to-A functions using precision oversampling data converters. Recent advances in microphone design using MEMS techniques are now changing this, along with higher efficiency speaker drivers such as Class-D topologies. Both of these advances enable significant reductions in power consumption which is needed to address new applications such as voice control, that require 'always-on' operation. Such applications are often battery powered, driving the need for minimal power consumption. The CMX655D addresses these needs providing an update to the traditional audio codec that is both very low power and small in size.

The CMX655D has a digital microphone interface that connects single or dual microphones to the device and the same parallel processing streams.

A 1-Watt mono Class-D amplifier drives differential audio outputs for a filterless speaker. A separate single-ended analogue lineout is also provided for a headphone. The Class-D amplifier features programmable filtering and digital gain control. This architecture operates with far higher efficiency than conventional speaker drivers.

The device interfaces via standard serial busses that are commonly found on many microcontrollers, DSPs and low cost radio transceivers.

<sup>&</sup>lt;sup>1</sup> SPI<sup>™</sup> is a trademark of Motorola Inc.

<sup>© 2022</sup> CML Microsystems Plc

|                 | <u>Contents</u>                              |             |

|-----------------|----------------------------------------------|-------------|

| Section         |                                              | <u>Page</u> |

| 1               | Brief Description                            |             |

| 2               | Block Diagram                                |             |

| 2.1             | CMX655D                                      |             |

| 3               | Pin List                                     |             |

| 3.1             | CMX655D                                      | -           |

| 4               | External Components                          |             |

| 4.1             | CMX655D                                      |             |

| 4.1.1<br>4.1.2  | Power Supply and Pin Decoupling<br>SPI       |             |

| 4.1.2           | SP1<br>TWI                                   |             |

| 4.1.4           | Speaker and Microphone                       |             |

| 5               | General Description                          |             |

| 5.1             | Power Management                             |             |

| 5.1.1           | External Supplies                            |             |

| 5.1.2           | Regulated Supplies                           | 13          |

| 5.2             | Device Reset                                 |             |

| 5.2.1           | Power-On-Reset                               | -           |

| 5.2.2           | Reset Pin                                    |             |

| 5.3<br>5.3.1    | Main Clock Clock Frequency                   |             |

| 5.3.2           | Clock Generation                             |             |

| 5.3.3           | PLL                                          |             |

| 5.3.4           | Low Power Oscillator                         |             |

| 5.3.5           | Clock Control Registers                      | 16          |

| 5.4             | Microphone Interface                         | 18          |

| 5.4.1           | Digital Microphone Interface                 |             |

| 5.5             | Class-D Amplifier                            |             |

| 5.5.1<br>5.5.2  | Audio Outputs<br>Overload Current Protection |             |

| 5.5.2<br>5.5.3  | Thermal Protection                           |             |

| 5.5.4           | Clipping Detection                           |             |

| 5.6             | Audio Signal Processing                      |             |

| 5.6.1           | Record Level Control                         | 19          |

| 5.6.2           | Noise Gate                                   | 19          |

| 5.6.3           | Record Level Detection                       |             |

| 5.6.4           | Playback Preamplifier Gain                   |             |

| 5.6.5           | Playback Volume Control                      |             |

| 5.6.6<br>5.6.7  | Automatic Level Control<br>Digital Sidetone  |             |

| 5.6.8           | Voice Filters                                |             |

| 5.6.9           | Channel Multiplexing                         |             |

| 5.6.10          | Click-and-Pop Reduction                      | 30          |

| 5.7             | Control Interface                            | 31          |

| 5.7.1           | SPI Slave                                    |             |

| 5.7.2           | TWI Slave                                    |             |

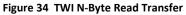

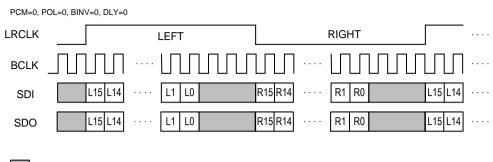

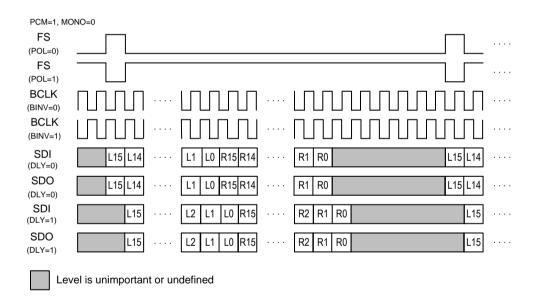

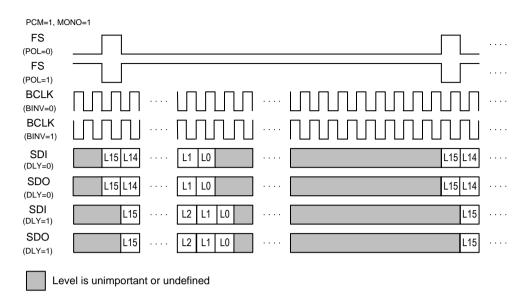

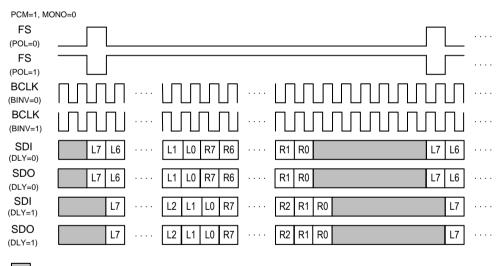

| 5.8<br>5.8.1    | Serial Audio Interface<br>I2S Mode           |             |

| 5.8.2           | Left-Justified Mode                          |             |

| 5.8.3           | PCM Mode                                     |             |

| 5.8.4           | Audio Companding                             |             |

| 5.8.5           | Serial Audio Interface Registers             |             |

| 5.9             | Interrupt Status and IRQN Pin                |             |

| 5.9.1           | Interrupt Registers                          |             |

| 5.10            | System Control                               |             |

| 5.10.1<br>E 11  | System Control Registers                     |             |

| 5.11            | Register Address Map                         |             |

| <b>6</b><br>6.1 | Application Notes                            |             |

| 6.1<br>6.1.1    | Programming Examples<br>Start-up             |             |

| 0.1.1           | Start up                                     | 43          |

$\ensuremath{\textcircled{}^{\odot}}$  2022 CML Microsystems Plc

| 6.1.2 | Configuration                         | .44  |

|-------|---------------------------------------|------|

| 6.1.3 | Enable Audio Channels                 | .45  |

| 6.1.4 | Shutdown                              | .45  |

| 7     | Performance Specification             | . 47 |

| 7.1   | Electrical Performance                | .47  |

| 7.1.1 | Absolute Maximum Ratings              | .47  |

| 7.1.2 | Operating Limits                      | .47  |

| 7.1.3 | Operating Characteristics             | .48  |

| 7.2   | Typical Performance Characteristics   | .55  |

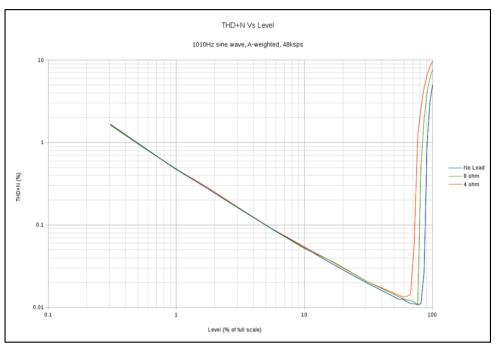

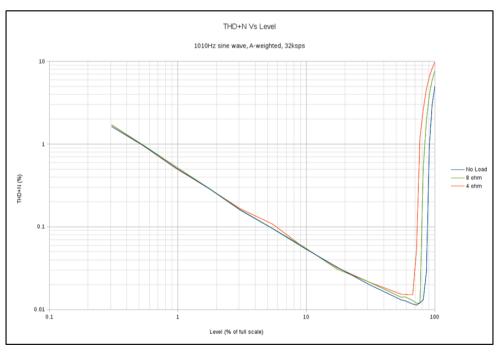

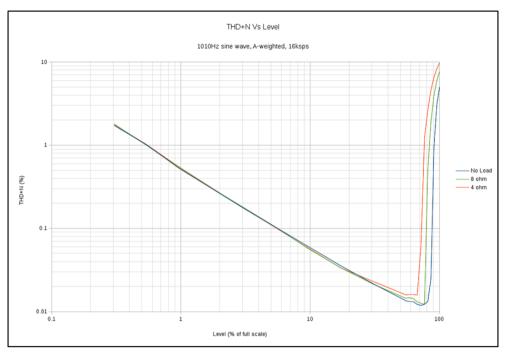

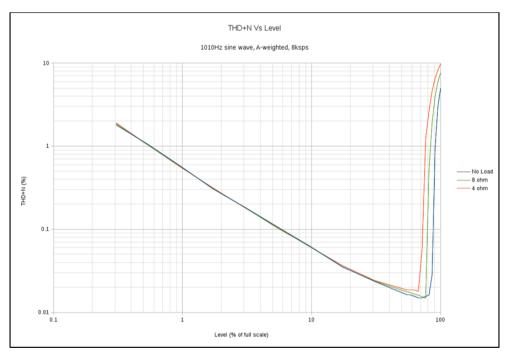

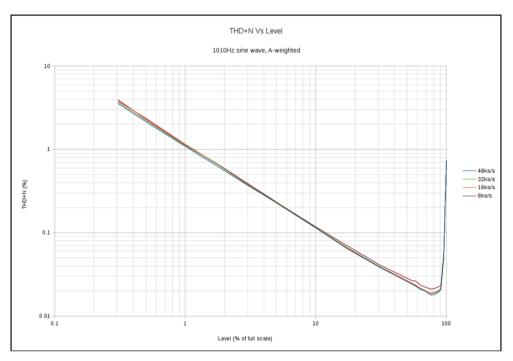

| 7.2.1 | THD+N vs. Level performance           | .55  |

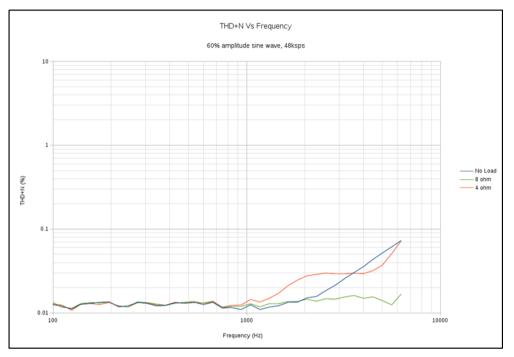

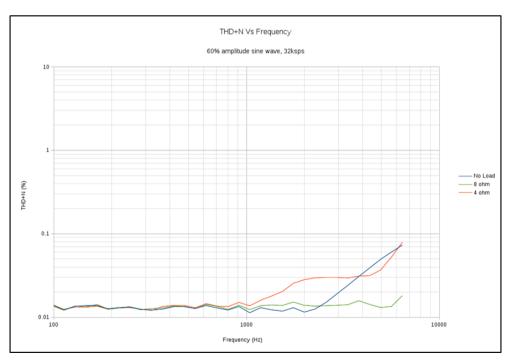

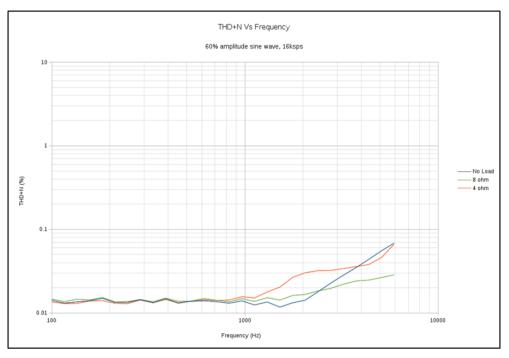

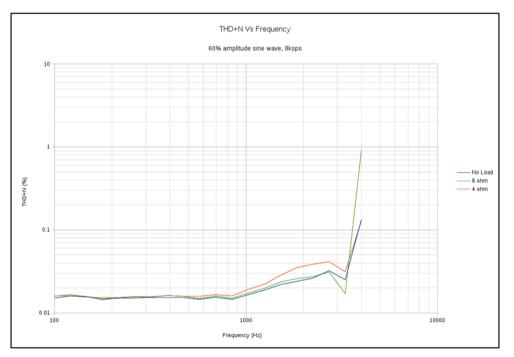

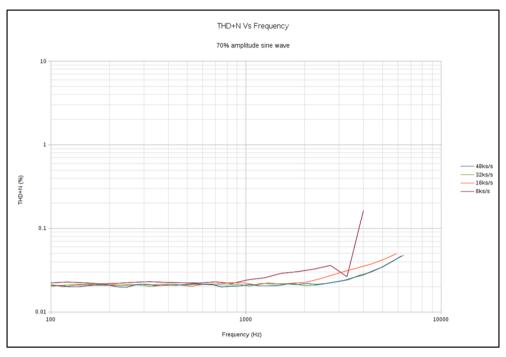

| 7.2.2 | THD+N vs. Frequency performance       | .58  |

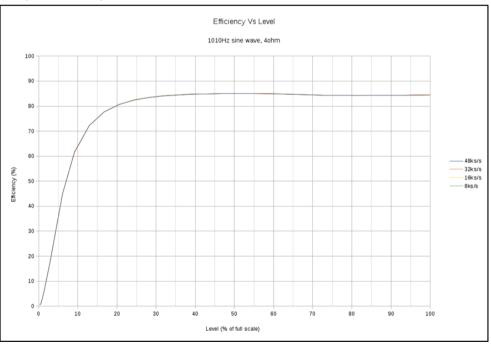

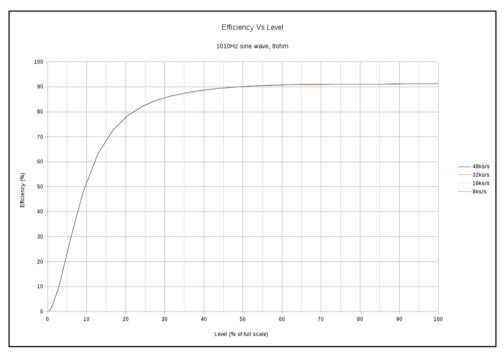

| 7.2.3 | Class D Amplifier Efficiency          | .60  |

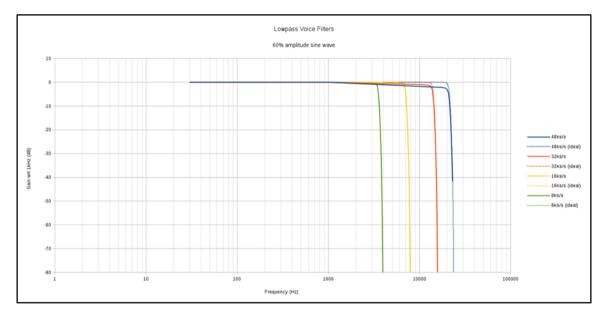

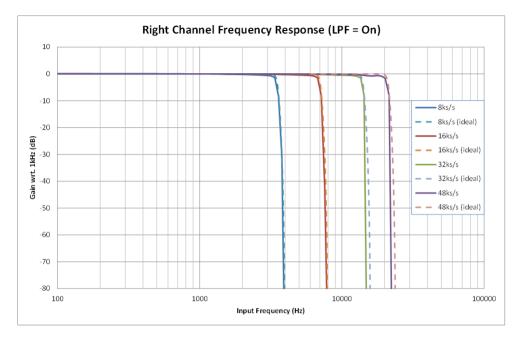

| 7.2.4 | Filter Performance Speaker Channel    | .61  |

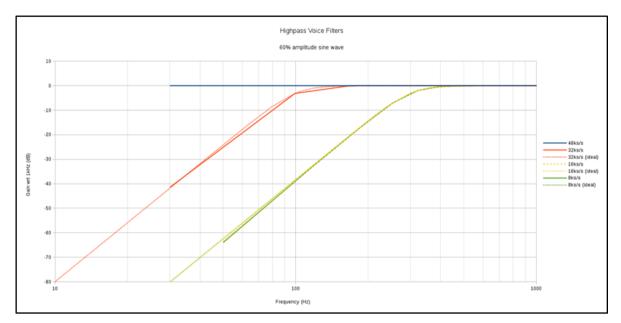

| 7.2.5 | Filter Performance Microphone Channel | .63  |

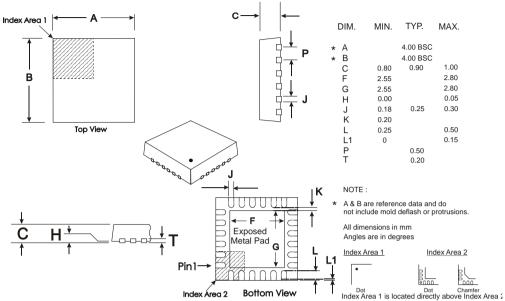

| 7.3   | Packaging                             | .65  |

| 7.3.1 | CMX655D                               |      |

#### Table

#### Page

Page

| Table 1  | CMX655D Pin List by Number                              | 6  |

|----------|---------------------------------------------------------|----|

| Table 2  | CMX655D Pin List by Number<br>CMX655D Pin List by Group | 7  |

| Table 3  | CMX655D Component Values                                | 9  |

| Table 4  | CMX655D SPI Component Value                             | 10 |

| Tabla 5  | CMX655D TW/L Component Values                           | 11 |

| Table 6  | External Supply Voltages                                | 13 |

| Table /  | Supply and POR Threshold Voltages                       | 13 |

| Table 8  | CMX655D Slave Addresses                                 | 32 |

| Table 9  | Register Address Map                                    | 41 |

| Table 10 | ) SPI Timing Parameter Values                           | 51 |

| Table 11 | . TWI Standard Mode Timing Parameters                   | 52 |

| Table 12 | 2 TWI Fast Mode Timing Parameters                       | 53 |

| Table 13 | 3 TWI Pull-up Resistors and Bus Capacitance             | 53 |

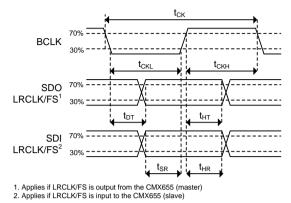

| Table 14 | SAI Timing Parameters                                   | 54 |

|          | Digital Microphone Timing Parameters                    |    |

|          |                                                         |    |

#### <u>Figure</u>

#### Figure 3 CMX655D Pin Arrangement Figure 4 CMX655D Power Supply and Pin Decoupling ......9 Figure 16 Audio signal processing block diagram with preamp block highlighted ......23 Figure 18 Audio signal processing block diagram with ALC block highlighted ......25

|           |                                                         | ~ ~ |

|-----------|---------------------------------------------------------|-----|

|           | 6 SPI Read Transfer                                     |     |

| 0         | 7 SPI N-Byte Write Transfer                             |     |

|           | 8 SPI N-Byte Read Transfer                              |     |

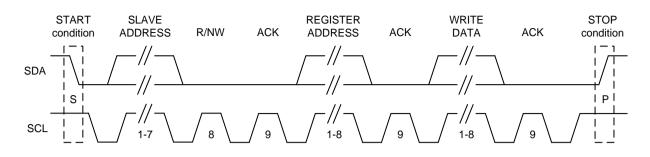

|           | 9 TWI Write Transfer                                    |     |

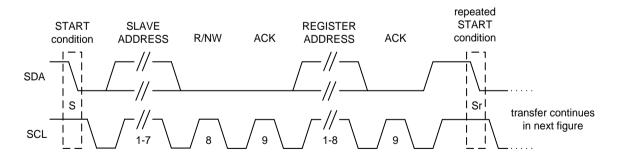

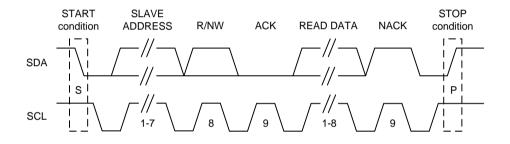

| 0         | 0 TWI Read Transfer Address Phase                       |     |

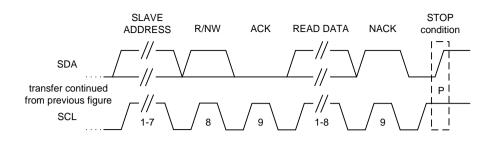

|           | 1 TWI Read Transfer Data Phase                          |     |

|           | 2 TWI Interrupt Status Register Read Transfer           |     |

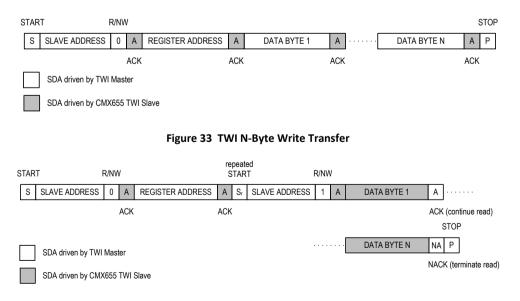

| 0         | 3 TWI N-Byte Write Transfer                             |     |

| -         | 4 TWI N-Byte Read Transfer                              |     |

|           | 5 I2S Mode Data Transfer                                |     |

|           | 6 Left-Justified Mode Data Transfer                     |     |

|           | 7 PCM Mode Dual-channel Data Transfer                   |     |

|           | 8 PCM Mode Single-channel Data Transfer                 |     |

|           | 9 PCM Slave Mode Dual-channel Companded Data Transfer   |     |

| Figure 40 | OSPI Timing Diagram                                     | 51  |

| Figure 42 | 1 TWI Timing Diagram                                    | 52  |

|           | 2 SAI Timing Diagram                                    |     |

|           | 3 Digital Microphone Timing Diagram                     |     |

| Figure 44 | 4 Class D amplifier THD+N vs. Level 48ksps              | 55  |

|           | 5 Class D amplifier THD+N vs. Level 32ksps              |     |

| Figure 46 | 6 Class D amplifier THD+N vs. Level 16ksps              | 56  |

| Figure 47 | 7 Class D amplifier THD+N vs. Level 8ksps               | 56  |

| Figure 48 | 8 Line out amplifier THD+N vs. Level 48/32/16/8ksps     | 57  |

| Figure 49 | 9 Class D amplifier THD+N vs. Frequency 48ksps          | 58  |

| Figure 50 | 0 Class D amplifier THD+N vs. Frequency 32ksps          | 58  |

|           | 1 Class D amplifier THD+N vs. Frequency 16ksps          |     |

| Figure 52 | 2 Class D amplifier THD+N vs. Frequency 8ksps           | 59  |

|           | 3 Line out amplifier THD+N vs. Frequency 48/32/16/8ksps |     |

| Figure 54 | 4 Class D amplifier efficiency 4Ω                       | 60  |

| Figure 5  | 5 Class D Amplifier Efficiency 8Ω                       | 61  |

| Figure 56 | 6 Low Pass Filter Response Speaker Channel              | 61  |

| Figure 57 | 7 High Pass Filter Response Speaker Channel             | 62  |

| Figure 58 | 8 Low Pass Filter response Microphone Channels          | 63  |

| Figure 59 | 9 High Pass Filter Response Microphone Channels         | 64  |

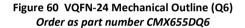

|           | 0 VQFN-24 Mechanical Outline (Q6)                       |     |

|           |                                                         |     |

### <u>History</u>

| Version | Changes                                                                                                                                                                                                                                                             | Date                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1       | Document title changed to "CMX655D/CMX655A Ultra Low-Power Codec"<br>Section 7.2 – Typical Performance Characteristics graphs added<br>Section 5.6.7 – Automatic Level Control: description and associated register tables<br>"greyed out" pending further revision | 8 <sup>th</sup> August 2018    |

| 2       | Revised performance figures                                                                                                                                                                                                                                         | 3 <sup>rd</sup> September 2018 |

| 3       | First public release                                                                                                                                                                                                                                                | 19 <sup>th</sup> October 2018  |

| 4       | All references to CMX655A removed                                                                                                                                                                                                                                   | 22 <sup>nd</sup> October 2019  |

| 5       | Section 6.1.1: App Notes – Start-up programming example revised to achieve lowest power consumption.<br>Section 7.1.3.1: Revised typical current consumption to 260µA when using RCLK mode.                                                                         | 1 <sup>st</sup> October 2020   |

| 6       | Section 4.1.1 – Power Supply and Pin Decoupling: C6 and C7 added to Figure 4 and<br>Table 3<br>Global Change of pin 4 name from VDD_A to DEC_1V2<br>Section 6 Application Notes – revised and expanded information on programming<br>examples                       | 5 <sup>th</sup> May 2022       |

This is Provisional Information; changes and additions may be made to this specification. Parameters marked TBD or left blank will be included in later issues. Items that are highlighted or greyed out should be ignored. These will be clarified in later issues of this document.

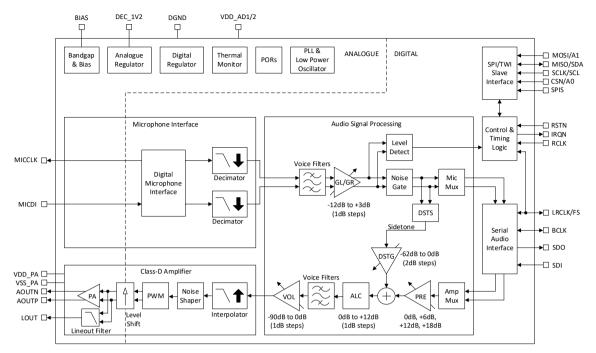

# 2 Block Diagram

# 2.1 CMX655D

Figure 2 CMX655D Block Diagram

© 2022 CML Microsystems Plc

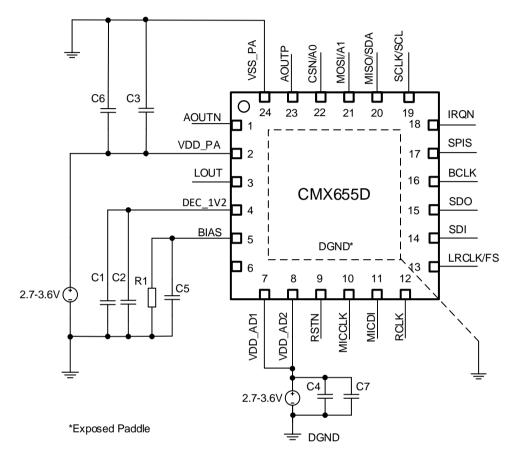

# 3 Pin List

# 3.1 CMX655D

# Table 1 CMX655D Pin List by Number

| Number | Name               | Туре  | Function                                                         |  |  |

|--------|--------------------|-------|------------------------------------------------------------------|--|--|

| 1      | AOUTN              | AO    | Class-D Amplifier Output Negative                                |  |  |

| 2      | VDD_PA             | VDD   | Class-D Supply: 2.7-3.6V (high current)                          |  |  |

| 3      | LOUT               | AO    | Lineout                                                          |  |  |

| 4      | DEC_1V2            | VDD   | 1.2V Regulator Decouple                                          |  |  |

| 5      | BIAS               | AO    | Bias Current Resistor                                            |  |  |

| 6      | NC1                | NC    | No Connection                                                    |  |  |

| 7      | VDD_AD1            | VDD   | Analogue/Digital Supply 2.7-3.6V (1.75-3.6V if VDD_PA unused)    |  |  |

| 8      | VDD_AD2            | VDD   | Analogue/Digital Supply 2.7-3.6V (1.75-3.6V if VDD_PA unused)    |  |  |

| 9      | RSTN               | DI    | Active Low Reset                                                 |  |  |

| 10     | MICCLK             | DO    | Digital Microphone Clock Output                                  |  |  |

| 11     | MICDI              | DI    | Digital Microphone Data Input                                    |  |  |

| 12     | RCLK               | DI    | PLL Reference/Main clock                                         |  |  |

| 13     | LRCLK/FS           | DIO   | Left-Right Clock/PCM Frame Sync/PLL Reference                    |  |  |

| 14     | SDI                | DI    | Serial Audio Data Input                                          |  |  |

| 15     | SDO                | DO    | Serial Audio Data Output                                         |  |  |

| 16     | BCLK               | DIO   | Serial Audio Data Clock                                          |  |  |

| 17     | SPIS               | DI    | SPI Select: 0=TWI, 1=SPI                                         |  |  |

| 18     | IRQN               | DO    | Active Low Interrupt. Open-drain – connect to VDD_AD via pull up |  |  |

| 19     | SCLK/SCL           | DI    | SPI SCLK/TWI SCL                                                 |  |  |

| 20     | MISO/SDA           | DIO   | SPI MISO/TWI SDA                                                 |  |  |

| 21     | MOSI/A1            | DI    | SPI MOSI/TWI A1                                                  |  |  |

| 22     | CSN/A0             | DI    | SPI CSN/TWI AO                                                   |  |  |

| 23     | AOUTP              | AO    | Class-D Amplifier Output Positive                                |  |  |

| 24     | VSS_PA             | GND   | Class-D Ground                                                   |  |  |

| PADDLE | DGND               | GND   | Digital and Analogue Ground                                      |  |  |

| AIO    | Analogue Input / C | utput | DIO Digital Input / Output                                       |  |  |

| AI     | Analogue Input     |       | DI Digital Input                                                 |  |  |

| AO     | Analogue Output    |       | DO Digital Output                                                |  |  |

| NC     | Not Connected      |       | VDD Supply                                                       |  |  |

| GND    | Ground             |       |                                                                  |  |  |

$\ensuremath{\textcircled{}^{\circ}}$  2022 CML Microsystems Plc

#### Table 2 CMX655D Pin List by Group

| Number    | Name                                  | Туре  | Function                                                         |  |  |

|-----------|---------------------------------------|-------|------------------------------------------------------------------|--|--|

| Power     |                                       |       |                                                                  |  |  |

| 2         | VDD_PA                                | VDD   | Class-D Supply: 2.7-3.6V (high current)                          |  |  |

| 4         | DEC_1V2                               | VDD   | 1.2V Analogue Regulator Decouple                                 |  |  |

| 7         | VDD_AD1                               | VDD   | Analogue/Digital Supply 2.7-3.6V (1.75-3.6V if VDD_PA unused)    |  |  |

| 8         | VDD_AD2                               | VDD   | Analogue/Digital Supply 2.7-3.6V (1.75-3.6V if VDD_PA unused)    |  |  |

| 24        | VSS_PA                                | GND   | Class-D Ground                                                   |  |  |

| PADDLE    | DGND                                  | GND   | Digital and Analogue Ground                                      |  |  |

| Referen   | ce and Bias                           |       |                                                                  |  |  |

| 5         | BIAS                                  | AI    | Bias Current Resistor                                            |  |  |

| Class-D   | Amplifier Outputs                     |       |                                                                  |  |  |

| 1         | AOUTN                                 | AO    | Class-D Amplifier Output Negative                                |  |  |

| 3         | LOUT                                  | AO    | Lineout                                                          |  |  |

| 23        | AOUTP                                 | AO    | Class-D Amplifier Output Positive                                |  |  |

| Microph   | one Interface                         |       |                                                                  |  |  |

| 10        | MICCLK                                | DO    | Digital Microphone Clock Output                                  |  |  |

| 11        | MICDI                                 | DI    | Digital Microphone Data Input                                    |  |  |

| General   | System & Control                      |       |                                                                  |  |  |

| 9         | RSTN                                  | DI    | Active Low Reset                                                 |  |  |

| 12        | RCLK                                  | DI    | PLL Reference/Main clock                                         |  |  |

| 18        | IRQN                                  | DO    | Active Low Interrupt. Open-drain - connect to VDD_AD via pull-up |  |  |

| Control   | nterface                              |       |                                                                  |  |  |

| 17        | SPIS                                  | DI    | SPI Select: 0=TWI, 1=SPI                                         |  |  |

| 19        | SCLK/SCL                              | DI    | SPI SCLK/TWI SCL                                                 |  |  |

| 20        | MISO/SDA                              | DIO   | SPI MISO/TWI SDA                                                 |  |  |

| 21        | MOSI/A1                               | DI    | SPI MOSI/TWI A1                                                  |  |  |

| 22        | CSN/A0                                | DI    | SPI CSN/TWI A0                                                   |  |  |

| Serial Au | idio Interface                        |       |                                                                  |  |  |

| 13        | LRCLK/FS                              | DIO   | Left-Right Clock/PCM Frame Sync/PLL Reference                    |  |  |

| 14        | SDI                                   | DI    | Serial Audio Data Input                                          |  |  |

| 15        | SDO                                   | DO    | Serial Audio Data Output                                         |  |  |

| 16        | BCLK                                  | DIO   | Serial Audio Data Clock                                          |  |  |

| 0         | Analogue Input / Ou                   | itout | DIO Digital Input / Output                                       |  |  |

| 0         | Analogue Input / Ot<br>Analogue Input | ilput | DI Digital Input                                                 |  |  |

| )         | Analogue Output                       |       | DO Digital Output                                                |  |  |

|           | Not Connected                         |       | VDD Supply                                                       |  |  |

| ND        | Ground                                |       |                                                                  |  |  |

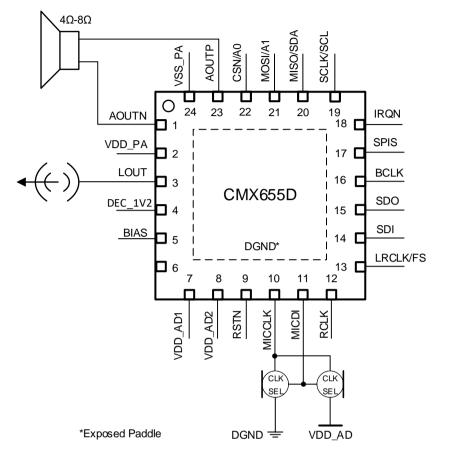

Figure 3 CMX655D Pin Arrangement

© 2022 CML Microsystems Plc

# 4 External Components

## 4.1 CMX655D

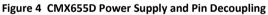

## 4.1.1 Power Supply and Pin Decoupling

The CMX655D has two supply pins, VDD\_AD and VDD\_PA, which should be connected to the same nominal supply voltage of 3V. If the Class-D amplifier is not required, VDD\_PA may be disconnected from the supply and connected to ground allowing VDD\_AD to operate from a minimum supply voltage of 1.75V.

#### Table 3 CMX655D Component Values

| C1 | 100nF |

|----|-------|

| C2 | 100pF |

| C3 | 10nF  |

| C4 | 10nF  |

| C5 | 10pF  |

| C6 | 10µF  |

| C7 | 10µF  |

| R1 | 60kΩ  |

|    |       |

Capacitors  $\pm$ 5%, Resistors  $\pm$ 1%

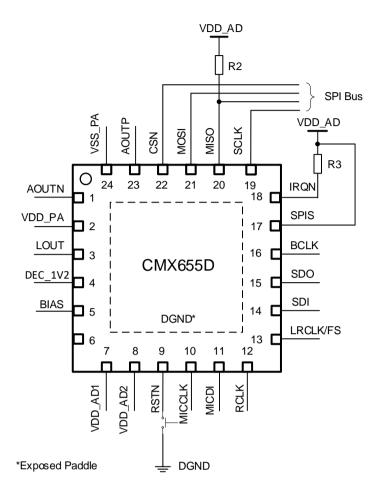

## 4.1.2 SPI

| Table 4 | CMX655D | SPI | Component Value |

|---------|---------|-----|-----------------|

|---------|---------|-----|-----------------|

| R2 | 10kΩ |

|----|------|

| R3 | 47kΩ |

Resistors  $\pm 1\%$

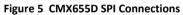

## 4.1.3 TWI

## Table 5 CMX655D TWI Component Values

| R3 | 47kΩ |

|----|------|

| R4 | Rp   |

| R5 | Rp   |

|    |      |

Resistors ±1%

The value of  $R_p$  is given in Table 13.

#### 4.1.4 Speaker and Microphone

Figure 7 CMX655D Speaker and Microphone Connections

© 2022 CML Microsystems Plc

#### 5 General Description

## 5.1 Power Management

#### 5.1.1 External Supplies

The external unregulated supplies required by the CMX655D are VDD\_AD connected to the VDD\_AD pin and VDD\_PA connected to the VDD PA1 pin. The exposed paddle on the underside of the package is the digital and analogue ground.

VDD\_PA solely powers the Class-D power-amplifier output stage that drives the AOUTN and AOUTP pins. VDD\_AD powers the Class-D lineout output stage and the remaining analogue and digital circuits.

When the CMX655D Class-D power-amplifier is in use, the VDD\_PA and VDD\_AD supplies must operate at the same voltage between 2.7-3.6V. If the CMX655D Class-D power-amplifier is not required, the VDD\_PA supply may be connected to analogue ground and the VDD\_AD supply may operate between 2.7V-3.6V. If both the Class-D power-amplifier and lineout are not required, the VDD\_AD supply may operate between 1.75-3.6V, see Table 10 below.

#### **Table 6 External Supply Voltages**

| Class-D PA In Use | Class-D Lineout<br>In Use | VDD_AD       | VDD_PA         |

|-------------------|---------------------------|--------------|----------------|

| Yes               | Yes                       | 2.7 to 3.6V  | Same as VDD_AD |

| Yes               | No                        | 2.7 to 3.6V  | Same as VDD_AD |

| No                | Yes                       | 2.7 to 3.6V  | Not Required   |

| No                | No                        | 1.75 to 3.6V | Not Required   |

#### 5.1.2 Regulated Supplies

The CMX655D contains integrated voltage regulators powered from VDD\_AD that generate 1.2V regulated supply rails for the digital (VDD\_D) and analogue (VDD\_A) circuits in the device. The regulated analogue supply rail is externally decoupled via the DEC\_1V2 pin.

#### 5.2 Device Reset

The CMX655D device reset is activated by the integrated power-on-reset (POR) generator on the VDD\_D voltage domain and the active low reset pin RSTN. While reset is in progress, the CMX655D SPI/TWI interface must remain in its idle state, without being accessed.

#### 5.2.1 Power-On-Reset

The CMX655D POR voltage thresholds are listed in Table 7.

| Table 7 | Supply | and POR | Threshold | Voltages |

|---------|--------|---------|-----------|----------|

|         |        |         |           |          |

| Supply | Nominal Voltage (V) | POR Voltage (V) |

|--------|---------------------|-----------------|

| VDD_A  | 1.2                 | 0.93            |

| VDD_D  | 1.2                 | 0.93            |

The reset signal produced by each POR generator is asserted within  $1\mu$ s of the power-on-reset threshold voltage being exceeded.

Once the VDD\_D power-on-reset threshold voltage has been exceeded the device will be released from reset and this will occur within  $10\mu$ s of the VDD\_AD supply reaching 1.75V.

#### 5.2.2 Reset Pin

The CMX655D may be reset while the device remains powered-up by externally driving the RSTN pin low to DGND. A reset duration of 1µs minimum is recommended.

<sup>© 2022</sup> CML Microsystems Plc

#### 5.3 Main Clock

The control registers and functions associated with the audio signal processing, the Class-D amplifier, the microphone channels and the Serial Audio Interface require the main clock to be active before they may be modified.

Note: After device reset, the first main clock source selected must always be the low power oscillator (LPOSC), and the main clock must then be started. The main clock source configuration may be subsequently changed.

#### 5.3.1 Clock Frequency

The CMX655D is designed to operate with a main internal clock frequency of 24.576MHz.

#### 5.3.2 Clock Generation

From reset, the device is in its lowest power state with the main clock (CLK) internally deactivated. The main clock must first be configured and activated before attempting to access and control other device functions however, device registers can be accessed via the SPI/TWI Control Interface while the main clock is not active.

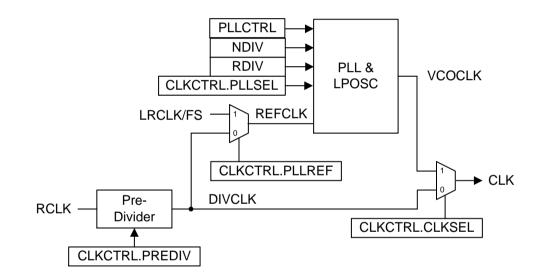

The required main clock frequency of 24.576MHz may be directly applied to the CMX655D via the RCLK pin. If the exact main clock frequency cannot be supplied by the external system, the CMX655D integer-N PLL may be configured and enabled to generate the required main clock from either RCLK or the serial audio interface sample rate clock LRCLK/FS external signals, as shown in Figure 8.

#### Figure 8 Main Clock Generation

The LRCLK/FS signal may only be selected as the PLL reference clock if the CMX655D Serial Audio Interface operates as a slave. In this operating mode, LRCLK/FS is generated by the external master and is an input to the CMX655D and the RCLK input is unused and may be tied low or high as appropriate.

If the CMX655D Serial Audio Interface (SAI) operates as the slave, the CMX655D main clock must be synchronous to LRCLK/FS to avoid audio sample slippage due to clock drift between the CMX655D internal sample rate (derived from the main clock) and the external sample rate indicated on LRCLK/FS and generated by the SAI master. If LRCLK/FS is not used as the PLL reference clock to derive the main clock when the CMX655D SAI operates as the slave, then the external system should ensure that LRCLK/FS is synchronous with respect to RCLK.

The CLKCTRL, RDIVHI, RDIVLO, NDIVHI, NDIVLO and PLLCTRL register settings should first be configured prior to activating the main clock.

Prior to activating the main clock, the IRQN pin may be configured to indicate when the main clock has successfully started by setting the CLKRDY bit in the **ISM** register. The main clock is activated by writing \$01 (Clock Start command) to the **COMMAND** register. The CLKRDY bit in the **ISR** register is set when the clock goes ready. This bit is cleared on reading the **ISR** register. It is not possible to modify the **CLKCTRL** register after the main clock is activated. The **RDIVHI**, **RDIVLO**, **NDIVHI**, **NDIVLO** and **PLLCTRL** registers should not be modified if the main clock is active and generated by the PLL.

To return the device to its lowest power state, the **SYSCTRL** register should first be cleared after which the main clock may be deactivated by writing \$00 (Clock Stop command) to the **COMMAND** register. The main clock will stop within four main clock cycles after the Clock Stop command has been transferred. If the main clock is derived from the PLL clock at the time the main clock is deactivated, the external clock source used for the PLL reference (i.e. RCLK or LRCLK/FS) must only be disabled at least four REFCLK cycles after the Clock Stop command has been transferred.

After the main clock has stopped, the Microphone Interface, Class-D Amplifier, Audio Signal Processing and Serial Audio Interface are held in reset until the main clock is next restarted.

The CMX655D low-power oscillator, LPOSC, generates a nominal 24.576MHz clock. The LPOSC allows the CMX655D to perform record level detection without an external clock supplied to the device. When the LPOSC is used as the main clock source, the SAI and Class-D amplifier must be disabled because the LPOSC frequency is too low and not sufficiently accurate to support these functions. If the detected microphone audio level exceeds a programmable threshold an associated interrupt may be indicated on the IRQN pin. The interrupt may be used to wake-up a sleeping external controller that subsequently re-enables the external clock source (i.e. RCLK or LRCLK/FS) and places the CMX655D back into a fully featured operating mode that makes use of the active external clock to derive the main clock.

#### 5.3.3 PLL

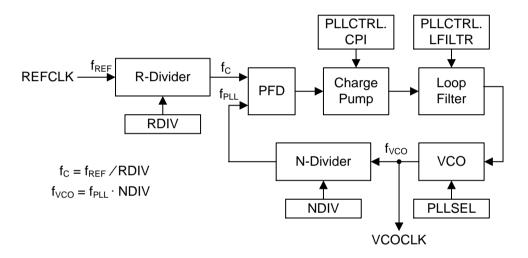

The basic integer-N PLL block diagram is shown in Figure 9.

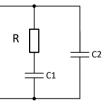

The REFCLK is taken from RCLK (i.e. a common crystal oscillator frequency) or the sample rate clock input on LRCLK/FS (i.e. 8/16/32/48kHz). The frequency range of REFCLK is 8kHz–20MHz. The PLL is fully integrated within the CMX655D so there is no requirement for any external loop filter components. The PLL loop filter is shown in Figure 10.

Figure 10 PLL Loop Filter

C1 is 54pF, C2 is 5.4pF and R is adjustable via bits 7-4 of the register PLLCTRL.

<sup>© 2022</sup> CML Microsystems Plc

## 5.3.4 Low Power Oscillator

The LPOSC generates a nominal 24.576MHz clock. When the LPOSC is selected as the main clock source, the VCO operates as an open-loop ring oscillator and the remaining PLL components are disabled. The LPOSC supports record level detection without the requirement of an external clock source to be applied to the CMX655D.

## 5.3.5 Clock Control Registers

#### 5.3.5.1 CLKCTRL (\$03)

Clock Control (R/W) Reset Value: \$00

| 7                                                      | 6                            | 5               | 4                | 3             | 2              | 1          | 0      |  |  |

|--------------------------------------------------------|------------------------------|-----------------|------------------|---------------|----------------|------------|--------|--|--|

| 0                                                      | S                            | R               | PLLREF           | PLLSEL        | CLKSE          | EL .       | PREDIV |  |  |

|                                                        |                              |                 |                  |               |                |            |        |  |  |

| SR                                                     | Sample                       | Rate (f₅)       |                  |               |                |            |        |  |  |

| 0                                                      | 8ksps                        | 8ksps           |                  |               |                |            |        |  |  |

| 1                                                      | 16ksps                       |                 |                  |               |                |            |        |  |  |

| 2                                                      | 32ksps                       | 32ksps          |                  |               |                |            |        |  |  |

| 3                                                      | 48ksps                       | 48ksps          |                  |               |                |            |        |  |  |

| PLLREF                                                 | PLL Refe                     | erence Clock    | Source           |               |                |            |        |  |  |

| 0                                                      | DIVCLK                       |                 |                  |               |                |            |        |  |  |

| 1                                                      | LRCLK/F                      | S - requires C  | CMX655D Serial A | Audio Interfa | ice to operate | as a slave |        |  |  |

| PLLSEL                                                 | PLL Sele                     | ct              |                  |               |                |            |        |  |  |

| 0                                                      |                              | op VCO (LPO     | SC)              |               |                |            |        |  |  |

| 1                                                      | Closed-l                     |                 | /                |               |                |            |        |  |  |

|                                                        |                              |                 |                  |               |                |            |        |  |  |

| CLKSEL                                                 |                              | Clock Selection |                  |               |                |            |        |  |  |

| 0                                                      | Select D                     |                 |                  |               |                |            |        |  |  |

| 1                                                      | Select V                     | Select VCOCLK   |                  |               |                |            |        |  |  |

| PREDIV                                                 | Pre-divi                     | der             |                  |               |                |            |        |  |  |

| 0                                                      | Divide b                     |                 |                  |               |                |            |        |  |  |

| 1                                                      | Divide b                     |                 |                  |               |                |            |        |  |  |

| 2-3                                                    | Divide b                     | y 4             |                  |               |                |            |        |  |  |

| RDIVHI (\$04)                                          |                              |                 |                  |               |                |            |        |  |  |

| <b>R-Divider Hig</b>                                   | h Byte (R/W)                 |                 |                  |               |                |            |        |  |  |

| Reset Value:                                           | \$00                         |                 |                  |               |                |            |        |  |  |

| 7                                                      | 6                            | 5               | 4                | 3             | 2              | 1          | 0      |  |  |

|                                                        | 0                            |                 | -                |               | <br>RDIV[12:8] | _          | -      |  |  |

| <b>RDIVLO (\$05</b> )<br>R-Divider Low<br>Reset Value: | v Byte (R/W)                 |                 |                  |               |                |            |        |  |  |

| 7                                                      | 6                            | 5               | 4                | 3             | 2              | 1          | 0      |  |  |

|                                                        |                              |                 | RDIV             | [7:0]         |                |            |        |  |  |

| 000//40.01                                             | Divide V 1                   | _               |                  |               |                |            |        |  |  |

| RDIV[12:0]                                             | Divide Valu                  |                 |                  |               |                |            |        |  |  |

| 0<br>1-8191                                            | Divide by 82<br>Divide by 1- |                 |                  |               |                |            |        |  |  |

| 1-0131                                                 | Divide by 1-                 | 0131            |                  |               |                |            |        |  |  |

5.3.5.2

5.3.5.3

# 5.3.5.4 NDIVHI (\$06)

N-Divider High Byte (R/W) Reset Value: \$00

| 7                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                       |

| <b>NDIVLO (\$0</b><br>N-Divider Lo<br>Reset Value                                                                                                                                                                                     |

| 7                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                       |

| NDIV[12:0<br>0<br>1-8191                                                                                                                                                                                                              |

| <b>PLLCTRL (\$0</b><br>PLL Control<br>Reset Value                                                                                                                                                                                     |

| 7                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                       |

| R     I       0     2       1     2       3     2       4     2       5     2       6     2       7     2       8     2       9     2       10     2       11     8       12     2       13     2       14     2       15     3       |

| CPI       0         0       0         1       0         2       0         3       0         4       0         5       0         6       0         7       0         8       0         9       0         10       1         12       2 |

#### 5.4 Microphone Interface

#### 5.4.1 Digital Microphone Interface

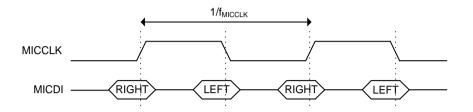

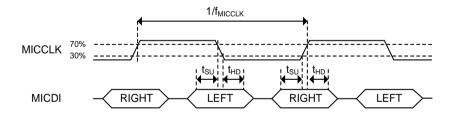

The CMX655D drives the MICCLK pin which connects to the external microphone(s) clock input and receives a PDM bitstream on MICDI from the microphone(s) data output. Digital MEMS microphones are configured to output the PDM bitstream for either positive or negative clock edge operation, with the data-line going high-impedance for the inactive clock edge. This allows two microphones to share a common clock and data line when configured to operate on opposite clock edges to support 2-channel audio. The CMX655D samples left channel data on the falling edge of MICCLK and right channel data on the rising edge of MICCLK as shown in Figure 11.

Figure 11 CMX655D Digital Microphone Interface

The CMX655D drives MICCLK with a 50% duty cycle at a frequency of  $f_{MICCLK}$ . If the sample rate is 48ksps, then  $f_{MICCLK}$  = 3.072MHz. For the remaining sample rates of 8/16/32ksps,  $f_{MICCLK}$  = 2.048MHz.

## 5.5 Class-D Amplifier

#### 5.5.1 Audio Outputs

The CMX655D Class-D amplifier provides differential power outputs (AOUTP, AOUTN) for driving a speaker with  $4\Omega$ - $8\Omega$  impedance and a single-ended lineout (LOUT) for driving a minimum load impedance of  $18k\Omega$  in parallel with 120 pF.

Class-D Power Amplifier specifications are provided for 4 ohm and 8 ohm loads. The amplifier also operates with other load impedances ranging from below 4 ohms to infinite ohms (open circuit). Performance with load impedance other than 4 ohms and 8 ohms may be different than is specified for 4 ohm and 8 ohm loads. Generally, as load impedance decreases, amplifier output power increases and power efficiency decreases. Maximum speaker driver current limiting and optionally enabled thermal protection can limit the minimum load impedance and output level for load impedance less than 4 ohms.

#### 5.5.2 Overload Current Protection

The CMX655D differential power outputs of the Class-D amplifier are protected against overload current conditions with an automatic shut-off protection circuit. Overload current protection is enabled when the **SYSCTRL** register PAMP bit is set to 1. The overload current condition may be configured to signal an interrupt via the IRQN pin as described in section 5.9.

#### 5.5.3 Thermal Protection

The CMX655D includes an integrated thermal detection circuit which automatically powers-down the Class-D amplifier differential power outputs when the device temperature reaches a critical level. Thermal protection is enabled when the **SYSCTRL** register PAMP bit is set to 1. The thermal protection event may be configured to signal an interrupt via the IRQN pin as described in section 5.9.

#### 5.5.4 Clipping Detection

A clipping detection circuit within the CMX655D Class-D amplifier monitors if the differential power output stage is in saturation and distorting the playback signal. The clipping detection circuit is enabled when the **SYSCTRL** register PAMP bit is set to 1. The clipping detection interrupt generation is enabled using the **ISE** register. The clipping detection circuit may be configured to signal an interrupt via the IRQN pin as described in section 5.9.

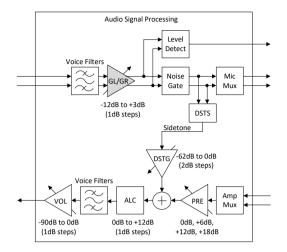

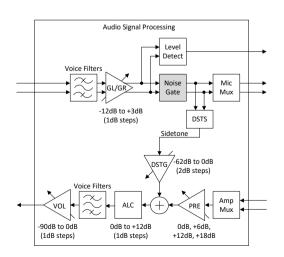

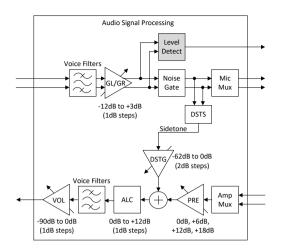

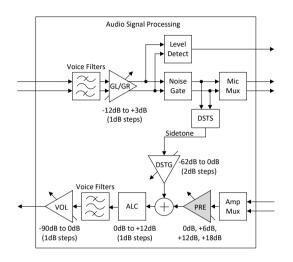

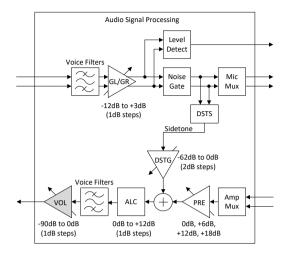

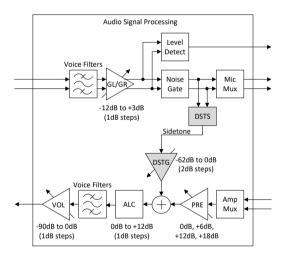

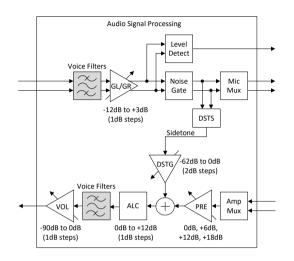

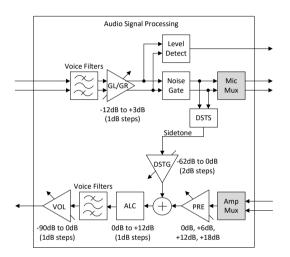

#### 5.6 Audio Signal Processing

#### 5.6.1 Record Level Control

#### Figure 12 Audio signal processing block diagram with gain level block highlighted

The record levels of the left and right channels are controlled by the gain settings in the **LEVEL** register. The gain applied to each channel may be independently set from -12dB to +3dB in 1dB steps.

#### 5.6.1.1 Record Level Control Register

#### LEVEL (\$0F)

Record Level (R/W) Reset Value: \$00

| 7  | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|----|---|---|---|---|---|----|---|

| GL |   |   |   |   | G | iR |   |

#### GL Gain Left channel

0-15 -12dB to +3dB (+1dB steps)

## GR Gain Right channel

0-15 -12dB to +3dB (+1dB steps)

#### 5.6.2 Noise Gate

#### Figure 13 Audio signal processing block diagram with Noise Gate block highlighted

© 2022 CML Microsystems Plc

The noise gate function is designed to attenuate low-level record signals that fall below a pre-programmed noise threshold. Noise gating is implemented using downward expansion such that the output signal level is attenuated in proportion to the degree in which the peak input signal level is below the expansion threshold. Downward expansion results in a soft noise gating response due to the gradual attenuation applied to the input signal. The input-to-output signal level ratio below the threshold may be programmed as 1:2, 1:3 or 1:4. The noise gate is controlled by the **NGCTRL** register. The ideal expansion attenuation  $A_{EXP}$  (dB) when the input signal (dBFS) is below the expansion threshold (dBFS) for a given an expansion ratio of 1:E is:

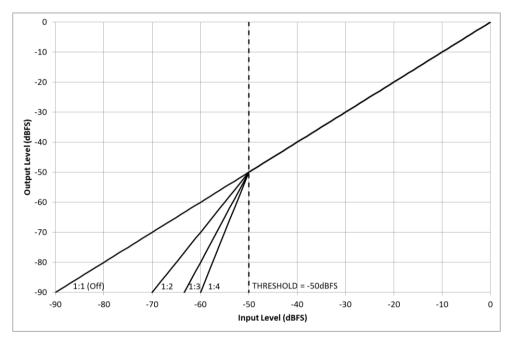

However, it should be noted that  $A_{EXP}$  is only controlled using 1dB of resolution and that the maximum attenuation applied by the noise gate is limited to 31dB. Figure 14 shows the ideal noise gate response for these ratios with the threshold set to -50dBFS. The 1:1 ratio is effective when the noise gate is disabled.

Figure 14 Noise Gate Response

When enabled, the noise gate function operates independently on the left and right record channel. The noise gate response time is programmed using the **NGTIME** register. The release time determines how long it would take for the noise gate to apply 12dB of downwards expansion when the input signal falls below the threshold. The attack time determines how long it would take the noise gate to remove 12dB of downwards expansion once the signal rises back above the threshold. The release and attack times therefore determine the rate at which expansion is applied and removed. The attenuation applied to the left and right record channel may be read from **NGLSTAT** and **NGRSTAT** registers respectively.

#### 5.6.2.1 Noise Gate Registers

#### NGCTRL (\$1C)

Noise Gate Control (R/W) Reset Value: \$00

| 7                   | 6                                             | 5                          | 4      | 3 | 2      | 1 | 0 |

|---------------------|-----------------------------------------------|----------------------------|--------|---|--------|---|---|

| EN                  | RA                                            | TIO                        |        |   | THRESH |   |   |

| <b>EN</b><br>0<br>1 | <b>Enable</b><br>Noise Gate o<br>Noise Gate e | disabled (1:1 r<br>enabled | ratio) |   |        |   |   |

| RATIO | Input-to-output signal level ratio below Threshold when Noise Gate enabled |

|-------|----------------------------------------------------------------------------|

| 0     | 1:2                                                                        |

| 1     | 1:3                                                                        |

| 2-3   | 1:4                                                                        |

| 2-3 | 1.4 |

|-----|-----|

|     |     |

|     |     |

|     |     |

THRESH 0-31

Threshold -63dBFS to -32dBFS (+1dB steps)

# NGTIME (\$1D)

Noise Gate Time (R/W) Reset Value: \$00

| 7       | 6        | 5        | 4 | 3 | 2 | 1       | 0 |

|---------|----------|----------|---|---|---|---------|---|

| 0       |          | ATTACK   |   |   |   | RELEASE |   |

| АТТАСК  | Attack T | īme (ms) |   |   |   |         |   |

| )       | 1.5      |          |   |   |   |         |   |

| L       | 3        |          |   |   |   |         |   |

| 2       | 4.5      |          |   |   |   |         |   |

| 3       | 6        |          |   |   |   |         |   |

| 1       | 12       |          |   |   |   |         |   |

| 5       | 24       |          |   |   |   |         |   |

| 5       | 48       |          |   |   |   |         |   |

| 7       | 96       |          |   |   |   |         |   |

| RELEASE | Release  | Time (s) |   |   |   |         |   |

| )       | 0.06     |          |   |   |   |         |   |

| L       | 0.12     |          |   |   |   |         |   |

| 2       | 0.24     |          |   |   |   |         |   |

| 3       | 0.48     |          |   |   |   |         |   |

| Ļ       | 0.96     |          |   |   |   |         |   |

| 5       | 1.92     |          |   |   |   |         |   |

#### NGLSTAT (\$1E)

6

7

Noise Gate Left Channel Status (R) Reset Value: \$00

3.84

7.68

| 7 | 6 | 5 | 4     | 3 | 2 | 1 | 0 |

|---|---|---|-------|---|---|---|---|

|   | 0 |   | ATTEN |   |   |   |   |

|   |   |   |       |   |   |   |   |

| ATTEN | Attenuation |  |  |  |

|-------|-------------|--|--|--|

| 0-31  | 0dB to +31d |  |  |  |

OdB to +31dB (+1dB steps)

# NGRSTAT (\$1F)

Noise Gate Right Channel Status (R) Reset Value: \$00

| 7 | 6 | 5 | 4     | 3 | 2 | 1 | 0 |

|---|---|---|-------|---|---|---|---|

| 0 |   |   | ATTEN |   |   |   |   |

| ATTEN | Attenuation               |

|-------|---------------------------|

| 0-31  | OdB to +31dB (+1dB steps) |

#### 5.6.3 Record Level Detection

#### Figure 15 Audio signal processing block diagram with Level Detect block highlighted

The record level detection function continuously monitors the record signal level and can be configured to trigger an interrupt when the record signal level exceeds a pre-programmed detection threshold. This feature is useful in low-power listening mode applications, such as a voice activated switch (VOX), where the CMX655D record level interrupt signal is used to wake-up a sleeping external host. The record level detection function interrupt enable bits are set in the **ISM** register and the record level detection thresholds for the left and right channels are independently set by the **LDCTRL** and **RDCTRL** registers respectively.

Each of left and right level detectors operates in a one-shot manner; a detector is automatically disabled when triggered and cannot be enabled again until its corresponding MICL or MICR bit in the **ISR** is cleared by a read of the **ISR** register.

#### 5.6.3.1 Record Level Detection Registers

#### LDCTRL (\$0D)

Left Channel Detection Control (R/W) Reset Value: \$00

| 7              | 6     | 5                                         | 4               | 3                     | 2               | 1            | 0               |  |  |  |

|----------------|-------|-------------------------------------------|-----------------|-----------------------|-----------------|--------------|-----------------|--|--|--|

| LEN            |       |                                           |                 | LTHRESH               |                 |              |                 |  |  |  |

|                |       |                                           |                 |                       |                 |              |                 |  |  |  |

| LEN            | Left  | Channel Det                               | ection Enable   |                       |                 |              |                 |  |  |  |

| 0              | Disat | Disable left channel interrupt detection. |                 |                       |                 |              |                 |  |  |  |

| 1              |       |                                           | el interrupt de |                       |                 |              |                 |  |  |  |

|                |       |                                           | ally cleared to |                       |                 |              | bit is equival  |  |  |  |

|                | state | is always th                              | e same as tha   | t of the MICL         | ISE register b  | oit.         |                 |  |  |  |

|                |       |                                           |                 |                       |                 |              |                 |  |  |  |

| LTHRESH        |       |                                           | ection Thresh   | •••                   |                 |              |                 |  |  |  |

| 0-89           |       |                                           | S (+1dB steps)  |                       |                 |              |                 |  |  |  |

| 90-127         | -1dB  | FS                                        |                 |                       |                 |              |                 |  |  |  |

| RDCTRL (\$0E)  |       |                                           |                 |                       |                 |              |                 |  |  |  |

| Right Channe   |       | `ontrol (R/W                              | )               |                       |                 |              |                 |  |  |  |

| Reset Value: S |       |                                           | ,               |                       |                 |              |                 |  |  |  |

|                | ,     |                                           |                 |                       |                 |              |                 |  |  |  |

| 7              | 6     | 5                                         | 4               | 3                     | 2               | 1            | 0               |  |  |  |

| REN            |       |                                           |                 | RTHRESH               |                 |              |                 |  |  |  |

|                |       |                                           |                 |                       |                 |              |                 |  |  |  |

| REN            | Right | Channel De                                | tection Enabl   | е                     |                 |              |                 |  |  |  |

| D              | Disat | ole right char                            | nnel interrupt  | detection.            |                 |              |                 |  |  |  |

| 1              | Enab  | le right chan                             | nel interrupt o | detection.            |                 |              |                 |  |  |  |

|                | REN   | is automatic                              | ally cleared to | 0 if the <b>ISR</b> N | /ICR bit is set | to 1. The RE | N bit is equiva |  |  |  |

state is always the same as that of the MICR ISE register bit.

| RTHRESH | <b>Right Channel Detection Threshold</b> |  |  |  |

|---------|------------------------------------------|--|--|--|

| 0-89    | -90dBFS to -1dBFS (+1dB steps)           |  |  |  |

| 90-127  | -1dBFS                                   |  |  |  |

# 5.6.4 Playback Preamplifier Gain

#### Figure 16 Audio signal processing block diagram with preamp block highlighted

The **PREAMP** register sets the playback preamplifier gain to 1/2/4/8 (approximately 0/6/12/18dB).

# 5.6.4.1 Playback Preamplifier Gain Register

#### PREAMP (\$29)

Playback Preamp Gain (R/W) Reset Value: \$00

| 7 | 6 | 5      | 4 | 3 | 2 | 1 | 0   |  |

|---|---|--------|---|---|---|---|-----|--|

| 0 |   |        |   |   |   |   | PRE |  |

|   |   | с. с.: |   |   |   |   |     |  |

| PRE | Pre-amplifier Gain |

|-----|--------------------|

| 0   | 1 (OdB)            |

| 1   | 2 (6dB)            |

| 2   | 4 (12dB)           |

| 3   | 8 (18dB)           |

#### 5.6.5 Playback Volume Control

#### Figure 17 Audio signal processing block diagram with the volume block highlighted

The VOLUME register sets the playback amplifier gain between 0dB and -90dB in 1dB steps.

#### 5.6.5.1 Playback Volume Register

#### VOLUME (\$2A)

0

1

Playback Volume (R/W) Reset Value: \$00

| 7      | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|--------|---|---|---|-----|---|---|---|

| SMOOTH |   |   |   | VOL |   |   |   |

#### SMOOTH Volume Smoothing

Volume smoothing disabled - the VOL setting is applied immediately Volume smoothing enabled - the VOL setting is applied gradually using intermediate gain steps near zero-crossings or after a 5ms timeout if no zero-crossing is detected

| VOL    | Volume Gain Setting       |

|--------|---------------------------|

| 0      | Mute                      |

| 1-91   | -90dB to 0dB (+1dB steps) |

| 92-127 | OdB                       |

The generation of the VOL interrupt status bit in the **ISR** bit register is enabled by setting the VOL interrupt enable bit in the **ISE** register. The VOL **ISR** bit indicates that volume gain adjustment has completed, which occurs 32 sample periods after the applied volume gain equals the volume gain setting. To avoid the immediate generation of a VOL interrupt, the VOL **ISE** bit should only be set following a change in the volume gain setting.

To reduce click-and-pop artefacts, it is recommended to mute the volume and wait for volume gain adjustment completion before clearing the PAMP bit in the **SYSCTRL** register when disabling the Class-D power amplifier.

#### 5.6.6 Automatic Level Control

#### Figure 18 Audio signal processing block diagram with ALC block highlighted

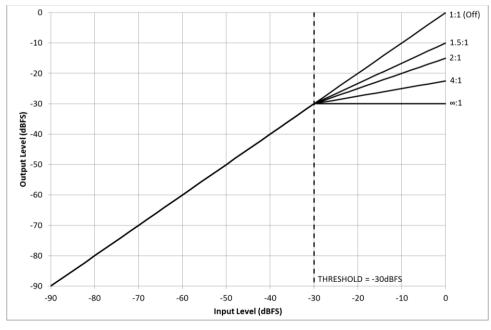

The ALC function is designed to enhance low-level playback signals by reducing the dynamic range of the output signal with respect to the input signal. The ALC is implemented using downward compression such that the output signal level is attenuated in proportion to the degree in which the peak input signal level is above the compression threshold. The ALC is controlled using the **ALCCTRL** register where the input-to-output signal level ratio above the compression threshold may be programmed as 1.5:1, 2:1, 4:1 or  $\infty$ :1. The ideal compression attenuation A<sub>COM</sub> (dB) when the input signal (dBFS) is above the compression threshold (dBFS) for a given a compression ratio of C:1 is:

$A_{COM} = (C-1)^{*}(Input - Threshold)/C$

However, it should be noted that  $A_{COM}$  is only controlled using 1dB of resolution. Figure 19 shows the ideal ALC response for these ratios with the threshold set to -30dBFS. The 1:1 ratio is effective when the ALC is disabled.

#### Figure 19 ALC Response

The ALC response time is programmed using the **ALCTIME** register. The attack time determines how long it would take the ALC to apply 12dB of downwards compression when the input signal rises above the threshold. The release time determines how long it would take the ALC to remove 12dB of downwards compression once the signal falls back below the threshold. The attack and release times therefore determine the rate at which compression is applied and removed.

To make-up for lost gain due to the downwards compression, up to 12dB of make-up gain is selectable using the ALCGAIN register. The make-up gain is applied regardless of whether the ALC is enabled. The compression attenuation applied by the ALC excluding the make-up gain may be read from the ALCSTAT register.

#### 5.6.6.1 ALC Registers

#### ALCCTRL (\$2B)

ALC Control (R/W) Reset Value: \$00

| 7  | 6  | 5   | 4 | 3 | 2      | 1 | 0 |

|----|----|-----|---|---|--------|---|---|

| EN | RA | TIO |   |   | THRESH |   |   |

0 ALC disabled (1:1 ratio) 1

ALC enabled

| 1.5:1 |

|-------|

| 2:1   |

| 4:1   |

| ∞:1   |

|       |

#### THRESH Threshold

-31dBFS to OdBFS (+1dB steps) 0-31

## ALCTIME (\$2C)

ALC Time (R/W) Reset Value: \$00

| 7         | 6          | 5       | 4 | 3 | 2        | 1 | 0 |         |  |  |  |

|-----------|------------|---------|---|---|----------|---|---|---------|--|--|--|

| 0         |            | ATTACK  |   |   | ATTACK 0 |   | 0 | RELEASE |  |  |  |

| A TT A CV | A          | (       |   |   |          |   |   |         |  |  |  |

| ATTACK    | Attack Tin | ne (ms) |   |   |          |   |   |         |  |  |  |

| 0         | 1.5        |         |   |   |          |   |   |         |  |  |  |

| 1         | 3          |         |   |   |          |   |   |         |  |  |  |

| 2         | 4.5        |         |   |   |          |   |   |         |  |  |  |

| 3         | 6          |         |   |   |          |   |   |         |  |  |  |

| 4         | 12         |         |   |   |          |   |   |         |  |  |  |

| 5         | 24         |         |   |   |          |   |   |         |  |  |  |

| 6         | 48         |         |   |   |          |   |   |         |  |  |  |

| 7         | 96         |         |   |   |          |   |   |         |  |  |  |

| RELEASE   | Release Ti | me (s)  |   |   |          |   |   |         |  |  |  |

| 0         | 0.06       |         |   |   |          |   |   |         |  |  |  |

| 1         | 0.12       |         |   |   |          |   |   |         |  |  |  |

| 2         | 0.24       |         |   |   |          |   |   |         |  |  |  |

| 3         | 0.48       |         |   |   |          |   |   |         |  |  |  |

| 4         | 0.96       |         |   |   |          |   |   |         |  |  |  |

| 5         | 1.92       |         |   |   |          |   |   |         |  |  |  |

| 6         | 3.84       |         |   |   |          |   |   |         |  |  |  |

| 7         | 7.68       |         |   |   |          |   |   |         |  |  |  |

# ALCGAIN (\$2D)

# ALC Make-up Gain (R/W)

| Reset | Value: | \$00 |

|-------|--------|------|

|       |        |      |

| 7                                                     | 6      | 5                     | 4 | 3 | 2   | 1 | 0 |

|-------------------------------------------------------|--------|-----------------------|---|---|-----|---|---|

| 0                                                     |        |                       |   |   | GAI | Ν |   |

| GAIN                                                  | Make-u | Make-up Gain          |   |   |     |   |   |

| 0-12                                                  | 0dB-12 | OdB-12dB (+1dB steps) |   |   |     |   |   |

| 13-15                                                 | 12dB   |                       |   |   |     |   |   |

| ALCSTAT (\$21                                         |        |                       |   |   |     |   |   |

| ALC Status (R                                         | .)     |                       |   |   |     |   |   |

| ALCSTAT (\$21<br>ALC Status (R<br>Reset Value: )<br>7 | .)     | 5                     | 4 | 3 | 2   | 1 | 0 |

ATTENALC Attenuation0-310dB to +31dB (+1dB steps)

#### 5.6.7 Digital Sidetone

#### Figure 20 Audio signal processing block diagram with the Digital Side Tone path and block highlighted

Digital sidetone feeds a proportion of the microphone signal back into the playback signal path to provide audible feedback to the speaking user. The sidetone level and input source are controlled by the **DST** register which provides programmable signal attenuation of -62dB to 0dB in +2dB steps.

#### 5.6.7.1 Digital Sidetone Register

#### DST (\$2F)

Digital Sidetone Control (R/W) Reset Value: \$00

| 7  | 6                          | 5 | 4 | 3    | 2 | 1 | 0 |  |

|----|----------------------------|---|---|------|---|---|---|--|

| EN | EN DSTS                    |   |   | DSTG |   |   |   |  |

| EN | EN Digital Sidetone Enable |   |   |      |   |   |   |  |

| 0  | Sidetone disabled (muted)  |   |   |      |   |   |   |  |

| 1  | Sidetone enabled           |   |   |      |   |   |   |  |

# DSTS Digital Sidetone Source

- 0 Left microphone signal

- 1 Right microphone signal

- 2-3 Mean of left and right microphone signals

#### DSTG Digital Sidetone Gain

0 to 31 -62dB to 0dB (+2dB steps)

# 5.6.8 Voice Filters

#### Figure 21 Audio signal processing block diagram with Voice Filter blocks highlighted

The voice filters provide narrow audio band filtering and may be optionally enabled as required.

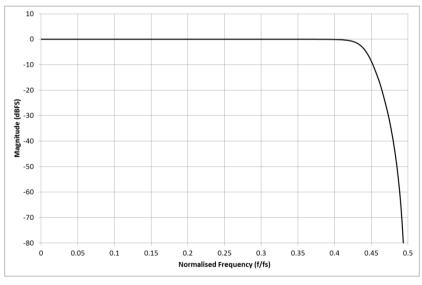

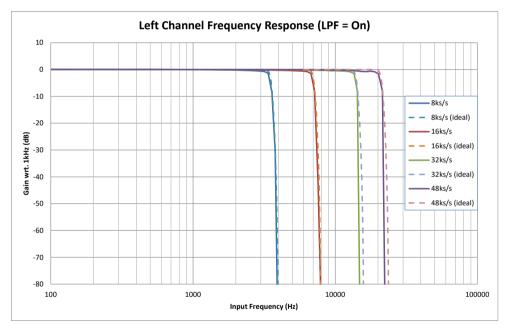

## 5.6.8.1 Low Pass Filter

The low pass IIR filter has a 4<sup>th</sup>-order Butterworth response with a passband -3dB point of 0.4375 x f<sub>s</sub> (i.e. 3500/7000/14000/21000Hz @ 8/16/32/48ksps). The low pass filter for the record and playback channels is enabled by the LPFEN bit in the **RVF** and **PVF** registers respectively. The frequency response of the low pass filter is shown in Figure 22.

Figure 22 Low Pass Filter Frequency Response

#### 5.6.8.2 DC Blocking Filter

The DC blocking filter provides 90dB of DC attenuation. The DC blocking filter for the record and playback channels is enabled by the DCBEN bit in the **RVF** and **PVF** registers respectively.

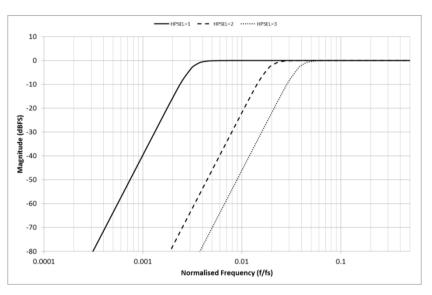

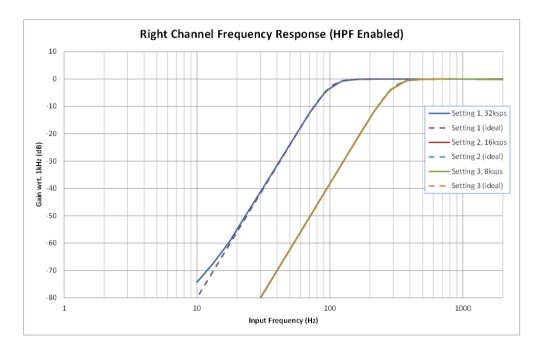

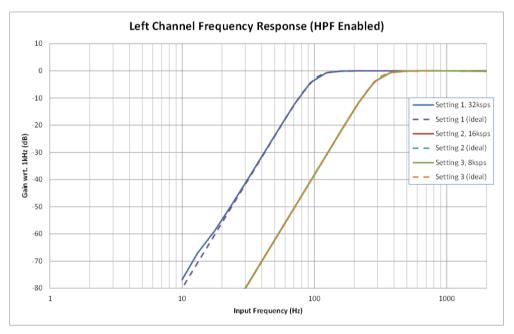

#### 5.6.8.3 High Pass Filter

The high pass IIR filter has a 4<sup>th</sup>-order Butterworth response with three selectable -3dB points to accommodate different applications and may be optionally disabled. The high pass filter for the record and playback channels is controlled by the HPSEL bits in the **RVF** and **PVF** registers respectively. The frequency response of the high pass filters are shown in Figure 23.

Figure 23 High Pass Filter Frequency Response

## 5.6.8.4 Voice Filters Registers

#### RVF (\$0C)

Record Voice Filters (R/W) Reset Value: \$00

| 7               | 6                             | 5                          | 4               | 3                          | 2             | 1             | 0     |  |

|-----------------|-------------------------------|----------------------------|-----------------|----------------------------|---------------|---------------|-------|--|

|                 | 0                             |                            |                 | LPFEN                      | DCBEN         | HPSEL         |       |  |

|                 |                               |                            |                 |                            |               |               |       |  |

| LPFEN           | Record Low Pass Filter Enable |                            |                 |                            |               |               |       |  |

| )               | Low pass f                    | Low pass filter disabled   |                 |                            |               |               |       |  |

| 1               | Low pass f                    | filter enabled             |                 |                            |               |               |       |  |

| DCBEN           | Record DC                     | Blocking Filt              | er Enable       |                            |               |               |       |  |

| 0               |                               | ng filter disabl           |                 |                            |               |               |       |  |

| 1               | DC blockir                    | DC blocking filter enabled |                 |                            |               |               |       |  |

| HPSEL           | Record Hi                     | gh Pass Filter             | Select          |                            |               |               |       |  |

| 0               | High pass                     | -<br>filter disabled       |                 |                            |               |               |       |  |

| 1               | High pass                     | filter with a -3           | BdB point of 0. | 003125 x f <sub>s</sub> (  | e.g3dB point  | of 50Hz @ 16  | ksps) |  |

| 2               | High pass                     | filter with a -3           | dB point of 0.  | 01875 x f <sub>s</sub> (e  | .g3dB point ( | of 300Hz @ 16 | ksps) |  |

| 3               | High pass                     | filter with a -3           | dB point of 0.  | 0375 x f <sub>s</sub> (e.g | 3dB point of  | f 300Hz @ 8ks | os)   |  |

|                 | 0,                            |                            |                 |                            |               |               |       |  |

| PVF (\$28)      |                               |                            |                 |                            |               |               |       |  |

| Playback Voic   | e Filters (R/W                | /)                         |                 |                            |               |               |       |  |

| Reset Value: \$ | 500                           |                            |                 |                            |               |               |       |  |

| 7               | 6                             | 5                          | 4               | 3                          | 2             | 1             | 0     |  |

© 2022 CML Microsystems Plc

0

LPFEN

DCBEN

HPSEL

| LPFEN | Playback Low Pass Filter Enable                                                        |

|-------|----------------------------------------------------------------------------------------|

| 0     | Low pass filter disabled                                                               |

| 1     | Low pass filter enabled                                                                |

| DCBEN | Playback DC Blocking Filter Enable                                                     |

| 0     | DC blocking filter disabled                                                            |

| 1     | DC blocking filter enabled                                                             |

| HPSEL | Playback High Pass Filter Select                                                       |

| 0     | High pass filter disabled                                                              |

| 1     | High pass filter with a -3dB point of 0.003125 x fs (e.g3dB point of 50Hz @ 16ksps)    |

| 2     | High pass filter with a -3dB point of 0.01875 x $f_s$ (e.g3dB point of 300Hz @ 16ksps) |

| 3     | High pass filter with a -3dB point of 0.0375 x fs (e.g3dB point of 300Hz @ 8ksps)      |

#### 5.6.9 Channel Multiplexing

#### Figure 24 Audio signal processing block diagram with Mic Mux and Amp Mux block highlighted

The left and right microphone output channels may be interchanged or duplicated by appropriately setting the MIC control bits in the **SAIMUX** register defined in section 5.8.5. The interchange and duplication of channels requires both microphone channels to be enabled.

The mono amplifier input channel may be selected from the left input or the right input or the mean of the left and right inputs by appropriately setting the AMP control bits in the **SAIMUX** register.

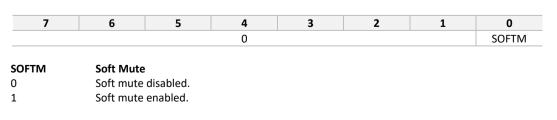

#### 5.6.10 Click-and-Pop Reduction

The CMX655D provides a soft mute function that generates low-level background noise when the playback volume is muted which potentially reduces audible click-and-pop artefacts.

#### 5.6.10.1 Click-and-Pop Reduction Register

#### CPR (\$30)

Click-and-Pop Reduction (R/W) Reset Value: \$00

#### 5.7 Control Interface

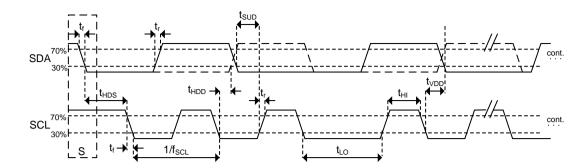

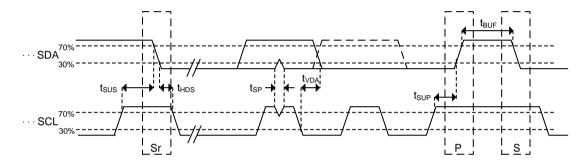

The CMX655D is configured and controlled via the Control Interface. The interface communicates as a SPI Slave when the external SPIS pin is tied high to VDD\_AD or as a TWI Slave when the external SPIS pin is tied low to DGND. These interfaces allow communication with standard MCUs and DSPs and are commonly used by existing audio codecs.

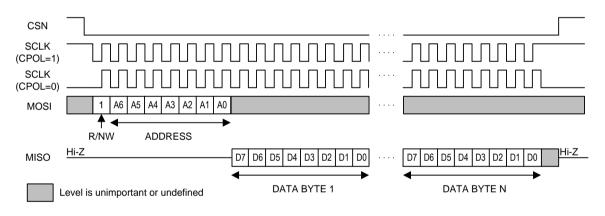

#### 5.7.1 SPI Slave

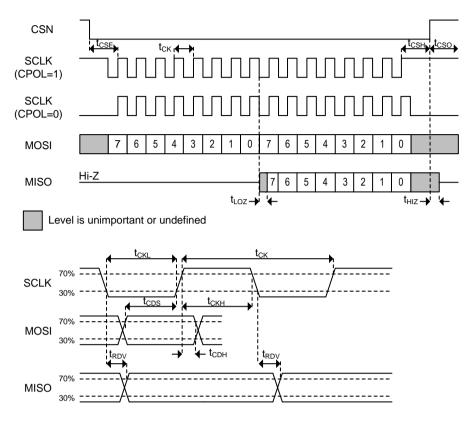

The CMX655D SPI Slave responds to activity on the SPI-bus when the chip-select pin CSN is driven low. Input data on MOSI is clocked in by the CMX655D SPI Slave on the rising edge of SCLK. Output data on MISO is clocked out by the CMX655D SPI Slave on the falling edge of SCLK when transferring read data.

The CMX655D SPI Slave only drives MISO when transferring read data from a valid device address. This feature allows the CMX655D SPI pin connections to be potentially shared with other CML C-BUS slave devices. An external pull-up resistor to VDD\_AD (or pull-down resistor to DGND) must be connected to MISO to prevent the node from floating when not driven by the CMX655D SPI Slave or any other connected device. The CMX655D SPI Slave is insensitive to the polarity of SCLK at the start and end of each transfer and is compatible with SPI masters operating in SPI Mode 0 (CPOL=0, CPHA=0) or SPI Mode 3 (CPOL=1, CPHA=1).

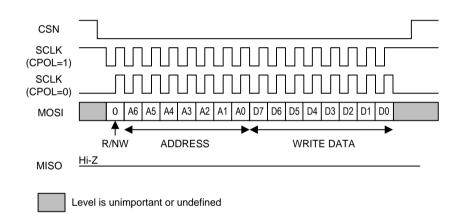

The CMX655D communicates over the SPI interface using a transfer width of 16-bits. Figure 25 shows the SPI transfer protocol for performing a single-byte write to the CMX655D.

#### Figure 25 SPI Write Transfer

The first bit on MOSI is the Read/NotWrite bit (R/NW) and this is set to 0 to indicate a write transfer and the following 7bits (A6 to A0) indicate the register address to be written (MSB first). The remaining 8-bits on MOSI (D7 to D0) indicate the data to be written (MSB first).

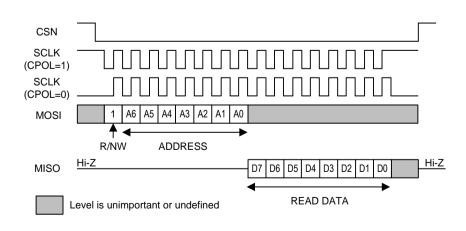

Figure 26 shows the SPI transfer protocol for performing a single-byte read from the CMX655D.

CMX655D