# FlashPro for Software v11.4 User's Guide

NOTE: PDF files are intended to be viewed on the printed page; links and cross-references in this PDF file may point to external files and generate an error when clicked. View the online help included with software to enable all linked content.

# **Table of Contents**

| About FlashPro                                                                         | 5          |

|----------------------------------------------------------------------------------------|------------|

| Supported Families                                                                     | 10         |

| FlashPro Interface                                                                     | 12         |

| Introductory Programming Tutorials                                                     | 19         |

| Advanced Tutorials                                                                     | 52         |

| Programming Settings and Operations                                                    | 66         |

| Single Device Configuration                                                            | 71         |

| Chain Programming                                                                      | 75         |

| Chain Editing                                                                          | 83         |

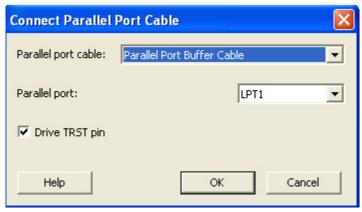

| Configuring a Programmer                                                               | 86         |

| Configuring Security                                                                   | 89         |

| IGLOO and ProASIC3 Programming Programming File Actions for IGLOO and ProASIC3 Devices |            |

| SmartFusion and Fusion (AFS) Programming                                               | 102        |

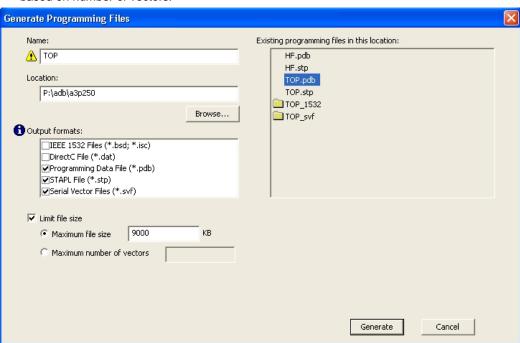

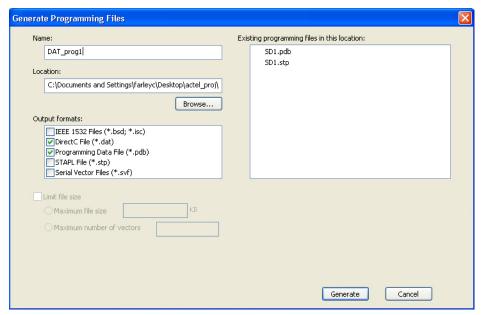

| Generating Programming Files                                                           | 106        |

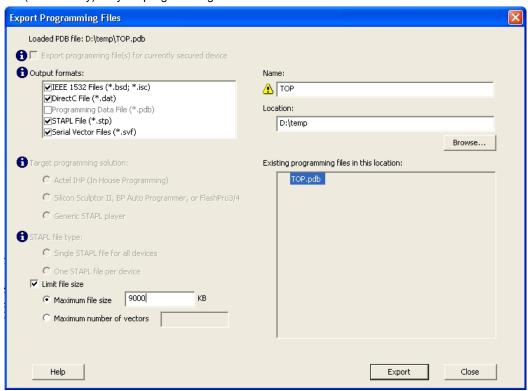

| Importing and Exporting Files                                                          | 126        |

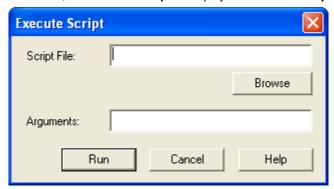

| Using Hot Keys import_config remove_device remove_non_actel_device_from_database       | 155<br>163 |

| Troubleshooting                                                                        | 185        |

| Electrical Parameters                                                                  | 215        |

| Electrical Specifications                                                              | 219        |

| Solutions to Common Issues Using Device Debug                                          | 226        |

| Frequently Asked Questions                                                             | 228        |

### Table of Contents

| Embedded Flash Memory (NVM) Frequently Asked Questions |     |

|--------------------------------------------------------|-----|

| Device Debug User Interface                            | 238 |

| Debug SERDES                                           | 250 |

| Live Probes                                            | 255 |

| Active Probes                                          | 256 |

| Contacting Microsemi                                   | 277 |

| Regulatory and Compliance Information                  | 279 |

| Product Support                                        | 280 |

# About FlashPro

FlashPro is Microsemi's programming software tool for SmartFusion, IGLOO, ProASIC3, Fusion devices. You will be able to navigate easily through the FlashPro software because of its similarities with other Microsemi software tools. The FlashPro software includes the following features:

- Supports modification of I/O states during programming

- Supports automatic construction of chain from scan chain operation

- Supports importing non-Microsemi BSDL files for automatic chain construction

- Supports direct multiple Microsemi device chain programming and serialization

- Supports single device STAPL files generation

- Supports single device SVF files generation

- Supports single device IEEE 1532 files generation

- Supports Chain STAPL file generation

- Supports Chain SVF file generation

- Supports a single GUI to drive multiple FlashPro5/4/3/3X programmers for parallel programming

- Supports 1.2V programming for IGLOO devices

Note: Note: Parallel programming via FlashPro (USB/LPT1) or FlashPro Lite programmers is not supported.

- Supports device serialization for parallel programming

- A redesigned GUI, which features a project manager to manage the programming files and data

- Enhanced In-System Programming (ISP) Support

An optional In-House Programming (IHP) service is available if you are purchasing Microsemi devices in volume. Contact Microsemi for more information.

For step-by-step instructions on how to use these features, see the FlashPro Tutorial.

If you arrived here by pressing the F1 key in FlashPro, use the **Search** tool in help for more information on specific content, or click the **Help** button embedded in any dialog box or GUI for context-specific help.

### **Installing FlashPro Express Software**

See the FlashproExpress Installation Instructions on the Microsemi website for information on how to install FlashproExpress software and relevant system requirements.

View the detailed Install Instructions and System Requirements at the Flashpro Express software page:

http://www.microsemi.com/products/fpga-soc/design-resources/programming/flashproexpress#overview

# **Programming Tool Model Overview**

The FlashPro software is designed for use in the operation, user design, and production programming flows.

### **Design Debug**

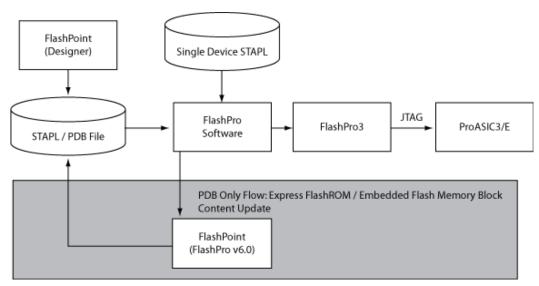

The figure below illustrates the programming design flow when an engineer is in debug mode. In the programming design flow, the new Programming files (STAPL/ PDB) are generated for a design change and are sent to the FlashPro software for testing and debugging the design.

Note: FlashPoint is integrated into Designer; therefore, the STAPL file is generated from Designer. FlashPro v6.2 and greater can be used to export STAPL files from PDB files created by FlashPoint (Designer).

Figure 1 · Programming Design Flow

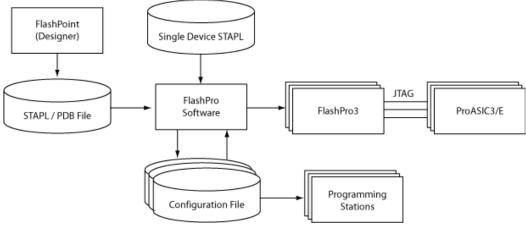

### **Operation/Production Planning**

The figure below shows an illustration of the operation flow. In this illustration, the production coordinator generates the programming files (STAPL/PDB) with or without serialization and/or security settings (see Programming application note for further information). The production coordinator loads the programming file in the FlashPro software to set up the configurations for production programming, such as Serialization options, Action selections, and Procedure selections, etc.

Figure 2 · Operation Flow

The production coordinator may want to generate different configuration files for each programming station (depending on the logistics and serialization options). For example, if the Programming file contains 10,000 serial data and the production coordinator decides to split the serial data designation to one thousand for each programming station, then ten configuration files will be generated (one for each of the ten programming stations). However, if you are not using serialization, you only need one configuration file.

The production coordinator can test the configuration files with one or more FlashPro5/4/3/3X programmers before sending it to the production programming floor. If PDB files are used in the production flow, warning icons may appear on the FlashPro/FlashPoint GUI because the automatic audit cannot find the source file on the production environment; the PDB file contains the valid programming data. If STAPL files are used, loaded STAPL files will be audited on execution of an action to determine if the original STAPL file has been modified. If it has not been modified, the action will continue to run. If it has been modified you will be prompted to reload the modified STAPL file, or to continue running the current action. If you select to reload the modified STAPL file, all previous programming settings will be refreshed and will need to be performed again.

### **Operation/Production Programming**

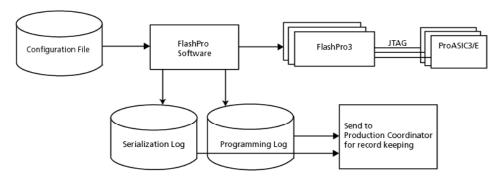

The figure below shows an illustration of the production programming flow. The operator imports the configuration file and begins programming the devices by clicking the **Run** button. The operator's interaction with FlashPro should be limited.

At the end of a programming session, the serialization log file (if applicable) and the programming log file are sent back to the production coordinator for record keeping.

Figure 3 · Production Programming Flow

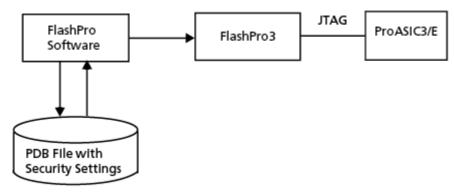

### Express Configuration Programming (IGLOO, ProASIC3 and Fusion devices only)

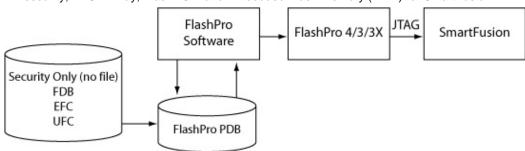

The figure below illustrates the Express Configuration Programming Flow. In this flow, you can program the security setting into the IGLOO, ProASIC3 and Fusion family device directly from the FlashPro software.

Note: FlashPoint is integrated into the FlashPro v6.0 and later software.

Figure 4 · Express Configuration Programming Flow

# Programming Tool User Model Overview - SmartFusion Only

The FlashPro software is designed for use in the operation, user design, and production programming flows.

### **Design Debug**

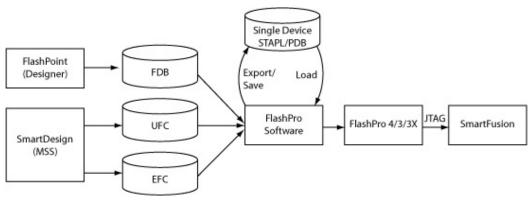

The figure below illustrates the programming design flow when an engineer is in debug mode. In the programming design flow, the new files (FDB, UFC, EFC) are generated for a design change and are sent to the FlashPro software for testing and debugging the design.

Figure 5 · SmartFusion Programming Design Debug Flow

### **Operation/Production Planning**

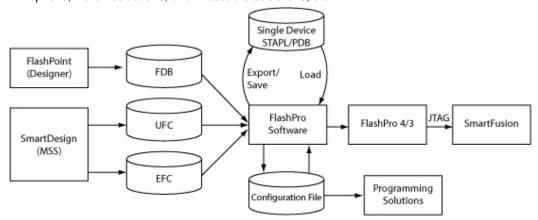

The figure below shows an illustration of the operation flow. In this illustration, the production coordinator generates the programming files (STAPL/PDB) with or without serialization and/or security settings (see Programming application note for further information). The production coordinator loads the programming file in the FlashPro software to set up the configurations for production programming, such as Serialization options, Action selections, and Procedure selections, etc.

Figure 6 · SmartFusion Operation Flow

The production coordinator may want to generate different configuration files for each programming station (depending on the logistics and serialization options). For example, if the Programming file contains 10,000 serial data and the production coordinator decides to split the serial data designation to one thousand for each programming station, then ten configuration files will be generated (one for each of the ten programming stations). However, if you are not using serialization, you only need one configuration file.

The production coordinator can test the configuration files with one or more FlashPro5/4/3/3X programmers before sending it to the production programming floor. If PDB files are used in the production flow, warning icons may appear on the FlashPro/FlashPoint GUI because the automatic audit cannot find the source file on the production environment; the PDB file contains the valid programming data. If STAPL files are used, loaded STAPL files will be audited on execution of an action to determine if the original STAPL file has been modified. If it has not been modified, the action will continue to run. If it has been modified you will be prompted to reload the modified STAPL file, or to continue running the current action. If you select to reload the modified STAPL file, all previous programming settings will be refreshed and will need to be performed again.

### **Operation/Production Programming**

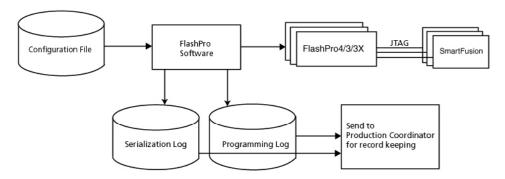

The figure below shows an illustration of the production programming flow. The operator imports the configuration file and begins programming the devices by clicking the **Run** button. The operator's interaction with FlashPro should be limited.

At the end of a programming session, the serialization log file (if applicable) and the programming log file are sent back to the production coordinator for record keeping.

Figure 7 · SmartFusion Production Programming Flow

# **Creating a New PDB for SmartFusion**

The figure below illustrates the new <u>SmartFusion programming flow</u>. In this flow you can program the security, FPGA Array, FlashROM and Embedded Flash Memory (NVM) for SmartFusion.

Figure 8 · Creating a New PDB for SmartFusion

# **SmartFusion2 Programming**

SmartFusion2 programming is executed from within Libero SoC.

See the Libero SoC help for information on SmartFusion2 programming, including programming authentication error codes and programming error codes.

# Supported Families

Microsemi's Libero SoC software supports the following families of devices:

- SmartFusion2

- IGLOO2

- SmartFusion

- IGLOO

- ProASIC3

- Fusion

When we specify a family name, we refer to the device family and all its derivatives, unless otherwise specified. See the table below for a list of supported device families and their derivatives:

Table 1 · Product Families and Derivatives

| Device<br>Family | Family<br>Derivatives   | Description                                                                                                                                                                          |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SmartFusion2     | N/A                     | Address fundamental requirements for advanced security, high reliability and low power in critical industrial, military, aviation, communications and medical applications.          |

| IGLOO2           | N/A                     | Low-power mixed-signal programmable solution                                                                                                                                         |

| SmartFusion      | SmartFusion             | SmartFusion intelligent mixed-signal FPGAs are the only devices that integrate an FPGA, ARM Cortex-M3, and programmable analog, offering full customization and IP protection.       |

| Fusion           | N/A                     | Mixed-signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM® Cortex <sup>TM</sup> -M1 soft processors, and flash memory into a monolithic device. |

| <u>IGLOO</u>     | IGLOO                   | The ultra-low-power, programmable solution                                                                                                                                           |

|                  | IGLO0e                  | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                |

|                  | IGLOO nano              | The industry's lowest power, smallest size solution                                                                                                                                  |

|                  | IGLOO PLUS              | The low-power FPGA with enhanced I/O capabilities                                                                                                                                    |

| ProASIC3         | ProASIC3                | The low-power, low-cost, FPGA solution                                                                                                                                               |

|                  | ProASIC3E               | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                             |

|                  | ProASIC3<br>nano        | Lowest cost solution with enhanced I/O capabilities                                                                                                                                  |

|                  | ProASIC3L               | The FPGA that balances low power, performance, and low cost                                                                                                                          |

|                  | Automotive<br>ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                 |

|                  | Military<br>ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                |

|                  | RT ProASIC3             | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                          |

# Installing FlashPro Software and Hardware

See the FlashPro Installation Instructions on the Microsemi website for information on how to install FlashPro software/hardware and relevant system requirements.

View the detailed Install Instructions and System Requirements at the FlashPro software page: http://www.microsemi.com/products/fpga-soc/design-resources/programming/flashpro#overview

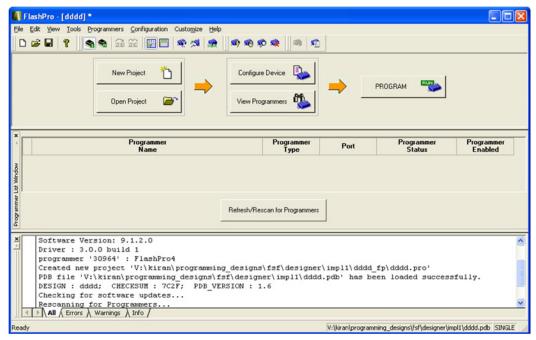

# Starting FlashPro

You can start the FlashPro software from **Programs > Microsemi FlashPro vx.x > FlashPro**. If you installed the program in a folder other than FlashPro, choose that folder from the **Programs** menu.

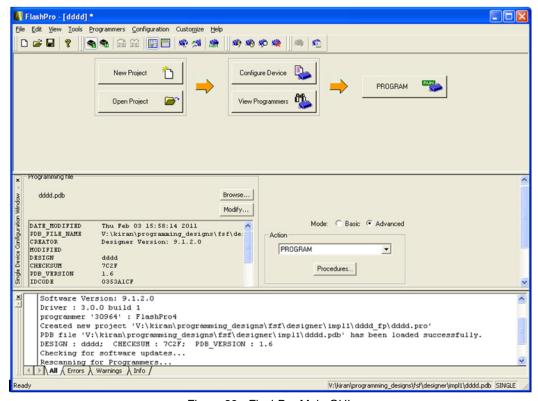

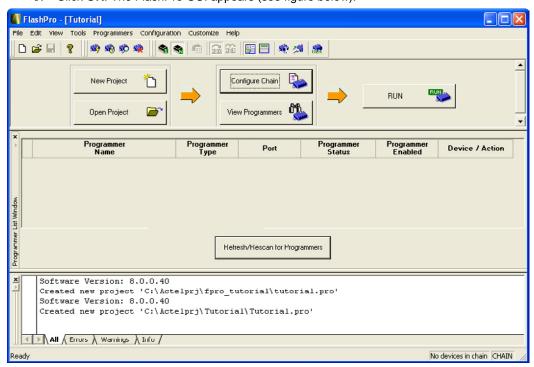

The figure below shows the FlashPro GUI. From this GUI, you can create a new project by clicking the **New Project** button or open an existing project by clicking the **Open Project** button.

You can also access the above features from the menu bar. You can access all the other features after you open or create a new project.

# FlashPro Interface

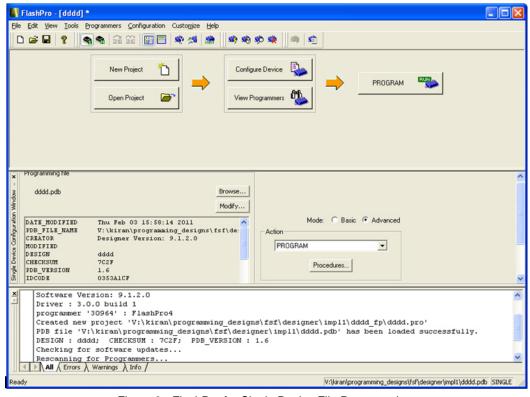

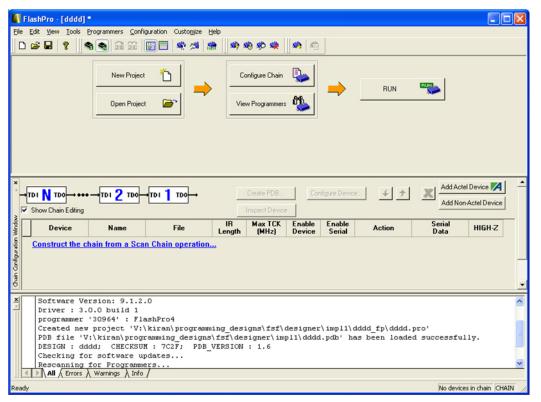

The main FlashPro interface consists of two views, one for Single Device Programming and the other for Chain Programming (see figure below). The GUI consists of a Flow window, Device Configuration Window (for single or chain programming), Log window and a Status bar. The Log window displays programming information, error messages, and warning messages. The Status bar displays your programming mode (chain programming or single device programming) and file status.

Figure 9 · FlashPro for Single Device File Programming

Note the different options in the Flow window for the Chain Programming GUI and the Single Device Programming GUI. In addition to the different Flow window options, the Chain Programming GUI view consists of the Chain Configuration window which displays the devices in your chain.

Figure 10 · FlashPro for Chain Programming

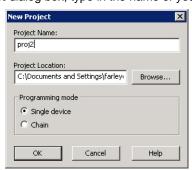

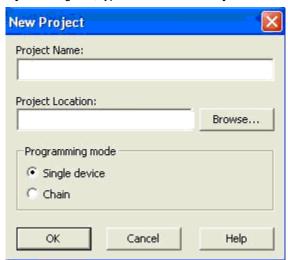

# Creating a New Project

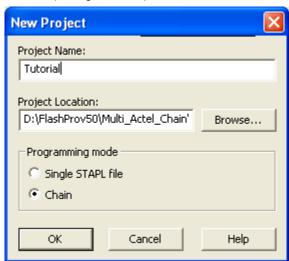

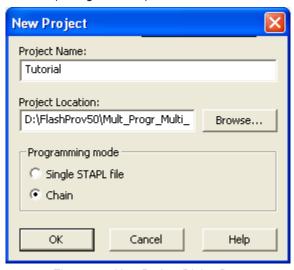

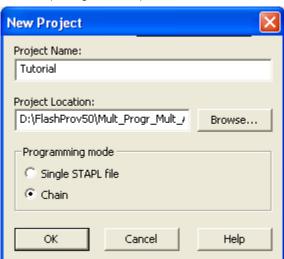

With the FlashPro software, you have the option of choosing either the **Single STAPL file** or **Chain programming** mode. You make this choice through the **New Project** dialog box (see figure below). By choosing the **Chain Programming** mode, you are enabling chain programming. The **Single STAPL file Programming** mode functions with the same programming capabilities as the FlashPro software v4.2.

#### To create a new project:

- 1. Click the **New Project** button or from the **File** menu choose **New Project**.

- 2. From the New Project dialog box, type in the name of your project in the Project Name field.

Figure 11 · New Project Dialog Box

- 3. If necessary, change the default location of your project in the Project Location field.

- 4. Choose your **Programming** mode (Single device or Chain).

- 5. Click **OK**. The FlashPro GUI displays (see figure below).

Figure 12 · FlashPro GUI

Note: You can switch between the two programming modes from Tools > Mode. From there, you can choose either Single Device Programming or Chain Programming.

# Opening a Project

You can open a project from the File menu or by clicking on the Open Project button in the flow window.

#### To open a project:

- 1. From the File menu, choose Open Project. The Open Project dialog box appears.

- 2. Find your project file or type in your project file name in the **File name** field.

- 3. Click Open.

# Saving a Project

Click the Save button on the toolbar, or from the File menu choose Save Project to save your project.

If you want to save your project under a different name/path, from the **File** menu choose **Save Project As** and save your project with the new name.

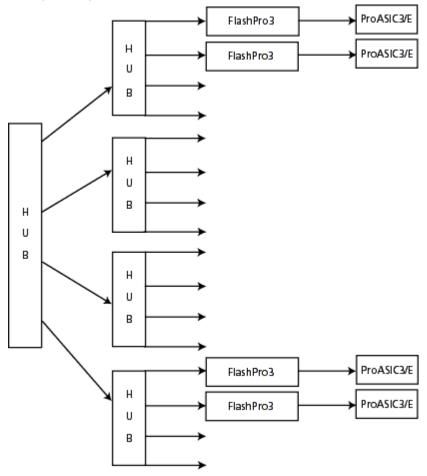

# Parallel Programming with FlashPro5/4/3/3X

Parallel programming enables you to program multiple Microsemi devices in parallel with multiple programmers. In parallel programming, all targeted devices are programmed with the same programming file (STAPL). The targeted device or chain configuration that is connected to each programmer must be identical.

The FlashPro software together with the FlashPro5/4/3/3X programmers supports parallel programming via a USB port. You can connect up to sixteen FlashPro5/4/3/3X's to a PC via a USB v1.1 or a USB v2.0 port. FlashPro5/4/3/3X requires a self-powered hub.

Connecting FlashPro5/4/3/3X (a USB v2.0 enabled programmer) to USB v1.1 port increases device programming time due to a slow data transfer rate on the USB v1.1 port in comparison to a USB v2.0 port.

Note: FlashPro (USB/LPT1) or FlashPro Lite programmers do not support parallel programming.

The following figure illustrates how you can connect a FlashPro5/4/3/3X programmer for parallel programming.

Figure 13 · Connecting a FlashPro5/4/3/3X Programmer

An independent thread processes the STAPL file during parallel programming. In an Microsemi test, parallel programming is approximately five times faster than programming 16 devices sequentially.

Note: Microsemi has tested Belkin PCI-USB cards and hubs. We have found that parallel programming works best with the vendor's latest driver installed and with the matching hubs.

# Serialization with FlashPro

You can use the FlashROM in the ProASIC3 device for serialization. For each target ProASIC3 device, different FlashROM contents are generated.

Serial Programming enables you to program a sequence of ProASIC3 devices in serial with an identical FPGA program and with different serialization data. Serialization data can consist of different FlashROM content and/or AES key values. To learn how to activate the serialization feature, see <a href="Skip Serial Data">Skip Serial Data</a> or Reuse Serial Data.

There are two different STAPL formats that support serial programming, multiple actions to multiple serial data and single action to multiple FlashROM.

### **Multiple Actions to Multiple FlashROM Serial Data**

This format supports a generic STAPL player because the STAPL player does not provide a mechanism for Serial Programming. One programming action is created to target different serial data. See examples below:

- PROGRAM\_1 programs the FPGA Array and the first serial data.

- PROGRAM\_2 programs the FPGA Array and the second serial data.

### Single Action to Multiple FlashROM Serial Data

This format is created when the target programmer is FlashPro, Sculptor II, or BP auto programmer, where the newly innovated Microsemi Serial Programming mechanism is supported. One programming action will program multiple serial data in serial.

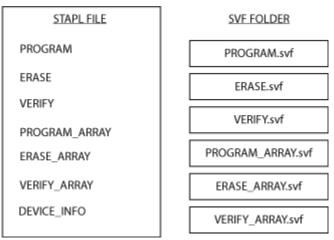

### FlashPro and SVF

SVF (Serial Vector Format) is an industry standard file format that is used to describe JTAG operations. Like STAPL files, SVF files are used for describing the in-system programming algorithm for SmartFusion, IGLOO, ProASIC3 and Fusion family devices. Unlike STAPL files, SVF files support only one ACTION or programming flow per file, due to language limitations. In addition, the SVF specification does not support message display and flow control, such as conditional statements or loops.

As a result, Microsemi tools (Designer and FlashPro software) generate a set of SVF files corresponding to the equivalent STAPL ACTIONS that are applicable to the silicon features selected.

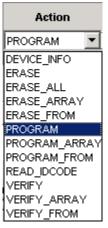

For example, for a typical STAPL file that has the following ACTIONS: ERASE, ERASE\_ALL, PROGRAM, PROGRAM\_ARRAY, VERIFY, VERIFY\_ARRAY, DEVICE\_INFO, READ\_IDCODE, and VERIFY\_DEVICE\_INFO, a set of corresponding SVF files are generated and named: ERASE.svf, ERASE\_ALL.svf, PROGRAM.svf, PROGRAM\_ARRAY.svf, etc. These files are generated in a folder, <Programming File Name>\_svf, created during generation. The diagram below demonstrates the differences between the STAPL and SVF files that are created.

Figure 14 · STAPL vs SVF files

Table 2 · SVF Outline

NOTE: DEVICE\_INFO.svf file is not generated because SVF files do not support messsage display or flow control.

| SVF File    | Array | FROM | NVM<br>(Flash<br>Memory<br>System<br>Builder) | Security<br>Settings | Previously<br>Programmed<br>Device? |

|-------------|-------|------|-----------------------------------------------|----------------------|-------------------------------------|

| ERASE       | Х     | Х    |                                               |                      | YES or NO                           |

| ERASE_ALL   | Х     | х    |                                               | X                    | YES or NO                           |

| ERASE_ARRAY | Х     |      |                                               |                      | YES or NO                           |

| ERASE_FROM  |       | х    |                                               |                      | YES or NO                           |

| SVF File                | Array | FROM | NVM<br>(Flash<br>Memory<br>System<br>Builder) | Security<br>Settings | Previously<br>Programmed<br>Device? |

|-------------------------|-------|------|-----------------------------------------------|----------------------|-------------------------------------|

| ERASE_SECURITY          |       |      |                                               | Х                    | YES or NO                           |

| PROGRAM                 | Х     | Х    |                                               |                      | YES or NO                           |

| PROGRAM_ARRAY           | Х     |      |                                               |                      | YES or NO                           |

| PROGRAM_FROM            |       | Х    |                                               |                      | YES or NO                           |

| PROGRAM_NVM             |       |      | Х                                             |                      | YES or NO                           |

| PROGRAM_SECURITY        |       |      |                                               | Х                    | YES or NO                           |

| VERIFY                  | Х     | Х    | Х                                             |                      | YES or NO                           |

| VERIFY_ARRAY            | Х     |      |                                               |                      | YES or NO                           |

| VERIFY_FROM             |       | х    |                                               |                      | YES or NO                           |

| VERIFY_NVM              |       |      | Х                                             |                      | NO                                  |

| ENC_DATA_AUTHENTICATION | Х     |      |                                               |                      | YES                                 |

#### **STAPL Actions not Available with SVF**

The following STAPL actions are not available with SVF: DEVICE\_INFO, VERIFY\_DEVICE\_INFO, READ\_IDCODE

# FlashPro and the 1532 File Format

1532 is an IEEE industry standard file format that is used to describe JTAG operations. Like STAPL files, 1532 files are used for describing the in-system programming algorithm for SmartFusion, IGLOO, ProASIC3 and Fusion family devices. 1532 programming file generation will generate two files (\*.isc, \*.bsd) within a folder.

The folder will be created with the following name <Programming File Name>\_1532. The \*.bsd file contains the IEEE 1532 programming algorithm. The \*.isc file contains the programming data to be programmed into the device.

IEEE 1532 programming files will only be exported in FlashPro for SmartFusion devices when an FDB has been properly imported.

## **STAPL to 1532 Action Mapping**

The IEEE 1532 standard requires using default ACTION names in order to function with 1532 compliant players. The table below describes the STAPL to 1532 ACTION name mappings.

NOTE: 1532 ACTIONs can have a data member parameter to allow reuse of the same ACTION name for different features.

Table 3 · STAPL to 1532 Action Name Mapping

| STAPL Action            | 1532 Action       |

|-------------------------|-------------------|

| ERASE_FROM              | ERASE(FROM)       |

| PROGRAM_FROM            | PROGRAM(FROM)     |

| VERIFY_FROM             | VERIFY(FROM)      |

| PROGRAM                 | PROGRAM           |

| PROGRAM_ARRAY           | PROGRAM(ARRAY)    |

| ERASE_ARRAY             | ERASE(ARRAY)      |

| ERASE                   | ERASE             |

| ERASE_ALL               | ERASE(ALLDATA)    |

| VERIFY                  | VERIFY            |

| VERIFY_ARRAY            | VERIFY(ARRAY)     |

| READ_IDCODE             | READ(IDCODE)      |

| ENC_DATA_AUTHENTICATION | VERIFY(ENCDATA)   |

| PROGRAM_SECURITY        | PROGRAM(SECURITY) |

| DEVICE_INFO             | READ              |

| VERIFY_NVM              | VERIFY_NVM        |

| VERIFY_SECURITY         | VERIFY(SECURITY)  |

| PROGRAM_NVM             | PROGRAM_NVM       |

### **STAPL Actions not Available with 1532**

The following STAPL action is not available with 1532: VERIFY\_DEVICE\_INFO

# **Introductory Programming Tutorials**

# Single STAPL/PDB File Basic Tutorial

This section provides step-by-step instructions to familiarize you with the basic features of the FlashPro software, specifically how to program a device. For more detailed step-by-step instructions and help with advanced features of the software, please see specific topics in the online help.

Note: This tutorial assumes that you have already installed the latest version of FlashPro software and have started the program.

First, create a new project and name it Tutorial. If FlashPro is launched through the Libero SoC, a new project will be created automatically and a PDB or FDB file loaded, if available.

#### To Create a Project:

- 1. Click the **New Project** button in FlashPro.

- 2. In the New Project dialog box, type Tutorial in the Project Name field.

Figure 15 · New Project Dialog Box

- 3. If necessary, change the default location of your project in the Project Location field.

- 4. Select the Single device Programming mode

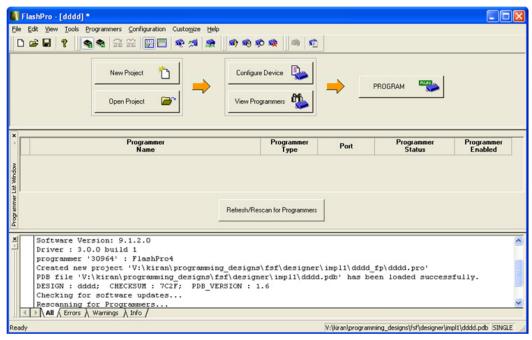

- 5. Click **OK**. The FlashPro GUI displays (see figure below). The Programmer List Window updates with your programmer information.

Figure 16 · FlashPro Main Window

### **Loading and Configuring a Programming File**

Once you have created your project and connected your programmer, you are ready to load your PDB or STAPL file.

#### To load a Programming file:

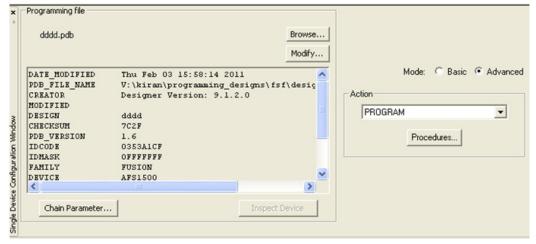

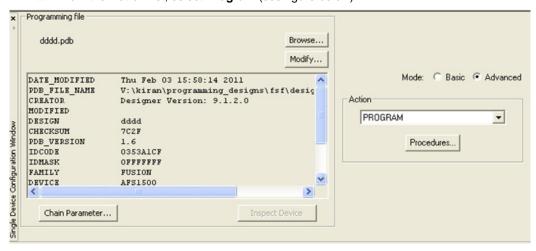

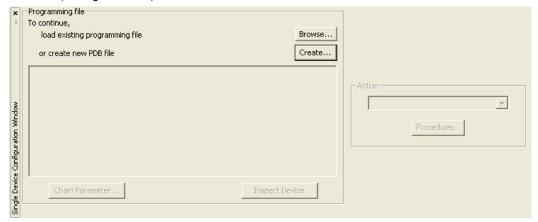

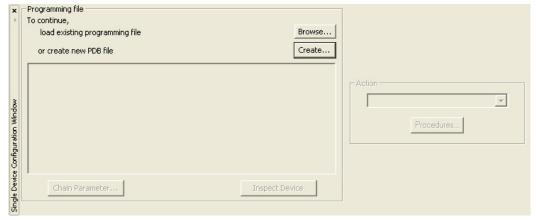

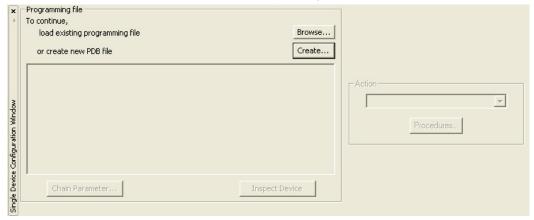

- 1. Click the Configure device button. The Single Device Configuration window displays in FlashPro.

- 2. Click the **Browse** button to find your Programming file.

- 3. From the Load Programming File dialog box, select your Programming file and click Open.

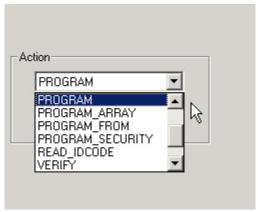

The Single Device Configuration Window updates to list your Programming file information and the actions available with your Programming file in the Action list box (see figure below). Program is the default action displayed in the Action list box.

Note: Microsemi recommends using the default settings.

Figure 17 · Single Device Configuration Window

This tutorial gives instructions on how to program a device. For an explanation on the other actions available, see <a href="Programming File Actions">Programming File Actions</a>.

### **Programming a Device**

Now that you have loaded your PDB file, programming a device is the next step.

#### To program a device:

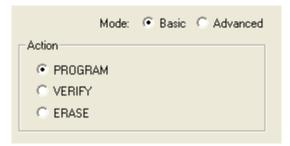

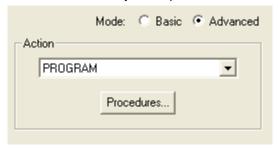

1. From the **Action** list, select **Program** (see figure below).

Figure 18 · Selecting Program from the Action List box

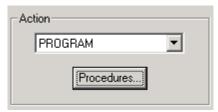

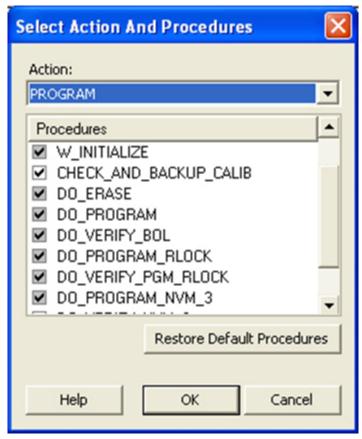

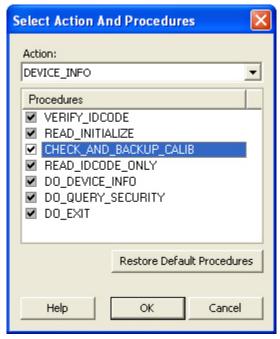

2. Click the **Procedures** button (see figure below).

Figure 19 · Procedures Button

The **Select Action And Procedures** dialog box appears, showing the procedures for the Programming action (see figure below). Microsemi recommends using the default settings.

Figure 20 · Select Action and Procedures Dialog Box

- 3. Click the **Restore Default Procedures** button.

- 4. In FlashPro click the **Program** button to program your device.

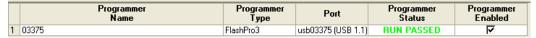

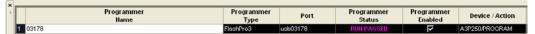

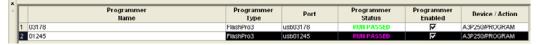

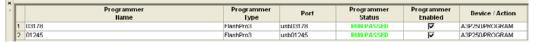

The **Programmer List Window** updates the **Programmer Status** column with Run Passed indicating that you have successfully programmed the device (see figure below).

Note: The status indicator updates during programming to show the programming progress, then it will change to a pass or fail result when the operation is complete.

Figure 21 · Successfully Programmed Device

5. View the **Log** window and take note of the details about your programmed device.

# Single Microsemi Device with Serialization Tutorial

This tutorial provides step-by-step instructions on how to program a single Microsemi Device with Serialization. Before you begin this tutorial, make sure you have already installed the FlashPro software and that you are familiar with the basic features of using the FlashPro software.

First, create the file generator using FROM for device serialization. You must have access to the Libero IDE v8.0 or later software to complete this step.

#### To Configure the FROM data for serialization:

- 1. Generate FROM via the Catalog.

- From the Properties section in the FlashROM Settings dialog box, select Auto Inc or Read From

File region. For the Auto Inc region, specify the step value. You will not be able to modify this value in

the FlashPoint software.

- 3. Complete the normal design flow and finish place and route.

- 4. Select Program FlashROM.

- Click Browse to find the UFC file.

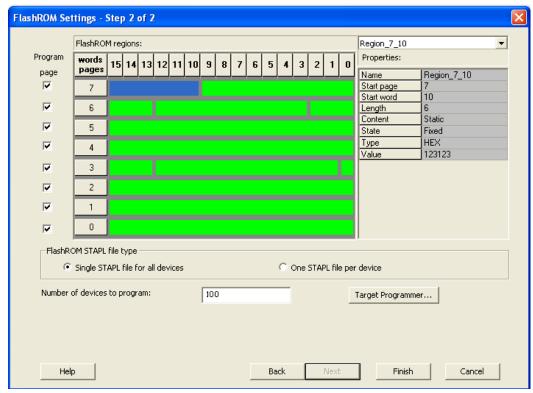

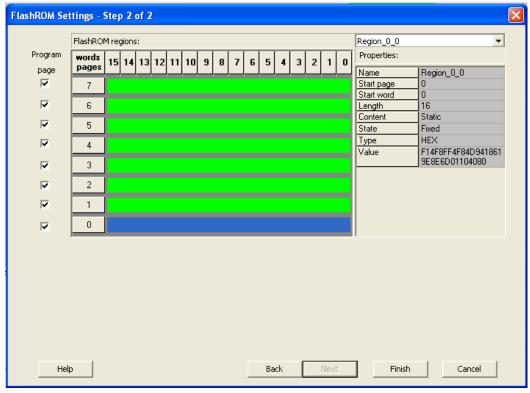

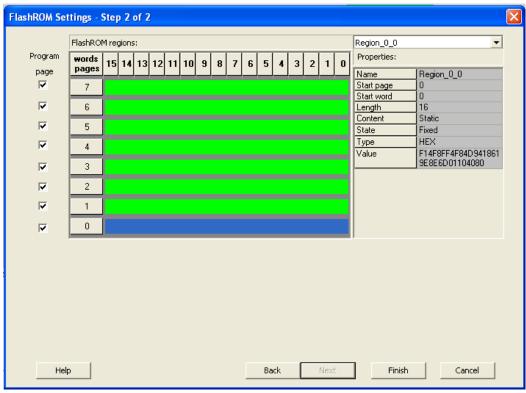

- Check the FPGA Array box and click Next. The FlashROM Settings window appears (as shown in the figure below).

Figure 22 · FlashROM Settings- Step 2 of 2

7. Select the FROM page you want to program and data value for the configured regions.

Note: Note: The generated STAPL file contains only the data that targets the selected FROM page.

- Modify properties for the serialization by specifying the Start and Max values. For the Auto Inc region, specify the Start and Max values. For the Read From File region, select the file name of the custom serialization file

- 9. Select the FlashROM programming file type you want to generate from the two options below:

Choose single STAPL file for all devices: generates one programming file with all FROM values.

Choose one STAPL file per device: generates a separate programming file for each FROM value.

- 10. Enter the number of devices you want to program and generate the required programming file.

- 11. Click the Finish button.

You have completed the steps to enable device serialization. Now you are ready to program a device using Device Serialization in FlashPro.

#### To program a device using device serialization:

- 1. Click the **New Project** button in the FlashPro.

- In the New Project dialog box, type Tutorial in the Project Name field.

- 3. Check the Single STAPL file option from the Programming Mode area.

- 4. If necessary, change the default location of your project in the Project Location field.

- 5. Click **OK**. The FlashPro GUI appears (see figure below).

Figure 23 · FlashPro Main GUI

The Programmer List Window updates with your programmer information.

- Click the Configure STAPL File button to load the STAPL file. The Single STAPL Configuration Window appears in the FlashPro GUI.

- 7. Click the **Browse** button to find your STAPL file.

- 8. From the **Load STAPL File** dialog box, find your STAPL file and click **Open**. The **Single STAPL Configuration Window** updates to list your STAPL file information and the actions available with your STAPL file in the **Action** list box (see figure below).

Figure 24 · Single STAPL Configuration Window with STAPL File Uploaded

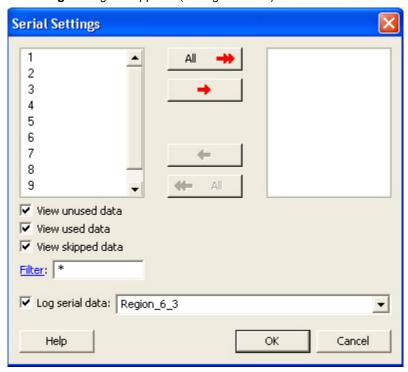

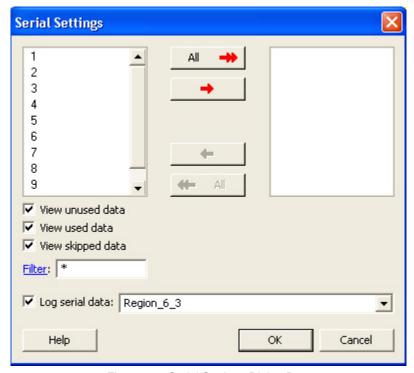

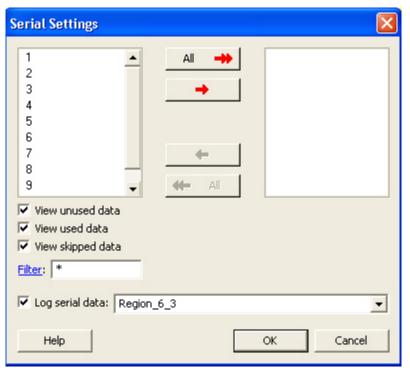

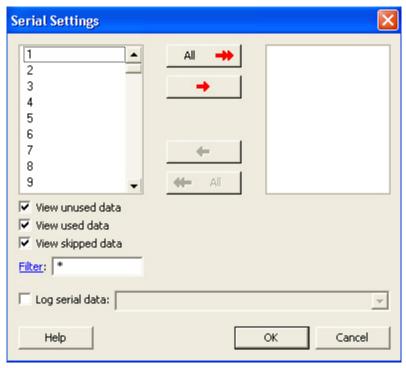

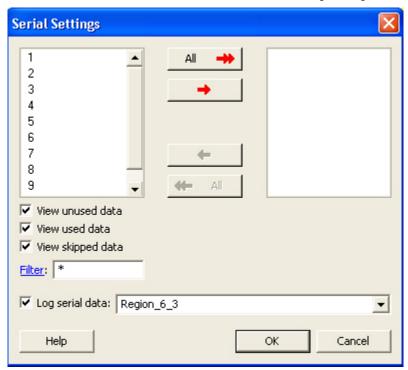

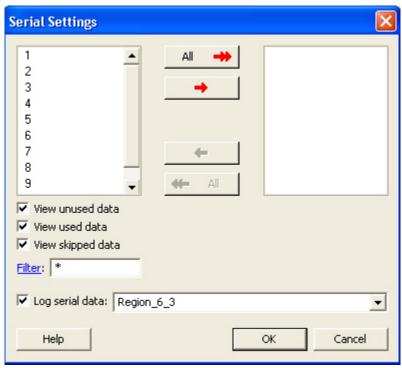

From the Single Device Configuration Window in FlashPro, check the Serialization box and click the Select Serialization Indexes button.

The **Serial Settings** dialog box appears (see figure below).

Figure 25 · Serial Settings Dialog Box

- 10. From the **Serial Settings** dialog box, click **All** to select all the serial data.

- 11. Click **OK**. The **Serialization Indexes** text box updates (see figure below).

Figure 26 · Single STAPL File Configuration Window- Serialization Indexes Update

12. Click the **Program** button to program your device using serialization.

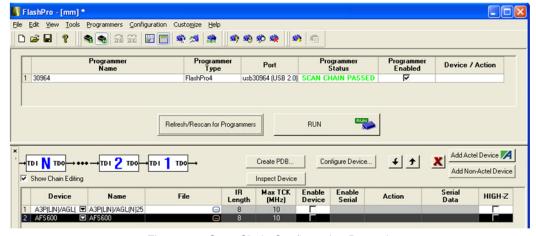

# **Chain Programming Tutorial**

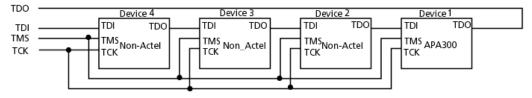

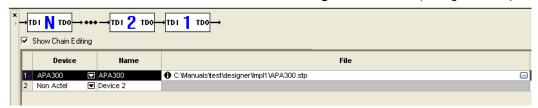

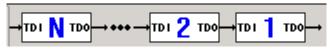

This tutorial demonstrates how to directly program an APA300 device that is part of a heterogeneous JTAG chain. The example in this tutorial uses one APA300 device and three non-Microsemi devices configured as shown in the figure below.

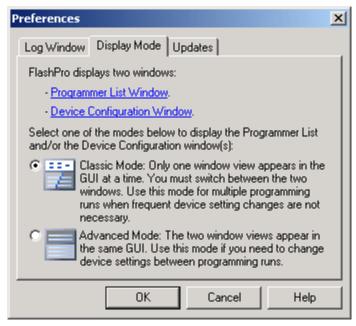

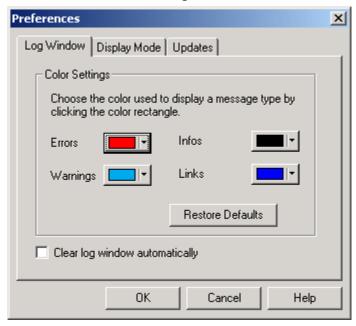

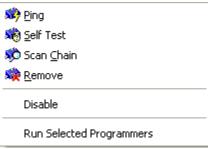

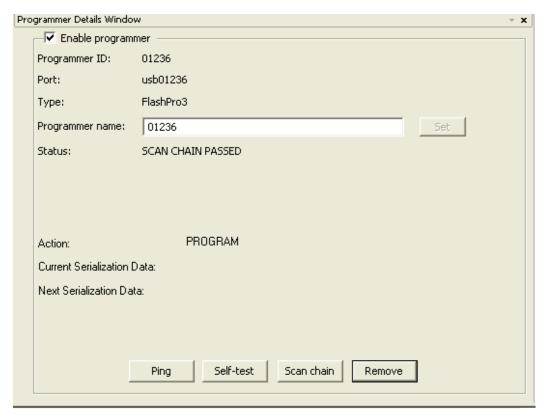

Note: This tutorial is performed in Advanced Mode. You can change your display mode to Advanced Mode from the <u>Preferences</u> dialog box.

Figure 27 · APA Device Tutorial Example

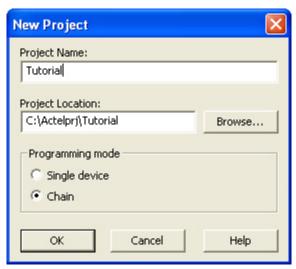

First, create a new project.

#### To create a new project:

- 1. Click the New Project button in FlashPro.

- 2. In the **New Project** dialog box, type Tutorial in the Project Name field.

- Select the Chain option in the Programming Mode.

Figure 28 · New Project Dialog Box

- 4. If necessary, change the default location of your project in the Project Location field.

- 5. Click **OK**. The FlashPro GUI appears (see figure below).

Figure 29 · FlashPro Main GUI

Note: Note: The Programmer List Window updates with your programmer information.

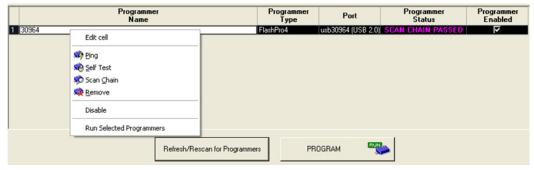

From the Menu bar, click Programmers > Scan Chain (or select the programmer in the Programmer List Window, right-click and choose Scan Chain).

**Scan Chain** shows how the devices are ordered in the chain in the **Log** window (see figure below). In this example, APA300 is the first device and will be programmed first in the chain since it is connected directly to TDO.

```

programmer '30175' : Scan Chain...

programmer '30175' : Found 32 instruction register bits.

programmer '30175' : Checking IDCODEs...

programmer '30175' : Device 1: 11A081CF Mfr: Actel Part: APA300

programmer '30175' : Device 2: Unknown

programmer '30175' : Device 3: Unknown

programmer '30175' : Device 4: Unknown

programmer '30175' : Scan Chain PASSED.

```

Figure 30 · Log Window Scan Chain Order

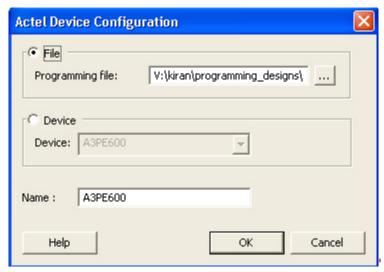

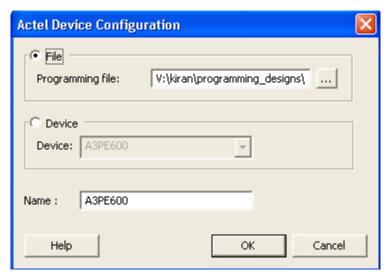

7. From the Chain Configuration window, click either; Add Actel Device or Add Non-Actel Device buttons to add devices to the chain. In this example, click the Add Microsemi Device button because the APA300 is the first device in the chain.

The **Add Microsemi Device** dialog box displays (see figure below).

Figure 31 · Add Microsemi Device Dialog Box

- 8. Select the **File** radio button and click the **Browse** button to find your programming file.

- 9. Select the **Device** radio button, then choose the APA300 device from the **Device** drop-down.

- 10. In the **STAPL File** field, load the APA300.stp file by using the **Browse** button \_\_\_\_\_ to locate the file.

- 11. In the Name field, keep APA300 as the default name.

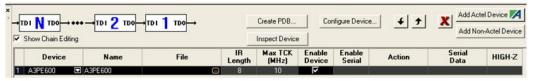

- 12. The APA300 device is added to the Chain Configuration Window (see figure below).

Figure 32 · Chain Configuration Window: Device One

12. Click the **Add Non-Microsemi Device** button to add the non-Microsemi device. The Add Non-Microsemi Device dialog box appears (see figure below). You can load the BSDL file or enter the IR length and Max TCK Frequency of the device. In this tutorial, you will enter the IR length and Max TCK frequency for this device.

Figure 33 · Add Non-Microsemi Device Window

- 14. For this device, enter 8 in the IR length field and keep the Max TCK freq default to 1MHz.

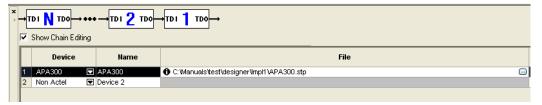

- Name the device, "Device 2" and click **OK**. The second device now appears in the Chain Configuration Window (as shown in the figure below).

Figure 34 · Chain Configuration Window: Device Two

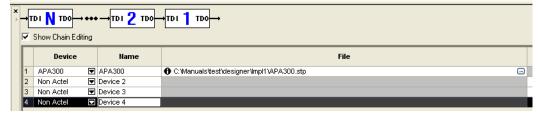

- 16. Repeat step 15 for Device 3 and Device 4.

- 17. Check the **Enable Device** box for the APA300 device. After you add all the devices in the chain, the **Chain Configuration Window** should look like the figure below.

Figure 35 · Chain Configuration Window: All Devices in the Chain

- 18. After you have added all of the devices to the chain in the correct order, click the **Run** button to program the chain.

- 19. When programming is complete, the results are listed in the Log window (see figure below).

```

programmer '30175'

: Scan Chain..

programmer '30175'

Scan Chain PASSED

programmer '30175'

device 'APA300' : Executing action PROGRAM

programmer '30175'

device 'APA300' : SERIAL# = OC1DFA7BB06080

programmer '30175'

device 'APA300' : PROGRAMMING ARRAY

programmer '30175'

device 'APA300'

VERIFYING PROGRAMMED BITS...

programmer '30175' :

device 'APA300' :

VERIFYING NON-PROGRAMMED BITS..

programmer '30175' : device 'APA300' : Finished: Tue Jul 18 18:09:59 2006 (Elapsed time 00:03:00)

programmer '30175'

device 'APA300' : Executing action PROGRAM PASSED.

programmer '30175'

: Chain programming PASSED.

0 - 0 - 0 - 0 - 0 - 0

```

Figure 36 · Programmer List Window: Programming Complete

# **SmartFusion Programming Tutorial**

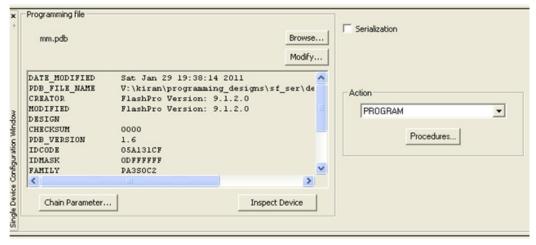

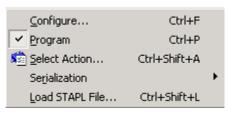

You can program your SmartFusion device without using the Libero SoC by using an EFC or UFC file from standalone SmartDesign, or using an FDB file from standalone Designer.

#### To program a SmartFusion device without using the Libero SoC:

- Start FlashPro and click New Project to create a new project. Specify your Project Name, Project Location and Programming Mode.

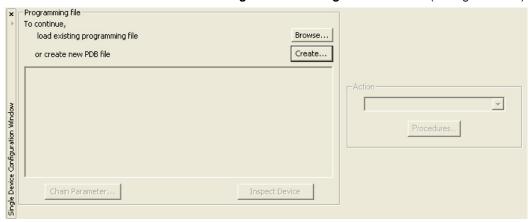

- 2. Click Configure Device.

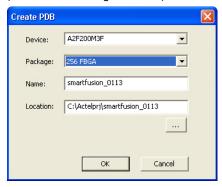

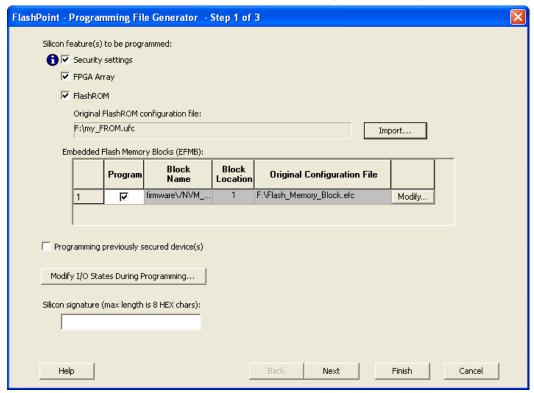

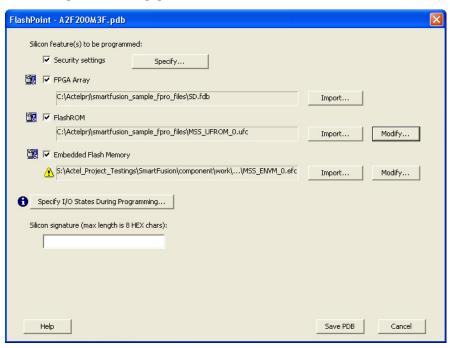

- 3. **Single Mode**: Click the **Create** button to create your new PDB programming file. The create PDB dialog box appears (as shown in the figure below).

Figure 37 · Create PDB Dialog Box

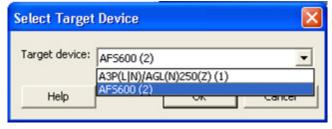

**Chain Mode**: Click **Add Microsemi Device** and choose a SmartFusion device from the drop-down menu. Click the **Create PDB** button in the Chain Configuration Window. The Create PDB dialog box appears.

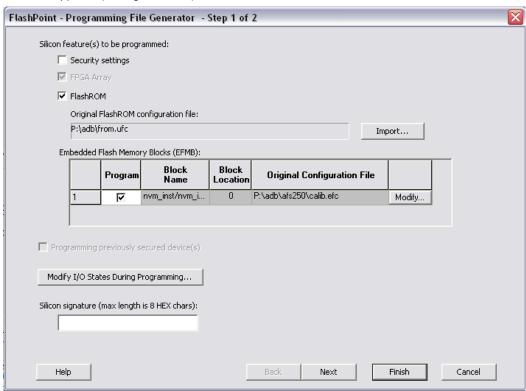

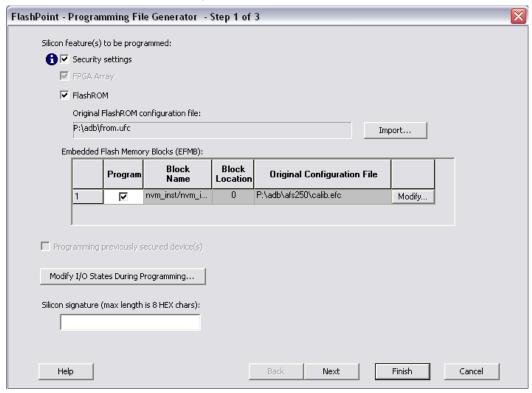

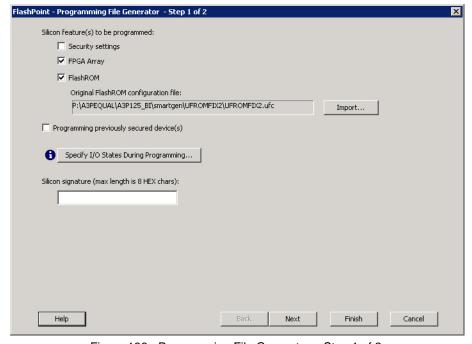

- 4. Specify your PDB parameters. Click **OK** to continue. The <u>FlashPoint SmartFusion Programming File</u> dialog box appears.

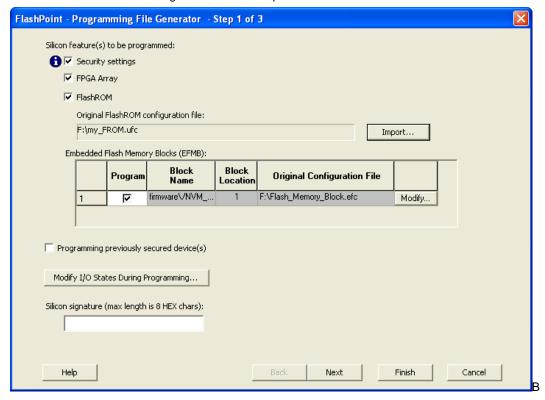

- Specify your <u>security settings</u> and select which silicon features you want to program. Click the <u>Import</u> button for your <u>FPGA Array</u>, <u>FlashROM</u> and <u>Embedded Flash Memory files</u> to add them to your PDB file.

You must have a FDB file to program your FPGA Array, a UFC file to program your FlashROM, and a EFC file to program your Embedded Flash Memory.

Click the **Modify** buttons if you wish to modify your FlashROM or Embedded Flash Memory files before you save your PDB file.

- (Optional) Specify your I/O States During Programming.

- 7. Click Save PDB to save your new PDB file.

If you make changes to your Security, I/O States During Programming, EFC, UFC or FDB file, click **Modify** in FlashPro to open and re-save your PDB with the updated files and settings.

See <u>Reprogramming a Secured Device</u> for information on programming a secured SmartFusion device.

# Modifying Memory Contents and Programming a Device Tutorial

This tutorial provides step-by-step instructions on how to load a Program Database (PDB) file, modify the memory contents, and program the device.

Before you begin this tutorial, you should have a design with an EFMB client in it with a generated programming file for this design. You will first create a new project and title it "tutorial." If FlashPro is launched through Libero SoC, a new project will automatically be created and a PDB file will be loaded, if available.

### Creating a new project

If you are familiar with this feature, follow the basic procedures for <u>creating a new project</u>. However, if you would like step-by-step instructions, see the creating a new project section in the <u>Single STAPL/PDB File</u> Basic Tutorial.

### **Loading and Configuring a PDB File**

Once you have created your project and connected your programmer, you are ready to load your PDB file.

#### To load a PDB file:

- 1. Click the Configure Device button. The Single PDB Configuration window appears in FlashPro.

- 2. Click the **Browse** button to find your PDB file.

- 3. From the Load PDB File dialog box, find your PDB file and click Open.

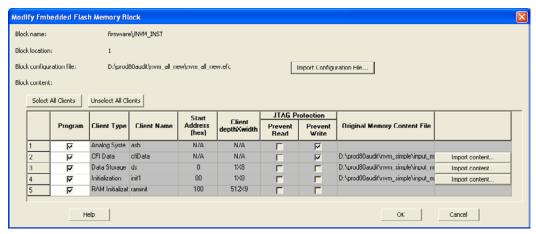

### **Modify Embedded Flash Memory Block Content**

Now, you are ready to modify the Embedded Flash Memory Block content.

#### To modify Embedded Flash Memory Block content:

1. Click the PDB Configuration button to open FlashPoint.

Figure 38 · Program File Generator

- Check the Program box.

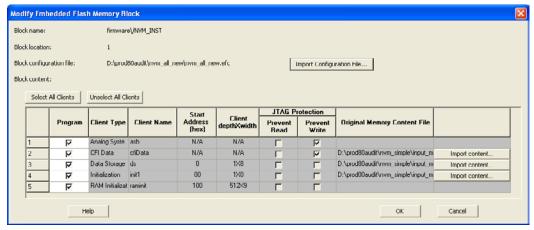

- Click the Modify button to import Embedded Flash Memory Block configuration and memory content file. The Modify Embedded Flash Memory Block dialog box appears

Figure 39 · Modify Embedded Flash Memory Block Content Dialog Box

- 4. Click the Import Configuration File button to import the Embedded Flash Memory Block configuration and memory content from the EFC file. This will populate the client table below. All clients that belong to this block will be selected by default.

- 5. Click the **Import content** button if you want to change the client memory content.

- 6. Click OK.

- 7. Click Finish.

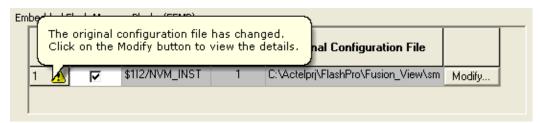

Note: FlashPoint audits original configuration and memory content files and warns you if the files cannot be located or if they have been updated. These files are not required as the last updated configuration and memory content is stored in the PDB.

Figure 40 · Audit Warning

Proceed to program the device. For steps on how to program a device, see the **Programming a device** section of the **Single STAPL/PDB file basic tutorial**.

# Modifying FlashROM Contents and Programming a Device Tutorial

This tutorial provides step-by-step instructions on how to load a Program Database (PDB) file, modify the memory contents, and program the device.

Before you begin this tutorial, you should have a design with an EFMB client in it with a generated programming file for this design. You will first create a new project and title it "tutorial." If FlashPro is launched through the Libero SoC Project Manager, a new project will automatically be created and a PDB file will be loaded, if available.

### Creating a new project

If you are familiar with this feature, follow the basic procedures for <u>creating a new project</u>. However, if you would like step-by-step instructions, see the creating a new project section in the <u>Single STAPL/PDB File Basic Tutorial</u>.

### Loading and Configuring a PDB File

Once you have created your project and connected your programmer, you are ready to load your PDB file.

#### To load a PDB file:

Click the Configure Device button. The Single Device Configuration Window displays in FlashPro (see figure below).

Figure 41 · Single Device Configuration Window

Click the Browse button to find your PDB file. From the Load Programming File dialog box, find your PDB file and click Open.

### **Modify FlashROM Content**

Now you are ready to modify the FlashROM content.

- Click the PDB Configuration button. This opens FlashPoint.

- 2. Select FlashROM under Silicon feature(s) to be programmed (see figure below).

Figure 42 · FlashPoint Programming File Generator

- 3. Click the **Browse** button to select the \*.ufc FlashROM configuration file by and navigating to the configuration file. This file is normally present in the SmartGen subfolder of the Libero SoC project, in a folder with the FlashROM IP block's name.

- 4. Click Next.

- 5. Select the FlashROM pages you want to program (see figure below).

Figure 43 · FlashROM Settings Dialog Box

#### 6. Click Finish.

Proceed to program the device. For steps on how to program a device, see the <u>Programming a device</u> section of the <u>Single STAPL/PDB file basic tutorial</u>.

# **Programming Only Security Settings Tutorial**

This tutorial provides step-by-step instructions on how to program only the security settings into a device. No design or PDB file is needed to follow this tutorial.

First create a new project and name it tutorial. If FlashPro is launched from the Project Manager, a new project will automatically be created and a PDB file will be loaded, if available. For this tutorial you always need to create a new project.

### **Creating a New Project**

If you are familiar with this feature, follow the basic procedures for <u>creating a new project</u>. However, if you would like step-by-step instructions, see the creating a new project section in the <u>Single STAPL/PDB file basic tutorial</u>.

## **Configuring the Security Settings**

Once you have created your project and connected your programmer, you are ready to load your PDB file.

#### To configure the security settings:

Click the Configure Device button. The Single Device Configuration window appears in FlashPro (see figure below).

Figure 44 · Single Device Configuration Window

2. Click Create. This opens the Create PDB dialog box, as shown in the figure below.

Figure 45 · Create PDB Dialog Box

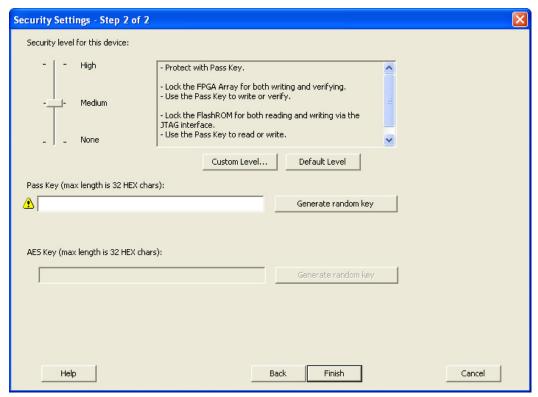

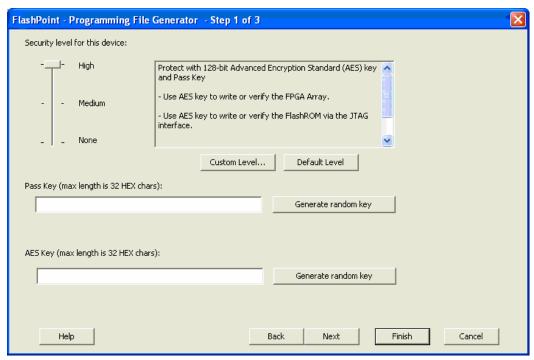

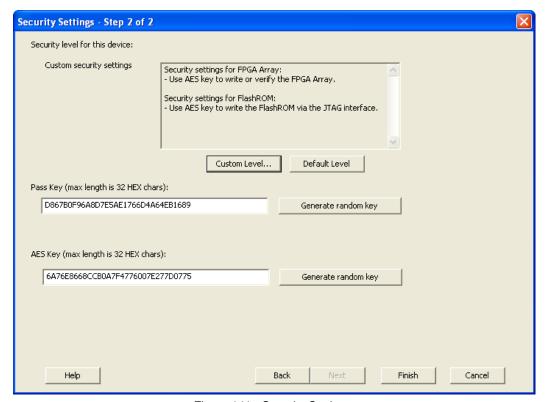

- 3. Select the desired device and package (if available) from the drop down list, and specify the filename and location. Click OK. FlashPoint opens. SmartFusion, IGLOO, ProASIC3 and Fusion family devices support securing the device with a pass key as well as encrypting programming files using an AES key. Flash devices can also be permanently locked, preventing reprogramming.

- 4. Check the Security Settings checkbox to secure the unsecured device.

**Warning**: Make a note of the security keys that you are using. Once a device is secured, it cannot be reprogrammed without those keys.

Figure 46 · Security Settings Dialog Box

#### 5. Click Finish.

Proceed to program the device. For steps on how to program a device, see the <u>Programming a device</u> section of the <u>Single STAPL/PDB file basic tutorial</u>.

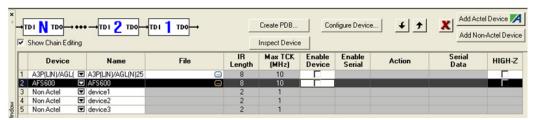

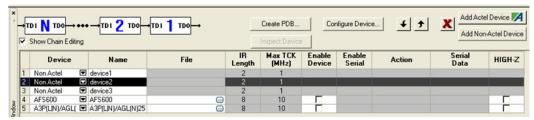

# **Automatic Chain Construction Tutorial**

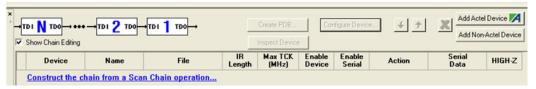

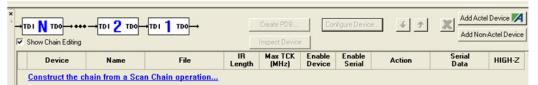

This tutorial demonstrates how to automatically scan a chain of devices and construct the chain within FlashPro. Automatic chain construction saves the effort of manually adding each device to your chain.

The software also scans the chain before constructing it, which reduces the possibilities of having errors in the chain. This feature is fully automated if your chain is composed of only Microsemi devices. If you have non-Microsemi devices in your chain, you can still use the Auto Chain Construction feature. However, you will be required to either manually add the BSDL file or enter the IR length and max TCK for each non-Microsemi device. This tutorial goes through the flow for an Microsemi-only chain first, followed by instructions on adding Non-Microsemi devices to the database.

Note: This tutorial requires that your chain is connected to the computer you are using, via an Microsemi programmer, and that you have suitable programming files to program the devices in your chain.

#### To automatically scan a chain of devices and construct the chain:

- 1. Start a new project in FlashPro. Select **Chain** as the Programming Mode.

- 2. Click the **Configure Chain** button in FlashPro.

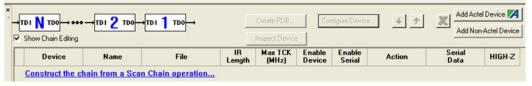

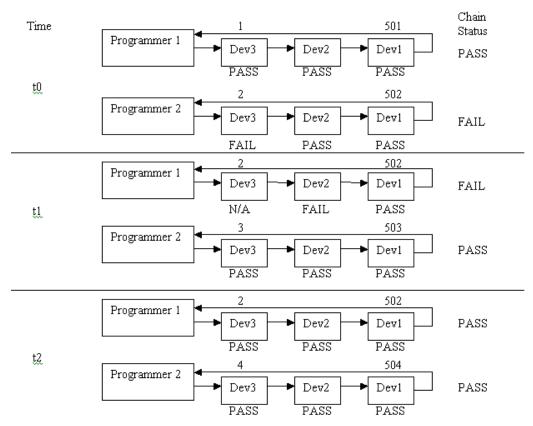

- From the Configuration menu, choose Construct Chain Automatically; or click the Construct the chain from a Scan Chain operation link in the Chain Configuration Window, see below.

Figure 47 · Construct Chain Automatically

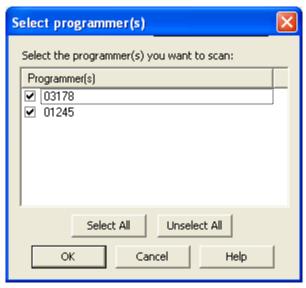

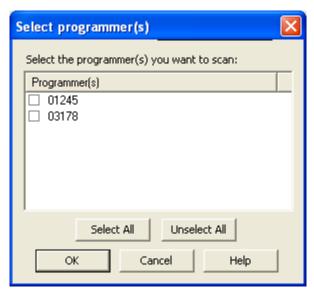

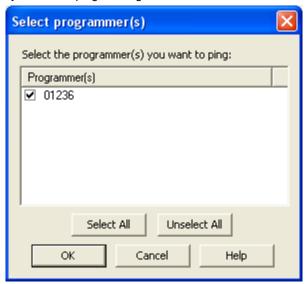

4. A popup appears asking you to select the programmer you would like to use from the ones attached to your computer. Choose the appropriate programmer (as shown in the figure below) and click **OK**.

Figure 48 · Select Programmer Popup

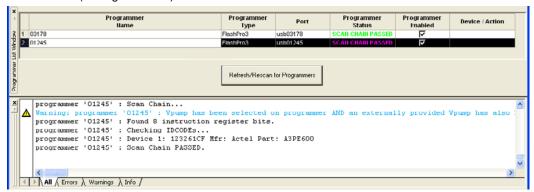

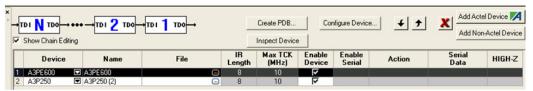

Automatic chain construction starts. The Log window documents the detection and verification of all devices in your chain. The devices are added to the chain in the Chain Configuration Window; see figure below for an example.

Figure 49 · Scan Chain Configuration Passed

In some cases, FlashPro is not able to uniquely identify the device due to shared IDCODEs, and lists all possible devices (ex: AGL030V2/AGL030V5). Once a programming file is loaded for that device, the device field only shows one device, since the programming file will only be targeted to one device.

### **Adding Non-Microsemi Devices to the Chain**

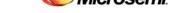

FlashPro recognizes non-Microsemi devices in the chain, but it does not contain any device information, such as IR length or Max TCK. The figure below lists Microsemi devices and non-Microsemi devices in the chain.

Figure 50 · Non-Microsemi Devices in a Chain

You must import the BSDL file into Microsemi's non-Microsemi device database for FlashPro to recognize your non-Microsemi device.

To import the device BSDL into the FlashPro non-Microsemi device database and run the scan chain:

- From the Tools menu, choose Import Settings for Non-Microsemi Devices. This opens the Import

<u>Settings for Non-Microsemi Devices</u> dialog box. This dialog box enables you to import and remove

<u>BSDL files from the database and lists all the device information contained in the BSDL file.</u>

- Click the Import BSDL Files button and navigate to the folder that contains your BSDL files. Select the file and click OK. Once the BSDL is imported into the database, the original BSDL file is no longer audited by FlashPro. If changes are made to the original source BSDL file, it will not affect the BSDL file that has been imported into the non-Microsemi device database.

Remove BSDL files from the database by selecting the file and clicking the **Remove** button.

3. Once you have the appropriate BSDL files loaded to the database, you can construct the chain. To do so, from the Configuration menu, choose Construct Chain Automatically and select the appropriate programmer from the dialog box. FlashPro runs a scan chain, detects the devices in the chain, and associates them with the BSDL files in the database, as shown in the figure below.

Figure 51 · Non-Microsemi Devices in the Chain with Associated BSDL Files

It is possible to add multiple BSDL files to your Non-Microsemi device database that have the same IDCODE. If the BSDL files list the same IR length but different TCK values, FlashPro automatically chooses the file with the lowest TCK value by default and no action is required. If the IR lengths are different you receive an error message asking you to resolve the conflict.

To resolve the issue, click the drop-down arrow adjacent to the device name. This opens the Non-Microsemi Device Configuration dialog box (as shown in the figure below). From here you can choose the BSDL file that you wish to use. Browse to the BSDL file or use the Data to input the IR length and Max TCK Frequency. Once you select your data you can enter a new name or use the default.

Figure 52 · Non-Microsemi Device Configuration Dialog Box

For a tutorial on manually adding both Microsemi and non-Microsemi devices to your chain as well as programming the chain, refer to the <u>Chain Programming Tutorial</u>.

#### See Also

<u>Understanding the Chain Configuration Window</u> Import Settings for Non-Microsemi Devices

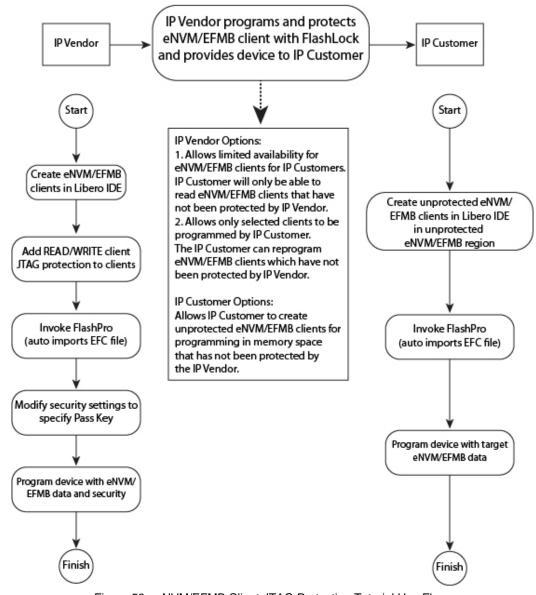

### eNVM/EFMB Client JTAG Protection Use Flow

eNVM/EFMB client JTAG protection enables you to protect specific clients with a User Pass Key while leaving others unprotected.

See the <u>eNVM Client JTAG Protection Tutorial</u> or <u>EFMB Client JTAG Protection Tutorial</u> for step by step instructions.

Figure 53 · eNVM/EFMB Client JTAG Protection Tutorial Use Flow

### eNVM Client JTAG Protection Tutorial - SmartFusion

This tutorial provides step-by-step instructions on how to enable JTAG protection for eNVM clients. The protection can be read, write or both and it is protected with a User Pass Key (FlashLock).

The JTAG protection of eNVM clients enables you to protect specific clients with a User Pass Key while leaving others unprotected.

Before you begin this tutorial, make sure you have already installed the FlashPro software and that you are familiar with its basic features.

JTAG READ/WRITE protection is set when you create your original eNVM in Libero SoC. You cannot change this setting in FlashPro/FlashPoint.

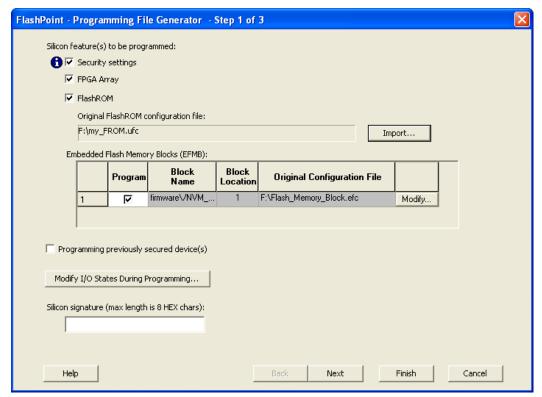

## Importing an EFC (Embedded Flash Configuration) File with Client JTAG protection in a Previously Unsecured PDB

1. Create a client in eNVM configurator with JTAG read and write protect (as shown in the figure below). If the MSS block is generated with an eNVM client with JTAG protection then FlashPro requires that you specify a User Pass Key prior to programming or exporting programming files.

Figure 54 · Generating the EFC File with JTAG Protection

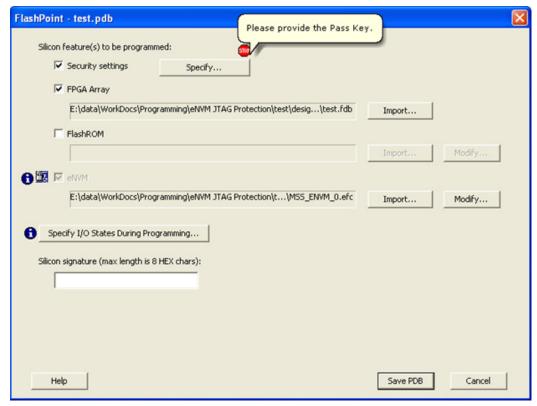

Import the EFC file with JTAG protection in FlashPoint. When the EFC file is imported the Security Settings box is checked automatically, implying that you must set the User Pass Key (as shown in the figure below).

The PDB file cannot be saved without specifying the pass key.

Figure 55 · Importing the EFC File with JTAG Protection

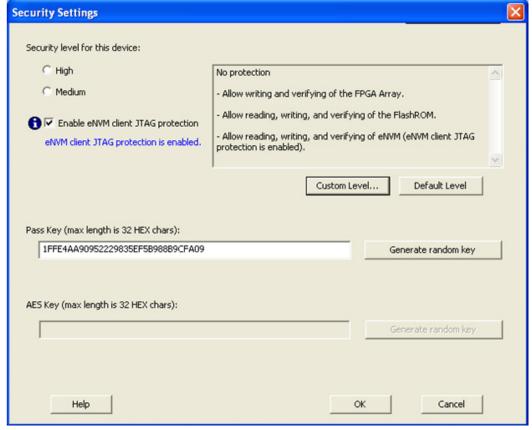

- Click Specify to open the Security Settings dialog box. Notice that Enable eNVM client JTAG

protection box is checked. This indicates that reading, writing, and verifying of other eNVM pages are

allowed but the reading and writing of specific eNVM clients are protected.

- 4. To enforce the eNVM client JTAG protection in the PDB file, enter a **Pass Key** or click **Generate random key** (as shown in the figure below).

Figure 56 · Setting Security

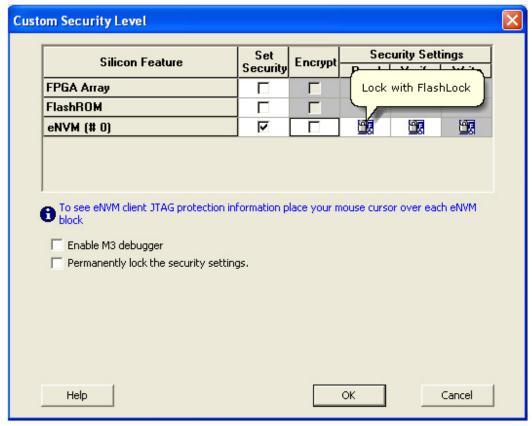

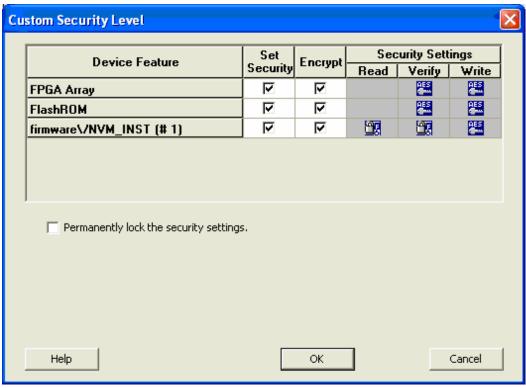

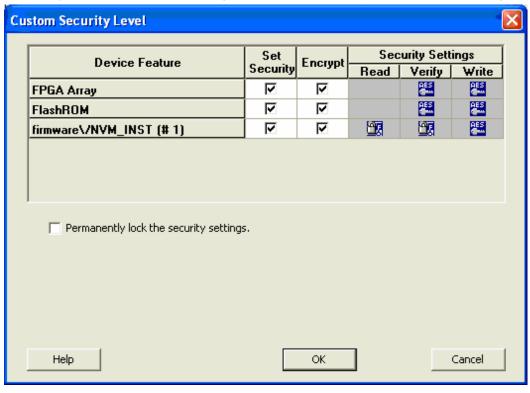

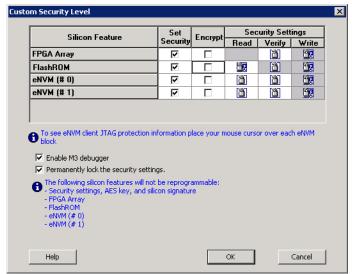

#### **Custom Level Security Settings**

If you select Custom Level security and decide to protect writing of the entire eNVM block, then the eNVM client JTAG protection Write, if enabled, will be overridden by full block protection.

If the Read protection of the eNVM block is left open, then the eNVM client JTAG protection Read will be enabled if a client has a read protection enabled.

If you choose to encrypt the entire eNVM block, then the eNVM client JTAG protection Write will be disabled if enabled, due to enforced encryption. The eNVM client JTAG protection Write, if enabled, will be overridden by full block protection.

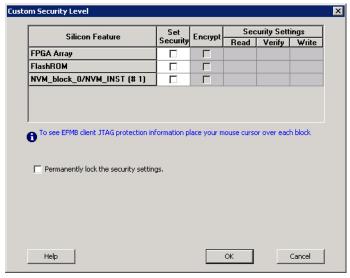

#### To set Custom Level Security:

1. Click Custom Level to open the Custom Security Level dialog box (as shown in the figure below)

Figure 57 · Setting Security for Unprotected eNVM Clients

- Click the Set Security checkbox to secure Read, Write and Verify using Flash Lock. In this mode you can unlock Read and Verify and only protect Write by FlashLock. The eNVM client JTAG read protection will be enabled.

- Click the Encrypt checkbox to secure Write using the AES Key. Read, Verify will be secured by FlashLock in this mode. You must enter the AES key in addition to the Pass Key before saving the PDB file.

### **Setting Standard Security Levels**

There are two types of standard level security: High and Medium. If either of the two is selected the eNVM client JTAG protection is overridden or disabled. You can enforce Read, Write and Verify protection of the entire eNVM block with the Pass Key and/or AES key. JTAG protection of specific pages will not be available.

# Importing EFC (Embedded Flash Configuration) File with Client JTAG Protection in Previously Secured PDB

The secure PDB file exported from FlashPro is called a secured PDB.

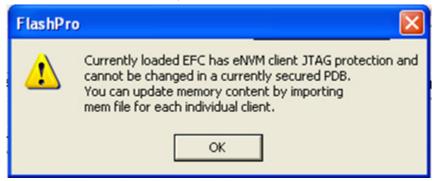

If you import an EFC file that has JTAG protection into a secured PDB file but does not have eNVM clients with JTAG protection enabled then the FlashPro returns an **EFC file has eNVM client JTAG protection** and cannot be loaded error, as shown in the figure below.

Figure 58 · EFC File with JTAG Protection Cannot be Imported into a Secured PDB Error Message You can import any EFC file that does not have JTAG protection.

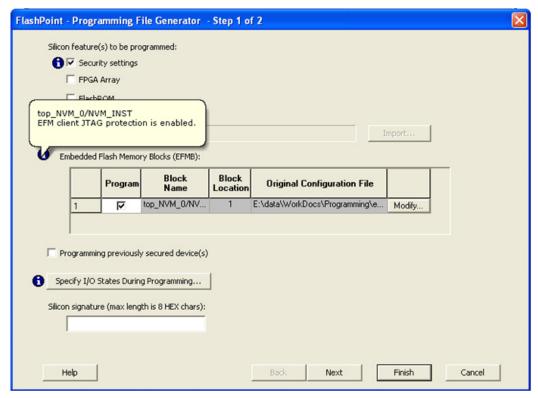

You cannot import a new EFC with JTAG protection into a secured PDB that already has an EFC file imported with eNVM client JTAG protection. You can update the memory content by importing MEM files for the specific clients (as shown in the figure below).

Figure 59 · New EFC File Cannot Overwrite Existing eNVM Client JTAG Protection Error Message

### EFMB Client JTAG Protection Tutorial - Fusion

This tutorial provides step-by-step instructions on how to enable JTAG protection for eNVM clients. The protection can be read, write or both and it is protected with a User Pass Key (FlashLock).

The JTAG protection of EFMB clients enables you to protect specific clients with a User Pass Key while leaving others unprotected.

One example use is IP customization. This enables an IP vendor to allow limited visibility to EFMB clients for IP customers. The IP vendor can protect specific clients and leave other clients unprotected for modification by IP customers. See the <a href="https://example.com/enables/enables/by-nc-tail/">enables an IP vendor to allow limited visibility to EFMB clients for IP customers. The IP vendor can protect specific clients and leave other clients unprotected for modification by IP customers. See the <a href="https://example.com/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enables/enabl

Before you begin this tutorial, make sure you have already installed the FlashPro and/or Designer software and that you are familiar with its basic features.

JTAG READ/WRITE protection is set when you create your original EFMB in Libero SoC. You cannot change this setting in Designer/FlashPoint or FlashPro/FlashPoint.

### **EFMB Client JTAG Protection in Designer/FlashPoint**

If the ADB file has an EFM (Embedded Flash Memory) block with page/client JTAG protection enabled, the EFC file appears in the FlashPoint window when you click the Programming File button in Designer.

A message indicating JTAG protection is enabled appears in the Embedded Flash Memory Block (EFMB) tooltip, as shown in the figure below.

Figure 60 · EFMB Client JTAG Protection

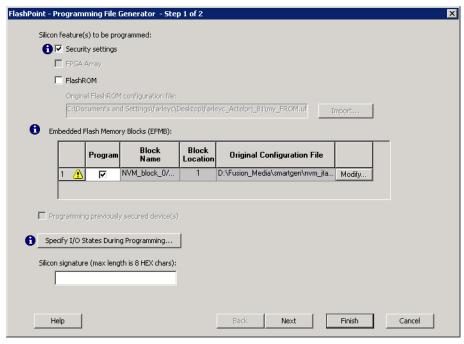

#### To set EFMB Client JTAG Protection:

- Check the Security Settings or Programming previously secured devices checkbox and click Next. The Security Settings dialog box opens.

- Specify the appropriate security settings.

If the EFM block is generated with an EFMB client with JTAG protection then FlashPro requires that you specify a User Pass Key prior to programming or exporting programming files.

Import the EFC file with JTAG protection in the FlashPoint dialog box. When the EFC file is imported

the Security Settings box is checked automatically, implying that you must set the User Pass Key (as

shown in the figure below).

The PDB file cannot be saved without specifying the pass key.

Figure 61 · Importing the EFC File with JTAG Protection

- 4. Click **Next** to open the Security Settings dialog box. Notice that the **Enable EFMB client JTAG protection** box is checked. This indicates that reading, writing, and verifying of other EFMB pages are allowed but the reading and writing of specific EFMB clients are protected.

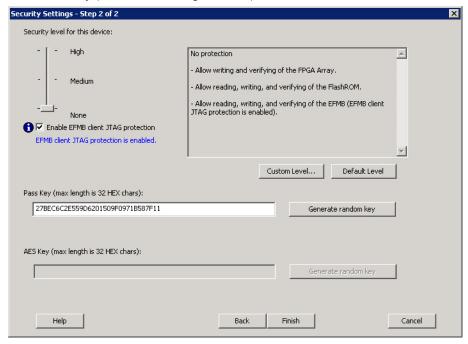

- To enforce the EFMB client JTAG protection in the PDB file, enter a Pass Key or click Generate random key (as shown in the figure below).

Figure 62 · Setting Security

#### **Custom Level Security Settings**

If you select Custom Level security and decide to protect writing of the entire EFMB, then the EFMB client JTAG protection Write, if enabled, will be overridden by full block protection.

If the Read protection of the EFMB is left open, then the EFMB client JTAG protection Read will be enabled if a client has Read protection enabled.

If you choose to encrypt the entire EFMB, then the EFMB client JTAG protection Write will be disabled due to enforced encryption. The EFMB client JTAG protection Write, if enabled, will be overridden by full block protection.

#### To set Custom Level Security:

1. Click Custom Level to open the Custom Security Level dialog box (as shown in the figure below)

Figure 63 · Setting Security for Unprotected eNVM Clients

- Click the Set Security checkbox to secure Read, Write and Verify using Flash Lock. In this mode you

can unlock Read and Verify and only protect Write by FlashLock. The EFMB client JTAG read

protection will be enabled.

- Click the Encrypt checkbox to secure Write using the AES Key. Read, Verify will be secured by FlashLock in this mode. You must enter the AES Key in addition to the Pass Key before saving the PDB file.

#### Setting Standard Security Levels

There are two types of standard level security: High and Medium. If either of the two is selected the EFMB client JTAG protection is overridden or disabled. You can enforce Read, Write and Verify protection of the entire EFMB with the Pass Key and/or AES key. JTAG protection of specific pages will not be available.

#### **EFMB client JTAG Protection via FlashPro/FlashPoint**

If the PDB file was created with the EFMB client and JTAG protection is enabled you can click Modify in FlashPro to change the settings.

### Fusion Calibration Backup and Recovery Tutorial

This tutorial provides step-by-step instructions on how to backup and recover default calibration data on a Fusion device. It assumes that you have created a new project, connected your programmer, and loaded a Fusion PDB/STAPL file created in Designer v8.4 or above.

If you would like step-by-step instructions on how to create a new project, see the Creating a New Project section in the FlashPro Single STAPL Basic Tutorial..

If you would like step-by-step instructions on loading a programming file, see the Loading and Configuring a Programming File section in the <u>FlashPro Single STAPL Basic Tutorial</u>.

Note: This feature is only supported in STAPL and PDB programming files.

### **Backing Up Default Fusion Calibration Data**

A backup copy of the Fusion calibration data is created once after ANY programming ACTION, except READ\_IDCODE, is executed. The copy will be stored in the spare pages of eNVM. The FlashPro Log window shows that a backup copy of the calibration data has been created (as shown in the figure below).

```

programmer '07898' : Scan Chain...

programmer '07898' : Scan Chain PASSED.

programmer '07898' : Executing action PROGRAM

programmer '07898' : Checking for Backup Calibration Data...

programmer '07898' : Reading Master Calibration Data...

programmer '07898' : Writing Calibration Backup Copy

programmer '07898' : Erase ...

programmer '07898' : Completed erase

programmer '07898' : Programming FPGA Array

```

Figure 64 · FlashPro Log Window

### **Recovering Default Fusion Calibration Data**

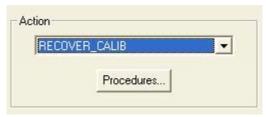

- 1. Load the PDB/STAPL file created in Designer v8.4 or above.

- In the FlashPro Configuration window, click Advanced and select RECOVER\_CALIB (as shown in the figure below).

Figure 65 · RECOVER CALIB

Click Run to restore the original Fusion calibration data. The Log window shows the data is restored (as shown in the figure below).

```

programmer '07898' : Scan Chain...

programmer '07898' : Scan Chain PASSED.

programmer '07898' : Executing action RECOVER_CALIB

programmer '07898' : Checking for Backup Calibration Data...

programmer '07898' : Reading Master Calibration Data...

programmer '07898' : Writing Calibration Backup Copy

programmer '07898' : Checking for Backup Calibration Data...

programmer '07898' : Restoring Master Calibration Data...

```

Figure 66 · Restoring Original Calibration Data

Note: The Calibration data can only be restored after a backup has been made.

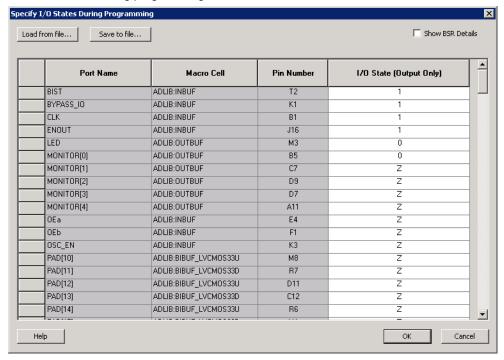

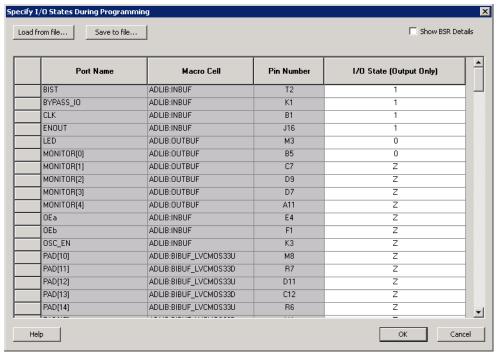

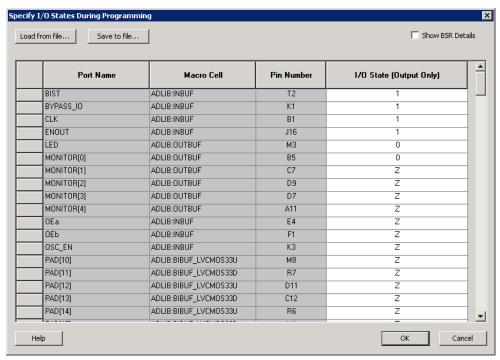

### Specify I/O States During Programming Tutorial

This tutorial explains how to modify the I/O states during programming within FlashPro for used and unused I/Os. It also explains how to modify the Boundary Scan Registers (BSRs) for each I/O to allow for more detailed customization of the I/O states during programming. Finally, it shows how to save and load these settings with a file.

Note: This tutorial requires a design with a valid \*.pdb file associated with it. If you launch FlashPro from a Libero SoC project, a FlashPro project is created automatically and the PDB file loaded. Otherwise, you can start a new FlashPro project and load a PDB file; refer to <a href="Single STAPL/PDB file basic tutorial">Single STAPL/PDB file basic tutorial</a> for more information.

You can also modify the individual Boundary Scan Registers; see the <u>Modify Boundary Scan Registers</u> section for more information.

#### To modify the state of an I/O during programming:

- Once your PDB is successfully loaded, from the Configuration menu, choose PDB Configuration.

This brings up FlashPoint . FlashPoint is the tool that allows you to modify the PDB programming file

from within FlashPro.

- In FlashPoint, click the Specify I/O States During Programming button. The Specify I/O States

During Programming dialog box appears (as shown below). This dialog box enables you to modify the

I/O states during programming for all used and unused I/Os.

Figure 67 · I/O States During Programming Window

The default view displays a grid with 4 columns: Port Name, Macro Cell, Pin Number, and I/O State (Output Only). Port Name lists the port associated with each of theses pins, if the pin is not used in the design, the Port Name for this pin reads Unused. The Pin Number column contains a list of all the pins for the package associated with the design open in FlashPro.The Macro Cell column contains the Microsemi macro associated with each pin, as with Port Names, if the pin is not used, the Macro Cell for this pin reads Unused. The I/O State column is the only column editable in FlashPro.

3. Select an I/O State from the drop-down menu for each I/O you want to modify.

Please refer to <u>Specifying I/O States During Programming</u> for information on sorting and selecting multiple entries in the grid.

4. Click **Save** in the Specify I/O States During Programming window, then **Finish** in FlashPoint to return to FlashPro. The PDB is updated with your new settings.

Congratulations, you have successfully modified the I/O states that will be held during programming.

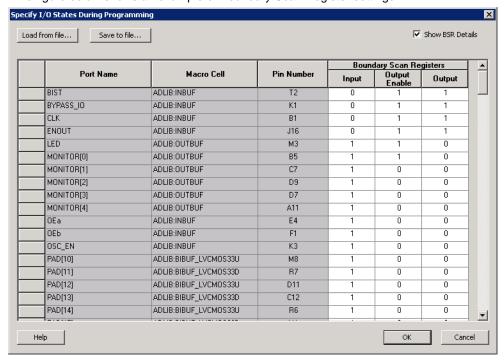

### **Modifying Boundary Scan Registers**

Each I/O in your device is comprised of an Input, Output and Output Enable Boundary Scan Register (BSR) cell.

The BSR cells enable you to define I/O states during programming and control the individual states for each Input, Output, and Output Enable register.

Specify I/O States During Programming Tutorial

#### To modify the individual Boundary Scan Registers of an I/O in your device:

- Select the Show BSR Details checkbox in the Specify I/O States During Programming window.

This replaces the I/O State (Output Only) column with a Boundary Scan Registers column that is split into Input, Output Enable and Output.

- 2. Modify each of the registers for any I/O to set your custom options. See the <u>Specifying I/O States</u> <u>During Programming I/O States and BSR Details help topic</u> for an explanation of the individual BSR settings.

- 3. (Optional) Uncheck the Show BSR Details checkbox to return to the default view.

Note: Note: Updated I/Os with non-default settings are displayed as *User-Defined BSR* in the default view.

Click OK and complete programming to save your updated settings to the ADB and programming files.

### Saving and Loading I/O State Settings

Click Save to File to save your changes. This enables you to save your custom I/O settings in an IOS file. Click Load from File to load a previously saved \*.ios file.

You must click OK and complete programming to save your updated settings to the ADB and programming files.

#### See Also

<u>Specifying I/O States During Programming</u>

Specifying I/O States During Programming - I/O States and BSR Details

### **Advanced Tutorials**

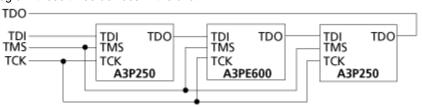

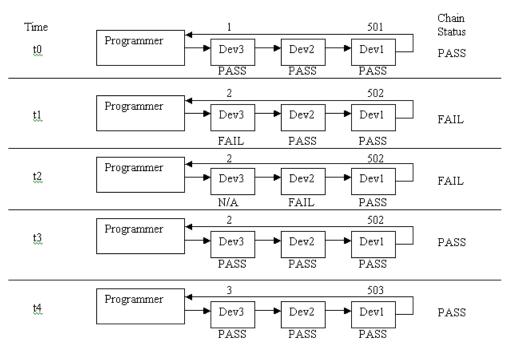

### Multiple Device Chain Programming

This tutorial provides step-by-step instructions on how to program multiple Microsemi devices in a chain. You should already be familiar with the basic features of the FlashPro software.

Note: This tutorial does not provide software installation instructions. Please have FlashPro already installed before you begin.

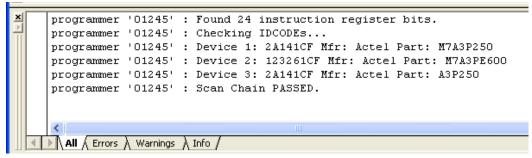

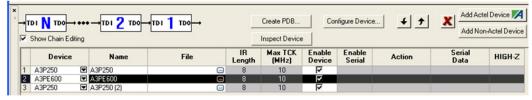

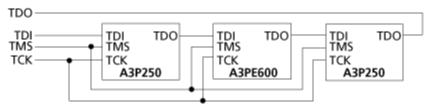

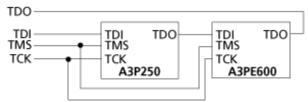

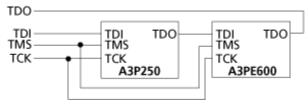

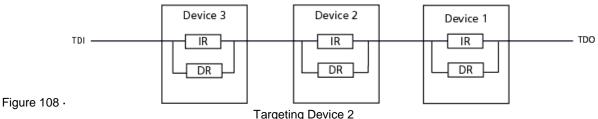

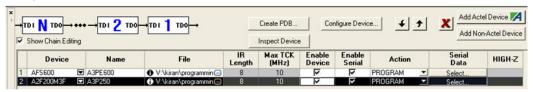

In the figure below, there are three devices in a chain (two A3P250 and one A3PE600). In this section, we will program these three devices in the chain.

Figure 68 · APA Device Tutorial Example

First you need to create a project.

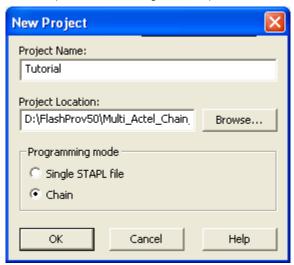

#### To create a new project:

- Click the New Project button in FlashPro.

- 2. From the **New Project** dialog box, type "Tutorial" in the Project Name field.

- 3. Check the Chain box (see figure below).

Figure 69 · New Project Dialog Box

- 4. If necessary, change the default location of your project in the **Project Location** field.

- 5. Click **OK**. The FlashPro main window appears.

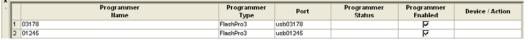

Note: Note: The Programmer List window updates with your programmers information.

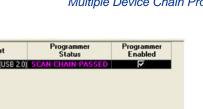

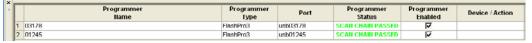

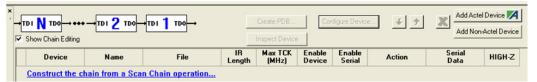

From the Programmers menu, choose Scan Chain (or select the programmer in the Programmer List window, right-click, then choose Scan Chain) (see figure below).

Figure 70 · Select Programmer Window

Scan Chain shows how the devices are ordered in the chain in the log window (see figure below). In this case, A3P250 is the first device that will be programmed in the chain since it is connected directly to TDO.

Figure 71 · Scan Chain Order in the Log Window

7. Click the Configure Chain button. The Chain Configuration window displays (see figure below).

Figure 72 · Chain Configuration Window

In the Chain Configuration window, click the Add Device button to add devices to the chain. The Add Microsemi Device dialog box appears (as shown in the figure below).

Figure 73 · Add Microsemi Device Dialog Box

Choose the "A3P250" device from the **Device** drop-down.

- 10. In the STAPL file field, use the Browse button to locate the A3P250.stp file.

- In the Name field, leave A3P250 as default. The A3P250 device is added into the Chain Configuration window (see figure below).

Figure 74 · Device One Chain Configuration Window

- 12. Repeat the same process for A3PE600 and the other A3P250 respectively.

- After you have finished adding all of the devices in the chain, the Chain Configuration window updates.

Figure 75 · Chain Configuration Window: All Devices in the Chain

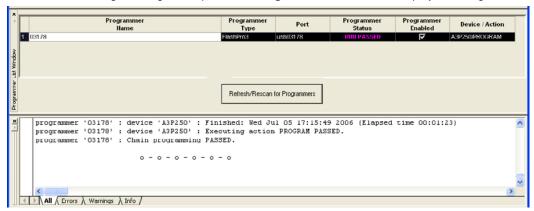

- 14. Once all the devices have been added to the chain in the correct order, click the Run button to program the chain.

- 15. When Programming is complete, the Programmer List window displays. See figure below.

Figure 76 · Programmer List Window Done

Congratulations! You have just completed the FlashPro Multiple Microsemi Device Chain Programming tutorial.

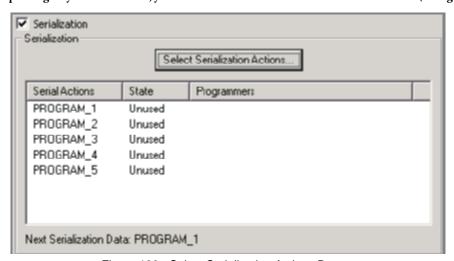

### Multiple Device Serialization Chain Programming

This tutorial provides step-by-step instructions on how to program multiple Microsemi devices with serialization. Before you begin this tutorial, you should already be familiar with the basic features of the FlashPro software.

Note: This tutorial does not provide software installation instructions. Please have FlashPro already installed before you begin.

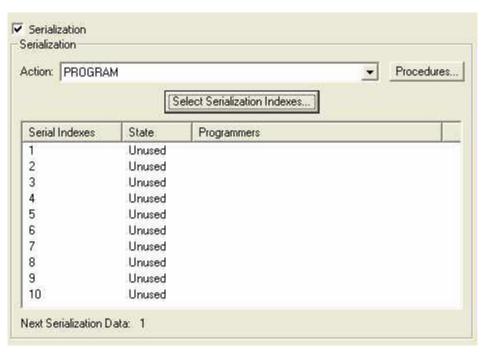

In this tutorial you will program two devices in a chain (one device is A3P250 and the other is A3PE600). The STAPL file for the first A3P250 device contains 10 serialization data. See figure below.

Figure 77 · APA Device Tutorial Example

First you need to create a project.

#### To create a new project:

- 1. Click the New Project button in FlashPro.

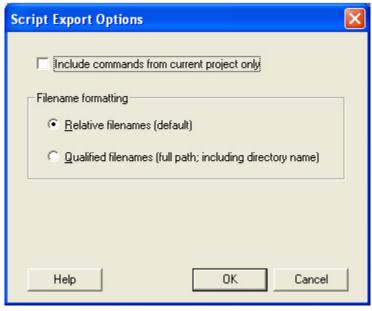

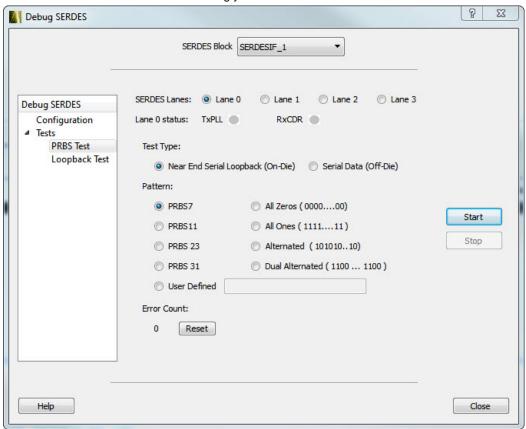

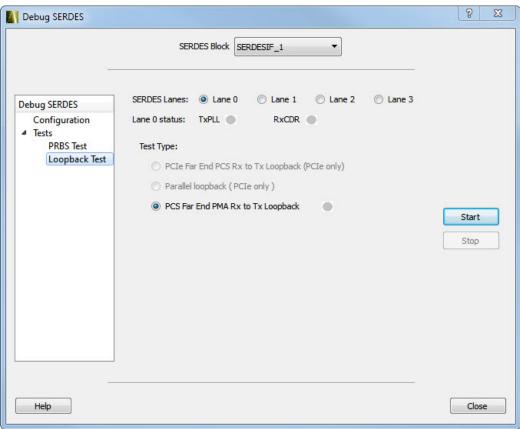

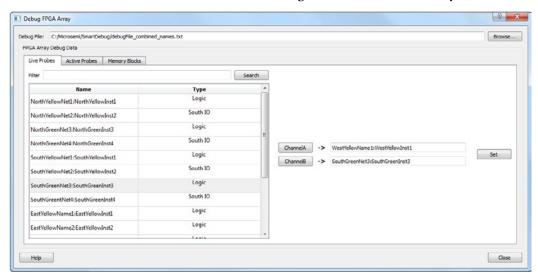

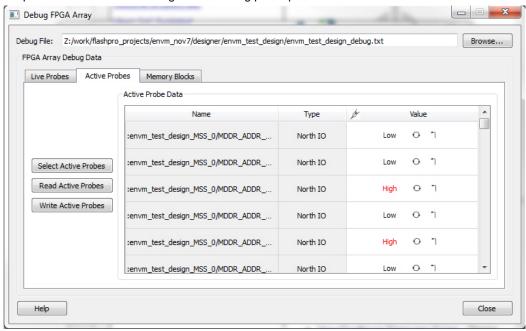

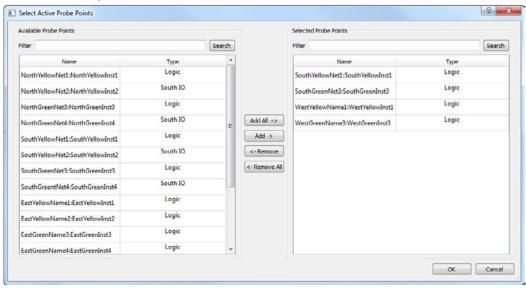

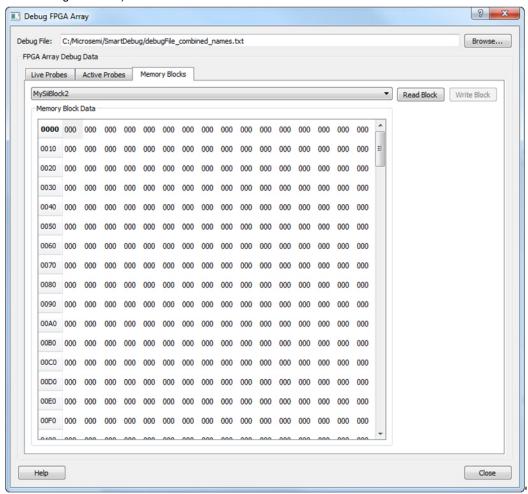

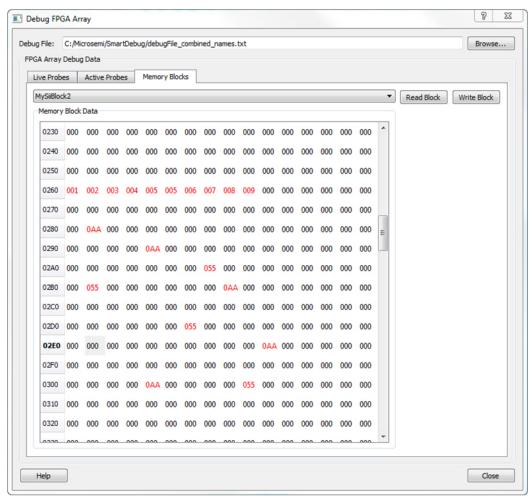

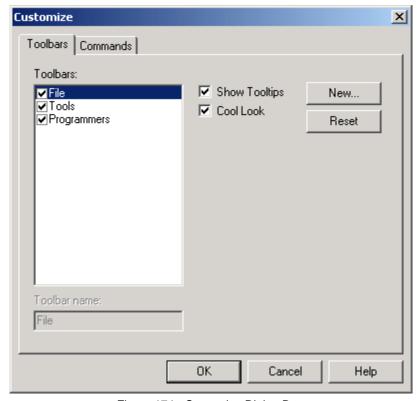

- 2. From the New Project dialog box, type "Tutorial" in the Project Name field.