# Application Manual

Real Time Clock Module

**RX-4035SA/LC**

#### **NOTICE**

- This material is subject to change without notice.

- Any part of this material may not be reproduced or duplicated in any form or any means without the written permission of Seiko Epson.

- The information about applied circuitry, software, usage, etc. written in this material is intended for reference only. Seiko Epson does not assume any liability for the occurrence of infringing on any patent or copyright of a third party. This material does not authorize the licensing for any patent or intellectual copyrights.

- When exporting the products or technology described in this material, you should comply with the

applicable export control laws and regulations and follow the procedures required by such laws and

regulations.

- You are requested not to use the products (and any technical information furnished, if any) for the

development and/or manufacture of weapon of mass destruction or for other military purposes. You

are also requested that you would not make the products available to any third party who may use the

products for such prohibited purposes.

- These products are intended for general use in electronic equipment. When using them in specific

applications that require extremely high reliability, such as the applications stated below, you must

obtain permission from Seiko Epson in advance.

- / Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and related (automobiles, aircraft, trains, vessels, etc.) / Medical instruments to sustain life / Submarine transmitters / Power stations and related / Fire work equipment and security equipment / traffic control equipment / and others requiring equivalent reliability.

- All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.

# Contents

| 1. | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

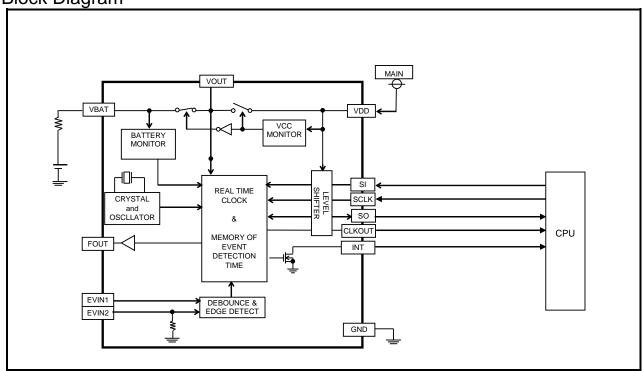

| 2. | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                |

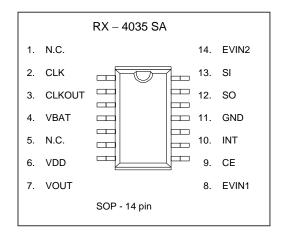

| 3. | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                |

| 4. | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                |

| 5. | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                |

| 6. | Frequency Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                |

| 7. | Electrical Characteristics  7.1. DC Electrical Characteristics.  7.2. AC Electrical Characteristics(1)  7.3. AC Electrical Characteristics(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4<br>5                           |

| 8. | Usage 8.1 Usage of automatic battery switch-over circuit 8.2 Timing chart of VDD, VBAT and VOUT 8.3 Examples of battery connections 8.4 Note of battery switch-over circuit                                                                                                                                                                                                                                                                                                                                                                                                                    | 7<br>8<br>9                      |

| 9. | Functional descriptions.  9.1. Overview of Functions.  9.2. Register table.  9.3 Time stamp functions.  9.3.1 EDFG bit.  9.3.2 Time stamp registers. (BANK=1,address 0-6h)  9.3.3 EDCH1,EDCH2 Indication bit of event input terminal.  9.3.4EDFG bit of event detection function.  9.3.5 Event detection timing chart.  9.5. Periodic Interrupt Function.  9.6. Alarm Interrupt Function.  9.7. The various detection Functions.  10.1. Data transfer method.  10.2. Write methods for data transfer.  10.3. Read methods for data transfer.  10.4. Caution points on read/write of time data. | 10 19 19 19 19 19 20 24 25 31 33 |

| 11 | . External Connection Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                               |

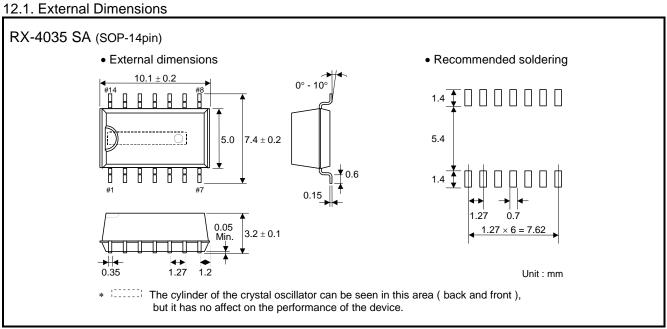

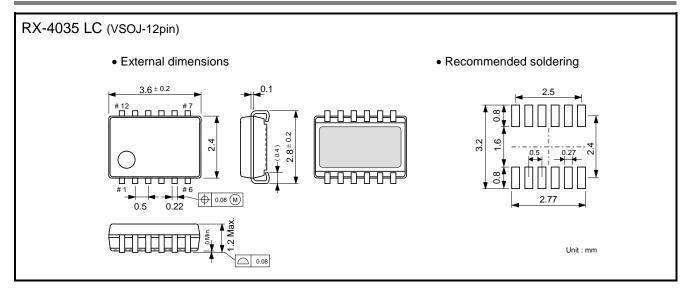

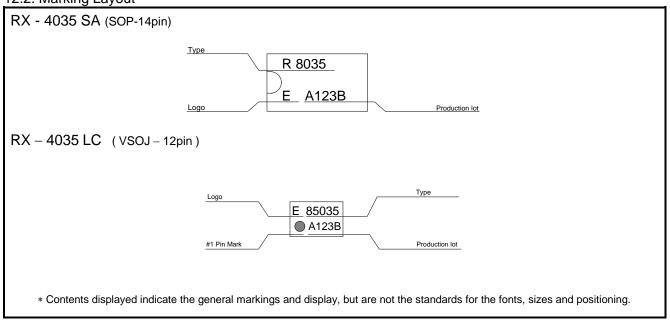

| 12 | 2. External Dimensions / Marking Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                               |

| 13 | 3. Reference Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                               |

|    | Application notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                               |

#### SPI Interface Real-time Clock Module

# RX - 4035 SA/LC

#### 1. Overview

RX-4035 is an SPI interface real-time clock which includes a 32.768-kHz quartz oscillator that has been adjusted for high precision  $\pm$  5 PPM at  $\pm$ 25°C.

This module provides time-stamp function and automatic battery switch-over circuit with low currents backup. And provides six types of interrupts, dual alarm function, oscillation stop detection, and power supply voltage monitoring.

Since the internal oscillation circuit is driven by regulated voltage, 32.768-kHz precision is stable and free of voltage fluctuation effects.

RX-4035 is most suitable for power reduction, resource expansion of CPU, elimination of parts, improvement of tamper performance of a system in all electrical equipment.

#### 1.2. Features

- Built-in 32.768 kHz crystal unit : Frequency adjusted for high accuracy (  $\pm$  5 × 10<sup>-6</sup> at 25°C ).

- Available automatic battery backup switch-over function with RESET output.

- When internal power supply was switched from VCC to battery, I2C-interface is inhibited, and RTC data are protected automatically.

- · Available time-stamp function and interrupt out to CPU by trigger input from two event input ports.

- Time-stamp function is available in supply from VDD or VBAT.

- Includes time (H/M/S) and calendar (YR/MO/WEEK/DATE/DAY) counter functions (BCD code)

- Selectable 12-hour mode or 24-hour clock mode.

- Auto calculation of leap years until 2099. (2100 is not leap year.)

- Dual alarm functions (Alarm\_Wk: Day of week, Hour, Min. Alarm\_Mo: Month, Day, Hour, Min)

- Oscillation stop detection function (used to determine reliability of internal data)

- Battery voltage monitoring function.

- Periodic interrupt function (Rate: Monthly, Hourly, every minute, every second, 0.5sec, OFF.)

- Built-in clock precision control logic

- 32768Hz output. C-MOS

- Supports 4wire SPI-Bus (1.25MHz)

- Wide clock (retention) voltage range: 0.7 V to 5.5 V

- Low current consumption: 350nA 3.0 V (Typ.). 4035SA

#### 2.Block Diagram

# 3. Pin Descriptions

### 3.1. Pin Layout

#### 3.2. Pin Functions

| Signal name | 1/0 | Function                                                                                                                                                                                                                                                          |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVIN1       | I   | Event input terminal 1 for timestamp request. Built in de-bounce circuit.  There is no built in resistor. A High level signal is a detection event.                                                                                                               |

| EVIN2       | I   | Event input terminal 1 for timestamp request. Built in de-bounce circuit and pull-down resistor. A High level signal is a detection event.                                                                                                                        |

| CE          | I   | The CE pin is used for interfacing with the CPU. Should be held high to allow access to the CPU. Incorporates a pull-down resistor. Should be held low or open when the CPU is powered off. Allows a maximum input voltage of 5.5 V regardless of supply voltage. |

| CLK         | I   | The CLK pin is used to input clock pulses synchronizing the input and output of data to and from the SI and SO pins. Allows a maximum input voltage of 5.5 Vv regardless of supply voltage.                                                                       |

| SI          | I   | The SI pin is used to input data intended for writing in synchronization with the CLK pin. CMOS input. Allows a maximum input voltage of 5.5 V regardless of supply voltage.                                                                                      |

| SO          | 0   | The SO pin is used to output data intended for reading in synchronization with the CLK pin.CMOS output.                                                                                                                                                           |

| CLKOUT      | 0   | When RTC works in a VCC power source, 32768Hz is outputted always. C-MOS output type. When RTC works in a BAT power source, output is inhibited and it is shifted to Hi-Z state.                                                                                  |

| /INT        | 0   | Outputs Alarm_Mo, Alarm_Wk, event detection interrupts and periodic interrupts.  N-ch open drain type.                                                                                                                                                            |

| VDD         | I   | Input for main positive power supply.                                                                                                                                                                                                                             |

| VBAT        | I   | Connect a primary battery for backup. Normally, power is supplied from VCC to the IC. If VCC level is equal or less than -VDET1, power is supplied from this pin.                                                                                                 |

| VOUT        | 0   | Output of internal power source for outside devices.  And the secondary battery can be connected.  Be sure to connect a bypass capacitor rated at least 0.1 µF between VDD and GND.                                                                               |

| GND         | _   | For ground.                                                                                                                                                                                                                                                       |

| N.C.        | _   | Never connect. Keep open.                                                                                                                                                                                                                                         |

Note: Be sure to connect a bypass capacitor rated at least 0.1  $\mu F$  between VCC, VDD and GND.

# 4. Absolute Maximum Ratings

GND = 0 V

| Item                  | Symbol          | Condition             | Rating             | Unit |

|-----------------------|-----------------|-----------------------|--------------------|------|

| Supply voltage        | VDD             | VDD                   | -0.3 to +6.5       | V    |

| capping remage        | VBAT            | VBAT                  | 0.0                |      |

| Input voltage         | Vı              | CLK, SI, EVIN1,EVIN2  | GND-0.3 to +6.5    | V    |

| Output voltage        | Vo1             | SO, /INT              | GND-0.3 to +6.5    | V    |

| Output voltage        | Vo <sub>2</sub> | SO CLKOUT VOUT        | GND-0.3 to VDD+0.3 | V    |

| Output current        | lont            | VOUT                  | 20                 | mA   |

| Power Dissipation     | Pp              | Ta = 25°C             | 300                | mW   |

| Operating Temperature | Торт            |                       | -40 85             | °C   |

| Storage temperature   | Tstg            | Not a packaged state. | −55 to +125        | °C   |

# 5. Recommended Operating Conditions

GND = 0 V

| Item                                   | Symbol  | Condition | Min. | Тур. | Max. | Unit |

|----------------------------------------|---------|-----------|------|------|------|------|

| Operating supply voltage               | VACCESS | VDD       | VD2B |      | 5.5  | V    |

| Clock supply voltage                   | Vclk    | VBAT      | 1.00 |      | 5.5  | V    |

| Detection voltage of oscillation stop. | Vxstp   | XSTP = 1  |      | 0.6  | 1.00 | V    |

| Pull-up Voltage                        | VPUP    | /INT      |      |      | 5.5  | V    |

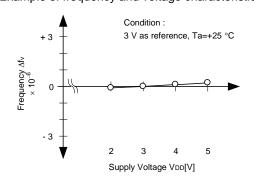

# 6. Frequency Characteristics

GND = 0 V

| Item                                                               | Symbol | Condition                                                      | Rating             | Unit                      |

|--------------------------------------------------------------------|--------|----------------------------------------------------------------|--------------------|---------------------------|

| Frequency precision $\Delta f/f$ $Ta = +25^{\circ}C$ $VDD = 3.0 V$ |        | AA; $5 \pm 5$ (*1)<br>AC; $0 \pm 5$ (*1)<br>B; $5 \pm 23$ (*1) | × 10 <sup>-6</sup> |                           |

| Frequency/voltage characteristics                                  | f/V    | Ta = +25°C<br>VDD = 2 V to 5 V                                 | ± 1 Max.           | × 10 <sup>-6</sup> / V    |

| Frequency/temperature characteristics                              | Тор    | Ta = $-20$ °C to +70 °C,<br>VDD = 3.0 V; +25 °C reference      | +10 / –120         | × 10 <sup>-6</sup>        |

| Oscillation start time                                             | tsta   | Ta = +25 °C<br>VDD = 2.0 V                                     | 1 Max.             | s                         |

| Aging                                                              | fa     | Ta = +25 °C<br>VDD=3.0 V; first year                           | ± 5 Max.           | × 10 <sup>-6</sup> / year |

<sup>\*1)</sup> AC rank. Precision gap per month: 13 seconds (excluding offset value)

# 7. Electrical Characteristics

# 7.1. DC Electrical Characteristics

\* Unless otherwise specified, GND = 0 V, VDD = 3 V,  $Ta = -40 \,^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$

| Symbol | Item                             | Pin name      | Condition                         | Min. | Typ.     | Max.        | Unit |

|--------|----------------------------------|---------------|-----------------------------------|------|----------|-------------|------|

| VIH1   | "H" Input Voltage1               | i iii lialiio | VCC =1.5V~5.5V                    | 0.8x | 1,77.    | 5.5         | OTIL |

|        | Tr input voltager                | CLK, SI       | VOC = 1.5 V 0.5 V                 | VCC  |          | 0.0         | V    |

| VIL1   | "L" Input Voltage1               | 1             |                                   | -0.3 |          | 0.2x        | 1    |

|        |                                  |               |                                   |      |          | VCC         |      |

| VIH2   | "H" Input Voltage2               | EVIN1,        | VDD=(1.0)∼5.5V                    | 0.8x |          | 5.5         | V    |

|        |                                  | EVIN2         |                                   | VDD  |          |             |      |

| VIL2   | "L" Input Voltage2               |               |                                   | -0.3 |          | 0.2x<br>VDD |      |

| IOH    | "H" Output Voltage               | CLKOUT        | VOH=VCC-0.5V                      |      |          | -0.5        | mA   |

| IOL1   |                                  | CLKOUT        |                                   | 0.5  |          |             |      |

| IOL2   | "L" Output Voltage               | /INT          | VOL=0.4V                          | 2.0  |          |             | mA   |

| IOL3   |                                  | SO            |                                   | 3.0  |          |             |      |

| IIL    | Input Leakage<br>Current         | CLK           | VI=5.5V or GND                    | -0.2 |          | 0.2         | μА   |

| IOZ    | Output Off-state<br>Current      | , /INT, SO    | VO=5.5V or GND                    | -0.2 |          | 0.2         | μА   |

| RDN    | Pull down resistor               | EVIN2         | built in.                         | 40   | 120      | 400         | ΚΩ   |

| VD2B   | Detector Threshold               | VCC           | Topt=+25°C                        | -3%  | 2.40     | +3%         | V    |

|        | Voltage. ( falling edge of VDD ) |               | ·                                 |      |          |             |      |

| VB2D   | Detector released                | VCC           | Topt=+25°C                        | -3%  | 2.472    | +3%         | V    |

|        | Voltage. (rising edge of VDD)    |               | ·                                 |      |          |             |      |

| ΔVDET  | Detector Threshold               | VCC           | Topt=-40~+85°C                    |      | ±100     |             | ppm/ |

| ΔTopt  | and Released                     |               |                                   |      |          |             | °C   |

|        | Voltage                          |               |                                   |      |          |             |      |

|        | Temperature coefficient          |               |                                   |      |          |             |      |

| VDET   | VBAT Voltage                     | VBAT          | Topt=-30 to +70°C                 |      | 1.25     |             | V    |

| V DL I | Monitoring Voltage               | V D/ (1       | 10μι30 ι0 +/0 C                   |      | 1.20     |             | "    |

| VDDOUT | VOUT                             | VOUT          | Topt=+25°C,                       |      | (VCC     |             | V    |

| 1      | output voltage 1                 |               | VDD=3.0V                          |      | -0.10)   |             |      |

|        |                                  |               | (lout=10mA)                       |      | <u> </u> |             |      |

| VDDOUT | VOUT                             | VOUT          | Topt=+25°C,VDD=2.0V               |      | (BAT     |             | V    |

| 2      | output voltage 2                 |               | VBAT=3.0V                         |      | -0.02)   |             |      |

|        |                                  |               | (lout=10μA)                       |      |          |             |      |

|        |                                  |               | VCC=3V, BAT=3V                    |      |          |             |      |

| IDD    | VDD current                      | VDD           | CLK=CE=0V                         |      | 1.2      | 3.5         | μΑ   |

|        |                                  |               | EVIN1=EVIN2=OPEN<br>Output = OPEN |      |          |             |      |

| IBAT1  | Time Keeping                     | VBAT          | VDD=0V, VBAT=3V                   |      | +        |             |      |

| IDATI  | Current at Backup                | VDAT          | CLK=CE=0V                         |      | 350      | 1200        | nA   |

|        | mode                             |               | EVIN1=EVIN2=OPEN                  |      |          | 1200        | ""   |

|        | 7                                |               | Output = OPEN                     |      |          |             |      |

| IBATL  | Leakage Current of               | VBAT          | VDD=3.0V                          |      |          |             |      |

|        | VBAT pin at                      |               | VBAT=0V or 5.5V                   | -1.0 |          | 1.0         | μΑ   |

|        | VDD_on                           |               | CLK=CE=0V                         |      |          |             |      |

|        |                                  |               | Output = OPEN                     |      |          |             |      |

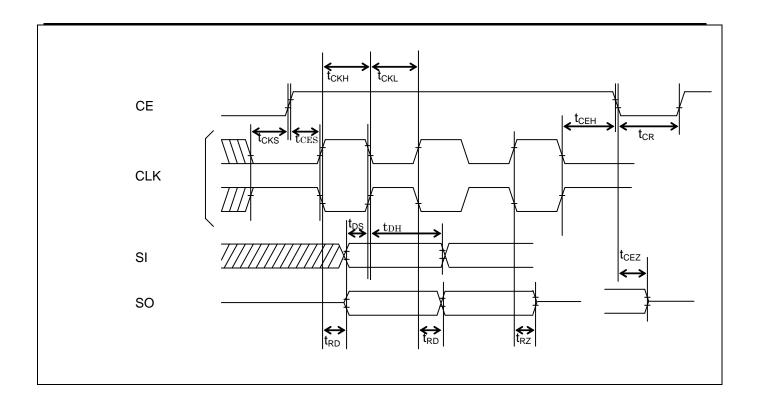

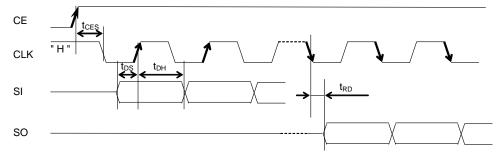

# 7.2. AC Electrical Characteristics(1)

- \* Unless otherwise specified: GND = 0 V, VDD = 1.7 V to 5.5 V, Ta = -40 °C to +85 °C

- \* Input conditions: VIH =  $0.8 \times \text{VDD}$ , VIL =  $0.2 \times \text{VDD}$ , VOH =  $0.8 \times \text{VDD}$ , VOL =  $0.2 \times \text{VDD}$ , CL = 50 pF

| Item                                          | Symbol | Condition | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|--------|-----------|------|------|------|------|

| CE setup time                                 | tces   |           | 400  |      |      | ns   |

| CE hold time                                  | tCEH   |           | 400  |      |      | ns   |

| CE recovery time                              | tCR    |           | 62   |      |      | μS   |

| CLK clock frequency                           | fclk   |           |      |      | 1.0  | MHz  |

| CLK "H" pulse width                           | tckh   |           | 400  |      |      | ns   |

| CLK "L" pulse width                           | tCKL   |           | 400  |      |      | ns   |

| CLK setup time                                | tcks   |           | 200  |      |      | ns   |

| Data output delay time                        | trd    |           |      |      | 300  | ns   |

| Data output floating time                     | trz    |           |      |      | 300  | ns   |

| Data output floating time after falling if CE | tCEZ   |           |      |      | 300  | ns   |

| Input data setup time                         | tDS    |           | 200  |      |      | ns   |

| Input data hold time                          | tDH    |           | 200  |      |      | ns   |

#### 7.3. AC Electrical Characteristics(2)

- \* Unless otherwise specified: GND = 0 V, VDD = 1.7 V to 5.5 V, Ta = -40 °C to +85 °C \* Input conditions: VIH =  $0.8 \times VDD$ , VIL =  $0.2 \times VDD$ , VOH =  $0.8 \times VDD$ , VOL =  $0.2 \times VDD$ , CL = 50 pF

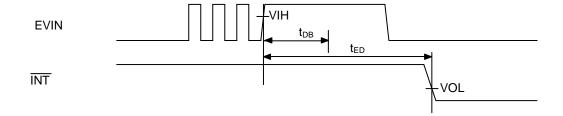

| Symbol              | Item                                  | Condition | Min.   | Тур.      | Max.   | Unit |

|---------------------|---------------------------------------|-----------|--------|-----------|--------|------|

| t <sub>DB</sub> *1) | Noise filtering time of EVIN1, EVIN2. |           | Typ -4 | 35 / 1996 | Typ +4 | ms   |

| t <sub>ED</sub>     | Event detection time                  |           | Typ -4 | tDB + 7.8 | Typ +4 | ms   |

<sup>\*1</sup> tDB select 35ms or 2seconds by DBSL bit.

### 8. Usage

#### 8.1 Usage of automatic battery switch-over circuit

#### 8.1.1 Overview.

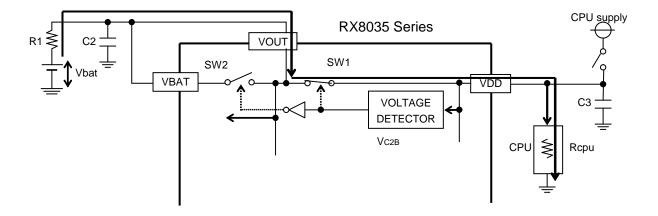

RX-4035 has three power supply terminal (VDD, VOUT, VBAT).

VOUT outputs internal supply voltage. When VOUT is higher than VB2D, internal power source is supplied from VDD,

and VOUT outputs the VDD voltage. When VOUT is lower than VD2B, internal power source is supplied from VBAT automatically. And VOUT outputs BAT voltage. And at same timing, SPI interface is invalidated, and data of RTC are protected automatically.

8.1.2 Instructions in battery connection to VBAT terminal.

RX4035 doesn't support cold start by only Battery.

A power source switch circuit is initialized by a supply of VDD.

Therefore, when Battery was set before VDD was supplied, a circuit becomes unstable.

and may be happen the thing that a leak current of about 100 microampere leak into a VBAT terminal, rarely.

This leak current may reduce life of battery.

When needs break off this leak current, please execute the following one of processing.

- 1) Before battery connection, supplying VDD.

- 2) Please supply to VDD terminal that voltage more than 2.47V more than 10ms, after battery connection.

- 3) Please short-circuit more than 10ms with a VBAT terminal and a VDD terminal, (need more than 2.47V) When short-circuit VDD and VBAT, please confirm the VBAT voltage enough.

A leak current does not occur in VBAT after the above-mentioned process.

8.1.3 The reference value of input leak current in VBAT terminal.

The input leak current and instructions.

As for the reference value in a free sampling Lot of an IBATL characteristic of "DC Electric characteristic specification" of this book, following.

VDD = 3.0V VBAT = 5.5V : Max: +9nA (-40 C +85 C)

VDD = 3.0V VBAT = 0.0V : Max: -3nA (-40 C +85 C)

#### Note

The VDD voltage; VD2B(Typ. 2.4V), VB2D(Typ. 2.47V) Both VDD side switch and VBAT side switch are in condition that these are near to ON or near to OFF by.

This condition may cause unnecessary leak.

Please consider the VDD voltage to change between MIN and MAN immediately, and it is not stagnant in the vicinity of the switch voltage as mentioned above.

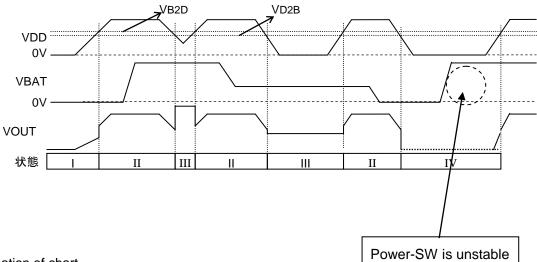

8.1.4 Power source switch chart

Link of VDD and VBAT and VOUT is shown in below chart.

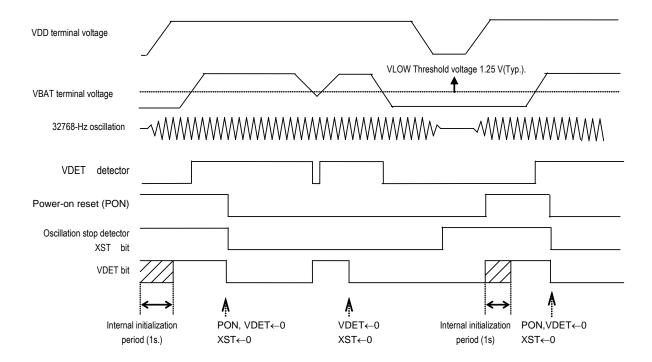

8.2 Timing chart of VDD, VBAT and VOUT.

Explanation of chart.

| Status | Explanations                                                                     |

|--------|----------------------------------------------------------------------------------|

| I      | It supplies it only in VDD. It is supplied in VOUT slowly.                       |

|        | VDD follows it with 1/2 voltage of VDD.                                          |

| II     | VCC is over VB2D. VOUT rises to VDD and the equal voltage.                       |

|        | VDD follows VDD afterwards. If VDD is higher than VD2B, it is VDD=VOUT.          |

| III    | When VDD is less than VD2B, VOUT is equal with VBAT.                             |

| IV     | When RX4035 is cold start by Battery, about 100uA current occur in VBAT, rarely. |

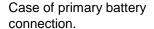

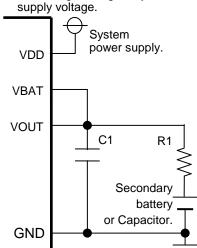

#### 8.3 Examples of battery connections.

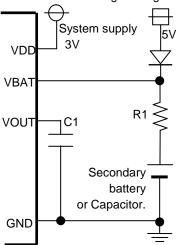

Case of secondary battery connection.

And charge voltage = system

Case of secondary battery connection.

when the main power supply voltage is different from the charge voltage.

### 8.4 Note of battery switch-over circuit.

While charging Back up power source charging current flow from CPU VDD via VDD pin & VOUT pin to Rechargeable battery or Capacitor. It is required to select carefully the value of R1 for this circuit.

This figure shows Discharge current route from Back up battery after switch OFF CPU VDD switch. When Rechargeable battery or big capacitance capacitor is used on VOUT pin like in this circuit ,after switch off the CPU VDD Switch discharge current flow from the battery to CPU as shown by heavy arrow line. If value of R1 is quite smaller than impedance of CPU (Rcpu) VDD Voltage might keep higher than level of VB2D that makes SW1 to be off, then SW1 might stay to be on. Therefore R1 is limited by following formula.

R1> Rcpu  $\times$  (Vbat – (VD2B)) / (VB2D)

And also sometimes R1 is limited by the specification of back up device. Please refer to specification from Back up device manufacture as well.

# 9. Functional descriptions

#### 9.1. Overview of Functions

#### 1) Clock and calendar functions

This function is used to set and read out month, date, day, hour, minute, and second.

Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2099. (2100 is not leap year.)

#### 2) Clock precision adjustment function

The clock precision can be adjusted forward or back in units of  $\pm 3.05 \times 10^{-6}$ . This function can be used to implement a higher precision clock function, such as by: • enabling higher clock precision throughout the year by taking seasonal clock precision adjustments into account in advance, or enabling correction of temperature-related clock precision variation in systems that include a temperature detection function.

Note: Only the clock precision can be adjusted. The adjustments have no effect on the 32.768-kHz output from the CLKOUT pin.

#### 3) Periodic interrupt function

In addition to the alarm function, Periodic interrupts can be output via the /INT pin.

Select among five Periodic frequency settings: 2 Hz, 1 Hz, 1/60 Hz, hourly, or monthly.

Select among two output waveforms for periodic interrupts: an ordinary pulse waveform (2 Hz or 1 Hz) or a waveform (every second, minute, hour, or month) for CPU-level interrupts that can support CPU interrupts.

A polling function is also provided to enable monitoring of pin states via registers.

#### 4) Alarm functions

This module is equipped with two alarm functions (Alarm Week and Alarm Month) that output interrupt signals to the host at preset times. The Alarm Week function can be used for day, hour, and minute-based alarm settings, and it outputs interrupt signals via the /INT pin. Multiple day settings can be selected (such as Monday, Wednesday, Friday, Saturday, and Sunday). The Alarm Month function can be used for month, day, hour, and minute-based settings, and it outputs interrupt signals via the /INT pin.

A polling function is also provided to enable checking of each alarm mode by the host.

#### 5) Data reliability monitoring function.

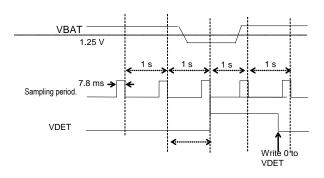

When oscillation has stopped, XSTP bit is set to one by oscillation stop detector. When the battery voltage(VBAT terminal) drops than VDET voltage threshold value = 1.25 V (Typ.), VDET bit is set to one. VDET detection is performed once per second in consideration of the module's low current consumption. When initial power-on occur in this module, PON bit is set to one. Power-on-reset occurs in VCC rise to VB2D from 0V and BAT is 0V basically.

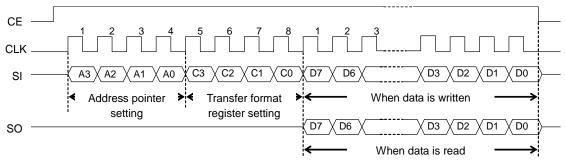

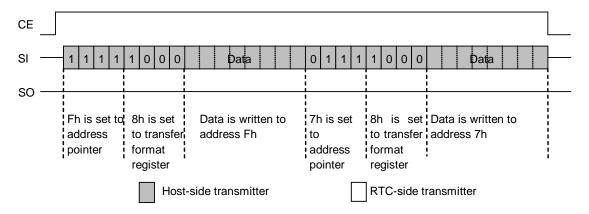

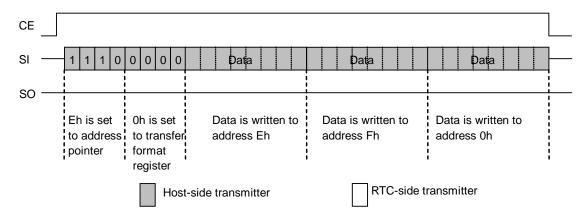

#### 6) Interface with CPU

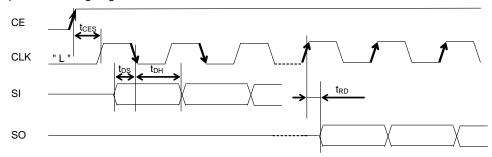

Data is read and written via the SPI bus interface using four signal lines: CLK (clock), SI (serial input), SO (serial output) and CE (chip enable).

The CLK's maximum clock frequency is 1.25MHz (when VDD ≥ VDET ).

#### 7) 32.768-kHz clock output

The 32.768-kHz clock (with precision equal to that of the built-in quartz oscillator) can be output via the FOUT pin.

Note: The precision of this 32.768-kHz clock output via the FOUT pin cannot be adjusted (even when using the clock precision adjustment function).

CLOCK OUTPUT IS DRIVEN BY VDD SUPPLY. THEREFORE, WHEN VDD VOLTAGE IS 0V, CLOCK OUTPUT IS 0V TOO.

#### 9.2. Register table

#### BANK=0

| Adrs | Function               | Data          |       |                 |       |      |      |       |       |

|------|------------------------|---------------|-------|-----------------|-------|------|------|-------|-------|

|      | T dilotori             |               | D6    | D5              | D4    | D3   | D2   | D1    | D0    |

| 0h   | Seconds                | -             | S40   | S20             | S10   | S8   | S4   | S2    | S1    |

| 1h   | Minutes                | -             | M40   | M20             | M10   | M8   | M4   | M2    | M1    |

| 2h   | Hours                  | <u>12</u> /24 | -     | H20<br>P/ A     | H10   | H8   | H4   | H2    | H1    |

| 3h   | Day of week            | -             | -     | -               | -     | -    | W4   | W2    | W1    |

| 4h   | Day of month           | -             | -     | D20             | D10   | D8   | D4   | D2    | D1    |

| 5h   | Months                 | -             | -     | -               | MO10  | MO8  | MO4  | MO2   | MO1   |

| 6h   | Years                  | Y80           | Y40   | Y20             | Y10   | Y8   | Y4   | Y2    | Y1    |

| 7h   | Digital Offset         | TEST          | F6    | F5              | F4    | F3   | F2   | F1    | F0    |

| 8h   | Alarm_Wk ; Minute      | *             | WkM40 | WkM20           | WkM10 | WkM8 | WkM4 | WkM2  | WkM1  |

| 9h   | Alarm_Wk ; Hour        | *             | *     | WkH20<br>WkP/ A | WkH10 | WkH8 | WkH4 | WkH2  | WkH1  |

| Ah   | Alarm_Wk; Day of week. | *             | WkW6  | WkW5            | WkW4  | WkW3 | WkW2 | WkW1  | WkW0  |

| Bh   | Alarm_Mo ; Minute      | *             | MoM40 | MoM20           | MoM10 | MoM8 | MoM4 | MoM2  | MoM1  |

| Ch   | Alarm_Mo ; Hour        | *             | *     | MoH20<br>MoP/ A | MoH10 | MoH8 | MoH4 | MoH2  | MoH1  |

| Dh   | RAM                    | *             | *     | *               | *     | *    | *    | *     | *     |

| Eh   | Control 1              | WkALE         | MoALE | DBSL            | EDEN  | TEST | CT2  | CT1   | CT0   |

| Fh   | Control 2              | BANK<br>TSFG  | VDET  | XSTP            | PON   | EDFG | CTFG | WkAFG | MoAFG |

#### BANK=1

| Adrs | Function                |               |      |               | Da      | ta    |       |       |       |

|------|-------------------------|---------------|------|---------------|---------|-------|-------|-------|-------|

|      |                         | D7            | D6   | D5            | D4      | D3    | D2    | D1    | D0    |

| 0h   | Time-stamp Sec.         | EDCH1         | TS40 | TS20          | TS10    | TS8   | TS4   | TS2   | TS1   |

| 1h   | Time-stamp Min          | EDCH2         | TM40 | TM20          | TM10    | TM8   | TM4   | TM2   | TM1   |

| 2h   | Time-stamp Hour         | -             | -    | TH20<br>TP/ A | TH10    | TH8   | TH4   | TH2   | TH1   |

| 3h   | Time-stamp Day of Week  | -             | -    | -             | -       | -     | TW4   | TW2   | TW1   |

| 4h   | Time-stamp Day of Month | -             |      | TD20          | TD10    | TD8   | TD4   | TD2   | TD1   |

| 5h   | Time-stamp Month        | - [           | -    | -             | TMO10   | TMO8  | TMO4  | TMO2  | TMO1  |

| 6h   | Time-stamp Year         | TY80          | TY40 | TY20          | TY10    | TY8   | TY4   | TY2   | TY1   |

| 7h   | Digital Offset          |               |      |               | Same as | BANK0 |       |       |       |

| 8h   | Reserved                | -             | -    | -             | -       | -     | -     | -     | -     |

| 9h   |                         | -             | -    | -             | -       | -     | -     | -     | -     |

| Ah   |                         | -             | -    | -             | -       | -     | -     | -     | -     |

| Bh   | Alarm_Mo ; Day          | DYE           | *    | MoD20         | MoD10   | MoD8  | MoD4  | MoD2  | MoD1  |

| Ch   | Alarm_Mo ; Month        | MOE           | *    | *             | MoMO10  | MoMO8 | MoMO4 | MoMO2 | MoMO1 |

| Dh   | RAM                     | Same as BANK0 |      |               |         |       |       |       |       |

| Eh   | Control 1               | Same as BANK0 |      |               |         |       |       |       |       |

| Fh   | Control 2               |               |      |               | Same as | BANK0 |       |       |       |

#### \*1. The PON bit is a power-on reset flag bit.

The PON bit is set to "1" when a reset occurs, such as during the initial power-up or when recovering from a supply voltage drop. At the same time, all bits in the Alarm\_Wk, Alarm\_Mo, RAM, Digital Offset, Control 1 and Control 2 registers except for the PON, VDET, XSTP bits are reset to "0". And output of INT are inhibited and Hi-Z.

Note: When PON = 1, all other register values are undefined, so be sure to perform a reset before using the module. Also, be sure to avoid entering incorrect date and time data, as clock operations are not guaranteed when the time data is incorrect.

- \*2. The TEST bits are used only testing in the factory. Clear all TEST bits to "0" always surely.

- \*3. All bits marked with " " are read-only bits. The read value of these bits are always "0". Writing is null and void.

- \*4. All bits marked with " \* " are read-write bits. As for these bits, set to 1 and clear are possible.

- \*5. By the write-access, it is null and void to set 1 to PON, VDET,XSTP,.

#### 9.2.1. Register map after power-on-reset.

### ●BANK=0

| Adrs | Function               |    |    |    | Da | ata |    |    |    |

|------|------------------------|----|----|----|----|-----|----|----|----|

|      | Function               | D7 | D6 | D5 | D4 | D3  | D2 | D1 | D0 |

| 0h   | seconds                | _  |    |    |    |     |    |    |    |

| 1h   | minutes                | _  |    |    |    |     |    |    |    |

| 2h   | houts                  |    | _  |    |    |     |    |    |    |

| 3h   | Day of week            | _  | _  | _  | _  | _   |    |    |    |

| 4h   | Day of month           | 0  | 0  |    |    |     |    |    |    |

| 5h   | Month                  | 0  | 0  | 0  |    |     |    |    |    |

| 6h   | Years                  |    |    |    |    |     |    |    |    |

| 7h   | Digital offset         | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| 8h   | Alarm_Wk ; Minute      | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| 9h   | Alarm_Wk ; Hour        | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Ah   | Alarm_Wk ; Day of Week | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Bh   | Alarm_Mo ; Minute      | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Ch   | Alarm_Mo ; Hour        | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Dh   | RAM                    | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Eh   | Control 1              | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  |

| Fh   | Control 2              | 0  | 1  | 1  | 1  | 0   | 0  | 0  | 0  |

#### ●BANK=1

| Adrs | Function                |               |    |    | Da      | ata     |    |    |    |

|------|-------------------------|---------------|----|----|---------|---------|----|----|----|

|      |                         | D7            | D6 | D5 | D4      | D3      | D2 | D1 | D0 |

| 0h   | Time-stamp Sec.         | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 1h   | Time-stamp Min          | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 2h   | Time-stamp Hour         | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 3h   | Time-stamp Day of Week  | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 4h   | Time-stamp Day of Month | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 5h   | Time-stamp Month        | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 6h   | Time-stamp Year         | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| 7h   | Digital offset          |               |    |    | Same as | s BANK0 |    |    |    |

| 8h   | Reserved                | - 1           | _  | _  | _       | T - 1   | _  | _  | _  |

| 9h   |                         | -             | _  | _  | _       |         | _  | _  | _  |

| Ah   |                         | -             | _  | _  | _       | _       | _  | _  | _  |

| Bh   | Alarm_Mo ; Day          | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| Ch   | Alarm_Mo ; Month        | 0             | 0  | 0  | 0       | 0       | 0  | 0  | 0  |

| Dh   | RAM                     | Same as BANK0 |    |    |         |         |    |    |    |

| Eh   | Control 1               | Same as BANK0 |    |    |         |         |    |    |    |

| Fh   | Control 2               |               |    |    | Same a  | s BANK0 |    |    |    |

- \*1. All bits marked with " " are read-only bits. The read value of these bits are always "0". Writing is null and void.

- \*2. All bits marked with " \* " are read-write bits. As for these bits, set to 1 and clear are possible.

- \*3. All bits marked with " / " are undefined bits after power-on-reset.

- \*4. By the write-access, it is null and void to set 1 to PON, VDET, XSTP, MoAFG, WkAFG.

#### 9.2.2. Time counter (Reg 0 to 2)

| Address | Function | bit 7 | bit 6 | bit 5        | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|--------------|-------|-------|-------|-------|-------|

| 0       | Seconds  | -     | S40   | S20          | S10   | S8    | S4    | S2    | S1    |

| 1       | Minutes  | _     | M40   | M20          | M10   | M8    | M4    | M2    | M1    |

| 2       | Hours    | _     | -     | H20<br>P, /A | H10   | H8    | H4    | H2    | H1    |

- The time counter counts seconds, minutes, and hours.

- The data format is BCD format (except during 12-hour mode). For example, when the "seconds" register value is "0101 1001" it indicates 59 seconds.

- \* Note with caution that writing non-existent time data may interfere with normal operation of the time counter.

#### 1) Second counter

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0       | Seconds  | _     | S40   | S20   | S10   | S8    | S4    | S2    | S1    |

- This second counter counts from "00" to "01," "02," and up to 59 seconds, after which it starts again from 00 seconds.

- When a value is written to the second counter, the internal counter is also reset to zero in less than one second

- after writing seconds data, clear VDET-bit to ZERO.

#### 2) Minute counter

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1       | Minutes  | _     | M40   | M20   | M10   | M8    | M4    | M2    | M1    |

• This minute counter counts from "00" to "01," "02," and up to 59 minutes, after which it starts again from 00 minutes.

#### 3) Hour counter

| Address | Function | bit 7  | bit 6 | bit 5         | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|--------|-------|---------------|-------|-------|-------|-------|-------|

| 2       | Hours    | 12 /24 | _     | H20<br>P , /A | H10   | Н8    | H4    | H2    | H1    |

#### /12,24 bit

This bit is used to select between 12-hour clock operation and 24-hour clock operation.

| /12,24       | Data |               | Description |           |

|--------------|------|---------------|-------------|-----------|

| Write / Dood | 0    | 12-hour clock |             | * Default |

| Write / Read | 1    | 24-hour clock |             |           |

<sup>\*</sup> Be sure to select between 12-hour and 24-hour clock operation before writing the time data.

- The hour counter counts hours, and its clock mode differs according to the value of its /12,24 bit.

- During 24-hour clock operation, bit 5 functions as H20 (two-digit hour display). During 12-hour clock operation, bit 5 functions as an AM/PM indicator ("0" indicates AM and "1" indicates PM).

| /12,24 bit | Description | Address 2 (   | Hours register<br>12-hour clock |               |               |

|------------|-------------|---------------|---------------------------------|---------------|---------------|

|            |             | 24-hour clock | 12-hour clock                   | 24-hour clock | 12-hour clock |

| 0          | 12-hour     | 00            | 12 ( AM 12 )                    | 12            | 32 ( PM 12 )  |

| 0          | clock       | 01            | 01 ( AM 01 )                    | 13            | 21 ( PM 01 )  |

|            | 0.00        | 02            | 02 ( AM 02 )                    | 14            | 22 ( PM 02 )  |

|            |             | 03            | 03 ( AM 03 )                    | 15            | 23 ( PM 03 )  |

|            |             | 04            | 04 ( AM 04 )                    | 16            | 24 ( PM 04 )  |

|            |             | 05            | 05 ( AM 05 )                    | 17            | 25 ( PM 05 )  |

|            |             | 06            | 06 ( AM 06 )                    | 18            | 26 ( PM 06 )  |

|            |             | 07            | 07 ( AM 07 )                    | 19            | 27 ( PM 07 )  |

| 1          | 24-hour     | 08            | 08 ( AM 08 )                    | 20            | 28 ( PM 08 )  |

| '          | clock       | 09            | 09 ( AM 09 )                    | 21            | 29 ( PM 09 )  |

|            |             | 10            | 10 ( AM 10 )                    | 22            | 30 ( PM 10 )  |

|            |             | 11            | 11 ( AM 11 )                    | 23            | 31 ( PM 11 )  |

|            |             | •             | •                               | •             | •             |

#### 9.2.3. Day counter (Reg 3)

| Address | Function    | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 3       | Day of Week | _     | _     | -     | _     | _     | W4    | W2    | W1    |

- The day counter is a divide-by-7 counter that counts from 00 to 01 and up 06 before starting again from 01.

- The correspondence between days and count values is shown below.

| Days           | W4 | W2 | W1 | Day       | Remark                               |

|----------------|----|----|----|-----------|--------------------------------------|

|                | 0  | 0  | 0  | Sunday    | 00 h                                 |

|                | 0  | 0  | 1  | Monday    | 01 h                                 |

|                | 0  | 1  | 0  | Tuesday   | 02 h                                 |

| Write / Read   | 0  | 1  | 1  | Wednesday | 03 h                                 |

|                | 1  | 0  | 0  | Thursday  | 04 h                                 |

|                | 1  | 0  | 1  | Friday    | 05 h                                 |

|                | 1  | 1  | 0  | Saturday  | 06 h                                 |

| Write prohibit | 1  | 1  | 1  | _         | Do not enter a setting for this bit. |

Weekday layout is one of example.

#### 9.2.4. Calendar counter (Reg 4 to 6)

| Address | Function     | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|--------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4       | Day of Month | _     | _     | D20   | D10   | D8    | D4    | D2    | D1    |

| 5       | Months       | _     | -     | -     | MO10  | MO8   | MO4   | MO2   | MO1   |

| 6       | Years        | Y80   | Y40   | Y20   | Y10   | Y8    | Y4    | Y2    | Y1    |

- The auto calendar function updates all dates, months, and years from January 1, 2001 to December 31, 2099.

- The data format is BCD format. For example, a date register value of "0011 0001" indicates the 31st.

- \* Note with caution that writing non-existent date data may interfere with normal operation of the calendar counter.

#### 1) Date counter

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4       | Days     | _     | _     | D20   | D10   | D8    | D4    | D2    | D1    |

- The updating of dates by the date counter varies according to the month setting.

- \* A leap year is set whenever the year value is a multiple of four (such as 04, 08, 12, 88, 92, or 96).

| Days         | Month                    | Date update pattern      |

|--------------|--------------------------|--------------------------|

|              | 1, 3, 5, 7, 8, 10, or 12 | 01, 02, 03 to 30, 31, 01 |

| Write / Read | 4, 6, 9, or 11           | 01, 02, 03 to 30, 01, 02 |

| Wille / Read | February in leap year    | 01, 02, 03 to 28, 29, 01 |

|              | February in normal year  | 01, 02, 03 to 28, 01, 02 |

#### 2) Month counter

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 5       | Months   | _     | _     | _     | MO10  | MO8   | MO4   | MO2   | MO1   |

• The month counter counts from 01 (January), 02 (February), and up to 12 (December), then starts again at 01 (January).

#### 3) Year counter

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 6       | Years    | Y80   | Y40   | Y20   | Y10   | Y8    | Y4    | Y2    | Y1    |

- The year counter counts from 00, 01, 02 and up to 99, then starts again at 00.

- \* In any year that is a multiple of four (04, 08, 12, 88, 92, 96, etc.), the dates in February are counted from 01, 02, 03 and up to 29 before starting again at 01.

#### 9.2.5. Clock precision adjustment register (Reg 7)

| Address | Function       | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 7       | Digital Offset | TEST  | F6    | F5    | F4    | F3    | F2    | F1    | F0    |

|         | (Default)      | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

- The binary encoded settings in the seven bits from F6 to F0 are used to set the precision of the clock generated from the 32768-Hz internal oscillator up to ±189 × 10<sup>-6</sup> in the forward (ahead) or reverse (behind) direction, in units of ± 3.05 × 10<sup>-6</sup>. (Only the clock precision can be adjusted. The 32.768-kHz output from the FOUT pin is not affected.)

- When not using this function, be sure to set "0" for bits F6 to F0.

- Always, clear TEST bits to "0" surely.

- \* For details, see "8.3. Clock Precision Adjustment Function".

#### 9.2.6. Alarm\_Wk register (Reg 8 to A)

| Address | Function          | bit 7 | bit 6 | bit 5             | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-------------------|-------|-------|-------------------|-------|-------|-------|-------|-------|

| 8       | Alarm_Wk ; Minute | _     | WkM40 | WkM20             | WkM10 | WkM8  | WkM4  | WkM2  | WkM1  |

| 9       | Alarm_Wk ; Hour   | ı     | -     | WkH20<br>WkP , /A |       | WkH8  | WkH4  | WkH2  | WkH1  |

| Α       | Alarm_Wk ; Day    | _     | WkW6  | WkW5              | WkW4  | WkW3  | WkW2  | WkW1  | WkW0  |

- The Alarm A function is used, along with the WkALE and WkAFG bits, to set alarms for specified day, hour, and minute values.

- When the Alarm\_Wk setting matches the current time, /IN pin is set to "L" and the WkALE bit is set to "1".

Note: If the current date/time is used as the Alarm\_Wk setting, the alarm will not occur until the counter counts up to the current date/time (i.e., an alarm will occur next time, not immediately).

- During 24-hour clock operation, the "Alarm\_Wk; Hours" register's bit 5 (WkH20, WkP, /A) functions as WkH20 (two-digit hour display), and during 12-hour clock operation it functions as an AM/PM indicator.

- When the Alarm\_Wk function's day values (WkW6 to WkW0) are all "0" Alarm\_Wk does not occur.

#### 9.2.7. Alarm\_ Month register (Reg B and C)

| Address | Function          | bit 7 | bit 6 | bit 5             | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-------------------|-------|-------|-------------------|-------|-------|-------|-------|-------|

| В       | Alarm_Mo ; Minute | _     | MoM40 | MoM20             | MoM10 | MoM8  | MoM4  | MoM2  | MoM1  |

| С       | Alarm_Mo ; Hour   | _     | -     | MoH20<br>MoP , /A | MoH10 | MoH8  | MoH4  | MoH2  | MoH1  |

- The Alarm Month function is used, along with the MoALE and MoAFG bits, to set alarms for specified hour and minute values.

- When the Alarm\_Month setting matches the current time, /INT pin is set to "L" and the MoALE bit is set to "1".

Note: If the current time is used as the Alarm\_Mo setting, the alarm will not occur until the counter counts up to the current time (i.e., an alarm will occur next time, not immediately).

- During 24-hour clock operation, the "Alarm\_Mo; Hours" register's bit 5 (MoH20, MoP, /A) functions as MoH20 (two-digit hour display), and during 12-hour clock operation it functions as an AM/PM indicator.

#### 9.2.8. RAM register (Reg D)

| Address | Function | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| D       | User RAM | *     | *     | *     | *     | *     | *     | *     | *     |

These bits, set to 1 and clear are possible.

#### 9.2.9. Control register 1 (Reg E)

| Address | Function  | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| E       | Control 1 | WkALE | MoALE | DBSL  | EDEN  | TEST  | CT2   | CT1   | CT0   |

|         | (Default) | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

<sup>\*)</sup> The default value is the value that is read (or is set internally) after the PON bit has been set to "1," such as after powering up from 0 V or recovering from a supply voltage drop.

#### 1) WkALE bit

This bit is used to set up the Alarm Wk function (to generate alarms matching day, hour, or minute settings).

| WkALE        | Data | Description                                                               | <b>5</b> , |

|--------------|------|---------------------------------------------------------------------------|------------|

|              | 0    | Alarm_Wk, match comparison operation invalid                              | * Default  |

| Write / Read | 1    | Alarm_Wk, match comparison operation valid (/INT = "L" when match occurs) |            |

<sup>\*</sup> For details, see "8.5. Alarm Wk Function".

#### 2) MoALE bit

This bit is used to set up the Alarm Mo function (to generate alarms matching hour or minute settings).

| MoALE        | Data | Description                                                               |           |

|--------------|------|---------------------------------------------------------------------------|-----------|

|              | 0    | Alarm_Mo, match comparison operation invalid                              | * Default |

| Write / Read | 1    | Alarm_Mo, match comparison operation valid (/INT = "L" when match occurs) |           |

<sup>\*</sup> For details, see "8.6. Alarm Mo Function".

#### 3) DBSL bit

This bit is used to select de-bounce time in EVIN input.

| DBSL         | Data | Description                                 |           |

|--------------|------|---------------------------------------------|-----------|

| Write / Read | 0    | De-bounce time are set up to 1996ms. (Typ.) | * Default |

| write / Read | 1    | De-bounce time are set up to 35ms. (Typ.)   |           |

#### 4) EDEN bit

This bit enables Event Detection and Timestamp function.

| EDEN           | Data | De                                                                      | escription |

|----------------|------|-------------------------------------------------------------------------|------------|

| Write / Read 0 |      | Event detection are stops, and BAN<br>Address0,1,2,4,5,6 of Bank1 and E | * Detault  |

|                |      | Enables event detection and timest                                      | amp.       |

#### 5) TEST bit

This bit is used by the manufacturer for testing. Always, clear this bit to "0" surely.

Be careful to avoid writing a "1" to this bit when writing to other bits.

| TEST         | Data | Description                            |        |

|--------------|------|----------------------------------------|--------|

| Write / Read | 0    | Normal operation mode * Do             | efault |

| write / Read | 1    | Setting prohibited (Factory test mode) |        |

#### 6) CT2, CT1, and CT0 bits

These bits are used to set up the operation of the periodic interrupt function that uses the /INT pin.

| ble die deed to cot up the operation of the periodic interrupt fariotical that deed the first pin |     |     |                |                           |                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------|-----|-----|----------------|---------------------------|-------------------------------------------------|--|--|--|

| CT2                                                                                               | CT1 | СТО |                | /INT pin's output setting |                                                 |  |  |  |

| 012 011                                                                                           |     | CIU | Waveform mode  | Cycle/Fall timing         |                                                 |  |  |  |

| 0                                                                                                 | 0   | 0   | _              | /INT = Hi-Z (= OFF)       | * Default                                       |  |  |  |

| 0                                                                                                 | 0   | 1   | _              | /INT = Fixed low          |                                                 |  |  |  |

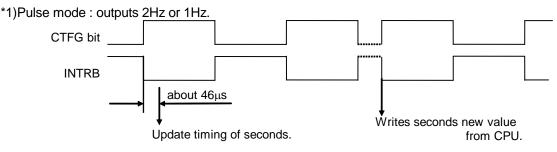

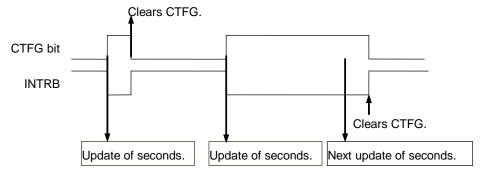

| 0                                                                                                 | 1   | 0   | Pulse mode *1) | 2 Hz                      | (50% duty)                                      |  |  |  |

| 0                                                                                                 | 1   | 1   | Pulse mode *1) | 1 Hz                      | (50% duty)                                      |  |  |  |

| 1                                                                                                 | 0   | 0   | Level mode *2) | Once per second           | (Synchronous with per-second count-up)          |  |  |  |

| 1                                                                                                 | 0   | 1   | Level mode *2) | Once per minute           | (Occurs when seconds reach ":00")               |  |  |  |

| 1                                                                                                 | 1   | 0   | Level mode *2) | Once per hour             | (Occurs when minutes and seconds reach "00:00") |  |  |  |

| 1                                                                                                 | 1   | 1   | Level mode *2) | Once per month            | (Occurs at 00:00:00 on first day of month)      |  |  |  |

<sup>\*</sup> For details, see "8.4. Periodic Interrupt".

#### 9.2.10. Control register 2 (Reg F)

| Address | Function  | bit 7        | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-----------|--------------|-------|-------|-------|-------|-------|-------|-------|

| F       | Control 2 | BANK<br>TSFG | VDET  | XSTP  | PON   | EDFG  | CTFG  | WkAFG | MoAFG |

|         | (Default) | (0)          | (0)   | (–)   | (1)   | (0)   | (0)   | (0)   | (0)   |

The default value is the value that is read (or is set internally) after the PON bit has been set to "1," such as after powering up from 0 V or recovering from a supply voltage drop.

" – " are read-only bits. The read value of these bits are always "0". Writing is null and void.

#### 1) BANK bit

This bit uses switch to Bank0 or Bank1.

#### 2) TSFG bit

This bit indicate reliability of the timestamp data.

When timestamp event occurs, if XSTP and VDET was "0" both, then TSFG is set to "1".

Or if one of XSTP or VDET are set, then TSFG are cleared to "0".

| one of Notified VBET are bot, then for a are decired to 0: |      |                                                               |           |  |  |  |  |

|------------------------------------------------------------|------|---------------------------------------------------------------|-----------|--|--|--|--|

| BANK<br>TSFG                                               | Data | Description                                                   |           |  |  |  |  |

| Write                                                      | 0    | Access is possible to a register of BANK0. Time and calendar. | * Default |  |  |  |  |

| (BANK)                                                     | 1    | Access is possible to a register of BANK1. Time stamp data.   |           |  |  |  |  |

| Read                                                       | 0    | When clears EDEN bit, TSFG bit clears too.                    | * Default |  |  |  |  |

| (TSFG)                                                     | 1    | Time stamp data are validly.                                  |           |  |  |  |  |

#### 3) VDET bit

VDET shows that the inside voltage was less than VDET

| VDET   | Data | Description                                                                                                                |           |

|--------|------|----------------------------------------------------------------------------------------------------------------------------|-----------|

| Write  | 0    | Clears the VDET bit to zero, restarts the VBAT drop detection operation and sets up for next VBAT drop detection operation | * Default |

| VVIILE | 1    | Ignored.                                                                                                                   |           |

| Read   | 0    | VBAT drop was not detected                                                                                                 | * Default |

| Read   | 1    | VBAT drop was detected (result is that bit value is held until cleared to zero)                                            |           |

<sup>\*</sup> For details, see "8.7. Detection Functions".

Note: after writing seconds data, clear VDET-bit to ZERO.

#### 4) XSTP bit

XSTP must be cleared to zero before it is used.

When it was detected a vibration stop, XSTP is set to "1". "0" shows that there is not a stop of an oscillation. If detect oscillation stop, XSTP set to "1". (Note: The logic of this bit is reverse of RX-8025.)

| XSTP   | Data | Description                                                                             | •         |

|--------|------|-----------------------------------------------------------------------------------------|-----------|

| Write  | 0    | Starts the oscillation stop detection function.                                         |           |

| vviite | 1    | Ignored.                                                                                |           |

| Dood   | 0    | Oscillation stop was not detected                                                       |           |

| Read   | 1    | Oscillation stop was detected (result is that bit value is held until a "0" is written) | * Default |

#### 4) PON bit

This bit indicates the power-on reset detection function's detection results.

The PON bit is set (= 1) when the internal Power-On Reset function operates.

|        | .,   |                                                                                       |           |

|--------|------|---------------------------------------------------------------------------------------|-----------|

| PON    | Data | Description                                                                           |           |

| Write  | 0    | Clears the PON bit to zero and sets up next detection operation                       |           |

| VVIILE | 1    | Ignored.                                                                              |           |

| Read   | 0    | Power-On Reset was not detected                                                       |           |

| Neau   | 1    | Power-On Reset was detected. (result is that bit value is held until cleared to zero) | * Default |

<sup>\*</sup> When PON = "1" all bits in the Clock Precision Adjustment register and in the Control 1 and Control 2 registers (except for the PON, VDET and XSTP bits) are reset to "0". This also causes output from /INT and /INT pin to be stopped (= Hi-Z).

VDD should rise from less than 0.2V so that Power-On-Reset occurs.

#### 9.2.11. Diagnosis of status based on detection results

The status of power supplies and reliability of time and calendar can be confirmed by reading the detection results indicated by PON bit, XSTP bit and VDET bit.

The following are status diagnosis based on various combinations of detection results.

|              | ddress F<br>rol 2 Reg |               | Diagnosis of status                                                                 |                                                                                                                                                                        |  |  |  |

|--------------|-----------------------|---------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| bit 4<br>PON | bit 5<br>XSTP         | bit 6<br>VDET | Status of power supply and oscillation circuit                                      | Status of clock and backup                                                                                                                                             |  |  |  |

| 0            | 1                     | 0             | Supply voltage was<br>normal. But oscillation has<br>stopped.                       | <ul> <li>Clock abnormality has occurred → Initialization is<br/>required</li> <li>Clock has stopped temporarily, possibly due to<br/>mechanical clash, etc.</li> </ul> |  |  |  |

| 0            | 1                     | 1             | <ul> <li>Supply voltage has<br/>dropped and oscillation<br/>has stopped.</li> </ul> | <ul> <li>Clock abnormality has occurred → Initialization is required。</li> <li>* Clock has stopped, maybe due to drop in backup power supply.</li> </ul>               |  |  |  |

| 0            | 0                     | 0             | Normal status.                                                                      | Normal status.                                                                                                                                                         |  |  |  |

| 0            | 0                     | 1             | <ul> <li>Supply voltage has<br/>dropped but oscillation<br/>continues.</li> </ul>   | Maybe initialization is unnecessary. But, exchange of a battery will be necessary.                                                                                     |  |  |  |

| 1            | 1                     | X             | <ul> <li>Supply voltage has<br/>dropped to 0 V.</li> </ul>                          | <ul> <li>Initialization is required regardless of the clock status<br/>and whether or not a voltage drop has occurred.</li> </ul>                                      |  |  |  |

| 1            | 0                     | х             | <ul> <li>Power supply flickering is<br/>likely.</li> </ul>                          | Initialization is required.                                                                                                                                            |  |  |  |

Note: after writing seconds data, clear VDET-bit to ZERO.

#### 9.3 Time stamp functions.

#### 9.3.1. EDFG bit

When an event signal valid was detected, EDFG is set. An event terminal detected first is recorded in EDCH1, EDCH2, after EDEN was set. When it was detected at the same time by two terminals, both bits are set.

| EDFG | status                              |           |

|------|-------------------------------------|-----------|

| 0    | Event detection does not yet occur. | (Default) |

| 1    | Event detected.                     |           |

Note: "1" is not written in EDFG. Only zero clear is possible.

#### 9.3.2 Time stamp registers. (BANK=1,address 0-6h)

| Adrs | Function                | Data  |      |       |       |      |      |      |      |

|------|-------------------------|-------|------|-------|-------|------|------|------|------|

|      |                         | D7    | D6   | D5    | D4    | D3   | D2   | D1   | D0   |

| 0h   | Time-stamp Sec.         | EDCH1 | TS40 | TS20  | TS10  | TS8  | TS4  | TS2  | TS1  |

| 1h   | Time-stamp Min          | EDCH2 | TM40 | TM20  | TM10  | TM8  | TM4  | TM2  | TM1  |

| 2h   | Time-stamp Hour         | -     | -    | TH20  | TH10  | TH8  | TH4  | TH2  | TH1  |

|      |                         |       |      | TP/ A |       |      |      |      |      |

| 3h   | Time-stamp Day of Week  | - :   | -    | -     | -     | -    | TW4  | TW2  | TW1  |

| 4h   | Time-stamp Day of Month | -     | -    | TD20  | TD10  | TD8  | TD4  | TD2  | TD1  |

| 5h   | Time-stamp Month        | -     | -    | -     | TMO10 | TMO8 | TMO4 | TMO2 | TMO1 |

| 6h   | Time-stamp Year         | TY80  | TY40 | TY20  | TY10  | TY8  | TY4  | TY2  | TY1  |

<sup>•</sup> All time stamp register are read only. Either date and time when an event was input first of an EVIN1 terminal and a RVIN2 terminal are recorded. The next event is not recorded unless EDEN is set to 1 from 0 again. When EDEN bit is cleared, all time stamp registers are cleared by zero. Therefore, time stamp data must be read before clearing an EDEN bit surely.

9.3.3 EDCH1,EDCH2 Indication bit of event input terminal.

| EDCH2 | EDCH1 | Result.                                                        |

|-------|-------|----------------------------------------------------------------|

| 0     | 0     | Events is not detected. (Default)                              |

| 0     | 1     | Event was detected in EVIN1 terminal.                          |

| 1     | 0     | Event was detected in EVIN2 terminal.                          |

| 1     | 1     | Two event was detected in EVIN1 and EVIN2 terminals same time. |

Note: When two signals were input between 7.8ms(Max.), it is judged to be the input of the same time.

#### 9.3.4EDFG bit of event detection function.

| EDFG | result.                      |             |

|------|------------------------------|-------------|

| 0    | Event input is not detected. | (Default 値) |

| 1    | Event input is detected.     |             |

When EDEN bit is 1, event input is detected in High from Low of EVIN terminal (tDB) time later.

After 7.8ms, EDFG bit is set to and INT terminal asserted to Low.

Detected event terminal is memorized in EDCH1,EDCH2.

When detected EVIN1; EDCH1=1, When detected EVIN2; EDCH2=1,

When during time of tDB, EVIN1 and EVIN2 kept high level, then both EDCH1 and EDCH2 are set to 1.

This time is recorded by a time stamp register.

As for the EDFG flag, only clearing to a zero is possible

As for the INT output of event detection, it is assumed that

When EDFG is cleared by zero, INT output is disabled.

Event detection is available in both of VBAT or VDD.

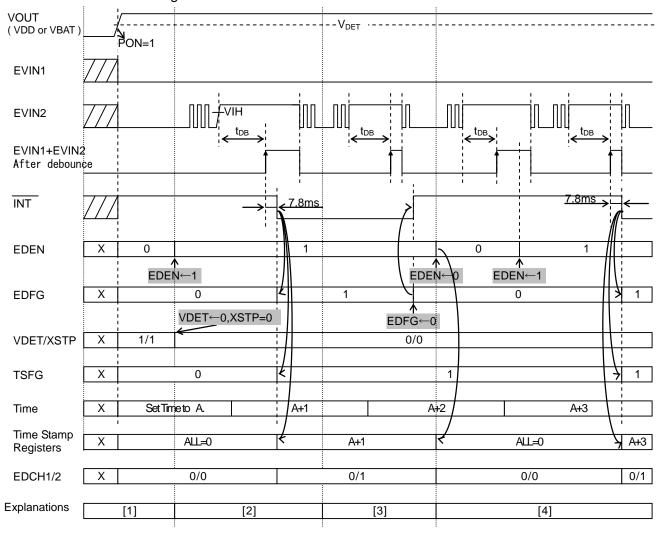

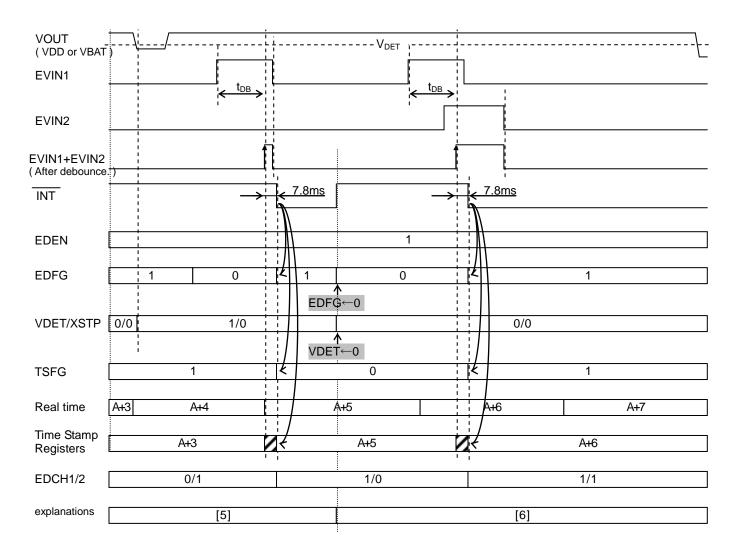

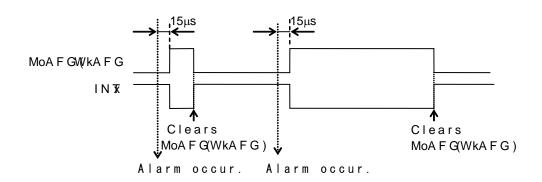

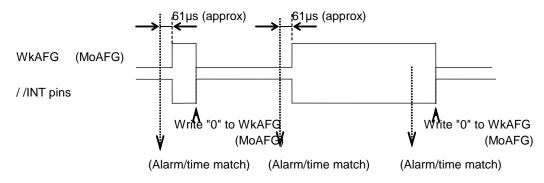

#### 9.3.5 Event detection timing chart.

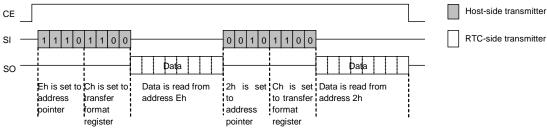

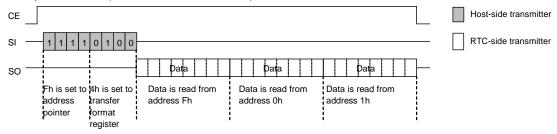

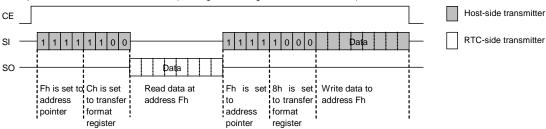

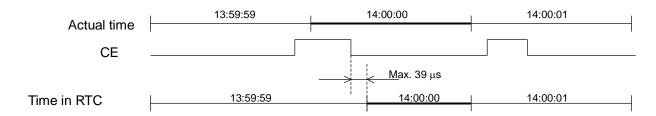

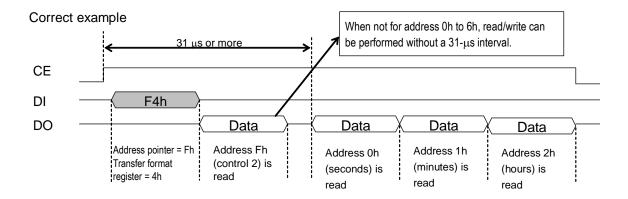

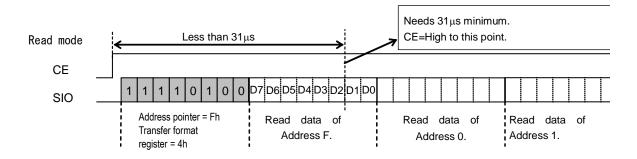

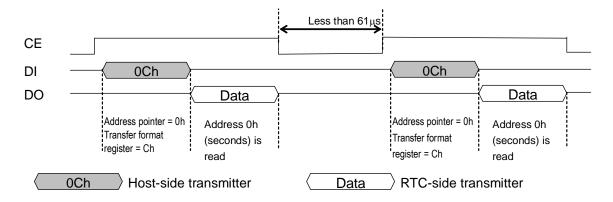

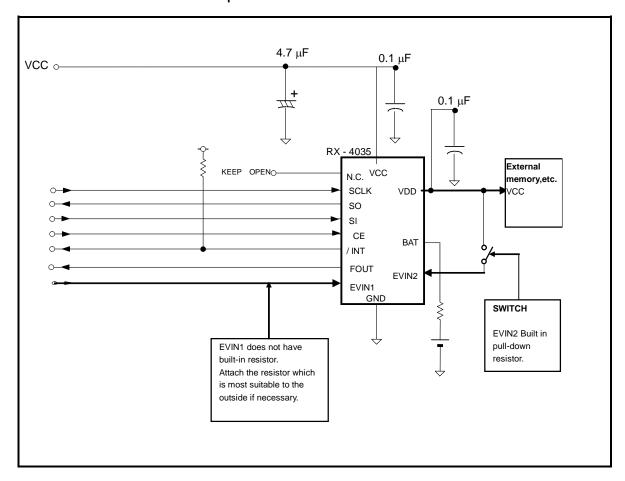

[1]