The PFS1200-12-054xA is a 1200 Watt AC to DC power-factor-corrected (PFC) power supply that converts standard AC or HVDC power into a main output of 12 VDC for powering intermediate bus architectures (IBA) in high performance and reliability servers, routers, and network switches.

Displays the CE-Mark for the European Low Voltage Directive (LVD).

## **Key Features & Benefits**

- Digital inrush current control

- High Efficiency

- Meets 80Plus Platinum efficiency requirement

- Universal input voltage range: 90 305 VAC

- High voltage DC input: 180 400 VDC

- Always-On standby output (model dependent):

- o 3.3 V

- o Programmable 5 V / 12 V

- Hot-plug capable

- Parallel operation with active current sharing

- Digital controls for improved performance

- High density design: 39 W/in<sup>3</sup>

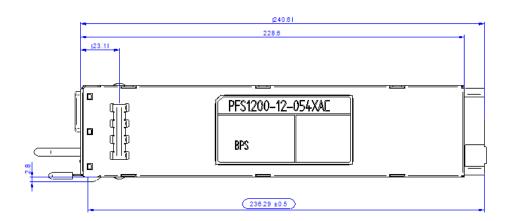

- Small form factor (WxHxL): 54.5 x 40 x 228.6 mm (2.15 x 1.57 x 8.98 in)

- I2C communication interface for control, programming and monitoring with Power Management Bus protocol and PSMI Protocol

- Over temperature, output over voltage and overcurrent protection

- 256 Bytes of EEPROM for user information

- 2 Status LEDs: OK and FAIL with fault signaling

## **Applications**

- High Performance Servers

- Routers

- Switches

### 1. ORDERING INFORMATION

| PFS            | 1200        | -    | 12        | -    | 054   | х                       | Α           | х                                                                                     |

|----------------|-------------|------|-----------|------|-------|-------------------------|-------------|---------------------------------------------------------------------------------------|

| Product Family | Power Level | Dash | V1 Output | Dash | Width | Airflow 1               | Input       | Options                                                                               |

| PFS Front-Ends | 1200 W      |      | 12 V      |      | 54 mm | N: Normal<br>R: Reverse | A: AC Input | blank: C14 Socket <sup>2</sup> C: C16 Socket <sup>2</sup> H: HVDC Socket <sup>3</sup> |

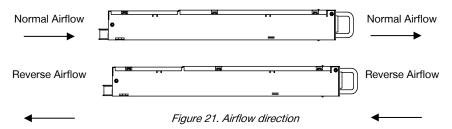

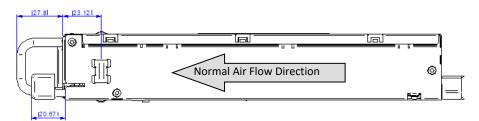

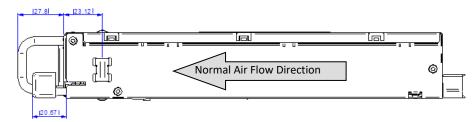

- N = Normal Airflow from Output connector to Input AC socket; R = Reverse Airflow from Input AC socket to Output connector

- C14 / C16 AC input connector, input range 90 ~ 264 VAC and 180 ~ 350 VDC

- Ordering PN: PFS1200-12-054xAH for both AC and HVDC (Anderson 2006G1-BK) input connector, input range is 180 ~ 400 VDC and 90 ~ 305 VAC

### 2. OVERVIEW

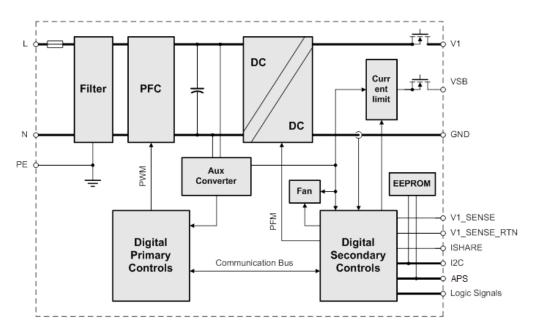

The PFS1200-12-054xA AC/DC power supply is with DSP control, high efficient front-end power supply. It incorporates resonance-soft-switching technology and interleaved power trains to reduce component stresses, providing increased system reliability and very high efficiency. With a wide input operational voltage range and minimal derating of output power with input voltage and temperature, the PFS1200-12-054xA power supply maximizes power availability in demanding server, network, and other high availability applications. The supply is fan cooled and ideally suited for integration with a matching airflow paths. Both the PFC stage and DC/DC stage is with DSP control. The DC/DC stage uses soft switching resonant techniques in conjunction with synchronous rectification. An active OR-ing device on the output ensures no reverse load current and renders the supply ideally suited for operation in redundant power systems. The always-on standby output, provides power to external power distribution and management controllers. It is protected with an active OR-ing device for maximum reliability. Status information is provided with front-panel LEDs. In addition, the power supply can be controlled and the fan speed set via the I2C bus. The I2C bus allows full monitoring of the supply, including input and output voltage, current, power, and inside temperatures. The fan speed is adjusted automatically depending on the actual power demand and supply temperature and can be overridden through the I2C bus.

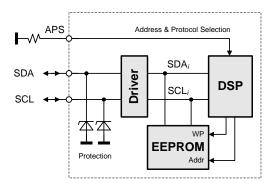

Figure 1. PFS1200-12-054NAH Series Block Diagram

# 3. ABSOLUTE MAXIMUM RATINGS

Stresses in excess of the absolute maximum ratings may cause performance degradation, adversely affect long-term reliability, and cause permanent damage to the supply.

| PARAMETER |               | DESCRIPTION / CONDITION | MIN | NOM MAX | UNIT |

|-----------|---------------|-------------------------|-----|---------|------|

| Vi maxc   | Maximum Input | Continuous              | 90  | 305     | VAC  |

## 4. INPUT SPECIFICATIONS

General Condition: T<sub>A</sub> = 0... 50°C unless otherwise specified.

| PARA               | METER                                                | DESCRIPTION / CONDITION                                                                                                       | MIN  | NOM     | MAX  | UNIT             |

|--------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------------------|

| $V_{inom}$         | Naminal Input Valtage                                |                                                                                                                               | 100  | 115/230 | 277  | VAC              |

| <b>V</b> i nom     | Nominal Input Voltage                                |                                                                                                                               | 200  |         | 380¹ | VDC              |

| $V_i$              | Input Voltage Ranges                                 | Normal operating ( $V_{i min}$ to $V_{i max}$ )                                                                               | 90   |         | 305  | VAC              |

|                    |                                                      |                                                                                                                               | 180  |         | 400  | VDC              |

| I <sub>i max</sub> | Max Input Current                                    |                                                                                                                               |      |         | 16   | A <sub>rms</sub> |

| lip                | Inrush Current Limitation                            | $V_{i min}$ to $V_{i max}$ , $T_{NTC} = 25$ °C(Figure 2)                                                                      |      |         | 60   | Ap               |

| F <sub>i</sub>     | Input Frequency                                      |                                                                                                                               | 47   | 50/60   | 63   | Hz               |

| PF                 | Power Factor                                         | <i>V<sub>i nom</sub></i> , 50 Hz, > 0.3 <i>I<sub>1 nom</sub></i>                                                              | 0.94 |         |      | W/VA             |

| 17                 | T 1 1 1 1 1 1 2                                      | <u> </u>                                                                                                                      | 74   |         | 84   | VAC              |

| Vi on              | V <sub>i on</sub> Turn-on Input Voltage <sup>2</sup> | Ramping up                                                                                                                    | 170  |         | 180  | VDC              |

|                    |                                                      |                                                                                                                               | 72   |         | 80   | VAC              |

| V <sub>i off</sub> | Turn-off Input Voltage                               | Ramping down                                                                                                                  | 168  |         | 178  | VDC              |

|                    |                                                      |                                                                                                                               | 309  |         | 314  | VAC              |

|                    |                                                      | Input Out of Range                                                                                                            | 402  |         | 410  | VDC              |

|                    |                                                      | $V_{115VAC}$ , $0.2 \cdot k_{nom}$ , $V_{x nom}$ , $T_A = 25 ^{\circ}C$                                                       |      | 90      |      |                  |

|                    |                                                      | $V_{115VAC}$ , $0.5\cdot I_{xnom}$ , $V_{xnom}$ , $T_A=25^{\circ}C$                                                           |      | 92      |      |                  |

| ,                  | Efficiency                                           | $V_{\text{i}115 \text{ VAC}}$ , $I_{\text{x} \text{ nom}}$ , $V_{\text{x} \text{ nom}}$ , $T_{\text{A}} = 25^{\circ}\text{C}$ |      | 89      |      |                  |

| η                  | Efficiency                                           | $V_{1230VAC}$ , $0.2 \cdot I_{x \text{ nom}}$ , $V_{x \text{ nom}}$ , $T_{A} = 25^{\circ}C$                                   |      | 90      |      |                  |

|                    |                                                      | $V_{230VAC}$ , $0.5 \cdot k_{nom}$ , $V_{x nom}$ , $T_A = 25 ^{\circ} C$                                                      |      | 94      |      |                  |

|                    |                                                      | $V_{230VAC}$ , $I_{x \text{ nom}}$ , $V_{x \text{ nom}}$ , $T_{A} = 25^{\circ}C$                                              |      | 91      |      |                  |

|                    |                                                      | Vi = 90Vac to 264Vac,V1 ≥ 11.4 V, Cout = 5000 μF, 80% nominal output power, Time from de-                                     |      |         |      |                  |

| T <sub>hold</sub>  | Hold-up Time                                         | assert INPUT_OK to Vout out of regulation or OUTPUT_OK de-asserts                                                             | 5    |         |      | ms               |

Asia-Pacific +86 755 298 85888 **Europe, Middle East** +353 61 225 977

**North America** +1 408 785 5200

For PFS1200-12-054NA/ PFS1200-12-054NAC and PFS1200-12-054RA/ PFS1200-12-054RAC, normal DC operation input range is 200 VDC to 350 VDC; normal AC operation input range is 100 VAC ~ 240 VAC.

The Front-End is provided with a minimum hysteresis of 3 V during turn-on and turn-off within the ranges.

### **4.1 INPUT FUSE**

Slow-acting 16 A input fuse  $(5 \times 20 \text{ mm})$  in series the L line inside the power supply protect against severe defects. The fuse Is not accessible from the outside and are therefore not serviceable parts.

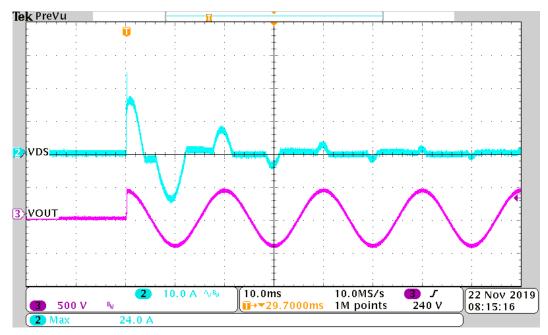

### **4.2 INRUSH CURRENT**

The AC-DC power supply exhibits low X-capacitance resulting in a low and short peak current, when the supply is connected to the mains. The internal bulk capacitor will be charged through an NTC which will limit the inrush current.

**NOTE:** Do not repeat plug-in / out operations within a short time, or else the internal in-rush current limiting device (NTC) may not sufficiently cool down and excessive inrush current or component failure(s) may result.

Figure 2. Inrush current, Vin = 305 Vac, 90°, CH3: Vin (500V/div), CH2: lin (10A/div)

## **4.3 INPUT UNDER-VOLTAGE**

If the sinusoidal input voltage stays below the input under voltage lockout threshold Vi on, the supply will be inhibited. Once the input voltage returns within the normal operating range, the supply will return to normal operation again.

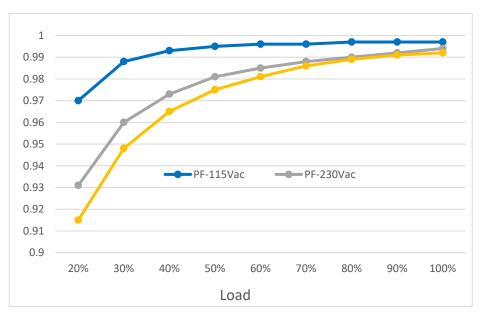

### **4.4 POWER FACTOR CORRECTION**

Power factor correction (PFC) is achieved by controlling the input current waveform synchronously with the input voltage. An analog controller is implemented giving outstanding PFC results over a wide input voltage and load ranges. The input current will follow the shape of the input voltage.

Figure 3. PF vs. Load

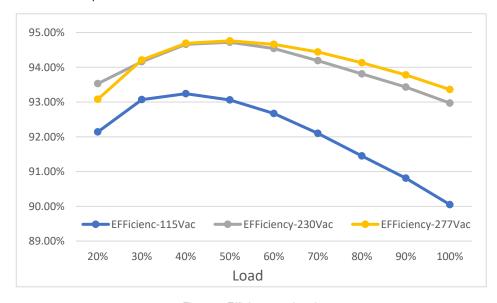

### 4.5 EFFICIENCY

High efficiency is achieved by using state-of-the-art silicon power devices in conjunction with soft-transition topologies minimizing switching losses and a full digital control scheme. Synchronous rectifiers on the output reduce the losses in the high current output path. The speed of the fan is digitally controlled to keep all components at an optimal operating temperature regardless of the ambient temperature and load conditions.

Figure 4. Efficiency vs. Load

# 5. OUTPUT SPECIFICATIONS

General Condition: Ta = 0...50°C unless otherwise specified.

| PARAME                  | TER                                           | DESCRIPTION / CONDITION                                                                                                                     | MIN  | NOM      | MAX   | UNIT                  |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-----------------------|

| Main Outp               |                                               | DESCRIPTION / SOMBITION                                                                                                                     |      |          |       |                       |

| V <sub>1 nom</sub>      | Nominal Output Voltage                        | 0.5.7 T 25.9C                                                                                                                               |      | 12.0     |       | VDC                   |

| V <sub>1 set</sub>      | Output Setpoint<br>Accuracy                   | $0.5 \cdot h_{\text{nom}}, \ T_{\text{amb}} = 25  ^{\circ}\text{C}$                                                                         | -0.5 |          | +0.5  | % V <sub>1 nom</sub>  |

| dV <sub>1 tot</sub>     | Total Regulation                              | $V_{1min}$ to $V_{1max},$ 0 to 100% $H_{1nom},$ $T_{amin}$ to $T_{amax}$                                                                    | -2   |          | +2    | % 1/ <sub>1 nom</sub> |

| P <sub>1 nom</sub>      | Nominal Output Power                          | $305 \text{ VAC} > V_{\text{in}} \ge 90 \text{ VAC}, V_1 = 12 \text{ VDC}$                                                                  |      | 1200     |       | W                     |

|                         | Refer to <i>Figure 6b</i> for derating curves | 400 VDC > 1/1n ≥180 VDC, 1/1 = 12 VDC                                                                                                       |      | 1200     |       | W                     |

| I <sub>1 nom</sub>      | Nominal Output Current                        | $305 \text{ VAC} > V_{10} \ge 90 \text{ VAC}, V_{11} = 12 \text{ VDC}$                                                                      |      | 100      |       | ADC                   |

|                         | Refer to Figure 3b/3c for derating curves     | 400 VDC > V <sub>in</sub> ≥180 VDC, V <sub>1</sub> = 12 VDC                                                                                 |      | 100      |       | ADC                   |

| V1 pp                   | Output Ripple Voltage                         | $V_{1 \text{ nom}}$ , 0 to100% $h_{1 \text{ nom}}$ , 20 MHz BW (See Section 5.1)                                                            |      |          | 120   | mVpp                  |

| $dV_{1 Load}$           | Load Regulation                               | $V_i = V_{i \text{ nom}}, 0 - 100 \% I_{i \text{ nom}}$                                                                                     |      | 80       |       | mV                    |

| dV₁ Line                | Line Regulation                               | $V_i = V_{i \text{ min}} V_{i \text{ max}}$                                                                                                 |      | 40       |       | mV                    |

| dl <sub>share</sub>     | Current Sharing                               | Deviation from $h$ tot / N, $h$ > 10%                                                                                                       | -3   |          | +3    | Α                     |

| dV <sub>dyn</sub>       | Dynamic Load Regulation                       | $\Delta h = 50\% \ h_{\text{nom}}, \ h = 10 \dots 100\% \ h_{\text{nom}}, \ dh/dt = 1A/\mu s$                                               | -0.6 |          | 0.6   | V                     |

| $T_{rec}$               | Recovery Time                                 | $\Delta h = 50\% \ h_{\text{nom}}, \ h = 10 \dots 100\% \ h_{\text{nom}},$<br>$dh/dt = 1A/\mu s$ , recovery within 1% of $V_{1 \text{nom}}$ |      |          | 2     | ms                    |

| tac v1                  | Start-up Time from AC                         |                                                                                                                                             |      |          | 3     | sec                   |

| t <sub>V1 rise</sub>    | Rise Time                                     | $V_1 = 1090\% \ V_{1 \text{ nom}}$                                                                                                          | 0.5  |          | 10    | ms                    |

| $C_{Load}$              | Capacitive Loading                            | $T_a = 25$ °C                                                                                                                               | 1000 |          | 20000 | μF                    |

| 3.3/5 V <sub>SB</sub> S | Standby Output                                |                                                                                                                                             |      |          |       |                       |

| V <sub>SB nom</sub>     | Nominal Output Voltage                        | VSB_SEL1 = 0<br>VSB_SEL2 = 0<br>VSB_SEL1 = 1                                                                                                |      | 3.3      |       | VDC                   |

|                         |                                               | VSB_SEL1 = 1<br>VSB_SEL2 = 0                                                                                                                |      | 5.0      |       | VDC                   |

| V <sub>SB set</sub>     | Output Setpoint<br>Accuracy                   | $0.5 \cdot k_{\text{SB nom}}, T_{\text{amb}} = 25^{\circ}\text{C}$                                                                          | -0.5 |          | +0.5  | % V <sub>1nom</sub>   |

| dV <sub>SB tot</sub>    | Total Regulation                              | $V_{imin}$ to $V_{imax}$ , 0 to 100% $I_{SBnom}$ , $T_{amin}$ to $T_{amax}$                                                                 | -5   |          | +5    | % V <sub>SBnom</sub>  |

| P <sub>SB nom</sub>     | Nominal Output Power                          | V <sub>SB</sub> = 3.3 VDC,                                                                                                                  |      | 16.5     |       | W                     |

| 1 SB HOITI              | Nominal Output Fower                          | $V_{SB} = 5.0 \text{ VDC},$                                                                                                                 |      | 16.5     |       | **                    |

| I <sub>SB nom</sub>     | Nominal Output Current                        | V <sub>SB</sub> = 3.3 VDC,<br>V <sub>SB</sub> = 5.0 VDC.                                                                                    |      | 5<br>3.3 |       | ADC                   |

| V <sub>SB pp</sub>      | Output Ripple Voltage                         | V <sub>SB nom</sub> , k <sub>SB nom</sub> , 20 MHz BW (See Section 5.1)                                                                     |      | 0.0      | 50    | mVpp                  |

|                         |                                               | VSB_SEL1 = 0, VSB_SEL2 = 0                                                                                                                  | 5.25 |          | 6.5   |                       |

| I <sub>SB max</sub>     | Current Limitation                            | VSB_SEL1 = 1, VSB_SEL2 = 0                                                                                                                  | 3.45 |          | 4.3   | ADC                   |

| $dV_{SBdyn}$            | Dynamic Load Regulation                       | $\Delta k_{\rm SB} = 50\% k_{\rm SB\ nom}, k_{\rm SB} = 5 \dots 100\% k_{\rm SB\ nom},$                                                     | -5   |          | 5     | % V <sub>SBnom</sub>  |

| Trec                    | Recovery Time                                 | $d\hbar/dt = 0.5 \text{ A/}\mu\text{s}$ , recovery within 1% of $\nu_{1 \text{ nom}}$                                                       |      |          | 250   | μs                    |

| t <sub>AC VSB</sub>     | Start-up Time from AC                         | V <sub>SB</sub> = 90% V <sub>SB nom</sub>                                                                                                   |      |          | 2     | sec                   |

| t/VSB rise              | Rise Time                                     | V <sub>SB</sub> = 1090% V <sub>SB nom</sub>                                                                                                 | 0.5  |          | 30    | ms                    |

| $G_{Load}$              | Capacitive Loading                            | $T_{\text{amb}} = 25^{\circ}\text{C}$                                                                                                       | 100  |          | 1,500 | μF                    |

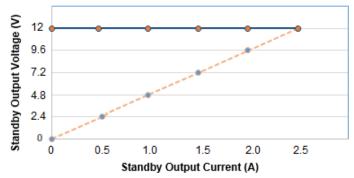

| 12 V <sub>SB</sub> St | andby Output             |                                                                    |                                 |      |    |       |                       |

|-----------------------|--------------------------|--------------------------------------------------------------------|---------------------------------|------|----|-------|-----------------------|

| V <sub>SB nom</sub>   | Nominal Output Voltage   | $0.5 \cdot I_{SB \text{ nom}}, T_{amb} = 25^{\circ}C$              | VSB_SEL1 = 0                    |      | 12 |       | VDC                   |

| V <sub>SB set</sub>   | Output Setpoint Accuracy |                                                                    | VSB_SEL2 = 1                    | -1   |    | +1    | % V <sub>SB nom</sub> |

| dV <sub>SB tot</sub>  | Total Regulation         | $V_{i  min}$ to $V_{i  max}$ , 0 to 100% $I_{SB  noi}$             | m, $T_{a  min}$ to $T_{a  max}$ | -5   |    | +5    | % V <sub>SB nom</sub> |

| P <sub>SB nom</sub>   | Nominal Output Power     | V <sub>SB</sub> = 12 VDC                                           |                                 |      | 24 |       | W                     |

| I <sub>SB nom</sub>   | Nominal Output Current   | V <sub>SB</sub> = 12 VDC                                           |                                 |      |    | 2     | Α                     |

| V <sub>SB pp</sub>    | Output Ripple Voltage    | VSB nom, ISB nom, 20 MHz BW (S                                     | ee Section 5.1)                 |      |    | 120   | mVpp                  |

| I <sub>SB max</sub>   | Current Limitation       |                                                                    |                                 | 2.1  |    | 2.6   | ADC                   |

| dV <sub>SBdyn</sub>   | Dynamic Load Regulation  | $\Delta k_{\rm SB} = 50\% k_{\rm SB  nom}, k_{\rm SB} = 5 \dots 1$ | 00% I <sub>SB nom</sub> ,       | -0.6 |    | 0.6   | V                     |

| Trec                  | Recovery Time            | $d\hbar/dt = 1 A/\mu s$ , recovery within                          | n 1% of V <sub>1 nom</sub>      |      |    | 2     | ms                    |

| tac vsb               | Start-up Time from AC    | $V_{SB} = 90\% V_{SB nom}$                                         |                                 |      |    | 2     | s                     |

| t√SB rise             | Rise Time                | V <sub>SB</sub> = 1090% V <sub>SB nom</sub>                        |                                 |      |    | 20    | ms                    |

| $C_{Load}$            | Capacitive Loading       | $T_{amb} = 25^{\circ}C$                                            |                                 | 100  |    | 1,500 | μF                    |

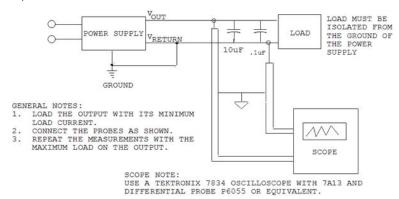

#### **5.1 OUTPUT VOLTAGE RIPPLE**

Internal capacitance at the 12 V output (behind the OR-ing circuitry) is minimized to prevent disturbances during hot plug. In order to provide low output ripple voltage in the application, external capacitors (a parallel combination of 10  $\mu$ F low ESR capacitor in parallel with 0.1  $\mu$ F ceramic capacitors) should be added close to the power supply output. The setup of *Figure* has been used to evaluate suitable capacitor types.

Table 1 and Table 2 should be used to reduce the output ripple voltage. The ripple voltage is measured with 20 MHz BWL, close to the external capacitors.

Figure 5. Output ripple test setup

**NOTE:** Care must be taken when using ceramic capacitors with a total capacitance of 1 μF to 50 μF on output V1, due to their high quality factor the output ripple voltage may be increased in certain frequency ranges due to resonance effects.

| EXTERNAL CAPACITOR V1                   | DV1MAX | UNIT |

|-----------------------------------------|--------|------|

| Standard test condition:                |        |      |

| 1 Pc 10 µF / min 16 V low ESR Capacitor | 120    | mVpp |

| 1 pc 0.1 uF / 50 V ceramic capacitor    |        |      |

| EXTERNAL CAPACITOR VSB                  | DV1MAX | UNIT |

|-----------------------------------------|--------|------|

| Standard test condition:                |        |      |

| 1 pc 10 μF / min 16 V low ESR Capacitor | 120    | mVpp |

| 1 pc 0.1 μF / 50V ceramic capacitor     |        |      |

Table 1. Suitable capacitors for V<sub>1</sub>

Table 2. Suitable capacitors for VSB

The output ripple voltage on  $V_{SB}$  is influenced by the main output  $V_1$ . Evaluating  $V_{SB}$  output ripple must be done when maximum load is applied to  $V_1$ .

### 6. PROTECTION SPECIFICATIONS

| PARAM               | METER                             | DESCRIPTION / CONDITION                                                                                                          | MIN                 | NOM | MAX               | UNIT |

|---------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------------------|------|

| F                   | Input Fuse (L)                    | Not user accessible                                                                                                              |                     | 16  |                   | Α    |

| <b>V</b> ₁ ov       | OV Threshold 1/4                  |                                                                                                                                  | 13.3                |     | 14.5              | VDC  |

| <i>t</i> ov v1      | OV Latch Off Time V <sub>1</sub>  |                                                                                                                                  |                     |     | 1                 | ms   |

| <b>V</b> SB OV      | OV Threshold VsB                  |                                                                                                                                  | 110%                |     | 120%              | VDC  |

| t <sub>OV VSB</sub> | OV Latch Off Time V <sub>SB</sub> |                                                                                                                                  |                     | 1   |                   | ms   |

| √₁ lim              | Over Current Limitation $V_1$     | $V_i > 90 \text{ VAC}, \ T_a < 50^{\circ}\text{C}$                                                                               | 110                 |     | 140               | Α    |

| IVSB lim            | Over Current Limitation VsB       | $T_{\rm a}$ < 50°C for 12V <sub>SB</sub><br>$T_{\rm a}$ < 50°C for 5V <sub>SB</sub><br>$T_{\rm a}$ < 50°C for 3.3V <sub>SB</sub> | 2.1<br>3.45<br>5.25 |     | 2.6<br>4.3<br>6.5 | Α    |

| t√1 sc              | Short Circuit Regulation Time     | $V_1 < 3 \text{ V}$ , time until $\mathcal{U}_1$ is limited to $< 200 \text{ A}$                                                 |                     |     | 2                 | ms   |

| T <sub>SD</sub>     | Over Temperature on Heat Sinks    | Automatic shut-down                                                                                                              |                     | 115 | 120               | °C   |

### **6.1 OVERVOLTAGE PROTECTION**

The PFS front-ends provide a fixed threshold overvoltage (OV) protection implemented with a HW comparator. Once an OV condition has been triggered, the supply will shut down and latch the fault condition. The latch can be unlocked by disconnecting the supply from the AC mains or by toggling the PSON\_L input

### **6.2 UNDERVOLTAGE DETECTION**

Both main and standby outputs are monitored. LED and PWOK\_L pin signal if the output voltage exceeds  $\pm 7\%$  of its nominal voltage. Output under voltage protection is provided on both outputs. When either V1 or VSB falls below 93% of its nominal voltage, the output is inhibited.

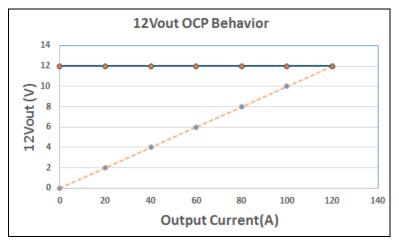

# **6.3 CURRENT LIMITATION**

### **6.3.1 MAIN OUTPUT**

When main output runs in current limitation mode its output will turn OFF below 2 V but will shut down after 6 attempts. If current limitation mode is still present after the unit retry, output will continuously perform this routine until current is below the current limitation point. The supply will go through soft start every time it retries from current limitation mode.

Figure 6a. Current Limitation on  $V_1$  ( $V_i = 230 \text{ VAC}$ )

**Output Power Derating Curve with Ambient Temperature** 1400 1200 NA Vin=90~132Vac RA Vin=90~132Vac NA Vin≥180Vac/180Vdc RA Vin≥180Vac/180Vdc 200 0 30 65 -5 0 10 20 40 45 50 55 60 **Ambient Temperature(°C)**

The output power derating of V1 refers to Figure 6b Ambient Derating Curve.

Figure 6b. Ambient Derating Curve

#### Note:

- 1. NA: Normal Airflow RA: Reverse Airflow Refer to Figure 21.

- 2. The application of power supply should also refer to installation instructions document

- 3. The power supply has no limitation on its output current/power in the respect of meeting the operating conditions shown by the derating limits shown above. It is the responsibility of the end user to ensure operating conditions are maintained within their safety agency certification limits to assure safe and reliable operation.

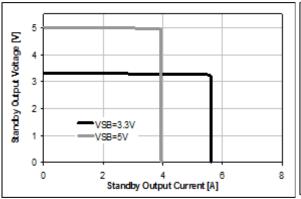

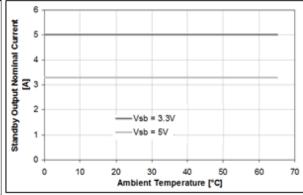

## **6.3.2 STANDBY OUTPUT**

### 3.3 / 5 V<sub>SB</sub>

The standby output exhibits a substantially rectangular output characteristic down to 0 V (no hiccup mode / latch off). If it runs in current limitation and its output voltage drops below the UV threshold, then the main output will be inhibited (standby remains on). The current limitation of the standby output is independent of the AC input voltage.

Figure 7. Current Limitation and Temperature Derating on 3.3 / 5 V<sub>SB</sub>

**Asia-Pacific** +86 755 298 85888 **Europe, Middle East** +353 61 225 977

North America +1 408 785 5200

### 12 V<sub>SB</sub>

On the standby output, a hiccup type over current protection is implemented. This protection will shut down the standby output immediately when standby current reaches or exceeds  $k_{SB \text{ lim}}$ . After an off-time of 1 s the output automatically tries to restart. If the overload condition is removed the output voltage will reach again its nominal value. At continuous overload condition the output will repeatedly trying to restart with 1s intervals. A failure on the Standby output will shut down both Main and Standby outputs.

Figure 8. Current Limitation on 12 V<sub>SB</sub>

# 7. MONITORING

| PARAMETER              | DESCRIPTION / CONDIT   | ON                                      | MIN N | OM MAX | UNIT |

|------------------------|------------------------|-----------------------------------------|-------|--------|------|

| $V_{\rm imon}$         | Input RMS Voltage      | $V_{i \min} \leq V_{i} \leq V_{i \max}$ | -2.5  | +2.5   | %    |

| / <sub>i mon</sub>     | Input RMS Current      | / <sub>i</sub> > 2 A <sub>rms</sub>     | -5    | +5     | %    |

| $P_{i  mon}$           | True Input Power       | $I_i > 2 A_{rms}$                       | -5    | +5     | %    |

| V₁ mon                 | V <sub>1</sub> Voltage |                                         | -2    | +2     | %    |

| ∕t mon                 | V <sub>1</sub> Current | I1 > 25 A                               | -2    | +2     | %    |

| л mon                  |                        | I1 ≤ 25 A                               | -1    | +1     | Α    |

| Po nom                 | Total Output Power     | Po > 120 W                              | -5    | +5     | %    |

| Po nom                 | Total Output Power     | Po ≤ 120 W                              | -12   | +12    | W    |

| $V_{\mathrm{SB\ mon}}$ | Standby Voltage        |                                         | -0.5  | +0.5   | V    |

| SB mon                 | Standby Current        | I <sub>SB</sub> ≤ I <sub>SB nom</sub>   | -0.5  | +0.5   | А    |

## 8. SIGNAL & CONTROL SPECIFICATIONS

## **8.1 ELECTRICAL CHARACTERISTICS**

| PARAMETER                    | DESCRIPTION / CONDITION                  |                                  | MIN  | NOM  | MAX | UNIT |

|------------------------------|------------------------------------------|----------------------------------|------|------|-----|------|

| PSKILL_H / PSON              | _L / HOTSTANDBYEN_H Inputs               |                                  |      |      |     |      |

| ИL                           | Input Low Level Voltage                  |                                  | -0.2 |      | 0.8 | V    |

| Ин                           | Input High Level Voltage                 |                                  | 2.4  |      | 3.5 | V    |

| <b>ſ</b> L, H                | Maximum Input Sink or Source Current     |                                  | 0    |      | 1   | mA   |

| $R_{ m pupskill\_H}$         | Internal Pull Up Resistor on PSKILL_H    |                                  |      | 20   |     | kΩ   |

| $R_{ m puPSON\_L}$           | Internal Pull Up Resistor on PSON_L      |                                  |      | 10   |     | kΩ   |

| $R_{ m puhotstandbyen_h}$    | Internal Pull Up Resistor on HOTSTANDB   | YEN_H                            |      | 2    |     | kΩ   |

| <i>R</i> Low                 | Resistance Pin to SGND for Low Level     |                                  | 0    |      | 1   | kΩ   |

| <i>R</i> HIGH                | Resistance Pin to SGND for High Level    |                                  | 50   |      |     | kΩ   |

| PWOK_H Output                |                                          |                                  |      |      |     |      |

| <b>V</b> oL                  | Output Low Level Voltage                 | $J_{\text{sink}} < 4 \text{ mA}$ | 0    |      | 0.4 | V    |

| V <sub>OH</sub>              | Output High Level Voltage                | $I_{\rm source}$ < 0.5 mA        | 2.6  |      | 3.5 | V    |

| R <sub>puPWOK_H</sub>        | Internal Pull Up Resistor on PWOK_H      |                                  |      | 1    |     | kΩ   |

| ACOK_H Output                |                                          |                                  |      |      |     |      |

| <b>V</b> oL                  | Output Low Level Voltage                 | J <sub>sink</sub> < 2 mA         | 0    |      | 0.4 | V    |

| <b>V</b> он                  | Output High Level Voltage                | $I_{\rm source} < 50~\mu A$      | 2.6  |      | 3.5 | V    |

| <i>R</i> <sub>puACOK_H</sub> | Internal Pull Up Resistor on ACOK_H      |                                  |      | 1    |     | kΩ   |

| SMB_ALERT_L Oเ               | utput                                    |                                  |      |      |     |      |

| $V_{ m ext}$                 | Maximum External Pull Up Voltage         |                                  |      |      | 12  | V    |

| <b>V</b> oL                  | Output Low Level Voltage                 | / <sub>source</sub> < 4 mA       | 0    |      | 0.4 | V    |

| <b>Ю</b> Н                   | Maximum High Level Leakage Current       |                                  |      |      | 10  | μΑ   |

| $R_{ m puSMB\_ALERT\_L}$     | Internal Pull Up Resistor on SMB_ALERT_L |                                  |      | None |     | kΩ   |

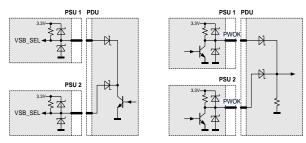

## **8.2 INTERFACING WITH SIGNALS**

All signal pins have protection diodes implemented to protect internal circuits. When the power supply is not powered, the protection devices start clamping at signal pin voltages exceeding ±0.5 V. Therefore, all input signals should be driven only by an open collector/drain to prevent back feeding inputs when the power supply is switched off. If interconnecting of signal pins of several power supplies is required, then this should be done by decoupling with small signal schottky diodes except for SMB\_ALERT\_L, ISHARE and I<sup>2</sup>C pins. SMB\_ALERT\_L pins can be interconnected without decoupling diodes, since these pins have no internal pull up resistor and use a 15 V zener diode as protection device against positive voltage on pins. ISHARE pins must be interconnected without any additional components. This in-/output is disconnected from internal circuits when the power supply is switched off.

Figure 9. Interconnection of Signal Pins

**Asia-Pacific** +86 755 298 85888

**Europe, Middle East** +353 61 225 977

North America +1 408 785 5200

# **8.3 FRONT LEDS**

There will be 2 Bi-color (Green/ Amber) LED to indicate power supply status. The LED are visible on the power supply's exterior face. The LED location meets ESD Requirements. Following are these definitions as:

| LED FUNCTION    | COLOR                                                                        | BRIGHTNESS     |

|-----------------|------------------------------------------------------------------------------|----------------|

| Input AC        | Green (520 nm – 540 nm)                                                      | 500-1000cd/m^2 |

| Output DC/Fault | Green (520 nm – 540 nm) / Amber (520 nm – 540 nm)<br>Amber (587 nm – 595 nm) | 500-1000cd/m^2 |

| COMMAND NAME              | OUTPUT V | OLTAGE STATUS | LED BEHAVIOR CO | LOR/BLINKING/SOLID/OFF |

|---------------------------|----------|---------------|-----------------|------------------------|

| CONDITION                 | VOUT (V) | VSTBY (V)     | INPUT           | OUTPUT/FAULT           |

| VOUT Normal Operation     | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | GREEN SOLID            |

| VOUT_OV_FAULT_LIMIT       | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| VOUT_OV_WARN_LIMIT        | 13.5     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| VSTBY_OV_FAULT_LIMIT      | 12.00    | 0.00          | GREEN SOLID     | AMBER SOLID            |

| VSTBY_OV_WARN_LIMIT       | 12.00    | 3.7/5.6/13.5  | GREEN SOLID     | AMBER BLINKING         |

| VOUT_UV_FAULT_LIMIT       | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| VOUT_UV_WARN_LIMIT        | 11.40    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| VSTBY_UV_FAULT_LIMIT      | 12.00    | 0.00          | GREEN SOLID     | AMBER SOLID            |

| VSTBY_UV_WARN_LIMIT       | 12.00    | 3.0/4.5/11.0  | GREEN SOLID     | AMBER BLINKING         |

| IOUT_OC_FAULT_LIMIT       | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| IOUT_OC_WARN_LIMIT        | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| ISTBY_OC_FAULT_LIMIT      | 12.00    | 0.00          | GREEN SOLID     | AMBER SOLID            |

| ISTBY_OC_WARN_LIMIT       | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| TEMPERATURE WARNING LIMIT | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| TEMPERATURE FAULT LIMIT   | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| VIN_OV_FAULT_LIMIT        | 0.00     | 3.3/5.0/12.0  | GREEN BLINKING  | AMBER SOLID            |

| VIN_OV_WARN_LIMIT         | 12.00    | 3.3/5.0/12.0  | GREEN BLINKING  | AMBER BLINKING         |

| VIN_UV_FAULT_LIMIT        | 0.00     | 0.00          | OFF             | OFF                    |

| VIN_UV_WARN_LIMIT         | 12.00    | 3.3/5.0/12.0  | GREEN BLINKING  | AMBER BLINKING         |

| IIN_OC_FAULT_LIMIT        | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| IIN_OC_WARN_LIMIT         | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| FAN_1_FAULT               | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| FAN_1_WARNING             | 12.00    | 3.3/5.0/12.0  | GREEN SOLID     | AMBER BLINKING         |

| IOUT SHORT CIRCUIT        | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | AMBER SOLID            |

| ISTBY SHORT CIRCUIT       | 12.00    | 0.00          | GREEN SOLID     | AMBER SOLID            |

| PS_ON High                | 0.00     | 3.3/5.0/12.0  | GREEN SOLID     | GREEN BLINKING         |

| PS_Kill                   | 0.00     | 0.00          | GREEN SOLID     | OFF                    |

Table 3. LED Status

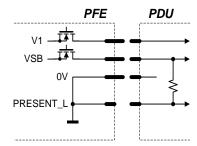

### 8.4 PRESENT L

This signaling pin is recessed within the connector and will contact only once all other connector contacts are closed. This active-low pin is used to indicate to a power distribution unit controller that a supply is plugged in. The maximum current on PRESENT\_L pin should not exceed 10 mA.

Figure 10. PRESENT\_L signal pin

## **8.5 PSKILL H INPUT**

The PSKILL\_H input is active-high and is located on a recessed pin on the connector and is used to disconnect the main output as soon as the power supply is being plugged out. This pin should be connected to SGND in the power distribution unit. The standby output will remain on regardless of the PSKILL\_H input state.

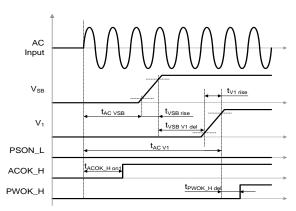

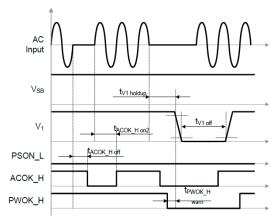

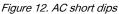

## 8.6 AC TURN-ON / DROP-OUTS / ACOK\_H

The power supply will automatically turn-on when connected to the AC line under the condition that the PSON\_L signal is pulled low and the AC line is within range. The ACOK\_H signal is active-high. See the timing diagram, *Figure 11* and *Table 4*.

| OPERATIN                | G CONDITION                           | MIN | MAX  | UNIT |

|-------------------------|---------------------------------------|-----|------|------|

| t <sub>AC VSB</sub>     | AC Line to 90% V/SB                   |     | 2    | sec  |

| t <sub>AC V1</sub>      | AC Line to 90% V <sub>1</sub>         |     | 2    | sec  |

| tACOK_H on1             | ACOK_H signal on delay (start-up)     |     | 2000 | ms   |

| tACOK_H on2             | ACOK_H signal on delay (dips)         |     | 100  | ms   |

| tACOK_H off             | ACOK_H signal off delay               |     | 5    | ms   |

| t <sub>VSB V1 del</sub> | $V_{\rm SB}$ to $V_{\rm 1}$ delay     | 10  | 500  | ms   |

| t√1 holdup              | Effective $V_1$ holdup time           | 5   |      | ms   |

| t/SB holdup             | Effective V <sub>SB</sub> holdup time | 20  |      | ms   |

| t <sub>ACOK_H V1</sub>  | ACOK_H to V₁ holdup                   | 5   |      | ms   |

| tacok_h vsb             | ACOK_H to VsB holdup                  | 15  |      | ms   |

| t√1 off                 | Minimum $V_1$ off time                | 1   | 2    | sec  |

| t/SB off                | Minimum V <sub>SB</sub> off time      | 1   | 2    | sec  |

NOTE: AC short dips means below 10 ms; AC long dips means 10 ms to 100 ms

Table 4. AC Turn-on / Dip Timing

Figure 11. AC turn-on timing

Figure 13. AC long dips

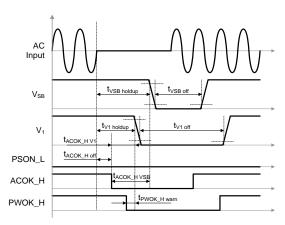

# 8.7 PSON\_L INPUT

The PSON\_L is an internally pulled-up (3.3 V) input signal to enable/disable the main output V1 of the front-end. This active-low pin is also used to clear any latched fault condition, see the parameters in *Table 5*.

| OPERATING CONDITION      |                            | MIN | MAX | UNIT |

|--------------------------|----------------------------|-----|-----|------|

| t <sub>PSON_L V1on</sub> | PSON_L to $V_1$ delay (on) | 2   | 20  | ms   |

| tPSON_L V1off            | PSON_L to 1/1 delay (off)  | 2   | 20  | ms   |

| tPSON_L H min            | PSON_L minimum High time   | 10  |     | ms   |

Table 5. PSON\_L timing

## 8.8 PWOK\_H SIGNAL

The PWOK\_H is an open drain output with an internal pull-up to 3.3 V indicating whether both  $V_{SB}$  and  $V_1$  outputs are within regulation. This pin is active-low. The timing diagram is shown in *Figure 14* and referenced in the *Table 6*.

Figure 14. PSON\_L and PWOK\_H turn-on/off timing

| OPERATING               | G CONDITION                                                               | MIN        | MAX      | UNIT     |

|-------------------------|---------------------------------------------------------------------------|------------|----------|----------|

| t <sub>PWOK_H del</sub> | PWOK_H to $V_1$ delay (on)                                                | 100        | 500      | ms       |

|                         | PWOK_H to V₁ delay (off) caused by:                                       |            |          |          |

|                         | PSKILL_H                                                                  | 0          | 1        | ms       |

| tpwok_H warn*           | PSON_L, OT, Fan Failure<br>ACOK_H (time change with loading<br>condition) | 0.5<br>0.5 | 5<br>100 | ms<br>ms |

| LPWOK_H warn            | UV and OV on VSB                                                          | 1          | 30       | ms       |

|                         | OC on V1 (Software trigger)                                               | -11        | 0        | ms       |

|                         | OC on V1 (Hardware trigger)                                               | -1         | 0        | ms       |

|                         | OV on V1                                                                  | -3         | 0        | ms       |

<sup>\*</sup> A positive value means a warning time, a negative value a delay (after fact).

Table 6. PWOK\_H timing

## 8.9 VSB VOLTAGE SELECTION (VSB\_SEL1, VSB\_SEL2)

The standby output voltage can be configured to three different values: 3.3V, 5V and 12V by pulling VSB\_SEL1 and VSB\_SEL2 input pins either to GND (Logic Low) or to 3.3V

| VSB_SEL1 | VSB_SEL2 | VSB Voltage   | UNIT |

|----------|----------|---------------|------|

| 0        | 0        | 3.3           | V    |

| 1        | 0        | 5             | V    |

| 0        | 1        | 12            | V    |

| 1        | 1        | Invalid (Off) |      |

Table 6. VSB Voltage selection

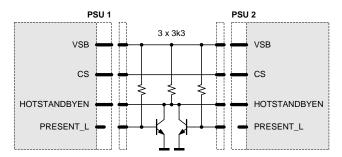

### **8.10 CURRENT SHARE**

The PFS front-ends have an active current share scheme implemented for  $V_1$ . All the ISHARE current share pins need to be interconnected in order to activate the sharing function. If a supply has an internal fault or is not turned on, it will disconnect its ISHARE pin from the share bus. This will prevent dragging the output down (or up) in such cases.

The current share function uses a analog bi-directional data exchange on a recessive bus configuration to transmit and receive current share information. The controller implements a Master/Slave current share function. The power supply providing the largest current among the group is automatically the Master. The other supplies will operate as Slaves and increase their output current to a value close to the Master by slightly increasing their output voltage. The voltage increase is limited to +250 mV.

The standby output uses a passive current share method (droop output voltage characteristic).

#### 8.11 SENSE INPUTS

Main output has sense lines implemented to compensate for voltage drop on load wires (no sense lines for 12VSB). The maximum allowed voltage drop is 200 mV on the positive rail and 100 mV on the PGND rail.

With open sense inputs the main output voltage will rise by 270 mV. Therefore, if not used, these inputs should be connected to the power output and PGND close to the power supply connector. The sense inputs are protected against short circuit. In this case the power supply will shut down.

### **8.12 HOT-STANDBY OPERATION**

The hot-standby operation is an operating mode allowing to further increase efficiency at light load conditions in a redundant power supply system. Under specific conditions one of the power supplies is allowed to disable its DC/DC stage. This will save the power losses associated with this power supply and at the same time the other power supply will operate in a load range having a better efficiency. In order to enable the hot standby operation, the HOTSTANDBYEN\_H and the ISHARE pins need to be interconnected. A power supply will only be allowed to enter the hot-standby mode, when the HOTSTANDBYEN\_H pin is high, the load current is low and the supply was allowed to enter the hot-standby mode by the system controller via the appropriate I<sup>2</sup>C command (by default disabled). The system controller needs to ensure that only one of the power supplies is allowed to enter the hot-standby mode.

If a power supply is in a fault condition, it will pull low its active-high HOTSTANDBYEN\_H pin which indicates to the other power supply that it is not allowed to enter the hot-standby mode or that it needs to return to normal operation should it already have been in the hot-standby mode.

NOTE: The system controller needs to ensure that only one of the power supplies is allowed to enter the hot-standby model.

Figure 15. Recommended hot-standby configuration

In order to prevent voltage dips when the active power supply is unplugged while the other is in hot-standby mode, it is strongly recommended to add the external circuit as shown in15. If the PRESENT\_L pin status needs also to be read by the system controller, it is recommended to exchange the bipolar transistors with small signal MOS transistors or with digital transistors.

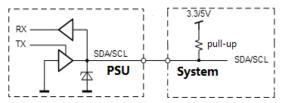

### 8.13 I2C / SMBUS COMMUNICATION

The interface driver in the PFS supply is referenced to the V1 Return. The PFS supply is a communication Slave device only; it never initiates messages on the I2C/SMBus by itself. The communication bus voltage and timing is defined in Table 7 further characterized through:

- There are no internal pull-up resistors

- The SDA/SCL IOs are 3.3/5 V tolerant

- Full SMBus clock speed of 100 kbps

- Clock stretching limited to 1 ms

- SCL low time-out of >25 ms with recovery within 10 ms

- Recognizes any time Start/Stop bus conditions

Figure 16. Physical layer of communication interface

The SMB\_ALERT\_L signal indicates that the power supply is experiencing a problem that the system agent should investigate. This is a logical OR of the Shutdown and Warning events. The power supply responds to a read command on the general SMB\_ALERT\_L call address 25(0x19) by sending its status register.

Communication to the DSP or the EEPROM will be possible as long as the input AC voltage is provided. If no AC is present, communication to the unit is possible as long as it is connected to a life V1 output (provided e.g. by the redundant unit). If only VSB is provided, communication is not possible.

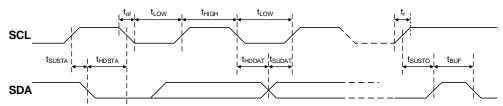

| PARAMETER          | DESCRIPTION / CONDITION                                     |                                              | MIN                   | NOM | MAX                       | UNIT |

|--------------------|-------------------------------------------------------------|----------------------------------------------|-----------------------|-----|---------------------------|------|

| ViL                | Input low voltage                                           |                                              | -0.5                  |     | 1.0                       | V    |

| V <sub>iH</sub>    | Input high voltage                                          |                                              | 2.3                   |     | 5.5                       | V    |

| $V_{hys}$          | Input hysteresis                                            |                                              | 0.15                  |     |                           | V    |

| VoL                | Output low voltage                                          | 3 mA sink current                            | 0                     |     | 0.4                       | V    |

| t <sub>r</sub>     | Rise time for SDA and SCL<br>(ViLmax-0.15V to ViHmin+0.15V) | 0.65V to 2.25V<br>f <sub>SCL</sub> ≤ 100 kHz | 20+0.1Cb <sup>3</sup> |     | 1000                      | ns   |

| t <sub>of</sub>    | Output fall time<br>(ViHmin+0.15V to ViLmax-0.15V)          | 2.25V to 0.65V<br>f <sub>SCL</sub> ≤ 100 kHz | 20+0.1Cb <sup>3</sup> |     | 300                       | ns   |

| <b>I</b> i         | Input current SCL/SDA                                       | 0.1  VDD < Vi < 0.9  VDD                     | -10                   |     | 10                        | μΑ   |

| $C_i$              | Internal Capacitance for each SCL/SDA                       |                                              |                       |     | 50                        | pF   |

| f <sub>SCL</sub>   | SCL clock frequency                                         |                                              | 0                     |     | 100                       | kHz  |

| Rpu                | External pull-up resistor                                   | f <sub>SCL</sub> ≤ 100 kHz                   |                       |     | 1000 ns / Cb <sup>3</sup> | Ω    |

| t <sub>HDSTA</sub> | Hold time (repeated) START                                  | f <sub>SCL</sub> ≤ 100 kHz                   | 4.0                   |     |                           | μS   |

| $t_{LOW}$          | Low period of the SCL clock                                 | f <sub>SCL</sub> ≤ 100 kHz                   | 4.7                   |     |                           | μS   |

Cb = Capacitance of bus line in pF, typically in the range of 10...400 pF

| t <sub>HIGH</sub>      | High period of the SCL clock         | f <sub>SCL</sub> ≤ 100 kHz | 4.0 |      | μS |

|------------------------|--------------------------------------|----------------------------|-----|------|----|

| <i>tsusta</i>          | Setup time for a repeated START      | f <sub>SCL</sub> ≤ 100 kHz | 4.7 |      | μS |

| <i>t</i> HDDAT         | Data hold time                       | f <sub>SCL</sub> ≤ 100 kHz | 0   | 3.45 | μS |

| <i>tsudat</i>          | Data setup time                      | f <sub>SCL</sub> ≤ 100 kHz | 250 |      | ns |

| t <sub>SUSTO</sub>     | Setup time for STOP condition        | f <sub>SCL</sub> ≤ 100 kHz | 4.0 |      | μs |

| <i>t<sub>BUF</sub></i> | Bus free time between STOP and START | f <sub>SCL</sub> ≤ 100 kHz | 5   |      | ms |

Table 7. I2C / SMBus Specification

Figure 17. I2C / SMBus Timing

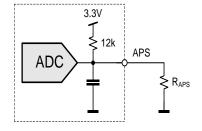

## 8.14 ADDRESS / PROTOCOL SELECTION (APS)

The APS pin provides the possibility to select the address by connecting a resistor to V1 return (0 V). A fixed addressing offset exists between the Controller and the EEPROM.

#### NOTES:

- If the APS pin is left open, the supply will operate with the Power Management Bus protocol at controller / EEPROM addresses 0xB6 / 0xA6.

- The APS pin is only read at start-up of the power supply. Therefore, it is not possible to change address dynamically.

| R <sub>APS</sub> (Ω) <sup>4</sup> | Protocol       | I2C Address 5 |        |

|-----------------------------------|----------------|---------------|--------|

| MAPS (12)                         | Protocol       | Controller    | EEPROM |

| 820                               |                | 0xB0          | 0xA0   |

| 2700                              | Power          | 0xB2          | 0xA2   |

| 5600                              | Management Bus | 0xB4          | 0xA4   |

| 8200                              |                | 0xB6          | 0xA6   |

| 15000                             |                | 0xB0          | 0xA0   |

| 27000                             | PSMI           | 0xB2          | 0xA2   |

| 56000                             | POIVII         | 0xB4          | 0xA4   |

| 180000                            |                | 0xB6          | 0xA6   |

Figure 18. I2C address and protocol setting

### 8.15 CONTROLER AND EEPROM ACCESS

The controller and the EEPROM in the power supply share the same I2C bus physical layer, see Figure 16. An I2C driver device assures logic level shifting (3.3/5 V) and a glitch-free clock stretching. The driver also pulls the SDA/SCL line to nearly 0 V when driven low by the DSP or the EEPROM providing maximum flexibility when additional external bus repeaters are needed. Such repeaters usually encode the low state with different voltage levels depending on the transmission direction.

The DSP will automatically set the I2C address of the EEPROM with the necessary offset when its own address is changed / set. In order to write to the EEPROM, first the write protection needs to be disabled by sending the appropriate command to the DSP. By default, the write protection is on.

The EEPROM provides 256 bytes of user memory. None of the bytes are used for the operation of the power supply.

<sup>5</sup> The LSB of the address byte is the R/W bit

<sup>&</sup>lt;sup>4</sup> E12 resistor values, use max 5% resistors

Figure 19. I2C Bus to DPS and EEPROM

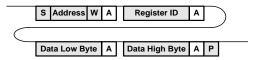

### **8.16 EEPROM PROTOCOL**

The EEPROM follows the industry communication protocols used for this type of device. Even though page write / read commands are defined, it is recommended to use the single byte write / read commands.

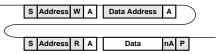

#### WRITE

The write command follows the SMBus 1.1 Write Byte protocol. After the device address with the write bit cleared a first byte with the data address to write to is sent followed by the data byte and the STOP condition. A new START condition on the bus should only occur after 5ms of the last STOP condition to allow the EEPROM to write the data into its memory.

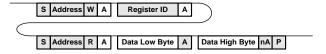

### **READ**

The read command follows the SMBus 1.1 Read Byte protocol. After the device address with the write bit cleared the data address byte is sent followed by a repeated start, the device address and the read bit set. The EEPROM will respond with the data byte at the specified location.

### 8.17 POWER MANAGEMENT BUS PROTOCOL

The Power Management Bus is an open standard protocol that defines means of communicating with power conversion and other devices. For more information, please see the System Management Interface Forum web site at www.powerSIG.org.

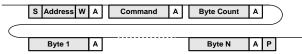

Power Management Bus command codes are not register addresses. They describe a specific command to be executed. The PFS1200-12-054NAH supply supports the following basic command structures:

- Clock stretching limited to 1 ms

- SCL low time-out of >25 ms with recovery within 10 ms

- Recognized any time Start/Stop bus conditions

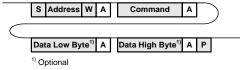

### WRITE

The write protocol is the SMBus 1.1 Write Byte/Word protocol. Note that the write protocol may end after the command byte or after the first data byte (Byte command) or then after sending 2 data bytes (Word command).

In addition, Block write commands are supported with a total maximum length of 255 bytes. See PFS Programming Manual for further information.

### **READ**

The read protocol is the SMBus 1.1 Read Byte/Word protocol. Note that the read protocol may request a single byte or word.

In addition, Block read commands are supported with a total maximum length of 255 bytes. See PFS Programming Manual BCA.00006 for further information.

#### 8.18 PSMI PROTOCOL

New power management features in computer systems require the system to communicate with the power supply to access current, voltage, fan speed, and temperature information. Current measurements provide data to the system for determining potential system configuration limitations and provide actual system power consumption for facility planning. Temperature and fan monitoring allow the system to better manage fan speeds and temperatures for optimizing system acoustics. Voltage monitoring allows the system to calculate input wattage and warning of system voltage regulation problems. The Power Supply Management Interface (PSMI) supports diagnostic capabilities and allows managing of redundant power supplies. The communication method is SMBus. The current design guideline is version 2.12.

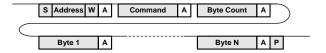

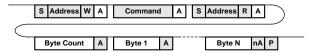

The communication protocol is register based and defines a read and write communication protocol to read / write to a single register address. All registers are accessed via the same basic command given below. No PEC (Packet Error Code) is used.

### WRITE

The write protocol used is the SMBus 2.0 Write Word protocol. All writes are 16-bit words; byte reads are not supported nor allowed. The shaded areas in the figure indicate bits and bytes written by the PSMI master device. See PFS Programming Manual for further information.

#### **READ**

The read protocol used is the SMBus 2.0 Read Word protocol. All reads are 16-bit words; byte reads are not supported nor allowed. The shaded areas in the figure indicate bits and bytes written by the PSMI master device. See PFS Programming Manual for further information.

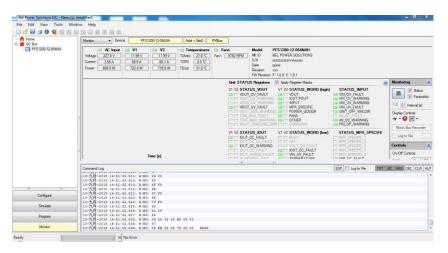

### 8.19 GRAPHICAL USER INTERFACE

Bel Power Solutions provides with its "Bel Power Solutions I2C Utility" a Windows® XP/Vista/Win7 compatible graphical user interface allowing the programming and monitoring of the PFS1200-12-054NAH Front-End. The utility can be downloaded on: <a href="https://documents.org/belfuse.com/power-solutions">belfuse.com/power-solutions</a> and supports Power Management Bus protocols.

The GUI allows automatic discovery of the units connected to the communication bus and will show them in the navigation tree. In the monitoring view the power supply can be controlled and monitored.

If the GUI is used in conjunction with the SNP-OP-BOARD-01 or YTM.G1Q01.0 Evaluation Kit it is also possible to control the PSON\_L pin(s) of the power supply.

Further there is a button to disable the internal fan for approximately 10 seconds. This allows the user to take input power measurements without fan consumptions to check efficiency compliance to the Climate Saver Computing Platinum specification.

The monitoring screen also allows to enable the hot-standby mode on the power supply. The mode status is monitored and by changing the load current it can be monitored when the power supply is being disabled for further energy savings. This obviously requires 2 power supplies being operated as a redundant system (as in the evaluation kit).

NOTE: The user of the GUI needs to ensure that only one of the power supplies have the hot-standby mode enabled.

Figure 20. Monitoring dialog of the I2C Utility

## 9. TEMPERATURE AND FAN CONTROL

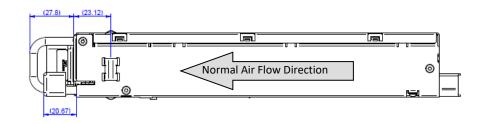

To achieve best cooling results sufficient airflow through the supply must be ensured. Do not block or obstruct the airflow at the rear of the supply by placing large objects directly at the output connector. The PFS1200-12-054NAH is provided with normal airflow, which means the air enters through the DC-output of the supply and leaves at the AC-inlet. PFS supplies have been designed for horizontal operation.

The fan inside of the supply is controlled by a microprocessor. The RPM of the fan is adjusted to ensure optimal supply cooling and is a function of output power and the inlet temperature.

For the normal airflow version additional constraints apply because of the AC-connector. In a normal airflow unit, the hot air is exiting the power supply unit at the AC-inlet.

The IEC connector on the unit is rated 105°C. If 70°C mating connector is used then end user must derated the input power to meet a maximum 70°C temperature at the front.

**NOTE:** It is the responsibility of the user to check the front temperature in such cases. The unit is not limiting its power automatically to meet such a temperature limitation.

# 10. ELECTROMAGNETIC COMPATIBILITY

## **10.1 IMMUNITY**

NOTE: Most of the immunity requirements are derived from EN 55024:1998/A2:2003.

| PARAMETER                      | DESCRIPTION / CONDITION                                                                                                                                                                                | CRITERION                                         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| ESD Contact Discharge          | IEC / EN 61000-4-2, ±8 kV, 25+25 discharges per test point (metallic case, LEDs, connector body)                                                                                                       | A                                                 |

| ESD Air Discharge              | IEC / EN 61000-4-2, ±15 kV, 25+25 discharges per test point (non-metallic user accessible surfaces)                                                                                                    | Α                                                 |

| Radiated Electromagnetic Field | IEC / EN 61000-4-3, 10 V/m, 1 kHz/80% Amplitude Modulation, 1 µs Pulse Modulation, 10 kHz2 GHz                                                                                                         | А                                                 |

| Burst                          | IEC / EN 61000-4-4, level 3 AC port ±2 kV, 1 minute DC port ±1 kV, 1 minute                                                                                                                            | А                                                 |

| Surge                          | IEC / EN 61000-4-5<br>Line to earth: level 3, ±2 kV<br>Line to line: level 2, ±1 kV                                                                                                                    | А                                                 |

| RF Conducted Immunity          | IEC/EN 61000-4-6, Level 3, 10 Vrms, CW, 0.15 80 MHz                                                                                                                                                    | Α                                                 |

| Voltage Dips and Interruptions | IEC/EN 61000-4-11 1: Vi 230 V, 100% Load, Phase 0 °, Dip 100%, Duration 10 ms 2: Vi 230 V, 100% Load, Phase 0 °, Dip 100%, Duration 20 ms 3: Vi 230 V, 100% Load, Phase 0 °, Dip 100%, Duration >20 ms | A<br>V <sub>SB</sub> : A, V <sub>1</sub> : B<br>B |

### **10.2 EMISSION**

| PARAMETER           | DESCRIPTION / CONDITION                                                | CRITERION |

|---------------------|------------------------------------------------------------------------|-----------|

| Conducted Fasicales | EN55022 / CISPR 22: 0.15 30 MHz, QP and AVG, single unit               | Class A   |

| Conducted Emission  | EN55022 / CISPR 22: 0.15 30 MHz, QP and AVG,<br>2 units in rack system | Class A   |

| Dedicted Francisco  | EN55022 / CISPR 22: 30 MHz 1 GHz, QP, single unit                      | Class A   |

| Radiated Emission   | EN55022 / CISPR 22: 30 MHz 1 GHz, QP,<br>2 units in rack system        | Class A   |

| Harmonic Emissions  | IEC61000-3-2, Vin = 115 VAC / 60 Hz, & Vin = 230VAC/ 50 Hz, 100% Load  | Class A   |

| AC Flicker          | IEC61000-3-3, Vin = 230 VAC / 60 Hz, 100% Load                         | Pass      |

# 11. SAFETY APPROVALS

Maximum electric strength testing is performed in the factory according to IEC/EN 62368-1, and UL 62368-1. Input-to-output electric strength tests should not be repeated in the field. Bel Power Solutions will not honor any warranty claims resulting from electric strength field tests.

| PARA | METER                    | DESCRIPTION / CONDITION                                              | MIN | NOM                               | MAX | UNIT |

|------|--------------------------|----------------------------------------------------------------------|-----|-----------------------------------|-----|------|

|      | Agency Approvals         | UL 62368-1<br>CAN/CSA-C22.2 No. 62368-1<br>IEC 62368-1<br>EN 62368-1 |     | Approved                          |     |      |

|      | Isolation Strength       | Input (L/N) to case (PE) Input (L/N) to output Output to case (PE)   | •   | Basic<br>Reinforced<br>Functional |     |      |

| dc   | Creepage / Clearance     | Primary (L/N) to protective earth (PE) Primary to secondary          |     | ccording to ety standard          |     | mm   |

|      | Electrical Strength Test | Input to case Input to output Output and Signals to case             |     | ccording to ety standard          |     | kVAC |

# 12. ENVIRONMENTAL SPECIFICATIONS

| PARAM                       | METER                | DESCRIPTION / CONDITION                                                                            | MIN | NOM | MAX  | UNIT |

|-----------------------------|----------------------|----------------------------------------------------------------------------------------------------|-----|-----|------|------|

| T <sub>A</sub>              | Ambient Temperature  | V <sub>min</sub> to V <sub>max</sub> , H <sub>nom</sub> , k <sub>B nom</sub> below 1800 m Altitude | -5  |     | +65  | °C   |

|                             |                      | (<1800 m, keep maximum operation temperature.<br>≥ 1800 m, decrease 1° C per 300 m)                |     |     |      | °C   |

| $T_{Aext}$                  | Extended Temp. Range | Derating output                                                                                    | +40 |     | +65  | °C   |

| $\mathcal{T}_{\mathcal{S}}$ | Storage Temperature  | Non-operational                                                                                    | -40 |     | +70  | °C   |

|                             | Altitude             | Operational, above Sea Level, refer derating to Ta                                                 | -   |     | 3000 | m    |

| <b>N</b> a                  | Audible Noise        | $V_{\text{nom}}$ , 50% $I_{\text{0 nom}}$ , $T_{\text{A}} = 25^{\circ}\text{C}$                    |     | 60  |      | dBA  |

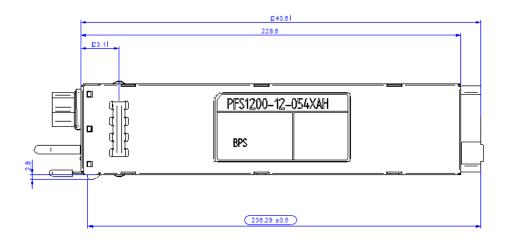

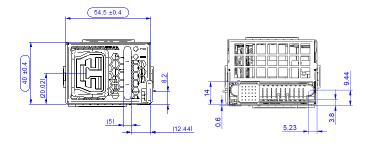

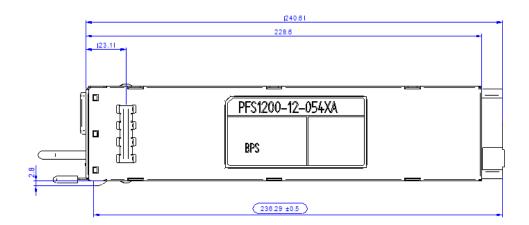

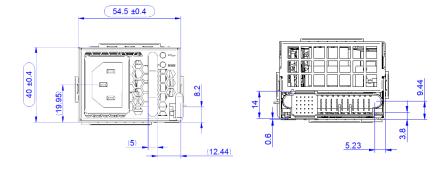

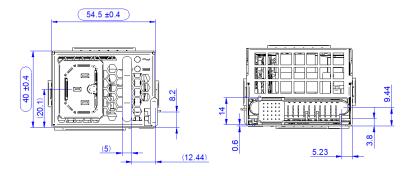

# 13. MECHANICAL SPECIFICATIONS

| Width         54.5           Dimensions         Height         40.0         mm           Depth         228.6 | PARAMET | TER        | DESCRIPTION / CONDITION | MIN | NOM   | MAX | UNIT |

|--------------------------------------------------------------------------------------------------------------|---------|------------|-------------------------|-----|-------|-----|------|

| Depth 228.6                                                                                                  |         |            | Width                   |     | 54.5  |     |      |

| ·                                                                                                            |         | Dimensions | Height                  |     | 40.0  |     | mm   |

| M Wainh                                                                                                      |         |            | Depth                   |     | 228.6 |     |      |

| W Weight 0.87 kg                                                                                             | М       | Weight     |                         |     | 0.87  |     | kg   |

## PFS1200-12-054NAH, PFS1200-12-054RAH

### Input AC connector Anderson Power Products 2006G1-BK

NOTE: A 3D step file of the power supply casing is available on request.

Figure 22. Side View

Figure 23. Top View

Figure 24. Front and Rear View

## PFS1200-12-054NA, PFS1200-12-054RA

# C14 Type Input AC connector Rong Feng SS-120-1.0B-2.8BV or equivalent

NOTE: A 3D step file of the power supply casing is available on request.

Figure 25. Side View

Figure 26. Side View

Figure 27. Side View

## PFS1200-12-054NAC, PFS1200-12-054RAC

# C16 Type Input AC connector Rong Feng SS-120B-1.0-4.0Ad or equivalent

NOTE: A 3D step file of the power supply casing is available on request.

Figure 28. Side View

Figure 29. Side View

Figure 30. Side View

## 14. CONNECTIONS

### **AC INPUT CONNECTOR:**

PFS1200-12-054NAH: **Power supplier connector:** ANDERSON POWER PRODUCTS 2006G1-BK **Mating connector:** Anderson Saf-D-Grid Power cord 2034KZ2 or equivalent,

http://www.andersonpower.com/

PFS1200-12-054NA/RA: Power supplier connector: IEC320 C14 type PFS1200-12-054NAC/RAC: Power supplier connector: IEC320 C16 type

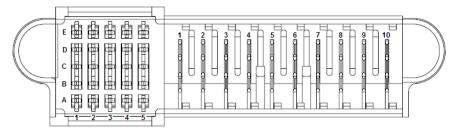

### DC OUTPUT CONNECTOR:

Power Supply Connector: Tyco Electronics P/N 2-1926736-3 (NOTE: Column 5 is recessed (short pins))

Mating Connector: Tyco Electronics P/N 2-1926739-5 or FCI 10108888-R10253SLF

| PIN            | NAME           | DESCRIPTION                                                                      |

|----------------|----------------|----------------------------------------------------------------------------------|

| Output         |                |                                                                                  |

| 6, 7, 8, 9, 10 | V1             | +12 VDC main output                                                              |

| 1, 2, 3, 4, 5  | PGND           | Power ground (return)                                                            |

| Control Pins   |                |                                                                                  |

| A1             | VSB            | Standby positive output                                                          |

| B1             | VSB            | Standby positive output                                                          |

| C1             | VSB            | Standby positive output                                                          |

| D1             | VSB            | Standby positive output                                                          |

| E1             | VSB            | Standby positive output                                                          |

| A2             | SGND           | Signal ground (VSB Return)                                                       |

| B2             | SGND           | Signal ground (VSB Return)                                                       |

| C2             | HOTSTANDBYEN_H | Hot standby enable signal: active-high                                           |

| D2             | VSB_SENSE_R    | VSB output negative sense                                                        |

| E2             | VSB_SENSE      | VSB output positive sense                                                        |

| A3             | APS            | I <sup>2</sup> C address and protocol selection (select by a pull down resistor) |

| B3             | N/C            | Reserved                                                                         |

| C3             | SDA            | I <sup>2</sup> C data signal line                                                |

| D3             | V1_SENSE_R     | Main output negative sense                                                       |

| E3             | V1_SENSE       | Main output positive sense                                                       |

| A4             | SCL            | I <sup>2</sup> C clock signal line                                               |

| B4             | PSON_L         | Power supply on input (connect to A2/B2 to turn unit on): active-low             |

| C4             | SMB_ALERT_L    | SMB Alert signal output: active-low                                              |

| D4             | VSB_SEL1       | VSB voltage selection (See section 8.9)                                          |