# UG298: Si5xxUC-EVB

### Universal Oscillator Evaluation Board

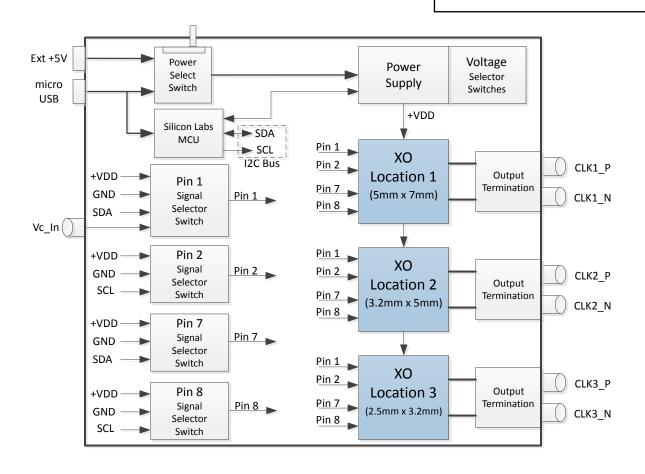

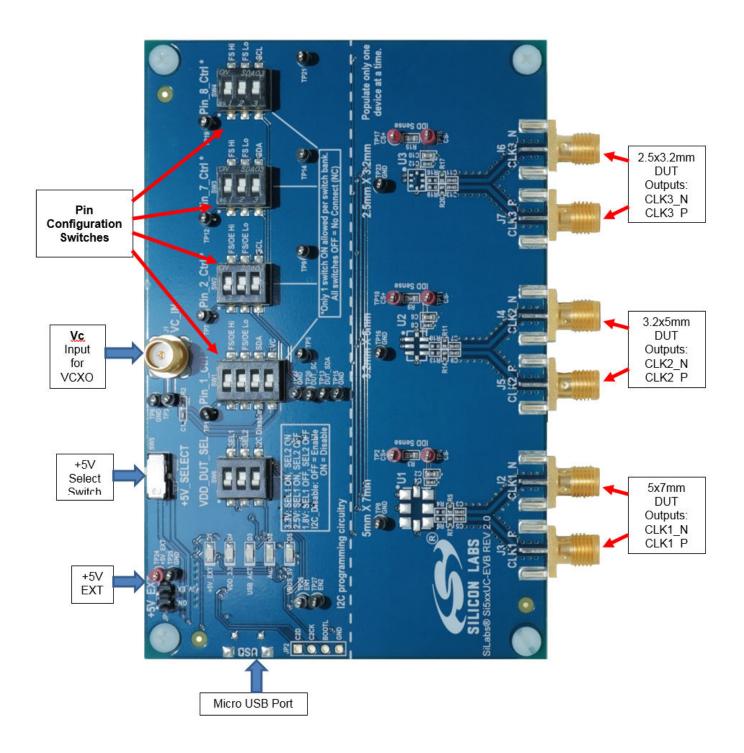

This document describes operation of the Silicon Laboratories Si5xxUC-EVB evaluation board designed to evaluate any of Silicon Labs' pin-controlled or I²C configurable Si5xx XOs or VCXOs. Three device sites are available to support one of either 5mm x 7mm, 3.2mm x 5mm, or 2.5mm x 3.2mm devices in either 4, 6, or 8 pin configurations. Selector switches make it easy to configure device control pins (pins 1, 2, 7, or 8) for proper operation without the use of jumpers. Similarly, XO device VDD voltage (3.3V, 2.5V, 1.8V) can be selected via switches based on either external +5V (for stand-alone operation) or micro USB sourced +5V USB operation. The EVB also features flexible output termination circuits and PCB layout optimized for superior signal integrity.

#### **KEY FEATURES**

- Evaluation of any Silicon Labs XO or VCXO (Si51x, Si53x, Si54x, Si55x, Si56x, Si57x, Si59x)

- AC coupled differential/single-ended output clocks.

- Voltage control (Vc) port for VCXO evalution.

- Switch selectable settings. No jumpers.

- · External power or USB powered.

- Use stand-alone or with our Programmable Oscillator Calculator SW tool

# **Table of Contents**

| 1. | Quick Start - Board Configuration Check List                    |       |     |  |  |  |   |  |  | . 3  |

|----|-----------------------------------------------------------------|-------|-----|--|--|--|---|--|--|------|

| 2. | Functional Description                                          |       |     |  |  |  |   |  |  | . 4  |

| 3. | General Operational Restrictions                                |       |     |  |  |  |   |  |  | . 5  |

|    | 3.1 Evaluate Only a Single Device at a Time                     |       |     |  |  |  |   |  |  | . 5  |

| 4. | Power Supply and I <sup>2</sup> C Bus Control                   |       |     |  |  |  |   |  |  | . 6  |

| 5. | Control Signal Switch Settings                                  |       |     |  |  |  |   |  |  | . 7  |

|    | 5.1 Oscillator Pin 1 Control DIP Switch (Pin_1_Ctrl)            |       |     |  |  |  |   |  |  | . 8  |

|    | 5.2 Oscillator Pin 2 Control DIP Switch (Pin_2_Ctrl)            |       |     |  |  |  |   |  |  | . 9  |

|    | 5.3 Oscillator Pin 7 Control DIP Switch (Pin_7_Ctrl)            |       |     |  |  |  |   |  |  | .10  |

|    | 5.4 Oscillator Pin 8 Control DIP Switch (Pin_8_Ctrl)            |       |     |  |  |  |   |  |  | . 11 |

| 6. | Supported Devices - Stand-Alone Mode                            |       |     |  |  |  |   |  |  | 12   |

| 7. | Supported Devices - Software Controlled Mode - I <sup>2</sup> C |       |     |  |  |  |   |  |  | 15   |

| 8. | USB Port and External Powering                                  |       |     |  |  |  |   |  |  | 16   |

| 9. | Output Clock Terminations                                       |       |     |  |  |  |   |  |  | 17   |

| 10 | D. EVB Test Points and LEDs                                     |       |     |  |  |  |   |  |  | 18   |

|    | 10.1 Test Points                                                |       |     |  |  |  |   |  |  | .18  |

|    | 10.2 LEDs                                                       |       |     |  |  |  |   |  |  | .18  |

| 11 | I. VCXO Voltage Control Input Circuit                           |       |     |  |  |  |   |  |  | 19   |

| 12 | 2. Programmable Oscillator Calculator Tool                      |       |     |  |  |  |   |  |  | 20   |

| 13 | 3. Layout of Board                                              |       |     |  |  |  |   |  |  | 21   |

|    |                                                                 |       |     |  |  |  |   |  |  |      |

|    | 13.1 Si56x XO and VCXO 2.5x3.2mm Footprint Recommend            | datio | n . |  |  |  | • |  |  | .22  |

## 1. Quick Start - Board Configuration Check List

Mount your oscillator device on the board at appropriate oscillator site location (U1, U2, or U3, but on only one location) if a device is not yet mounted.

- 1. Start with EVB board powered down/off.

- 2. Set DIP switches (described in Section 5. Control Signal Switch Settings) for your specific device:

- a. Look up your device as appropriate in the tables of Sections 6. Supported Devices Stand-Alone Mode or 7. Supported Devices Software Controlled Mode I<sup>2</sup>C.

- b. Make DIP switch settings per table entry for pins 1,2,7,8 as appropriate. See Sections 6. Supported Devices Stand-Alone Mode or 7. Supported Devices Software Controlled Mode I<sup>2</sup>C .

- 3. Verify output termination is appropriate for your device (see Section 9. Output Clock Terminations for more info).

- 4. Set +5V Select switch (SW5) based on how you will power the EVB, either via USB or via external +5V supply.

- 5. Connect power, either via USB port or external +5V power supply as chosen in previous step.

- 6. Output Clocks:

- For pin controlled oscillators, clock output should be available on output SMAs of DUT site in use.

- For I2C oscillators, run appropriate configuration software (e.g., Programmable Oscillator Software tool) and perform device configuration to get desired output clock.

## 2. Functional Description

The Si5xxUC-EVB is an evaluation board designed to support any Silicon Labs XO/VCXO device. The Si5xxUC-EVB is designed to operate in one of two general operational modes:

- Stand-alone mode: The stand-alone mode is for evaluation of fixed output frequency or pin-controlled XO/VCXO devices where I<sup>2</sup>C support is NOT required to operate or evaluate the device. Control of device pins, such as OE or FS, is done via on-board switches. In Stand-alone mode the on-board switches must be set according to the requirements of the device installed on the board. For example, if the installed device is a dual frequency part with output enable, the appropriate switches must be set to assert output enable (OE) and the frequency select pin (FS) to give the desired output frequency. Device VDD voltage can be set via on-board switches as well. Switch setting details for Stand-alone mode are shown in Section 4. Power Supply and I<sup>2</sup>C Bus Control (for power supply) and Section 5. Control Signal Switch Settings (for device pins).

- Software controlled mode: The software controlled mode is for use with PC-based software tools (such as our Programmable Oscillator Calculator Tool) to control/configure the device being evaluated via the device I<sup>2</sup>C bus. The software controlled mode is primarily intended for I<sup>2</sup>C controlled XO/VCXO devices. When using software controlled mode, some of the on-board switches must be placed in specific default settings to allow the on-board MCU to perform I<sup>2</sup>C control. Other switches must still be used on certain device signals, like output enable (OE). Switch setting details for software controlled mode are shown in Section 4. Power Supply and I<sup>2</sup>C Bus Control (for power supply & I<sup>2</sup>C) and Section 5. Control Signal Switch Settings (for device pins).

For each of the 3 device locations on the Si5XXUC-EVB, separate sets of SMA outputs and terminations are provided per XO "Device Under Test" (DUT) location even though only one device may be populated and used at a time (see Section 3. General Operational Restrictions below). Separate outputs and terminations per device site provides the best possible clock signal integrity for each DUT location.

## 3. General Operational Restrictions

## 3.1 Evaluate Only a Single Device at a Time

**Note:** It is strongly recommended to populate only one device on the Si5xxUC-EVB board at a time. Carefully read the next paragraph for important information.

The Si5xxUC-EVB supports evaluation of a single device in one of three different DUT locations. Device sizes supported are 5mm x 7mm, 3.2mm x 5mm, or 2.5mm x 3.2mm. All device locations can support 4, 6, or 8 pin configurations, but only one device at a time should be installed in any one of the three locations on the Si5xxUC-EVB. This restriction is made to ensure no problems will occur due to potential signal crosstalk, power supply over-loading/coupling, or signal contention/loading between multiple devices. Do not simply remove power from a mounted device in an attempt to place it in an "unused", but still mounted, state. Board control signals are wired in parallel to all 3 locations and a non-powered device may load control signals to a powered device under test. Please follow this "one device at a time" recommendation and only populate one device at a time.

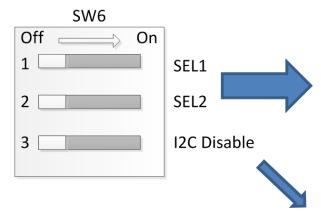

## 4. Power Supply and I<sup>2</sup>C Bus Control

The power supply uses a linear voltage regulator to drop the +5 V input supply voltage to one of the supported nominal VDD voltages of +3.3 V, +2.5 V, or +1.8 V. A switch is provided on the EVB (SW5) to select the +5 V source for the voltage regulator as either the USB port +5V or an external +5 V source. The EVB power supply supports operation in one of 2 general modes that correspond to the two operational EVB use cases.

- Stand-alone mode: Power can be sourced from either external supply or USB port, but software is not required and no EVB software tool should be actively connected to Si5XXUC-EVB when being used in Stand-alone mode. In Stand-alone mode the oscillator device VDD voltage is set via the "VDD\_DUT\_SEL" switch according to the voltage select table shown below. By default this switch is set to 1.8 V and will need to be changed if evaluating a non-I<sup>2</sup>C oscillator with 2.5 V or 3.3 V VDD.

- Software controlled mode: Power can be sourced from either external power supply or USB port, but the Programmable Oscillator Software tool can be used to set the VDD voltage to the oscillator. In software controlled mode, "VDD\_DUT\_SEL" switches should remain set to 1.8 V setting regardless of the desired VDD voltage.

The I<sup>2</sup>C Disable switch is typically set to the "Off" setting (to enable the on-board MCU to drive the I<sup>2</sup>C bus) unless the user is attempting to connect an external I<sup>2</sup>C master to communicate with the oscillator device. The I<sup>2</sup>C Disable control allows for disabling the on-board I<sup>2</sup>C buffer to disconnect the oscillator from the on-board MCU. This disconnection is useful if the user wishes to connect an external I<sup>2</sup>C bus master to communicate with the DUT.

# VDD\_DUT\_SEL

| D    | Device Voltage Select |                |  |  |  |  |  |  |  |  |  |

|------|-----------------------|----------------|--|--|--|--|--|--|--|--|--|

| SEL1 | SEL2                  | Voltage (V)    |  |  |  |  |  |  |  |  |  |

| On   | On                    | 3.3            |  |  |  |  |  |  |  |  |  |

| On   | Off                   | 2.5            |  |  |  |  |  |  |  |  |  |

| Off  | Off                   | 1.8            |  |  |  |  |  |  |  |  |  |

| OII  | OII                   | (SW ctrl mode) |  |  |  |  |  |  |  |  |  |

| 120       | Disable Control     |

|-----------|---------------------|

| Selection | Function            |

| On        | Disable DUT I2C bus |

| Off       | Enable DUT I2C bus  |

## 5. Control Signal Switch Settings

Four of the 5 on-board DIP switches (SW1, 2, 3, 4) are used for configuration of the EVB oscillator locations to match any standard oscillator pin-out. Using this DIP switch arrangement, the Si5xxUC-EVB can be configured to support all Silicon Labs oscillator devices. The oscillator device pins that can vary in function, depending on the device variant, are pins 1, 2, 7, and 8 as shown in the Device Pin-out Mapping table below. Pins 3, 4, 5, and 6 are typically fixed function pins that do not change with device variant.

**Note:** All device locations on the Si5xxUC-EVB can support up to 8 pin variant devices. Devices with fewer pins (4, 6 pin) can be installed in the same location and will fit within the 8 pin footprint.

|                 | Device Pin-out Mapping |                 |                  |                     |  |  |  |  |  |  |  |  |

|-----------------|------------------------|-----------------|------------------|---------------------|--|--|--|--|--|--|--|--|

| 4 pin<br>Device | 6 pin<br>Device        | 8 pin<br>Device | DIP Switch       | Function<br>Options |  |  |  |  |  |  |  |  |

| 1               | 1                      | 1               | Pin_1_Ctrl (SW1) | FS/OE/SDA/Vc        |  |  |  |  |  |  |  |  |

| -               | 2                      | 2               | FS/OE/SCL        |                     |  |  |  |  |  |  |  |  |

| 2               | 3                      | 3               | -                | GND <sup>1</sup>    |  |  |  |  |  |  |  |  |

| 3               | 4                      | 4               | -                | Output <sup>1</sup> |  |  |  |  |  |  |  |  |

| -               | 5                      | 5               | -                | Output <sup>1</sup> |  |  |  |  |  |  |  |  |

| 4               | 6                      | 6               | -                | VDD <sup>1</sup>    |  |  |  |  |  |  |  |  |

| -               | -                      | 7               | Pin_7_Ctrl (SW3) | FS/SDA              |  |  |  |  |  |  |  |  |

| -               | -                      | 8               | Pin_8_Ctrl (SW4) | FS/SCL              |  |  |  |  |  |  |  |  |

Note:

1. Fixed function pins

Configuration details of each of the 4 variable pin function DIP switches is described in following sections. For devices that may not utilize all 4 of the variable pin function switches, the corresponding unused DIP switch can be set to the NC setting (all Off position). Make sure to make the following switch settings with the Si5xxUC-EVB powered down. Once all are set appropriately, the board may be powered on.

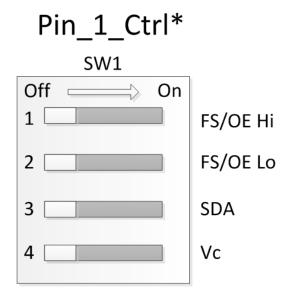

#### 5.1 Oscillator Pin 1 Control DIP Switch (Pin\_1\_Ctrl)

The pin 1 control DIP switch allows oscillator pin 1 to be driven from any of these 4 sources.

- 1. High (VDD) level

- 2. Low (GND) level

- 3. I2C bus SDA signal

- 4. External control voltage Vc (for VCXO applications)

**Note:** The 4 signal sources listed above are connected on separate pins on left side of the switch and all pins on right side are tied together (common) and then connect to pin 1 of the oscillator. **This means that only one (1) of the switches in this DIP switch bank can be in the ON position at a time.** Switching more than 1 switch to the on position at a time may cause undesired behavior. All switches can be set to OFF position to effectively isolate pin 1 from any signal source and is the No Connect (NC) state.

To determine the required Pin 1 switch settings for your specific device, please refer to the Supported Device Tables in Chapter 6. Supported Devices - Stand-Alone Mode and Chapter 7. Supported Devices - Software Controlled Mode - I<sup>2</sup>C.

|     | Pin 1 DIP Switch (4, 6, or 8 pin DUT) |     |     |              |  |  |  |  |  |  |  |  |

|-----|---------------------------------------|-----|-----|--------------|--|--|--|--|--|--|--|--|

| 1   | 2                                     | 3   | 4   | Pin 1 Signal |  |  |  |  |  |  |  |  |

| Off | Off                                   | Off | Off | NC           |  |  |  |  |  |  |  |  |

| On  | Off                                   | Off | Off | FS/OE high   |  |  |  |  |  |  |  |  |

| Off | On                                    | Off | Off | FS/OE low    |  |  |  |  |  |  |  |  |

| Off | Off                                   | On  | Off | SDA          |  |  |  |  |  |  |  |  |

| Off | Off                                   | Off | On  | Vc           |  |  |  |  |  |  |  |  |

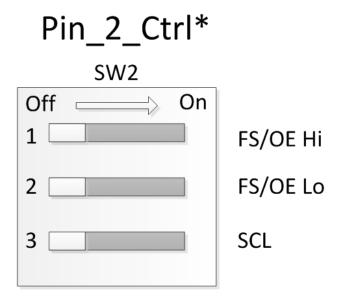

#### 5.2 Oscillator Pin 2 Control DIP Switch (Pin\_2\_Ctrl)

This DIP switch allows oscillator pin 2 to be driven from 1 of 3 sources.

- 1. High (VDD) level

- 2. Low (GND) level

- 3. I2C bus SCL signal

**Note:** The 3 signal sources listed above are located on separate pins on the left side of the switch and all pins on the right side are tied together (common) and then connect to pin 2 of the oscillator. **This means that only one (1) of the switches in this DIP switch bank can be in the ON position at a time.** Switching more than 1 switch to the ON position at a time may cause undesired behavior. All switches set to OFF position effectively isolates pin 2 from any signal source and is the No Connect (NC) state.

To determine the required Pin 2 switch settings for your specific device, please refer to the Supported Device Tables in Chapter 6. Supported Devices - Stand-Alone Mode and Chapter 7. Supported Devices - Software Controlled Mode - I<sup>2</sup>C.

|     | Pin 2 DIP Switch (6 or 8 pin DUT) |     |              |  |  |  |  |  |  |  |  |  |

|-----|-----------------------------------|-----|--------------|--|--|--|--|--|--|--|--|--|

| 1   | 2                                 | 3   | Pin 2 Signal |  |  |  |  |  |  |  |  |  |

| Off | Off                               | Off | NC           |  |  |  |  |  |  |  |  |  |

| On  | Off                               | Off | FS/OE high   |  |  |  |  |  |  |  |  |  |

| Off | On                                | Off | FS/OE low    |  |  |  |  |  |  |  |  |  |

| Off | Off                               | On  | SCL          |  |  |  |  |  |  |  |  |  |

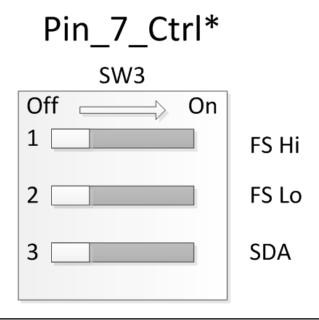

#### 5.3 Oscillator Pin 7 Control DIP Switch (Pin\_7\_Ctrl)

This DIP switch allows oscillator pin 7 to be driven from 1 of 3 sources.

- 1. High (VDD) level

- 2. Low (GND) level

- 3. I2C bus SDA signal

**Note:** The 3 signal sources listed above are located on separate pins on the left side of the switch and all pins on the right side are tied together (common) and then connect to pin 7 of the oscillator. **This means that only one (1) of the switches in this DIP switch bank can be in the ON position at a time.** Switching more than 1 switch to the ON position at a time may cause undesired behavior. All switches set to OFF position effectively isolates pin 7 from any signal source and is the No Connect (NC) state.

To determine the required Pin 7 switch settings for your specific device, please refer to the Supported Device Tables in Chapter 6. Supported Devices - Stand-Alone Mode and Chapter 7. Supported Devices - Software Controlled Mode - I<sup>2</sup>C.

|     | Pin 7 DIP Switch (8 pin DUT) |     |              |  |  |  |  |  |  |  |  |  |

|-----|------------------------------|-----|--------------|--|--|--|--|--|--|--|--|--|

| 1   | 2                            | 3   | Pin 7 Signal |  |  |  |  |  |  |  |  |  |

| Off | Off                          | Off | NC           |  |  |  |  |  |  |  |  |  |

| On  | On Off                       |     | FS high      |  |  |  |  |  |  |  |  |  |

| Off | On                           | Off | FS low       |  |  |  |  |  |  |  |  |  |

| Off | Off                          | On  | SDA          |  |  |  |  |  |  |  |  |  |

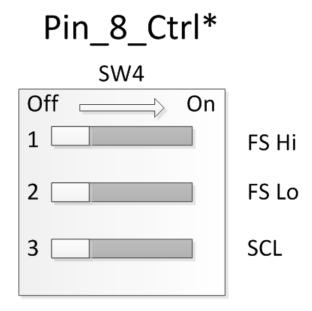

#### 5.4 Oscillator Pin 8 Control DIP Switch (Pin\_8\_Ctrl)

This DIP switch allows oscillator pin 8 to be driven from 1 of 3 sources.

- 1. High (VDD) level

- 2. Low (GND) level

- 3. I2C bus SCL signal

**Note:** The 3 signal sources listed above are located on separate pins on the left side of the switch and all pins on the right side are tied together (common) and then connect to pin 8 of the oscillator. **This means that only one (1) of the switches in this DIP switch bank can be in the ON position at a time.** Switching more than 1 switch to the ON position at a time may cause undesired behavior. All switches set to OFF position effectively isolates pin 8 from any signal source and is the No Connect (NC) state.

To determine the required Pin 8 switch settings for your specific device, please refer to the Supported Device Tables in Chapter 6. Supported Devices - Stand-Alone Mode and Chapter 7. Supported Devices - Software Controlled Mode - I<sup>2</sup>C.

|     | Pin 8 DIP Switch (8 pin DUT) |     |              |  |  |  |  |  |  |  |  |  |

|-----|------------------------------|-----|--------------|--|--|--|--|--|--|--|--|--|

| 1   | 2                            | 3   | Pin 8 Signal |  |  |  |  |  |  |  |  |  |

| Off | Off                          | Off | NC           |  |  |  |  |  |  |  |  |  |

| On  | Off                          | Off | FS high      |  |  |  |  |  |  |  |  |  |

| Off | On                           | Off | FS low       |  |  |  |  |  |  |  |  |  |

| Off | Off                          | On  | SCL          |  |  |  |  |  |  |  |  |  |

## 6. Supported Devices - Stand-Alone Mode

If using the Si5XXUC-EVB with a device that is either fixed frequency or has pin-controlled output frequency, this "Stand-alone mode" section should be used to configure the EVB.

If you have a device installed that utilizes the  $I^2C$  bus for making frequency or other changes to the device, please refer to Section 7. Supported Devices - Software Controlled Mode -  $I^2C$ .

The tables below show pin controlled XO and VCXO devices supported by the Si5xxUC-EVB along with possible package sizes and control pin mapping. The control pin mapping can be used to determine the corresponding switch settings on the Si5xxUC-EVB.

Table 6.1. Pin Controlled XOs

| SiLabs<br>Device | Туре | # Freqs          | # Pins | Pkg Sizes<br>(mm x mm) | Pin 1<br>Control | Pin 2<br>Control | Pin 7<br>Control | Pin 8<br>Control | Pin 4 Out-       | Pin 5 Out-<br>put |

|------------------|------|------------------|--------|------------------------|------------------|------------------|------------------|------------------|------------------|-------------------|

| Si510            | хо   | Single<br>(CMOS) | 4      | 5x7, 3.2x5,<br>2.5x3.2 | OE               | -                | -                | -                | CLK <sup>1</sup> | -                 |

| Si510            | ХО   | Single (Diff)    | 6      | 5x7, 3.2x5,<br>2.5x3.2 | NC               | OE               | -                | -                | CLK+             | CLK-              |

| Si511            | хо   | Single           | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE               | NC               | -                | -                | CLK+             | CLK-              |

| Si512            | хо   | Dual<br>(CMOS)   | 6      | 5x7, 3.2x5,<br>2.5x3.2 | FS               | OE               | -                | -                | CLK              | NC                |

| Si512            | ХО   | Dual (Diff)      | 6      | 5x7, 3.2x5,<br>2.5x3.2 | FS               | OE               | -                | -                | CLK+             | CLK-              |

| Si513            | ХО   | Dual<br>(CMOS)   | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE               | FS               | -                | -                | CLK              | NC                |

| Si513            | хо   | Dual (Diff)      | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE               | FS               | -                | -                | CLK+             | CLK-              |

| Si530            | ХО   | Single (Diff)    | 6      | 5x7                    | NC               | OE               | -                | -                | CLK+             | CLK-              |

| Si530            | хо   | Single<br>(CMOS) | 6      | 5x7                    | OE               | NC               | -                | -                | CLK              | NC                |

| Si531            | ХО   | Single           | 6      | 5x7                    | OE               | NC               | -                | -                | CLK+             | CLK-              |

| Si532            | хо   | Dual (Diff)      | 6      | 5x7                    | FS               | OE               | -                | -                | CLK+             | CLK-              |

| Si532            | хо   | Dual<br>(CMOS)   | 6      | 5x7                    | FS               | OE               | -                | -                | CLK              | NC                |

| Si533            | хо   | Dual (Diff)      | 6      | 5x7                    | OE               | FS               | -                | -                | CLK+             | CLK-              |

| Si533            | ХО   | Dual<br>(CMOS)   | 6      | 5x7                    | OE               | FS               | -                | -                | CLK              | NC                |

| Si534            | хо   | Quad (Diff)      | 8      | 5x7                    | NC               | OE               | FS1              | FS0              | CLK+             | CLK-              |

| Si534            | ХО   | Quad<br>(CMOS)   | 8      | 5x7                    | NC               | OE               | FS1              | FS0              | CLK              | NC                |

| Si535            | хо   | Single           | 6      | 5x7                    | NC               | OE               | -                | -                | CLK+             | CLK-              |

| Si536            | хо   | Single           | 6      | 5x7                    | OE               | NC               | -                | -                | CLK+             | CLK-              |

| Si540            | хо   | Single           | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | -                | -                | CLK+             | CLK-              |

| Si541            | хо   | Dual             | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/FS            | FS/OE            | -                | -                | CLK+             | CLK-              |

| SiLabs<br>Device | Туре | # Freqs                                       | # Pins | Pkg Sizes<br>(mm x mm) | Pin 1<br>Control | Pin 2<br>Control | Pin 7<br>Control | Pin 8<br>Control | Pin 4 Out-<br>put | Pin 5 Output |

|------------------|------|-----------------------------------------------|--------|------------------------|------------------|------------------|------------------|------------------|-------------------|--------------|

| Si542            | хо   | Quad                                          | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | FS1              | FS0              | CLK+              | CLK-         |

| Si544            | ХО   | Single/Dual/<br>Quad (or<br>I <sup>2</sup> C) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-         |

| Si545            | хо   | Single                                        | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | -                | -                | CLK+              | CLK-         |

| Si546            | хо   | Dual                                          | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/FS            | FS/OE            | -                | -                | CLK+              | CLK-         |

| Si547            | хо   | Quad                                          | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | FS1              | FS0              | CLK+              | CLK-         |

| Si549            | хо   | Single/Dual/<br>Quad (or<br>I <sup>2</sup> C) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-         |

| Si560            | хо   | Single                                        | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | -                | -                | CLK+              | CLK-         |

| Si561            | хо   | Dual                                          | 6      | 5x7, 3.2x5,<br>2.5x3.2 | OE/FS            | FS/OE            | -                | -                | CLK+              | CLK-         |

| Si562            | хо   | Quad                                          | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC            | NC/OE            | FS1              | FS0              | CLK+              | CLK-         |

| Si564            | хо   | Single/Dual/<br>Quad (or<br>I2C)              | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-         |

| Si590            | ХО   | Single (Diff)                                 | 6      | 5x7, 3.2x5             | NC               | OE               | -                | -                | CLK+              | CLK-         |

| Si590            | хо   | Single<br>(CMOS)                              | 6      | 5x7, 3.2x5             | OE               | NC               | -                | -                | CLK               | NC           |

| Si591            | хо   | Single                                        | 6      | 5x7, 3.2x5             | OE               | NC               | -                | -                | CLK+              | CLK-         |

### Note:

<sup>1.</sup> The pin number headings in Table 6.1 apply to 6/8 pin parts only. 4-pin devices like the Single CMOS Si510 have the clock output on pin 3 instead of pin 4. Please see the Si510/511 Data Sheet for more details on the pinout.

Table 6.2. Pin Controlled VCXOs

| SiLabs<br>Device | Туре | # Freqs                     | # Pins | Pkg Sizes<br>(mm x mm) | Pin 1<br>Control | Pin 2<br>Control | Pin 7<br>Control | Pin 8<br>Control | Pin 4 Out-<br>put | Pin 5 Out-<br>put |

|------------------|------|-----------------------------|--------|------------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|

| Si515            | VCXO | Single<br>(CMOS)            | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE               | -                | -                | CLK               | NC                |

| Si515            | VCXO | Single<br>(Diff)            | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE               | -                | -                | CLK+              | CLK-              |

| Si516            | VCXO | Dual<br>(CMOS)              | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | FS               | -                | -                | CLK               | NC                |

| Si516            | VCXO | Dual (Diff)                 | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | FS               | -                | -                | CLK+              | CLK-              |

| Si550            | VCXO | Single                      | 6      | 5x7                    | Vc               | OE               | -                | -                | CLK+              | CLK-              |

| Si552            | VCXO | Dual                        | 6      | 5x7                    | Vc               | FS               | -                | -                | CLK+              | CLK-              |

| Si554            | VCXO | Quad                        | 8      | 5x7                    | Vc               | OE               | FS1              | FS0              | CLK+              | CLK-              |

| Si565            | VCXO | Single                      | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE               | -                | -                | CLK+              | CLK-              |

| Si566            | VCXO | Dual                        | 6      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | FS               | -                | -                | CLK+              | CLK-              |

| Si567            | VCXO | Quad                        | 8      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE               | FS1              | FS0              | CLK+              | CLK-              |

| Si569            | VCXO | Single/<br>Dual (or<br>I2C) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE/FS            | SDA              | SCL              | CLK+              | CLK-              |

| Si595            | VCXO | Single                      | 6      | 5x7, 3.2x5             | Vc               | OE               | -                | -                | CLK+              | CLK-              |

| Si596            | VCXO | Dual                        | 6      | 5x7, 3.2x5             | Vc               | FS               | -                | -                | CLK+              | CLK-              |

| Si597            | VCXO | Quad                        | 8      | 5x7                    | Vc               | OE               | FS1              | FS0              | CLK+              | CLK-              |

# 7. Supported Devices - Software Controlled Mode - I<sup>2</sup>C

If using the Si5XXUC-EVB with a device that utilizes the  $I^2C$  bus for making frequency or other changes to the device, this "software controlled mode" section should be used to configure the EVB.

If you have a device installed that is either fixed frequency or has pin-controlled output frequency, refer to Section 6. Supported Devices - Stand-Alone Mode.

The tables below show I<sup>2</sup>C XO and I<sup>2</sup>C VCXO devices supported by the Si5xxUC-EVB along with possible package sizes and control pin mapping. The control pin mapping can be used to determine the corresponding switch settings on the Si5xxUC-EVB when using software controlled mode.

Table 7.1. I<sup>2</sup>C XOs

| SiLabs<br>Device | Type | # Freqs                                    | # Pins | Pkg Sizes<br>(mm x mm) | Pin 1<br>Control | Pin 2<br>Control | Pin 7<br>Control | Pin 8<br>Control | Pin 4 Out-<br>put | Pin 5 Out-<br>put |

|------------------|------|--------------------------------------------|--------|------------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|

| Si514            | хо   | I2C                                        | 6      | 5x7, 3.2x5,<br>2.5x3.2 | SDA              | SCL              | -                | -                | CLK+              | CLK-              |

| Si544            | хо   | I <sup>2</sup> C or (Single/<br>Dual/Quad) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-              |

| Si549            | хо   | I <sup>2</sup> C or (Single/<br>Dual/Quad) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-              |

| Si564            | хо   | I <sup>2</sup> C or (Single/<br>Dual/Quad) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | OE/NC/FS         | OE/NC/FS         | SDA/FS1          | SCL/FS0          | CLK+              | CLK-              |

| Si570            | хо   | I <sup>2</sup> C                           | 8      | 5x7                    | NC               | OE               | SDA              | SCL              | CLK+              | CLK-              |

| Si598            | хо   | I <sup>2</sup> C                           | 8      | 5x7                    | NC               | OE               | SDA              | SCL              | CLK+              | CLK-              |

Table 7.2. I<sup>2</sup>C VCXOs

| SiLabs<br>Device | Туре | # Freqs                               | # Pins | Pkg Sizes<br>(mm x mm) | Pin 1<br>Control | Pin 2<br>Control | Pin 7<br>Control | Pin 8<br>Control | Pin 4 Out-<br>put | Pin 5 Out-<br>put |

|------------------|------|---------------------------------------|--------|------------------------|------------------|------------------|------------------|------------------|-------------------|-------------------|

| Si569            | vcxo | I <sup>2</sup> C or (Single/<br>Dual) | 8      | 5x7, 3.2x5,<br>2.5x3.2 | Vc               | OE/FS            | SDA              | SCL              | CLK+              | CLK-              |

| Si571            | vcxo | I <sup>2</sup> C                      | 8      | 5x7                    | Vc               | OE               | SDA              | SCL              | CLK+              | CLK-              |

| Si599            | VCXO | I <sup>2</sup> C                      | 8      | 5x7                    | Vc               | OE               | SDA              | SCL              | CLK+              | CLK-              |

### 8. USB Port and External Powering

The USB port on the Si5xxUC-EVB utilizes a micro-USB connector that is located on the left edge of the board on the bottom side. A 2-meter micro USB cable is provided with the EVB kit. Any micro USB cable can be used that supports full USB connectivity.

If powering the EVB via the USB port, make sure switch SW5 is in the "USB" position. If properly connected to a live USB port, the green VBUS 5V should illuminate.

If powering the board via an external +5 V power supply, make sure SW5 is in the "EXT" position. Once +5 V is connected to the board via the +5V EXT connections, the green +5V EXT LED should illuminate.

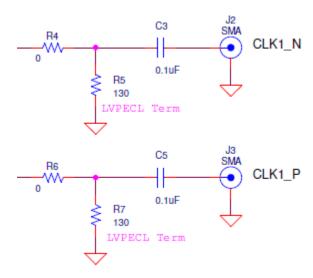

#### 9. Output Clock Terminations

The drawing in the figure below shows the default output termination circuit for CLK1 output of the Si5xxUC-EVB. This default source termination is for typical 3.3 V LVPECL. CLK2 and CLK3 are also terminated similarly for 3.3 V LVPECL. If not using LVPECL, this termination circuit may require component modification. The following table gives examples of recommended output termination components for various output formats when using Si51x, Si53x, Si54x, Si55x, Si56x, Si57x, and Si59x devices, but always refer to the specific device data sheet and/or appropriate application note for details of required output source termination for the specific device being evaluated.

Note that LVPECL, LVDS, and CML output formats require a 50  $\Omega$  termination of each output at the receiver (or 100  $\Omega$  differential). These termination components must be placed as close to the receiver as possible and are therefore not included on the Si5xxUC-EVB layout.

Figure 9.1. CLK1 Output Default Terminations

Table 9.1. Example Output Clock Source Terminations (Si51x, Si53x, Si54x, Si55x, Si56x, Si57x, and Si59x only)

| Output Format            | Series Resistor Position (e.g., R4, R6) | Parallel Resistor Position<br>(e.g., R5, R7) | Series Capacitor Position<br>(e.g., C3, C5) |  |

|--------------------------|-----------------------------------------|----------------------------------------------|---------------------------------------------|--|

| LVPECL 3.3 V: AC coupled | 0 Ω                                     | 130 Ω                                        | 0.1µF                                       |  |

| LVPECL 2.5 V: AC coupled | 0 Ω                                     | 90 Ω                                         | 0.1μF                                       |  |

| LVPECL: DC coupled       | 0 Ω                                     | Remove                                       | replace w/ 0 Ω                              |  |

| LVDS : AC coupled        | 0 Ω                                     | Remove                                       | 0.1μF                                       |  |

| LVDS : DC coupled        | 0 Ω                                     | Remove                                       | replace w/ 0 Ω                              |  |

| HCSL                     | 0 Ω                                     | Remove                                       | replace w/ 0 Ω                              |  |

| CML                      | 0 Ω                                     | Remove                                       | 0.1µF                                       |  |

| LVCMOS : AC coupled      | 0 Ω                                     | Remove                                       | 0.1µF                                       |  |

| LVCMOS : DC coupled      | 0 Ω                                     | Remove                                       | replace w/ 10 Ω                             |  |

#### 10. EVB Test Points and LEDs

#### 10.1 Test Points

The Si5xxUC-EVB has many test points that are useful for probing various nodes and/or making connections to external test equipment. Please refer to the schematic for the functionality of the various test points.

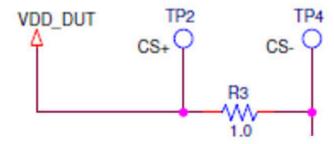

One set of test points in particular provides oscillator current sense capability and is shown in the drawing below. These two test points allow an external voltage measurement to be taken across the two test points to determine the current being used by the oscillator. Since the resistor value is 1  $\Omega$ , the voltage measured across these 2 test points corresponds to the current through the resistor. For example, if the measured voltage is 75 mV, the current flow is 75 mA. Each oscillator site has this current sense circuit.

Figure 10.1. Current Sense Test Points

#### 10.2 LEDs

The Si5xxUC-EVB has 5 status LEDs as shown in table below. The board silkscreen identifies each LED.

Table 10.1. Status LEDs

| LED name | Color | Location | Description                                                                      |

|----------|-------|----------|----------------------------------------------------------------------------------|

| +5V_EXT  | Green | D1       | External +5 V source is present (independent of +5V_SELECT (SW5) switch setting) |

| VBUS_5V  | Green | D5       | USB +5 V is present (independent of +5V_SELECT (SW5) switch setting)             |

| VDD_3.3  | Green | D4       | On-board MCU 3.3 V is present                                                    |

| USB_ACT  | Red   | D3       | USB port activity                                                                |

| Aux      | Red   | D2       | TBD (spare)                                                                      |

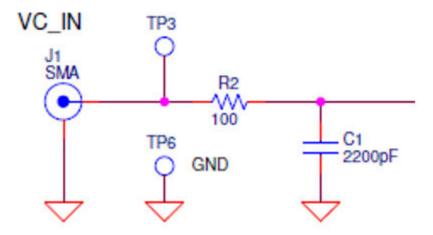

## 11. VCXO Voltage Control Input Circuit

The drawing below shows the VCXO control voltage input (VC\_IN) circuit used for evaluation of VCXOs. The VCXO control voltage can be applied using the J1 SMA connector, or using TP3/TP6. A simple RC circuit is included to low-pass filter any noise on the input. The RC circuit components can be removed or modified as required for your application.

Figure 11.1. VCXO Control Voltage Input "VC\_IN"

## 12. Programmable Oscillator Calculator Tool

The Programmable Oscillator Software Tool can be used with the Si5xxUC-EVB. This tool and corresponding Programmable Oscillator Software Tool User's Guide can be found on the Oscillator Software Tools page.

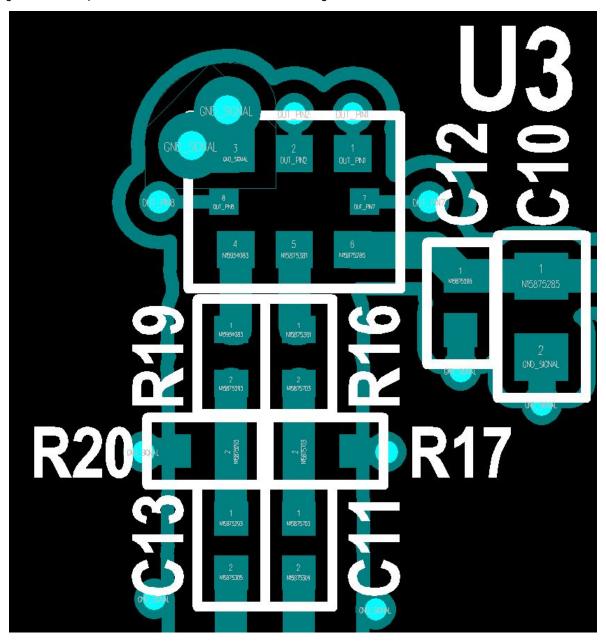

# 13. Layout of Board

#### 13.1 Si56x XO and VCXO 2.5x3.2mm Footprint Recommendation

For optimal thermal relief, use two ground vias next to the GND pin of the oscillator. Each via should have a 50mm diameter with a 25mm drill. These vias should be directly connected to the board's internal ground layers without the use of thermal relief spokes. This two via design has been implemented in all Si5xxUC-EVBs REV 4.0 or greater.

Figure 13.1. Si56x 2.5x3.2mm Footprint

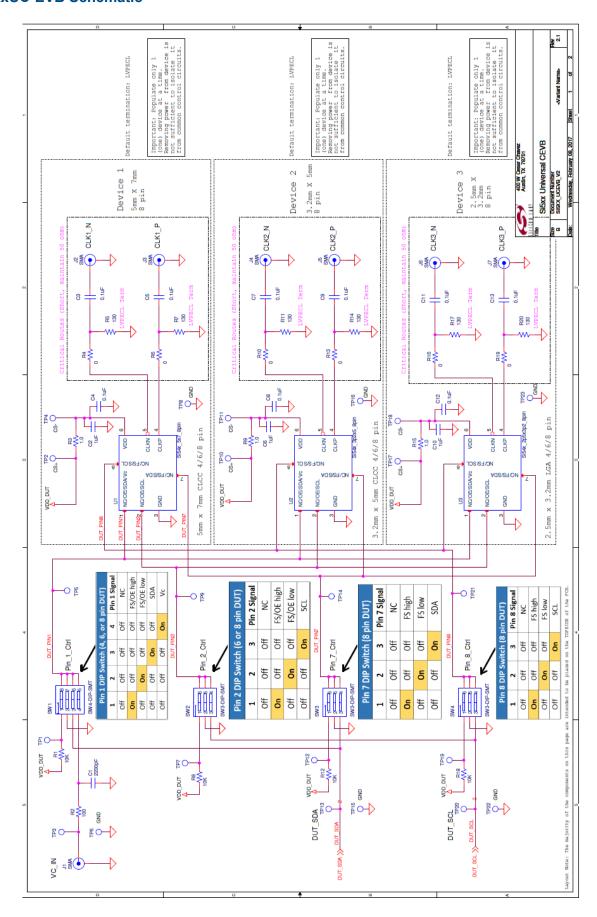

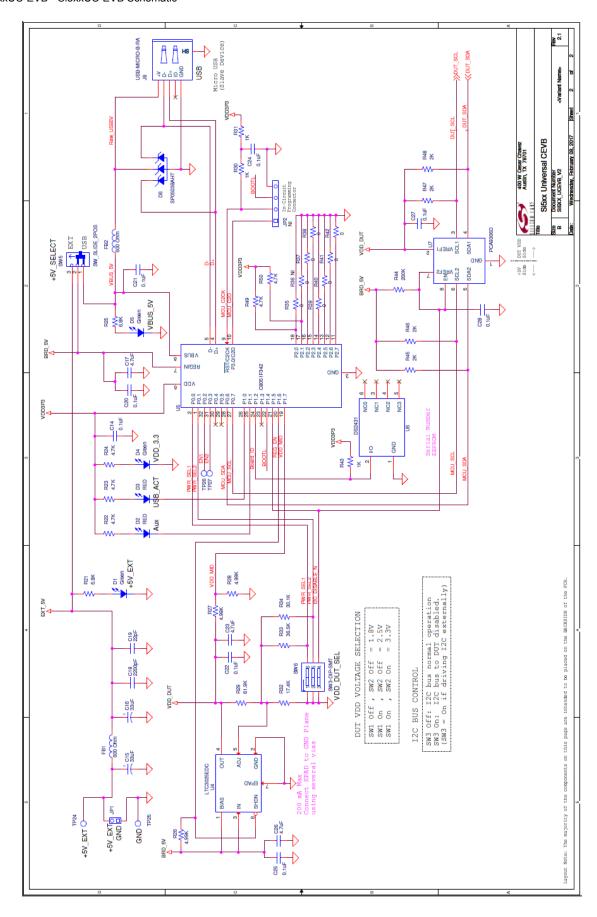

### 14. Si5xxUC-EVB Schematic

www.skyworksinc.com/CBPro

**Quality** www.skyworksinc.com/quality

**Support & Resources** www.skyworksinc.com/support

## Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, Clockbuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.