Sample &

Buv

LMP90100, LMP90099, LMP90098, LMP90097

Support &

Community

SNAS510S - JANUARY 2011 - REVISED JANUARY 2016

# LMP90100 and LMP9009x Sensor AFE System: Multichannel, Low-Power, 24-Bit Sensor **AFE With True Continuous Background Calibration**

#### Features 1

- 24-Bit, Low-Power Sigma-Delta ADC

- True Continuous Background Calibration at all Gains

- In-Place System Calibration Using Expected Value Programming

- Low-Noise Programmable Gain (1x to 128x)

- Continuous Background Open / Short and Out-of-Range Sensor Diagnostics

- 8 Output Data Rates (ODR) With Single-Cycle Settling

- 2 Matched Excitation Current Sources From 100 µA to 1000 µA (LMP90100/LMP90098)

- 4-DIFF / 7-SE Inputs (LMP90100/LMP90099) .

- 2-DIFF / 4-SE Inputs (LMP90098/LMP90097)

- 7 General-Purpose Input/Output Pins

- Chopper-Stabilized Buffer for Low Offset

- SPI 4/3-wire With CRC Data Link Error Detection

- 50-Hz to 60-Hz Line Rejection at ODR ≤13.42 SPS

- Independent Gain and ODR Selection per Channel

- Supported by WEBENCH® Sensor AFE Designer

- Automatic Channel Sequencer

- **Key Specifications**

- ENOB/NFR Up to 21.5/19 Bits

- Offset Error (Typical) 8.4 nV

- Gain Error (Typical) 7 ppm

- Total Noise < 10 µV-rms

- Integral Nonlinearity (INL Maximum) ± 15 ppm of FSR

- Output Data Rates (ODR) 1.6775 214.65 SPS

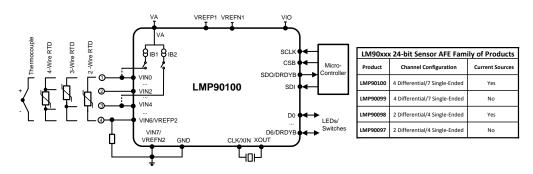

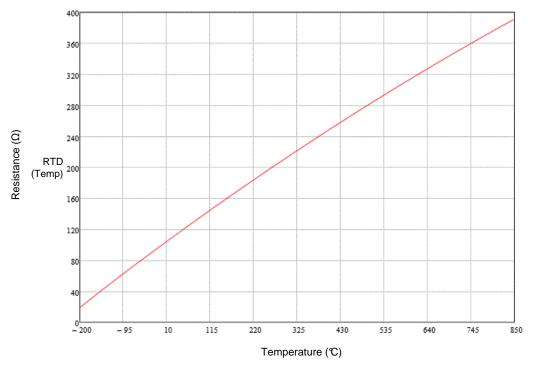

# **Typical Application Schematic**

- Analog Voltage, VA 2.85 to 5.5 V

- Operating Temp Range –40°C to 125°C

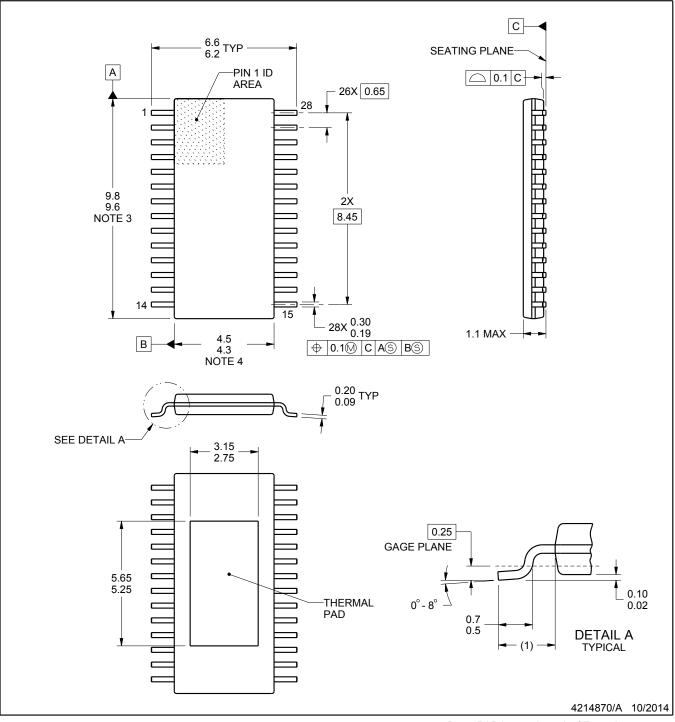

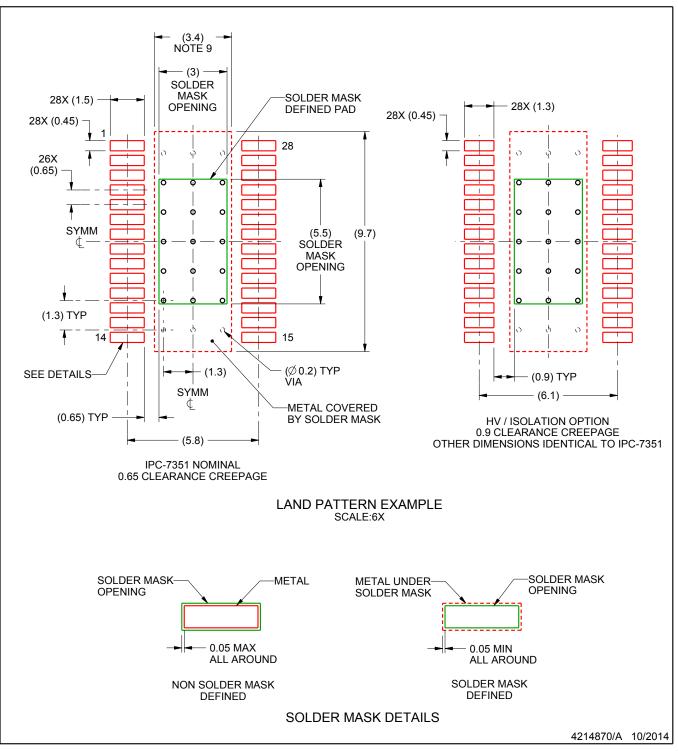

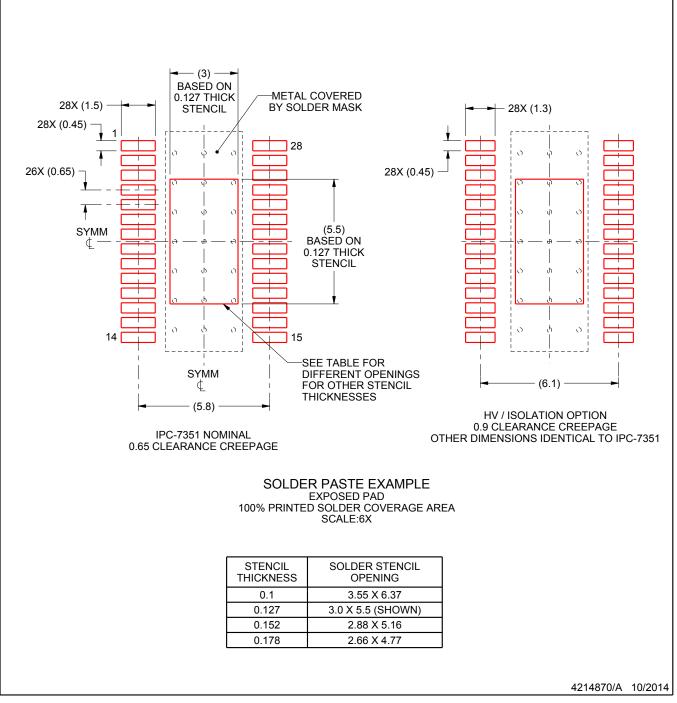

- 28-Pin HTSSOP Exposed Pad

# 2 Applications

- **Temperature and Pressure Transmitters**

- Strain Gauge Interface

- Industrial Process Control

# 3 Description

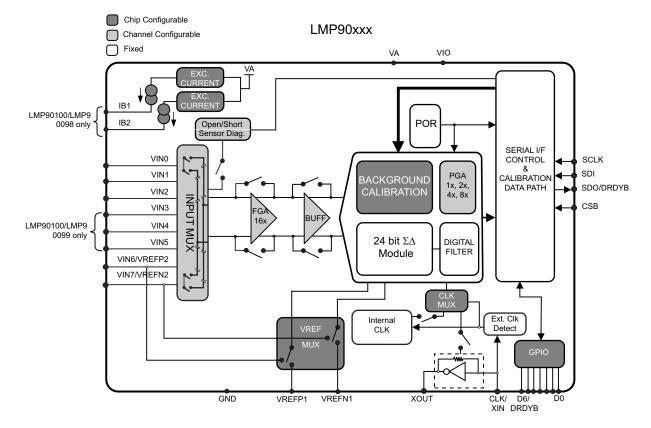

The LMP90xxx is a highly integrated, multichannel, low-power, 24-bit Sensor AFEs. The devices features a precision, 24-bit Sigma-Delta analog-to-digital converter (ADC) with a low-noise programmable gain amplifier and a fully differential high-impedance input multiplexer. A true analog continuous background calibration feature allows calibration at all gains and output data rates without interrupting the signal path. The background calibration feature essentially eliminates gain and offset errors across temperature and time, providing measurement accuracy without sacrificing speed and power consumption.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE               | BODY SIZE (NOM)           |                   |

|-------------|-----------------------|---------------------------|-------------------|

| LMP90097    |                       |                           |                   |

| LMP90098    | HTSSOP (28) 9.70 mm x | HTSSOP (28) 9.70 mm x 4.4 | 0.70 mm v 4.40 mm |

| LMP90099    |                       |                           | 9.70 mm x 4.40 mm |

| LMP90100    |                       |                           |                   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

NSTRUMENTS

**EXAS**

# **Table of Contents**

| 1 | Feat | ures 1                                    |

|---|------|-------------------------------------------|

| 2 | Арр  | lications 1                               |

| 3 | Des  | cription 1                                |

| 4 |      | cal Application Schematic 1               |

| 5 | Revi | sion History                              |

| 6 | Dese | cription (continued)                      |

| 7 | Pin  | Configuration and Functions 4             |

| 8 | Spe  | cifications5                              |

|   | 8.1  | Absolute Maximum Ratings 5                |

|   | 8.2  | ESD Ratings5                              |

|   | 8.3  | Recommended Operating Conditions5         |

|   | 8.4  | Thermal Information5                      |

|   | 8.5  | Electrical Characteristics 6              |

|   | 8.6  | SPI Timing Requirements 11                |

|   | 8.7  | CBS Setup and Hold Timing Requirements 11 |

|   | 8.8  | SCLK and SDI Timing Requirements 12       |

|   | 8.9  | SDO Timing Requirements 12                |

|   | 8.10 | SDO and DRDYB Timing Requirements 13      |

|   | 8.11 | Typical Characteristics 14                |

| 9 | Deta | iled Description 20                       |

|   | 9.1  | Overview 20                               |

|   | 9.2  | Functional Block Diagram 20               |

|   |      |                                           |

|    | 9.3  | Feature Description               | 20              |

|----|------|-----------------------------------|-----------------|

|    | 9.4  | Device Functional Modes           | 32              |

|    | 9.5  | Programming                       | 33              |

|    | 9.6  | Register Maps                     | 45              |

| 10 | Арр  | lication and Implementation       | <mark>56</mark> |

|    | 10.1 | Application Information           | 56              |

|    | 10.2 | Typical Applications              | 57              |

| 11 | Pow  | er Supply Recommendations         | <mark>63</mark> |

|    | 11.1 | VA and VIO                        | 63              |

|    | 11.2 | VREF                              | 63              |

| 12 | Laye | out                               | 64              |

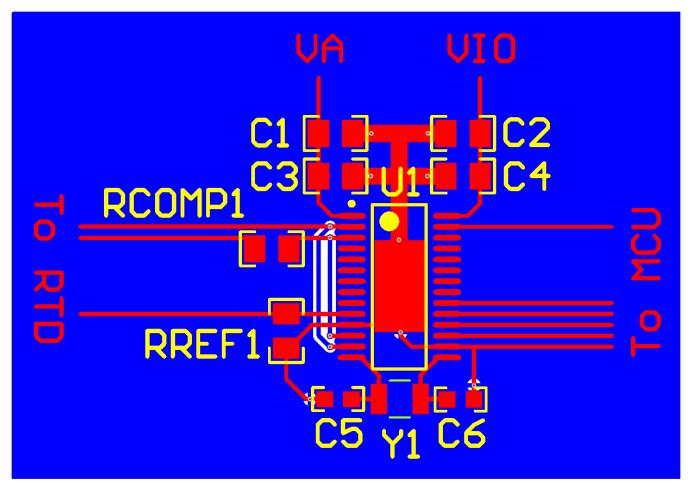

|    | 12.1 | Layout Guidelines                 | 64              |

|    | 12.2 | Layout Example                    | 64              |

| 13 | Dev  | ice and Documentation Support     | 65              |

|    | 13.1 | Device Support                    | 65              |

|    | 13.2 | Related Links                     | 66              |

|    | 13.3 | Community Resources               | 66              |

|    | 13.4 | Trademarks                        | 66              |

|    | 13.5 | Electrostatic Discharge Caution   | 66              |

|    | 13.6 | Glossary                          | 66              |

| 14 | Мес  | hanical, Packaging, and Orderable |                 |

|    |      | mation                            | <mark>66</mark> |

|    |      |                                   |                 |

# 5 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision R (January 2015) to Revision S  | Page |

|-------------------------------------------------------|------|

| Changed Buffer Enable/Disable.                        |      |

| Changed BUF_EN = 1 to 0.                              | 56   |

|                                                       |      |

| Changes from Revision Q (December 2014) to Revision R | Page |

| Added SDO Timing Requirements back in                 | 12   |

#### Changes from Revision P (March 2013) to Revision Q

| Page |

|------|

|------|

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Added footnote to INL, GE, and Crosstalk specifications.                                                                                                                                                                                                                                                                     | 6  |

| • | Changed t <sub>DOD1</sub> specification to 27ns                                                                                                                                                                                                                                                                              | 12 |

| • | Added sentence to the end of the Reset and Restart section                                                                                                                                                                                                                                                                   | 32 |

| • | Deleted CH_STS from Compute the CRC sentence                                                                                                                                                                                                                                                                                 | 40 |

|   |                                                                                                                                                                                                                                                                                                                              |    |

| C | hanges from Revision O (March 2013) to Revision P P | Page |

|---|-----------------------------------------------------|------|

| • | Changed layout of National Data Sheet to TI format  | . 48 |

# 6 Description (continued)

Another feature of the LMP90100/LMP90099/LMP90098/LMP90097 is continuous background sensor diagnostics, allowing the detection of open and short-circuit conditions and out-of-range signals, without requiring user intervention, resulting in enhanced system reliability.

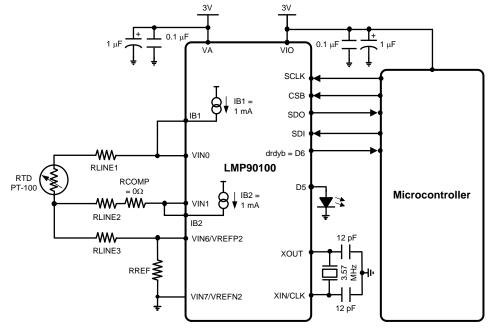

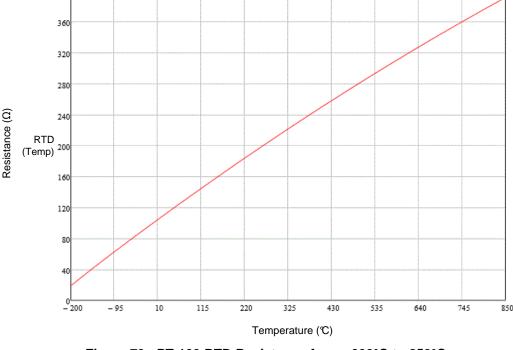

Two sets of independent external reference voltage pins allow multiple ratiometric measurements. In addition, two matched programmable current sources are available in the LMP90100/LMP90098 to excite external sensors such as resistive temperature detectors and bridge sensors. Furthermore, seven GPIO pins are provided for interfacing to external LEDs and switches to simplify control across an isolation barrier.

Collectively, these features make the LMP90100/LMP90099/LMP90098/LMP90097 complete analog front-ends for low-power, precision sensor applications such as temperature, pressure, strain gauge, and industrial process control. The LMP90100/LMP90099/LMP90098/LMP90097 are ensured over the extended temperature range of -40°C to +125°C and are available in a 28-pin HTSSOP package with an exposed pad.

NSTRUMENTS

EXAS

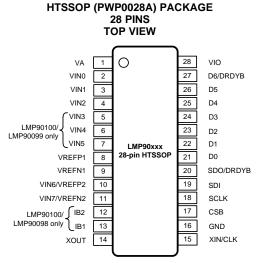

# 7 Pin Configuration and Functions

See below for specific information regarding options LMP90099, LMP90098, and LMP90097.

|               | PIN                                      | TVDE           | DECODIDITION                                                   |  |

|---------------|------------------------------------------|----------------|----------------------------------------------------------------|--|

| NAME          | NO.                                      | TYPE           | DESCRIPTION                                                    |  |

| VA            | 1                                        | Analog Supply  | Analog power supply pin                                        |  |

| VIN0 to VIN2  | 2 to 4                                   | Analog Input   | Analog input pins                                              |  |

| VIN3 to VIN5  | 5 to 7<br>(LMP90100, LMP90099<br>only)   | Analog Input   | Analog input pins                                              |  |

| VIN3 to VIN5  | 5 - 7<br>(LMP90098, LMP90097<br>only)    | No Connect     | No connect: must be left unconnected                           |  |

| VREFP1        | 8                                        | Analog Input   | Positive reference input                                       |  |

| VREFN1        | 9                                        | Analog Input   | Negative reference input                                       |  |

| VIN6 / VREFP2 | 10                                       | Analog Input   | Analog input pin or VREFP2 input                               |  |

| VIN7 / VREFN2 | 11                                       | Analog Input   | Analog input pin or VREFN2 input                               |  |

| IB2, IB1      | 12 to 13<br>(LMP90100, LMP90098<br>only) | Analog Output  | Excitation current sources for external RTDs                   |  |

| IB2, IB1      | 12 - 13<br>(LMP90099, LMP90097<br>only)  | No Connect     | No connect: must be left unconnected                           |  |

| XOUT          | 14                                       | Analog Output  | External crystal oscillator connection                         |  |

| XIN / CLK     | 15                                       | Analog Input   | External crystal oscillator connection or external clock input |  |

| GND           | 16                                       | Ground         | Power supply ground                                            |  |

| CSB           | 17                                       | Digital Input  | Chip select bar                                                |  |

| SCLK          | 18                                       | Digital Input  | Serial clock                                                   |  |

| SDI           | 19                                       | Digital Input  | Serial data input                                              |  |

| SDO / DRDYB   | 20                                       | Digital Output | Serial data output and data ready bar                          |  |

| D0 to D5      | 21 to 26                                 | Digital IO     | General purpose input/output (GPIO) pins                       |  |

| D6 / DRDYB    | 27                                       | Digital IO     | General purpose input/output pin or data ready bar             |  |

| VIO           | 28                                       | Digital Supply | Digital input/output supply pin                                |  |

| Thermal Pad   | _                                        | _              | You can leave this thermal pad floating.                       |  |

#### **Pin Functions**

# 8 Specifications

# 8.1 Absolute Maximum Ratings

See (1)(2)(3)

|                  |                                                        | MIN  | MAX     | UNIT |

|------------------|--------------------------------------------------------|------|---------|------|

| V <sub>A</sub>   | Analog Supply Voltage                                  | -0.3 | 6.0     | V    |

| V <sub>IO</sub>  | Digital I/O Supply Voltage                             | -0.3 | 6.0     | V    |

| $V_{REF}$        | Reference Voltage                                      | -0.3 | VA+0.3  | V    |

|                  | Voltage on Any Analog Input Pin to GND <sup>(4)</sup>  | -0.3 | VA+0.3  | V    |

|                  | Voltage on Any Digital Input PIN to GND <sup>(4)</sup> | -0.3 | VIO+0.3 | V    |

|                  | Voltage on SDO <sup>(4)</sup>                          | -0.3 | VIO+0.3 | V    |

|                  | Input Current at Any Pin <sup>(4)</sup>                |      | 5       | mA   |

|                  | Output Current Source or Sink by SDO                   |      | 3       | mA   |

|                  | Total Package Input and Output Current                 |      | 20      | mA   |

| $T_{JMAX}$       | Junction Temperature                                   |      | 150     | °C   |

| T <sub>stg</sub> | Storage Temperature                                    | -65  | 150     | °C   |

All voltages are measured with respect to GND, unless otherwise specified (1)

(2)Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the *Electrical Characteristics*. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

For soldering specifications: see product folder at www.ti.com and SNOA549.

(4)When the input voltage (VIN) exceeds the power supply (VIN < GND or VIN > VA), the current at that pin must be limited to 5mA and VIN has to be within the Absolute Maximum Rating for that pin. The 20 mA package input current rating limits the number of pins that can safely exceed the power supplies with current flow to four pins.

# 8.2 ESD Ratings

|                        |                         |                                                                                     | VALUE | UNIT |

|------------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

|                        |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                   | ±2500 |      |

| V <sub>(ESD)</sub> Ele | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left(2\right)}$ | ±1250 | V    |

|                        |                         | Machine Model (MM)                                                                  | +200  |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (1)

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

# 8.3 Recommended Operating Conditions

|                 |                                                  | MIN             | MAX                     | UNIT |

|-----------------|--------------------------------------------------|-----------------|-------------------------|------|

| V <sub>A</sub>  | Analog Supply Voltage                            | 2.85            | 5.5                     | V    |

| V <sub>IO</sub> | Digital I/O Supply Voltage                       | 2.7             | 5.5                     | V    |

| V <sub>IN</sub> | Full Scale Input Range                           |                 | ±V <sub>REF</sub> / PGA | V    |

| $V_{REF}$       | Reference Voltage                                | 0.5             | VA                      | V    |

|                 | Temperature Range for Electrical Characteristics | $T_{MIN} = -40$ | T <sub>MAX</sub> = 125  | °C   |

| T <sub>A</sub>  | Operating Temperature Range                      | -40             | 125                     | °C   |

### 8.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                                          | LMP90100,<br>LMP9009x<br>PWP | UNIT |

|------------------------------------------------------------------------|------------------------------|------|

|                                                                        | 28 PINS                      |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> | 41                           | °C/W |

(1)For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953. The maximum power dissipation is a function of  $T_{J(MAX)}$  AND  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient (2)temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ .

Copyright © 2011-2016, Texas Instruments Incorporated

SNAS510S - JANUARY 2011 - REVISED JANUARY 2016

# 8.5 Electrical Characteristics

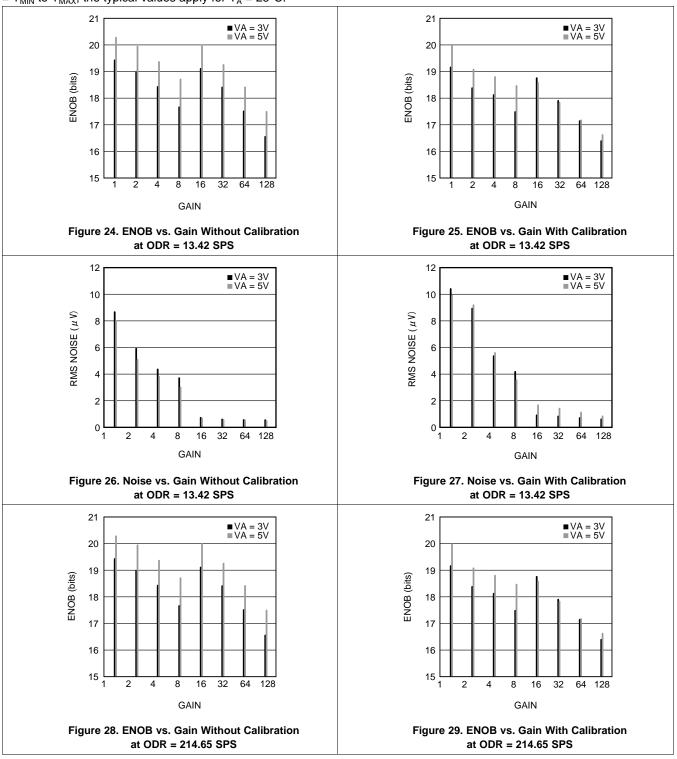

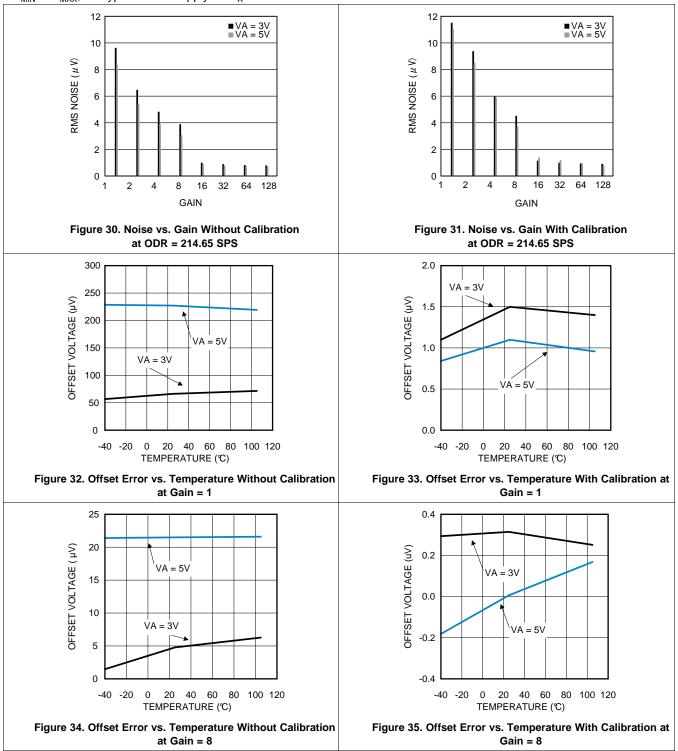

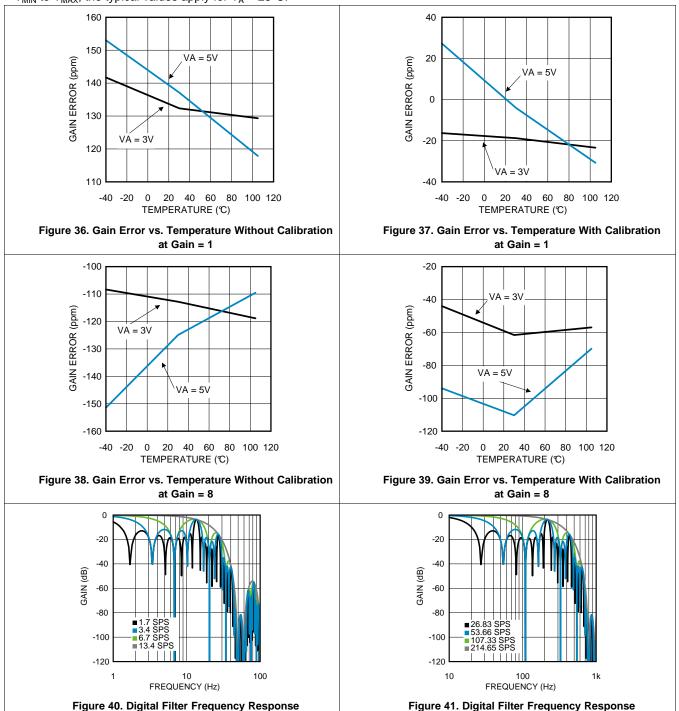

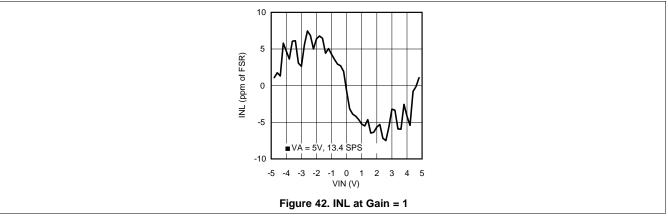

Unless otherwise noted, the key for the condition is (VA = VIO = VREF) / ODR (SPS) / buffer / calibration / gain. The typical values apply for  $T_A = 25^{\circ}$ C.

|        | PARAMETER                             | TEST CONDIT                                       | IONS        | MIN    | TYP                              | MAX                | UNIT                   |  |

|--------|---------------------------------------|---------------------------------------------------|-------------|--------|----------------------------------|--------------------|------------------------|--|

| n      | Resolution                            |                                                   |             |        | 24                               |                    | Bits                   |  |

| ENOB / | Effective Number of Bits              | 3V / all / ON / OFF / all. Shorted                | d input.    |        | Table 1                          |                    | Bits                   |  |

| NFR    | and Noise Free Resolution             | 5V / all / ON / OFF / all. Shorted                | d input.    |        | Table 3                          |                    | Bits                   |  |

| ODR    | Output Data Rates                     |                                                   |             | 1.6675 | Table 1                          | 214.6              | SPS                    |  |

|        | Gain                                  | FGA × PGA                                         |             | 1      | Table 1                          | 128                |                        |  |

| INU    | Integral Non Linearity (1)            | 3V / 214.65 / ON / ON / 1                         |             | -15    | ± 7                              | +15                | ppm                    |  |

| INL    | Integral Non-Linearity <sup>(1)</sup> | 3V & 5V / 214.65 / ON / ON / 1                    |             | ± 15   |                                  | ppm                |                        |  |

|        | Total Naisa                           | 3V / all / ON / ON / all. Shorted                 | input.      |        | Table 2                          |                    | μV                     |  |

|        | Total Noise                           | 5V / all / ON / OFF / all. Shorted                | d input.    |        | Table 4                          |                    | μV                     |  |

|        |                                       | 3V & 5V / all / ON or OFF / ON                    | / all       |        | Below<br>Noise<br>Floor<br>(rms) |                    | μV                     |  |

| OE     | Offset Error                          | 3V / 214.65 / ON / ON / 1                         |             |        | 1.22                             | 9.52               | μV                     |  |

|        |                                       | 3V / 214.65 / ON / ON / 128                       |             |        | 0.00838                          | 0.70               | μV                     |  |

|        |                                       | 5V / 214.65 / ON / ON / 1                         |             |        | 1.79                             | 8.25               | μV                     |  |

|        |                                       | 5V / 214.65 / ON / ON / 128                       |             |        | 0.0112                           | 0.63               | μV                     |  |

|        |                                       | 3V & 5V / 214.65 / ON or OFF                      | / OFF / 1-8 |        | 100                              |                    | nV/°C                  |  |

|        |                                       | 3V & 5V / 214.65 / ON / ON / 1                    | -8          |        | 3                                |                    | nV/°C                  |  |

|        | Offeret Drift Over Terrer (1)         | 3V & 5V / 214.65 / ON / OFF /                     | 16          |        | 25                               |                    | nV/°C                  |  |

|        | Offset Drift Over Temp <sup>(1)</sup> | 3V & 5V / 214.65 / ON / ON / 1                    | 6           |        | 0.4                              |                    | nV/°C                  |  |

|        |                                       | 3V & 5V / 214.65 / ON / OFF /                     | 128         |        | 6                                |                    | nV/°C                  |  |

|        |                                       | 3V & 5V / 214.65 / ON / ON / 1                    | 28          |        | 0.125                            |                    | nV/°C                  |  |

|        | Offset Drift over Time <sup>(1)</sup> | 5V / 214.65 / ON / OFF / 1, T <sub>A</sub>        |             | 2360   |                                  | nV / 1000<br>hours |                        |  |

|        | Onset Drift over Time (*)             | 5V / 214.65 / ON / ON / 1, T <sub>A</sub> = 150°C |             |        | 100                              |                    | nV / 1000<br>hours     |  |

|        |                                       | 25°C                                              |             |        | 7                                |                    |                        |  |

|        |                                       | 3V & 5V / 214.65 / ON / ON / 1                    | Full Range  | -80    |                                  | 80                 | ppm                    |  |

| GE     | Gain Error <sup>(1)</sup>             | 3V & 5V / 13.42 / ON / ON / 16                    |             |        | 50                               |                    | ppm                    |  |

|        |                                       | 3V & 5V / 13.42 / ON / ON / 64                    |             |        | 50                               |                    | ppm                    |  |

|        |                                       | 3V & 5V / 13.42 / ON / ON / 12                    |             | 100    |                                  | ppm                |                        |  |

|        | Gain Drift over Temp <sup>(1)</sup>   | 3V & 5V / 214.65 / ON / ON / a                    | I           |        | 0.5                              |                    | ppm/°C                 |  |

|        | Gain Drift over Time <sup>(1)</sup>   | 5V / 214.65 / ON / OFF / 1, T <sub>A</sub>        | = 150°C     |        | 5.9                              |                    | ppm /<br>1000<br>hours |  |

|        | Gain Dhit over Time (*)               | 5V / 214.65 / ON / ON / 1, T <sub>A</sub> =       | 150°C       |        | 1.6                              |                    | ppm /<br>1000<br>hours |  |

| CONVER | TER'S CHARACTERISTIC                  |                                                   |             |        |                                  |                    |                        |  |

|        |                                       |                                                   | 25°C        |        | 117                              |                    |                        |  |

|        |                                       | DC, 3V / 214.65 / ON / ON / 1                     | Full Range  | 70     |                                  |                    | dB                     |  |

| CMRR   | Input Common Mode<br>Rejection Ratio  | DC, 5V / 214.65 / OFF / OFF /                     | 25°C        |        | 120                              |                    | dB                     |  |

|        | Rejection Ratio                       | 1                                                 | Full Range  | 90     |                                  |                    | 1                      |  |

|        |                                       | 50/60 Hz, 5V / 214.65 / OFF / 0                   |             | 117    |                                  | dB                 |                        |  |

|        | Reference Common Mode<br>Rejection    | VREF = 2.5V                                       |             |        | 101                              |                    | dB                     |  |

(1) This parameter is specified by design and/or characterization and is not tested in production

6 Submit Documentation Feedback

# **Electrical Characteristics (continued)**

Unless otherwise noted, the key for the condition is (VA = VIO = VREF) / ODR (SPS) / buffer / calibration / gain. The typical values apply for  $T_A = 25^{\circ}$ C.

|         | PARAMETER                                                                              | TEST CONDIT                    | IONS       | MIN   | TYP  | MAX            | UNIT |  |

|---------|----------------------------------------------------------------------------------------|--------------------------------|------------|-------|------|----------------|------|--|

|         | Power Supply Rejection                                                                 | DC, 3V / 214.65 / ON / ON / 1  |            | 75    | 115  |                | dB   |  |

| PSRR    | Ratio                                                                                  | DC, 5V / 214.65 / ON / ON / 1  |            |       | 112  |                | dB   |  |

|         | Normal Mode Rejection                                                                  | 47 Hz to 63 Hz, 5V / 13.42 /   | 25°C       |       |      |                |      |  |

| NMRR    | Ratio <sup>(1)</sup>                                                                   | OFF / OFF / 1                  | Full Range | 78    |      |                | dB   |  |

|         |                                                                                        |                                | 25°C       |       | 136  |                | dB   |  |

|         | Cross-talk <sup>(1)</sup>                                                              | 3V / 214.65 / OFF / OFF / 1    | Full Range | 95    |      |                |      |  |

|         | Cross-taik (1)                                                                         |                                | 25°C       |       | 143  |                | dB   |  |

|         |                                                                                        | 5V / 214.65 / OFF / OFF / 1    | Full Range | 95    |      |                |      |  |

| POWER S | SUPPLY CHARACTERISTICS                                                                 |                                |            |       |      |                |      |  |

| VA      | Analog Supply Voltage                                                                  |                                |            | 2.85  | 3.0  | 5.5            | V    |  |

| VIO     | Digital Supply Voltage                                                                 |                                |            | 2.7   | 3.3  | 5.5            | V    |  |

|         |                                                                                        | 3V / 13.42 / OFF / OFF / 1,    | 25°C       |       | 400  |                |      |  |

|         |                                                                                        | ext. CLK                       | Full Range |       |      | 500            | μA   |  |

|         |                                                                                        | 5V / 13.42 / OFF / OFF / 1,    | 25°C       |       | 464  |                | μA   |  |

|         |                                                                                        | ext. CLK                       | Full Range |       |      | 555            |      |  |

|         |                                                                                        | 3V / 13.42 / ON / OFF / 64,    | 25°C       |       | 600  |                | μΑ   |  |

|         |                                                                                        | ext. CLK                       | Full Range |       |      | 700            |      |  |

|         |                                                                                        | 5V / 13.42 / ON / OFF / 64,    | 25°C       |       | 690  |                |      |  |

|         |                                                                                        | ext. CLK                       | Full Range |       |      | 800            | μA   |  |

|         |                                                                                        | 3V / 214.65 / ON / OFF / 64,   | 25°C       |       | 1547 |                |      |  |

|         |                                                                                        | int. CLK                       | Full Range |       |      | 1700           | μA   |  |

|         |                                                                                        | 5V / 214.65 / ON / OFF / 64,   | 25°C       |       | 1760 |                |      |  |

|         |                                                                                        | int. CLK F                     | Full Range |       |      | 2000           | μA   |  |

| IVA     | 3V / 214.65 / OFF / OFF / 1,           int. CLK           5V / 214.65 / OFF / OFF / 1, |                                | 25°C       |       | 826  |                |      |  |

|         |                                                                                        | Full Range                     |            |       | 1000 | μA             |      |  |

|         |                                                                                        | 25°C                           |            | 941   |      |                |      |  |

|         |                                                                                        | int. CLK                       | Full Range |       |      | 1100           | μA   |  |

|         |                                                                                        | Standby, 3V , int. CLK         |            |       | 3    | 10             | μA   |  |

|         |                                                                                        | Standby, 3V , ext. CLK         |            |       | 257  |                | μA   |  |

|         |                                                                                        | Standby, 5V, int. CLK          |            |       | 5    | 15             | μA   |  |

|         |                                                                                        | Standby, 3V, ext. CLK          |            |       | 300  |                | μA   |  |

|         |                                                                                        |                                | 25°C       |       | 2.6  |                |      |  |

|         |                                                                                        | Power-down, 3 V, int/ext CLK   | Full Range |       |      | 5              | μA   |  |

|         |                                                                                        |                                | 25°C       |       | 4.6  |                | -    |  |

|         |                                                                                        | Power-down, 5 V, int/ext CLK   | Full Range |       |      | 9              | μA   |  |

| REFEREN | ICE INPUT                                                                              | ŀ                              |            | I     |      |                |      |  |

| VREFP   | Positive Reference                                                                     |                                |            | VREFN |      | VA             | V    |  |

| VNEFF   |                                                                                        |                                |            | + 0.5 |      |                |      |  |

| VREFN   | Negative Reference                                                                     |                                |            | GND   |      | VREFP -<br>0.5 | V    |  |

| VREF    | Differential Reference                                                                 | VREF = VREFP - VREFN           |            | 0.5   |      | VA             | V    |  |

| ZREF    | Reference Impedance                                                                    | 3 V / 13.42 / OFF / OFF / 1    |            |       |      |                | MΩ   |  |

| IREF    | Reference Input                                                                        | 3 V / 13.42 / ON or OFF / ON o |            | ±2    |      | μA             |      |  |

| CREFP   | Capacitance of the Positive<br>Reference                                               | See <sup>(1)</sup> , gain = 1  |            | 6     |      | pF             |      |  |

Copyright © 2011–2016, Texas Instruments Incorporated

Submit Documentation Feedback 7

SNAS510S – JANUARY 2011 – REVISED JANUARY 2016

www.ti.com

# **Electrical Characteristics (continued)**

Unless otherwise noted, the key for the condition is (VA = VIO = VREF) / ODR (SPS) / buffer / calibration / gain. The typical values apply for  $T_A = 25^{\circ}$ C.

|                                              | PARAMETER                                | TEST CON                      | IDITIONS              | MIN            | TYP                                                                 | MAX       | UNIT  |

|----------------------------------------------|------------------------------------------|-------------------------------|-----------------------|----------------|---------------------------------------------------------------------|-----------|-------|

| CREFN                                        | Capacitance of the<br>Negative Reference | See <sup>(1)</sup> , gain = 1 |                       |                | 6                                                                   |           | pF    |

| ILREF                                        | Reference Leakage Current                | Power-down                    |                       |                | 1                                                                   |           | nA    |

| ANALOG                                       | INPUT                                    | Γ                             |                       |                |                                                                     |           |       |

|                                              |                                          | Gain = 1-8, buffer ON         |                       | GND +<br>0.1   |                                                                     | VA - 0.1  | V     |

| VINP                                         | Positive Input                           | Gain = 16 - 128, buffer ON    | GND +<br>0.4          |                | VA - 1.5                                                            | V         |       |

|                                              |                                          | Gain = 1-8, buffer OFF        |                       | GND            |                                                                     | VA        | V     |

|                                              |                                          | Gain = 1-8, buffer ON         |                       | GND +<br>0.1   |                                                                     | VA - 0.1  | V     |

| VINN Negative Input                          | Gain = 16 - 128, buffer ON               | I                             | GND +<br>0.4          |                | VA - 1.5                                                            | V         |       |

|                                              |                                          | Gain = 1-8, buffer OFF        |                       | GND            |                                                                     | VA        | V     |

| VIN                                          | Differential Input                       | VIN = VINP - VINN             |                       | ±VREF /<br>PGA |                                                                     |           |       |

| ZIN                                          | Differential Input Impedance             | ODR = 13.42 SPS               | DDR = 13.42 SPS       |                |                                                                     |           | MΩ    |

| CINP                                         | Capacitance of the Positive Input        | 5V / 214.65 / OFF / OFF /     |                       | 4              |                                                                     | pF        |       |

| CINN                                         | Capacitance of the<br>Negative Input     | 5V / 214.65 / OFF / OFF /     |                       | 4              |                                                                     | pF        |       |

| IIN                                          | Input Leakage Current                    | 3V & 5V / 13.42 / ON / OF     | F / 1-8               |                | 500                                                                 |           | pА    |

| IIIN                                         | Input Leakage Current                    | 3V & 5V / 13.42 / ON / OF     | F / 16 - 128          |                | 100                                                                 |           | pА    |

| DIGITAL I                                    | NPUT CHARACTERISTICS at                  | VA = VIO = VREF = 3.0V        |                       |                |                                                                     |           |       |

| VIH                                          | Logical "1" Input Voltage                |                               |                       | 0.7 x<br>VIO   |                                                                     |           | V     |

| VIL                                          | Logical "0" Input Voltage                |                               |                       |                | C                                                                   | ).3 x VIO | V     |

| IIL                                          | Digital Input Leakage<br>Current         |                               |                       | -10            |                                                                     | +10       | μA    |

| VHYST                                        | Digital Input Hysteresis                 |                               |                       |                | 0.1 x VIO                                                           |           | V     |

| DIGITAL (                                    | OUTPUT CHARACTERISTICS                   | at VA = VIO = VREF = 3.0V     | 1                     | 1              |                                                                     |           |       |

| VOH                                          | Logical "1" Output Voltage               | Source 300 µA                 |                       | 2.6            |                                                                     |           | V     |

| VOL                                          | Logical "0" Output Voltage               | Sink 300 µA                   |                       |                |                                                                     | 0.4       | V     |

| iozh,<br>Iozl                                | Tri-state Leakage Current                |                               |                       | -10            |                                                                     | 10        | μA    |

| COUT                                         | Tri-state Capacitance                    | See <sup>(1)</sup>            |                       |                | 5                                                                   |           | pF    |

| EXCITATI                                     | ON CURRENT SOURCES CH                    | ARACTERISTICS (LMP9010        | 00/LMP90098 only)     |                |                                                                     |           |       |

| IB1, IB2 Excitation Current Source<br>Output |                                          |                               |                       |                | 0, 100,<br>200, 300,<br>400, 500,<br>600, 700,<br>800, 900,<br>1000 |           | μΑ    |

|                                              |                                          | VA = VREF = 3 V 25°C          |                       |                | 2.5%                                                                |           |       |

|                                              | IB1/IB2 Tolerance                        |                               | Full Range            | -7%            |                                                                     | 7%        |       |

|                                              |                                          | VA = VREF = 5 V               | 25°C                  |                | 0.2%                                                                |           |       |

|                                              |                                          |                               | Full Range            | -3.5%          |                                                                     | 3.5%      |       |

|                                              | IB1/IB2 Output Compliance<br>Range       | VA = 3.0 V & 5.0 V, IB1/IB.   | 2 = 100 µA to 1000 µA |                | VA - 0.8                                                            |           | V     |

|                                              | IB1/IB2 Regulation                       | VA = 5.0 V, IB1/IB2 = 100     | μΑ to 1000 μΑ         |                | 0.07                                                                |           | % / V |

8

# **Electrical Characteristics (continued)**

Unless otherwise noted, the key for the condition is (VA = VIO = VREF) / ODR (SPS) / buffer / calibration / gain. The typical values apply for  $T_A = 25^{\circ}$ C.

|          | PARAMETER                  | TEST CONDITIONS                                           |                     | MIN | TYP    | MAX    | UNIT   |

|----------|----------------------------|-----------------------------------------------------------|---------------------|-----|--------|--------|--------|

|          |                            | VA = 3.0 V                                                |                     | 95  |        | ppm/°C |        |

| IBTC     | IB1/IB2 Drift              | VA = 5.0 V                                                |                     |     | 60     |        | ppm/°C |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.34%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 100 µA                                 | Full Range          |     |        | 1.53%  |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.22%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 200 µA                                 | Full Range          |     |        | 1%     |        |

|          |                            | 3V & 5V / 214.65 / OFF / OFF                              | 25°C                |     | 0.2%   |        |        |

|          |                            | / 1, IB1/IB2 = 300 µA                                     | Full Range          |     |        | 0.85%  |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.15%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 400 µA                                 | Full Range          |     |        | 0.8%   |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.14%  |        |        |

|          | ID1/ID2 Motobing           | OFF / 1, IB1/IB2 = 500 μA                                 | Full Range          |     |        | 0.7%   |        |

| IBMT     | IB1/IB2 Matching           | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.13%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 600 µA                                 | Full Range          |     |        | 0.7%   |        |

|          |                            | OFF / 1, IB1/IB2 = 700 μA                                 | 25°C                |     | 0.075% |        |        |

|          |                            |                                                           | Full Range          |     |        | 0.65%  |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /<br>OFF / 1, IB1/IB2 = 800 µA | 25°C                |     | 0.085% |        |        |

|          |                            |                                                           | Full Range          |     |        | 0.6%   |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.11%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 900 μA                                 | Full Range          |     |        | 0.55%  |        |

|          |                            | 3 V and 5 V / 214.65 / OFF /                              | 25°C                |     | 0.11%  |        |        |

|          |                            | OFF / 1, IB1/IB2 = 1000 µA                                | Full Range          |     |        | 0.45%  |        |

| IBMTC    | IB1/IB2 Matching Drift     | VA = 3.0 V and 5.0 V, IB1/IB2 =                           | = 100 μA to 1000 μA |     | 2      |        | ppm/°C |

| INTERNAL | _/EXTERNAL CLK             |                                                           |                     |     |        |        |        |

| CLKIN    | Internal Clock Frequency   |                                                           |                     |     | 893    |        | kHz    |

| CLKEXT   | External Clock Frequency   | See (1)                                                   |                     | 1.8 | 3.5717 | 7.2    | MHz    |

|          |                            | Input Low Voltage                                         |                     | 0   |        | V      |        |

|          | External Crystal Frequency | Input High Voltage                                        |                     |     | 1      |        | V      |

|          | External Crystal Frequency | Frequency                                                 |                     | 1.8 | 3.5717 | 7.2    | MHz    |

|          |                            | Start-up time                                             |                     | 7   |        | ms     |        |

| SCLK     | Serial Clock               |                                                           |                     |     |        | 10     | MHz    |

| Table 1. ENOB ( | (Noise Free Resolution) vs | s. Sampling Rate and Gain at VA | = VIO = VREF = 3 V |

|-----------------|----------------------------|---------------------------------|--------------------|

| TUDIO IL EILOD  |                            |                                 |                    |

|           | Gain of the ADC |           |           |           |           |           |           |           |  |  |

|-----------|-----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| ODR (SPS) | 1               | 2         | 4         | 8         | 16        | 32        | 64        | 128       |  |  |

| 1.6775    | 20.5 (18)       | 20.5 (18) | 19.5 (17) | 19 (16.5) | 20.5 (18) | 19.5 (17) | 19 (16.5) | 18 (15.5) |  |  |

| 3.355     | 20 (17.5)       | 20 (17.5) | 19 (16.5) | 18.5 (16) | 20 (17.5) | 19 (16.5) | 18.5 (16) | 17 (14.5) |  |  |

| 6.71      | 19.5 (17)       | 19.5 (17) | 18.5 (16) | 18 (15.5) | 19.5 (17) | 18.5 (16) | 17.5 (15) | 17 (14.5) |  |  |

| 13.42     | 19 (16.5)       | 18.5 (16) | 18 (15.5) | 17.5 (15) | 19 (16.5) | 18 (15.5) | 17.5 (15) | 16.5 (14) |  |  |

| 26.83125  | 20.5 (18)       | 20 (17.5) | 19.5 (17) | 19 (16.5) | 20 (17.5) | 19 (16.5) | 18 (15.5) | 17.5 (15) |  |  |

| 53.6625   | 20 (17.5)       | 19.5 (17) | 19 (16.5) | 18.5 (16) | 19.5 (17) | 18.5 (16) | 17.5 (15) | 17 (14.5) |  |  |

| 107.325   | 19.5 (17)       | 19 (16.5) | 18.5 (16) | 18 (15.5) | 19 (16.5) | 18 (15.5) | 17 (14.5) | 16.5 (14) |  |  |

| 214.65    | 19 (16.5)       | 18.5 (16) | 18 (15.5) | 17.5 (15) | 18.5 (16) | 17.5 (15) | 17 (14.5) | 16 (13.5) |  |  |

# Table 2. RMS Noise ( $\mu$ V) vs. Sampling Rate and Gain at VA = VIO = VREF = 3 V

| ODR (SPS) | Gain of the ADC |      |      |      |      |      |      |      |  |

|-----------|-----------------|------|------|------|------|------|------|------|--|

| ODR (SPS) | 1               | 2    | 4    | 8    | 16   | 32   | 64   | 128  |  |

| 1.6775    | 3.08            | 1.90 | 1.53 | 1.27 | 0.23 | 0.21 | 0.15 | 0.14 |  |

| 3.355     | 4.56            | 2.70 | 2.21 | 1.67 | 0.34 | 0.27 | 0.24 | 0.26 |  |

| 6.71      | 6.15            | 4.10 | 3.16 | 2.39 | 0.51 | 0.40 | 0.37 | 0.35 |  |

| 13.42     | 8.60            | 5.85 | 4.29 | 3.64 | 0.67 | 0.54 | 0.51 | 0.49 |  |

| 26.83125  | 3.35            | 2.24 | 1.65 | 1.33 | 0.33 | 0.27 | 0.26 | 0.25 |  |

| 53.6625   | 4.81            | 3.11 | 2.37 | 1.90 | 0.44 | 0.39 | 0.37 | 0.36 |  |

| 107.325   | 6.74            | 4.51 | 3.38 | 2.66 | 0.63 | 0.54 | 0.52 | 0.49 |  |

| 214.65    | 9.52            | 6.37 | 4.72 | 3.79 | 0.90 | 0.79 | 0.72 | 0.70 |  |

### Table 3. ENOB (Noise Free Resolution) vs. Sampling Rate and Gain at VA = VIO = VREF = 5 V

| SPS      | Gain of the ADC |           |           |           |           |           |           |           |  |  |

|----------|-----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| 373      | 1               | 2         | 4         | 8         | 16        | 32        | 64        | 128       |  |  |

| 1.6775   | 21.5 (19)       | 21.5 (19) | 20.5 (18) | 20 (17.5) | 21 (18.5) | 20.5 (18) | 19.5 (17) | 18.5 (16) |  |  |

| 3.355    | 21 (18.5)       | 21 (18.5) | 20 (17.5) | 19.5 (17) | 20.5 (18) | 20 (17.5) | 19 (16.5) | 18 (15.5) |  |  |

| 6.71     | 20.5 (18)       | 20 (17.5) | 19.5 (17) | 19 (16.5) | 20 (17.5) | 19.5 (17) | 19 (16.5) | 17.5 (15) |  |  |

| 13.42    | 20 (17.5)       | 19.5 (17) | 19 (16.5) | 18.5 (16) | 20 (17.5) | 19 (16.5) | 18 (15.5) | 17.5 (15) |  |  |

| 26.83125 | 21.5 (19)       | 21 (18.5) | 20.5 (18) | 20 (17.5) | 21 (18.5) | 20 (17.5) | 19.5 (17) | 18 (15.5) |  |  |

| 53.6625  | 21 (18.5)       | 20.5 (18) | 20 (17.5) | 19.5 (17) | 20.5 (18) | 19.5 (17) | 18.5 (16) | 17.5 (15) |  |  |

| 107.325  | 20.5 (18)       | 20 (17.5) | 19.5 (17) | 19 (16.5) | 20 (17.5) | 19 (16.5) | 18 (15.5) | 17 (14.5) |  |  |

| 214.65   | 20 (17.5)       | 19.5 (17) | 19 (16.5) | 18.5 (16) | 19.5 (17) | 18.5 (16) | 17.5 (15) | 16.5 (14) |  |  |

## Table 4. RMS Noise ( $\mu$ V) vs. Sampling Rate and Gain at VA = VIO = VREF = 5 V

| SPS      | Gain of the ADC |      |      |      |      |      |      |      |  |  |

|----------|-----------------|------|------|------|------|------|------|------|--|--|

| 353      | 1               | 2    | 4    | 8    | 16   | 32   | 64   | 128  |  |  |

| 1.6775   | 2.68            | 1.65 | 1.24 | 1.00 | 0.22 | 0.19 | 0.17 | 0.16 |  |  |

| 3.355    | 3.86            | 2.36 | 1.78 | 1.47 | 0.34 | 0.27 | 0.22 | 0.22 |  |  |

| 6.71     | 5.23            | 3.49 | 2.47 | 2.09 | 0.44 | 0.34 | 0.30 | 0.32 |  |  |

| 13.42    | 7.94            | 5.01 | 3.74 | 2.94 | 0.61 | 0.50 | 0.45 | 0.43 |  |  |

| 26.83125 | 2.90            | 1.86 | 1.34 | 1.08 | 0.29 | 0.24 | 0.23 | 0.23 |  |  |

| 53.6625  | 4.11            | 2.60 | 1.90 | 1.50 | 0.39 | 0.35 | 0.32 | 0.31 |  |  |

| 107.325  | 5.74            | 3.72 | 2.72 | 2.11 | 0.56 | 0.48 | 0.46 | 0.44 |  |  |

| 214.65   | 8.25            | 5.31 | 3.82 | 2.97 | 0.79 | 0.68 | 0.64 | 0.63 |  |  |

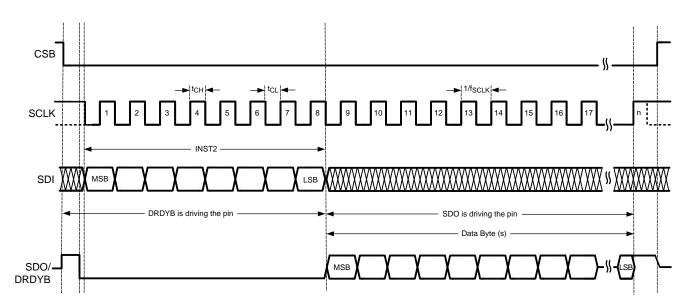

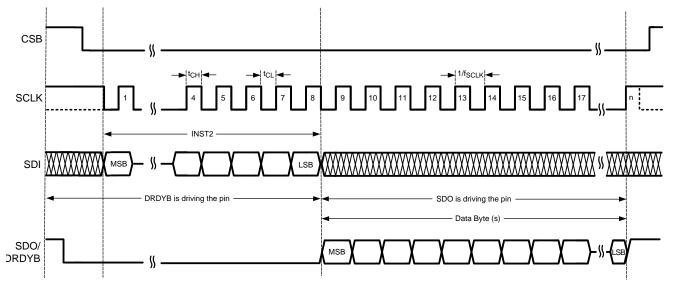

### 8.6 SPI Timing Requirements

| Unless otherwise noted, specified limits apply for VA = VIO = 3.0 V. |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

### Figure 1. SPI Timing Diagram

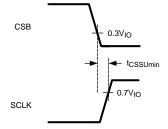

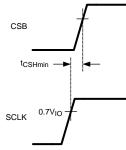

### 8.7 CBS Setup and Hold Timing Requirements

Unless otherwise noted, specified limits apply for VA = VIO = 3.0 V.

|                   |                                                  | MIN | NOM | MAX | UNIT |

|-------------------|--------------------------------------------------|-----|-----|-----|------|

| t <sub>CSSU</sub> | CSB Setup time prior to an SCLK rising edge      | 5   |     |     | ns   |

| t <sub>CSH</sub>  | CSB Hold time after the last rising edge of SCLK | 6   |     |     | ns   |

Figure 3. CSB Hold Timing

SNAS510S - JANUARY 2011 - REVISED JANUARY 2016

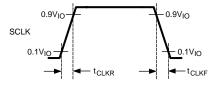

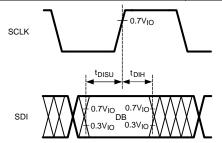

# 8.8 SCLK and SDI Timing Requirements

Unless otherwise noted, specified limits apply for VA = VIO = 3.0 V.

|                   |                                             | MIN | NOM  | MAX | UNIT |

|-------------------|---------------------------------------------|-----|------|-----|------|

| t <sub>CLKR</sub> | SCLK Rise time                              |     | 1.15 |     | ns   |

| t <sub>CLKF</sub> | SCLK Fall time                              |     | 1.15 |     | ns   |

| t <sub>DISU</sub> | SDI Setup time prior to an SCLK rising edge | 5   |      |     | ns   |

| t <sub>DIH</sub>  | SDI Hold time after an SCLK rising edge     | 6   |      |     | ns   |

Figure 4. SCLK Rise and Fall Time

Figure 5. SDI Setup and Hold Time

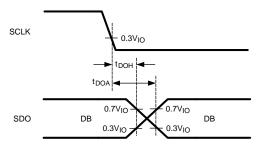

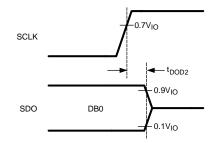

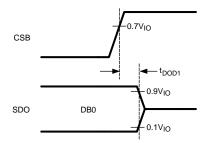

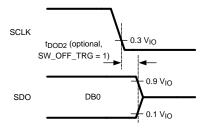

# 8.9 SDO Timing Requirements

Unless otherwise noted, specified limits apply for VA = VIO = 3.0 V.

|                   |                                               | MIN | NOM | MAX | UNIT |

|-------------------|-----------------------------------------------|-----|-----|-----|------|

| t <sub>DOA</sub>  | SDO Access time after a<br>SCLK falling edge  |     |     | 35  | ns   |

| t <sub>DOH</sub>  | SDO Hold time after a<br>SCLK falling edge    | 5   |     |     | ns   |

| t <sub>DOD1</sub> | SDO Disable time after the rising edge of CSB |     |     | 27  | ns   |

| t <sub>DOD2</sub> | SDO Disable time after<br>either edge of SCLK |     |     | 27  | ns   |

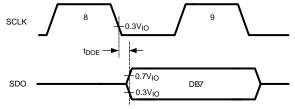

Figure 6. SDO and SCLK Timing

Figure 8. SDO Disable and SCLK Timing

Figure 7. SDO and  $\overline{\text{CS}}$  Timing

NSTRUMENTS

ÈXAS

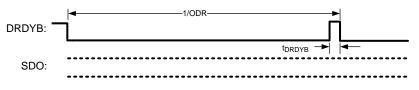

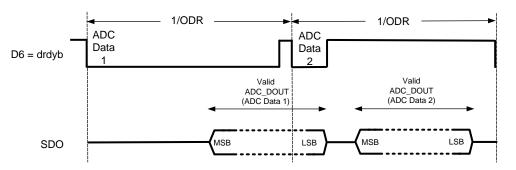

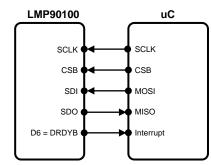

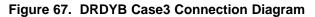

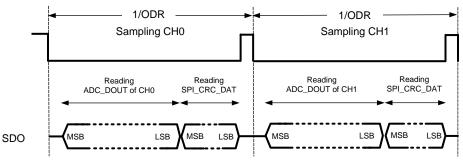

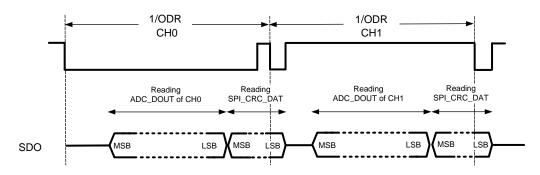

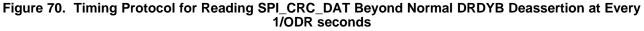

# 8.10 SDO and DRDYB Timing Requirements

|                    |                                         |                              | MIN | NOM | MAX | UNIT |

|--------------------|-----------------------------------------|------------------------------|-----|-----|-----|------|

| t <sub>DOE</sub>   | SDO Enable time from the                | falling edge of the 8th SCLK |     |     | 35  | ns   |

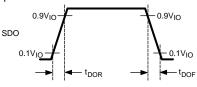

| t <sub>DOR</sub>   | SDO Rise time                           | See <sup>(1)</sup>           |     | 7   |     | ns   |

| t <sub>DOF</sub>   | SDO Fall time                           | See <sup>(1)</sup>           |     | 7   |     | ns   |

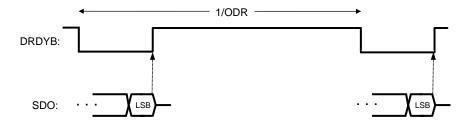

|                    | Data Ready Bar pulse at                 | ODR ≤ 13.42 SPS              |     | 64  |     |      |

| t <sub>DRDYB</sub> | every<br>1/ODR second, see<br>Figure 62 | 13.42 < ODR ≤ 214.65 SPS     |     | 4   |     | μs   |

Unless otherwise noted, specified limits apply for VA = VIO = 3.0 V.

(1) This parameter is specified by design and/or characterization and is not tested in production

Figure 10. SDO and SCLK Enable Timing

Figure 11. SDO Rise and Fall Timing

SNAS510S - JANUARY 2011 - REVISED JANUARY 2016

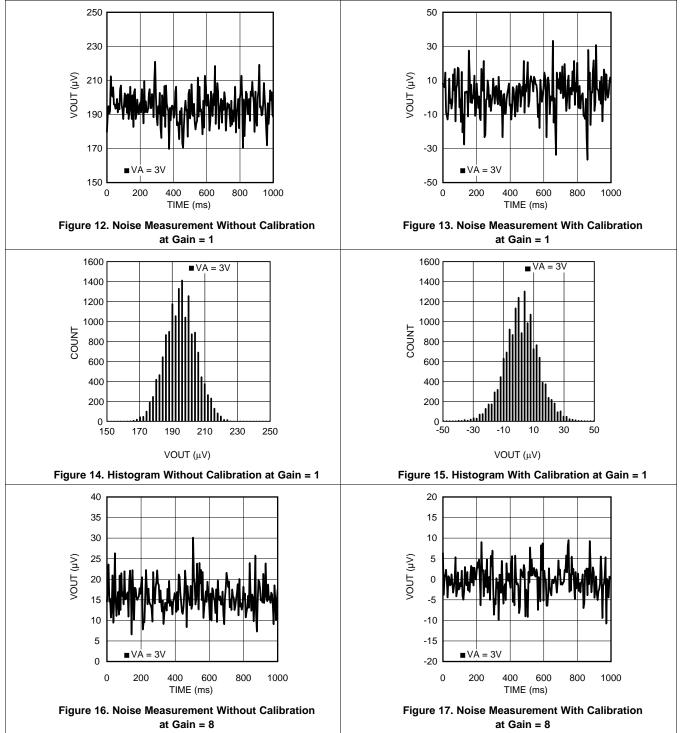

# 8.11 Typical Characteristics

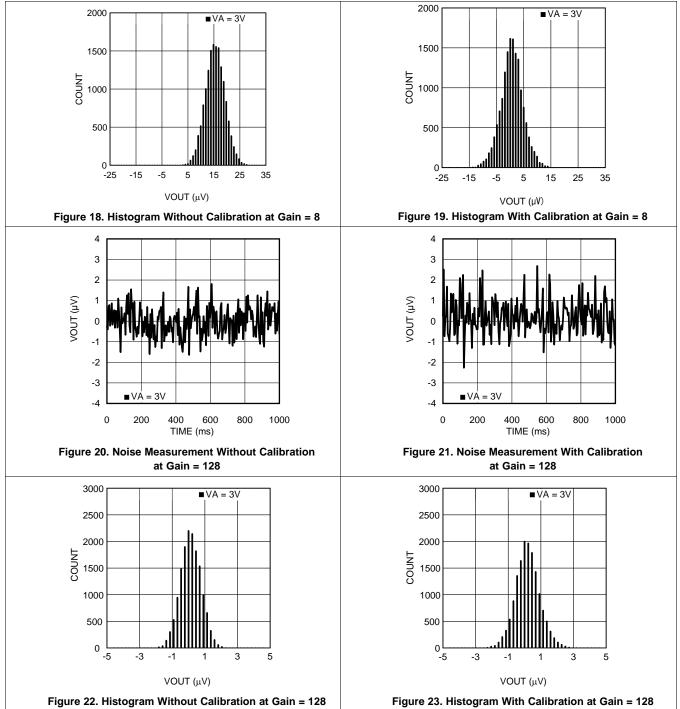

### **Typical Characteristics (continued)**

SNAS510S – JANUARY 2011 – REVISED JANUARY 2016

ISTRUMENTS

EXAS

# **Typical Characteristics (continued)**

### **Typical Characteristics (continued)**

SNAS510S – JANUARY 2011 – REVISED JANUARY 2016

EXAS

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

TEXAS INSTRUMENTS

www.ti.com

# 9 Detailed Description

### 9.1 Overview

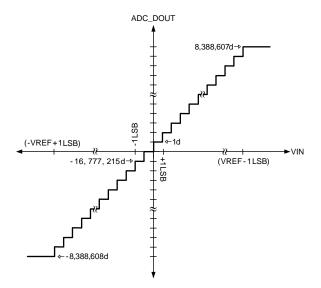

The LMP90xxx is a low-power 24-Bit  $\Sigma\Delta$  ADC with 4 fully differential / 7 single-ended analog channels for the LMP90100/LMP90099 and 2 full differential / 4 single-ended for the LMP90098/LMP90097. Its serial data output is two's complement format. The output data rate (ODR) ranges from 1.6775 SPS to 214.65 SPS.

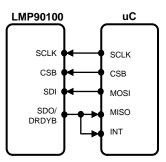

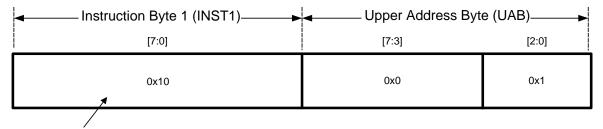

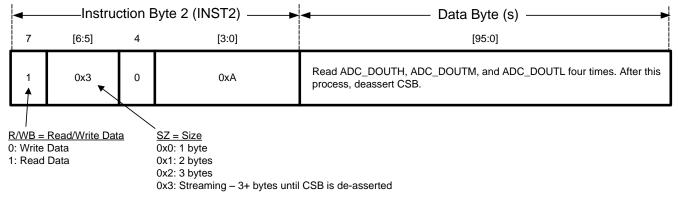

The serial communication for LMP90xxx is SPI, a synchronous serial interface that operates using 4 pins: chip select bar (CSB), serial clock (SCLK), serial data in (SDI), and serial data out / data ready bar (SDO/DRYDYB).

True continuous built-in offset and gain background calibration is also available to improve measurement accuracy. Unlike other ADCs, the LMP90xxx's background calibration can run without heavily impacting the input signal. This unique technique allows for positive as well as negative gain calibration and is available at all gain settings.

The registers can be found in *Programming*, and a detailed description of the LMP90xxx are provided in the following sections.

# 9.2 Functional Block Diagram

### 9.3 Feature Description

#### 9.3.1 True Continuous Background Calibration

The LMP90100/LMP90099/LMP90098/LMP90097 feature a 24 bit  $\Sigma\Delta$  core with continuous background calibration to compensate for gain and offset errors in the ADC, virtually eliminating any drift with time and temperature. The calibration is performed in the background without user or ADC input interruption, making it unique in the industry and eliminating down time associated with field calibration required with other solutions. Having this continuous calibration improves performance over the entire life span of the end product.

#### Feature Description (continued)

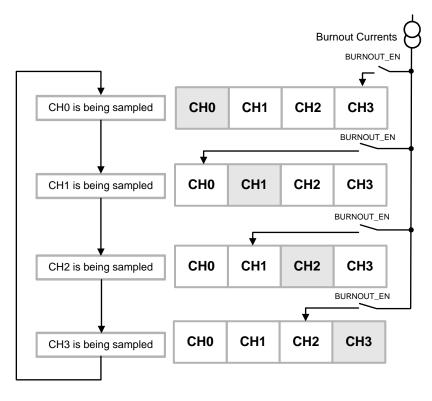

#### 9.3.2 Continuous Background Sensor Diagnostics

Sensor diagnostics are also performed in the background, without interfering with signal path performance, allowing the detection of sensor shorts, opens, and out-of-range signals, which vastly improves system reliability. In addition, the fully flexible input multiplexer described below allows any input pin to be connected to any ADC input channel providing additional sensor path diagnostic capability.

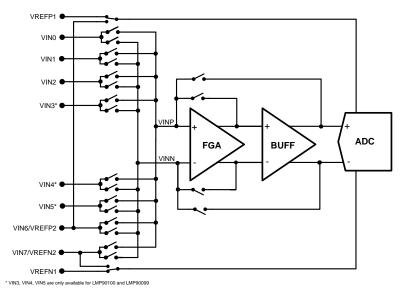

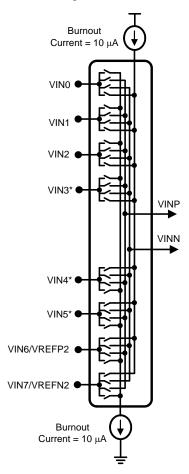

#### 9.3.3 Flexible Input MUX Channels

The flexible input MUX allows interfacing to a wide range of sensors such as thermocouples, RTDs, thermistors, and bridge sensors. The LMP90100/LMP90099's multiplexer supports 4 differential channels while the LMP90098/LMP90097 supports 2. Each effective input voltage that is digitized is VIN = VINx – VINy, where x and y are any input. In addition, the input multiplexer of the LMP90100/LMP90099 also supports 7 single-ended channels (LMP90098/LMP90097 supports 4), where the common ground is any one of the inputs.

#### 9.3.4 Programmable Gain Amplifiers (FGA and PGA)

The LMP90100/LMP90099/LMP90098/LMP90097 contain an internal 16x fixed gain amplifier (FGA) and a 1x, 2x, 4x, or 8x programmable gain amplifier (PGA). This allows accurate gain settings of 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x through configuration of internal registers. Having an internal amplifier eliminates the need for external amplifiers that are costly, space consuming, and difficult to calibrate.

#### 9.3.5 Excitation Current Sources (IB1 and IB2) - LMP90100/LMP90098

Two matched internal excitation currents, IB1 and IB2, can be used for sourcing currents to a variety of sensors. The current range is from 100  $\mu$ A to 1000  $\mu$ A in steps of 100  $\mu$ A.

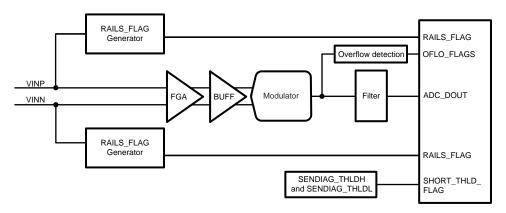

#### 9.3.6 Signal Path

#### 9.3.6.1 Reference Input (VREF)

The differential reference voltage VREF (VREFP – VREFN) sets the range for VIN.

The muxed VREF allows the user to choose between VREF1 or VREF2 for each channel. This selection can be made by programming the VREF\_SEL bit in the CHx\_INPUTCN registers (CHx\_INPUTCN: VREF\_SEL). The default mode is VREF1. If VREF2 is used, then VIN6 and VIN7 cannot be used as inputs because they share the same pin.

Refer to VREF for VREF applications information.

#### 9.3.6.2 Flexible Input MUX (VIN)

The LMP90xxx provides a flexible input MUX as shown in Figure 43. The input that is digitized is VIN = VINP - VINN; where VINP and VINN can be any available input.

The digitized input is also known as a channel, where CH = VIN = VINP - VINN. Thus, there are a maximum of 4 differential channels: CH0, CH1, CH2, and CH3 for the LMP90100/LMP90099. The LMP90098/LMP90097 has a maximum of 2 differential channels: CH0 and CH1 because it does not have access to the VIN3, VIN4, and VIN5 pins.

The LMP90xxx can also be configured single-endedly, where the common ground is any one of the inputs. There are a maximum of 7 single-ended channels: CH0, CH1, CH2, CH3, CH4, CH5, and CH6 for the LMP90100/LMP90099 and 4: CH0, CH1, CH2, CH3 for the LMP90098/LMP90097.

The input MUX can be programmed in the CHx\_INPUTCN registers. For example on the LMP90100, to program CH0 = VIN = VIN4 – VIN1, go to the CH0\_INPUTCN register and set:

1. VINP = 0x4

2. VINN = 0x1

## Feature Description (continued)

Figure 43. Simplified VIN Circuitry

### 9.3.6.3 Selectable Gains (FGA and PGA)

The LMP90xxx provides two types of gain amplifiers: a fixed gain amplifier (FGA) and a programmable gain amplifier (PGA). FGA has a fixed gain of 16x or it can be bypassed, while the PGA has programmable gain settings of 1x, 2x, 4x, or 8x.

Total gain is defined as FGA x PGA. Thus, LMP90xxx provides gain settings of 1x, 2x, 4x, 8x, 16x, 32x, 64x, or 128x with true continuous background calibration.

The gain is channel specific, which means that one channel can have one gain, while another channel can have the same or a different gain.

The gain can be selected by programming the CHx\_CONFIG: GAIN\_SEL bits.

#### 9.3.6.4 Buffer (BUFF)

There is an internal unity gain buffer that can be included or excluded from the signal path. Including the buffer provides a high input impedance but increases the power consumption.

When gain  $\geq$  16, the buffer is automatically included in the signal path. When gain < 16, including or excluding the buffer from the signal path can be done by programming the CHX\_CONFIG: BUF\_EN bit.

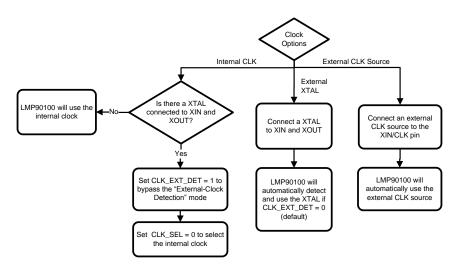

#### 9.3.6.5 Internal/External CLK Selection

LMP90xxx allows two clock options: internal CLK or external CLK (crystal (XTAL) or clock source).

There is an "External Clock Detection" mode, which detects the external XTAL if it is connected to XOUT and XIN. When operating in this mode, the LMP90xxx shuts off the internal clock to reduce power consumption. Below is a flow chart to help set the appropriate clock registers.

# Feature Description (continued)

Figure 44. CLK Register Settings

The recommended value for the external CLK is discussed in the next sections.

### 9.3.6.6 Programmable ODRs

If using the internal CLK or external CLK of 3.5717 MHz, then the output date rates (ODR) can be selected (using the ODR\_SEL bit) as:

- 1. 13.42/8 = 1.6775 SPS

- 2. 13.42/4 = 3.355 SPS

- 3. 13.42/2 = 6.71SPS

- 4. 13.42 SPS

- 5. 214.65/8 = 26.83125 SPS

- 6. 214.65/4 = 53.6625 SPS

- 7. 214.65/2 = 107.325 SPS

- 8. 214.65 SPS (default)

If the internal CLK is not being used and the external CLK is not 3.5717 MHz, then the ODR will be different. If this is the case, use the equation below to calculate the new ODR values.

| ODR_Base1 = (CLK <sub>EXT</sub> ) / (266,240)<br>ODR_Base2 = (CLK <sub>EXT</sub> ) / (16,640)<br>ODR1 = (ODR_Base1) / n | (1)<br>(2) |

|-------------------------------------------------------------------------------------------------------------------------|------------|

| where<br>• n = 1,2,4,8<br>ODR2 = (ODR_Base2) / n                                                                        | (3)        |

| where<br>• n = 1,2,4,8                                                                                                  | (4)        |

For example, a 3.6864 MHz XTAL or external clock has the following ODR values:

| ODR_Base1 = (3.6864 MHz) / (266,240) = 13.85 SPS     | (5) |

|------------------------------------------------------|-----|

| ODR_Base2 = (3.6864 MHz) / (16,640) = 221.54 SPS     | (6) |

| ODR1 = (13.85 SPS) / n = 13.85, 6.92, 3.46, 1.73 SPS | (7) |

|                                                      |     |

SNAS510S – JANUARY 2011 – REVISED JANUARY 2016

### **Feature Description (continued)**

ODR2 = (221.54 SPS) / n = 221.54, 110.77, 55.38, 27.69 SPS

The ODR is channel specific, which means that one channel can have one ODR, while another channel can have the same or a different ODR.

Note that these ODRs are meant for a single channel conversion; the ODR needs to be divided by n for n channels scanning. For example, if the ADC were running at 214.65 SPS and four channels are being scanned, then the ODR per channel would be 214.65/4 = 53.6625 SPS.

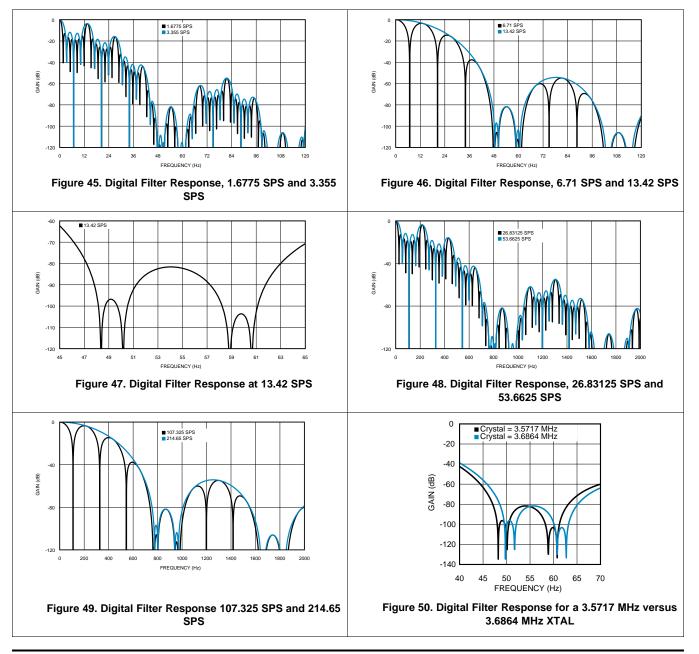

### 9.3.6.7 Digital Filter

The LMP90xxx has a fourth order rotated sinc filter that is used to configure various ODRs and to reject power supply frequencies of 50Hz and 60Hz. The 50/60 Hz rejection is only effective when the device is operating at ODR  $\leq$  13.42 SPS. If the internal CLK or the external CLK of 3.5717 MHz is used, then the LMP90xxx will have the frequency response shown in Figure 45 to Figure 49.

Copyright © 2011–2016, Texas Instruments Incorporated

Product Folder Links: LMP90100 LMP90099 LMP90098 LMP90097

www.ti.com

ISTRUMENTS

EXAS

(9)

www.ti.com

#### Feature Description (continued)

If the internal CLK is not being used and the external CLK is not 3.5717 MHz, then the filter response would be the same as the response shown in Figure 49, but the frequency will change according to the equation:

f<sub>NEW</sub> = [(CLK<sub>EXT</sub>) / 256 ] x (f<sub>OLD</sub> / 13.952k)

Using Equation 9, an example of the filter response for a 3.5717 MHz XTAL versus a 3.6864 MHz XTAL can be seen in Figure 50.

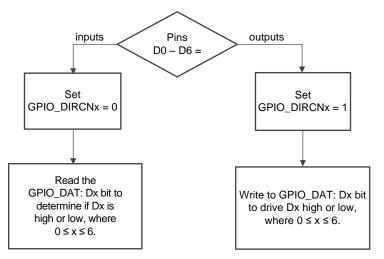

### 9.3.6.8 GPIO (D0–D6)

Pins D0-D6 are general-purpose input/output (GPIO) pins that can be used to control external LEDs or switches. Only a high or low value can be sourced to or read from each pin.

Figure 51 shows a flow chart how these GPIOs can be programmed.

Figure 51. GPIO Register Settings

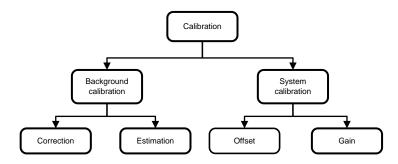

#### 9.3.7 Calibration

As seen in Figure 52, there are two types of calibration: background calibration and system calibration. These calibrations are further described in the next sections.

Figure 52. Types of Calibration

#### 9.3.7.1 Background Calibration

Background calibration is the process of continuously determining and applying the offset and gain calibration coefficients to the output codes to minimize the LMP90xxx's offset and gain errors. Background calibration is a feature built into the LMP90xxx and is automatically done by the hardware without interrupting the input signal.

Four differential channels, CH0-CH3, each with its own gain and ODRs, can be calibrated to improve the accuracy.

Copyright © 2011–2016, Texas Instruments Incorporated

SNAS510S – JANUARY 2011 – REVISED JANUARY 2016

**NSTRUMENTS**

Texas

### Feature Description (continued)

### 9.3.7.1.1 Types of Background Calibration

Figure 52 also shows that there are two types of background calibration:

- 1. Type 1: Correction the process of continuously determining and applying the offset and gain calibration coefficients to the output codes to minimize the LMP90xxx's offset and gain errors.

- This method keeps track of changes in the LMP90xxx's gain and offset errors due to changes in the

operating condition such as voltage, temperature, or time.

- 2. Type 2: Estimation the process of determining and continuously applying the last known offset and gain calibration coefficients to the output codes to minimize the LMP90xxx's offset and gain errors.

- The last known offset or gain calibration coefficients can come from two sources. The first source is the default coefficient which is pre-determined and burnt in the device's non-volatile memory. The second source is from a previous calibration run of Type 1: Correction.

The benefits of using type 2 calibration are a higher throughput, lower power consumption, and slightly better noise. The exact savings would depend on the number of channels being scanned, and the ODR and gain of each channel.

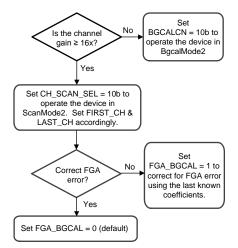

#### 9.3.7.1.2 Using Background Calibration

There are four modes of background calibration, which can be programmed using the BGCALCN bits. They are as follows:

- 1. BgcalMode0: Background Calibration OFF

- 2. BgcalMode1: Offset Correction / Gain Estimation

- 3. BgcalMode2: Offset Correction / Gain Correction

- Follow Figure 53 to set other appropriate registers when using this mode.

- 4. BgcalMode3: Offset Estimation / Gain Estimation

Figure 53. BgcalMode2 Register Settings

If operating in BgcalMode2, four channels (with the same ODR) are being converted, and  $FGA_BGCAL = 0$  (default), then the ODR is reduced by:

- 1. 0.19% of 1.6775 SPS

- 2. 0.39% of 3.355 SPS

- 3. 0.78% of 6.71 SPS

- 4. 1.54% of 13.42 SPS

- 5. 3.03% of 26.83125 SPS

- 6. 5.88% of 53.6625 SPS

### Feature Description (continued)

- 7. 11.11% of 107.325 SPS

- 8. 20% of 214.65 SPS

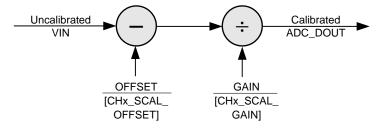

# 9.3.7.2 System Calibration

The LMP90xxx provides some unique features to support easy system offset and system gain calibrations.

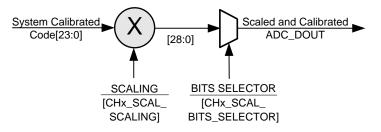

The System Calibration Offset Registers (CHx\_SCAL\_OFFSET) hold the System Calibration Offset Coefficients in 24-bit, two's complement binary format. The System Calibration Gain Registers (CHx\_SCAL\_GAIN) hold the System Calibration Gain Coefficient in 24-bit, 1.23, unsigned, fixed-point binary format. For each channel, the System Calibration Offset coefficient is subtracted from the conversion result prior to the division by the System Calibration Gain Coefficient.

A data-flow diagram of these coefficients can be seen in Figure 54.

Figure 54. System Calibration Data-Flow Diagram

There are four distinct sets of System Calibration Offset and System Calibration Gain Registers for use with CH0-CH3. CH4-CH6 reuse the registers of CH0-CH2, respectively.

The LMP90xxx provides two system calibration modes that automatically fill the Offset and Gain coefficients for each channel. These modes are the System Calibration Offset Coefficient Determination mode and the System Calibration Gain Coefficient Determination mode. The System Calibration Offset Coefficient Determination mode must be entered prior to the System Calibration Gain Coefficient Determination mode.

The system zero-scale condition is a system input condition (sensor loading) for which zero (0x00\_0000) systemcalibrated output code is desired. It may not, however, cause a zero input voltage at the input of the ADC.

The system reference-scale condition is usually the system full-scale condition in which the system's input (or sensor's loading) would be full-scale and the desired system-calibrated output code would be 0x80\_0000 (unsigned 24-bit binary). However, system full-scale condition need not cause full-scale input voltage at the input of the ADC.

The system reference-scale condition is not restricted to just the system full-scale condition. In fact, it can be any arbitrary fraction of full-scale (up to 1.25 times) and the desired system-calibrated output code can be any appropriate value (up to 0xA00000). The CHx\_SCAL\_GAIN register must be written with the desired system-calibrated output code (default:0x800000) before entering the System Calibration Gain Coefficient Determination mode. This helps in in-place system calibration.

Below are the detailed procedures for using the System Calibration Offset Coefficient Determination and System Calibration Gain Coefficient Determination modes.

### 9.3.7.2.1 System Calibration Offset Coefficient Determination Mode

- 1. Apply system zero-scale condition to the channel (CH0/CH1/CH2/CH3).

- 2. Enter the System Calibration Offset Coefficient Determination mode by programming 0x1 in the SCALCN register.

- 3. LMP90xxx starts a fresh conversion at the selected output data rate for the selected channel. At the end of the conversion, the CHx\_SCAL\_OFFSET register is filled-in with the System Calibration Offset coefficient.

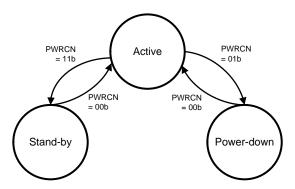

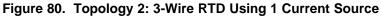

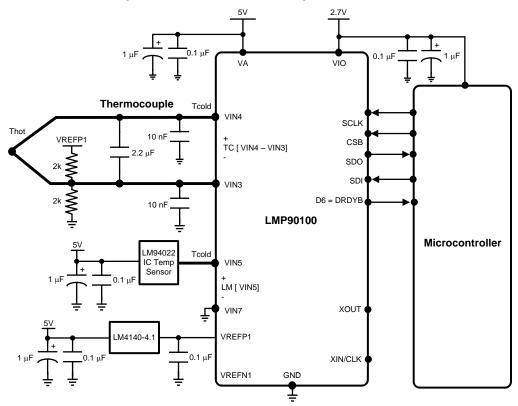

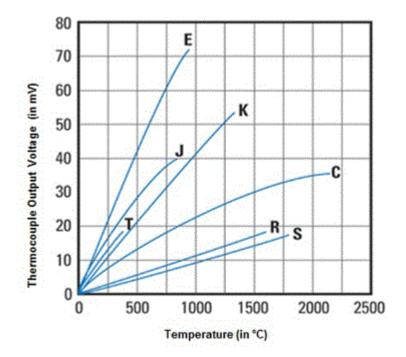

- 4. The System Calibration Offset Coefficient Determination mode is automatically exited.