# 10-Bit 18 MSPS Monolithic A/D Converter

**AD773**

#### **FEATURES**

Monolithic 10-Bit 18 MSPS A/D Converter

Low Power Dissipation: 1.2 W

Signal-to-Noise Plus Distortion Ratio

f<sub>IN</sub> = 1 MHz: 56 dB f<sub>IN</sub> = 8 MHz: 53 dB

Guaranteed No Missing Codes On-Chip Track-and-Hold Amplifier 100 MHz Full Power Bandwidth

High Impedance Reference Input

**Out of Range Output**

Twos Complement and Binary Output Data

Available in Commelcia and Military Temperature

Ranges

# PRODUCT DESCRIPTION

The AD773 is a monolithic 10-bit, 18 MSPS analog-to-digital converter incorporating an on-board, high performance track-and-hold amplifier (THA). The AD773 converts video bandwidth signals without the use of an external THA. The AD773 implements a multistage differential pipelined architecture with output error correction logic. The AD773 offers accurate performance and guarantees no missing codes over the full operating temperature range.

Output data is presented in binary and twos complement format. An out of range (OTR) signal indicates the analog input voltage is beyond the specified input range. OTR can be decoded with the MSB/MSB pins to signal an underflow or overflow condition. The high impedance reference input allows multiple AD773s to be driven in parallel from a single reference.

The combined dc precision and dynamic performance of the AD773 is useful in a variety of applications. Typical applications include: video enhancement, HDTV, ghost cancellation, ultrasound imaging, radar and high speed data acquisition.

The AD773 was designed using Analog Devices' ABCMOS-1 process which utilizes high speed bipolar and 2-micron CMOS transistors on a single chip. High speed, precision analog circuits are now combined with high density logic circuits. Laser trimmed thin film resistors are used to optimize accuracy and temperature stability.

The AD773 is packaged in a 28-pin ceramic DIP and is available in commercial (0°C to +70°C) and military (-55°C to +125°C) grades.

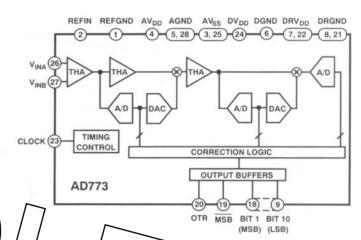

## FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHT

On-board THA

The high impedance differential input THA eliminates the need for external buffering or sample and hold amplifiers. The THA offers the choice of differential or single ended inputs. Input current is typically 5 µA.

- High Impedance Reference Input

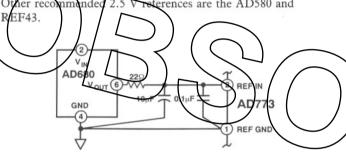

The high impedance reference input (200 kg) allows direct connection with standard +2.5 V references, such as the AD680, AD580 and REF43.

- Output Data Flexibility

Output data is available in bipolar offset and bipolar twos

complement binary format.

- Out of Range (OTR)

The OTR output bit indicates when the input signal is beyond the AD773's input range.

# REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

# AD773—SPECIFICATIONS

DC SPECIFICATIONS  $(T_{MIN}$  to  $T_{MAX}$  with  $AV_{DD}=+5$  V  $\pm$  5%,  $AV_{SS}=-5$  V  $\pm$  5%,  $DV_{DD}=+5$  V  $\pm$  5%,  $V_{REF}=+2.500$  V unless otherwise indicated)

|                                                        | AD773J   |            |       | AD773K |                                          |         |       |  |

|--------------------------------------------------------|----------|------------|-------|--------|------------------------------------------|---------|-------|--|

| Parameter                                              | Min      | Тур        | Max   | Min    | Тур                                      | Max     | Units |  |

| RESOLUTION                                             | 10       |            |       | 10     |                                          |         | Bits  |  |

| DC ACCURACY (+25°C)                                    |          |            |       |        |                                          |         |       |  |

| Integral Nonlinearity                                  |          |            |       |        |                                          |         | LSB   |  |

| $T_{MIN}$ to $T_{MAX}$                                 |          | $\pm 0.75$ |       |        | $\pm 0.75$                               | $\pm 2$ | LSB   |  |

| Differential Linearity Error                           |          |            |       |        |                                          |         | LSB   |  |

| TMIN to TMAX                                           |          | ±0.75      |       |        | ±0.75                                    | ±1      | LSB   |  |

| Offset                                                 |          | 0.5        |       |        | 0.5                                      | 3.5     | % FS  |  |

| Gain Error                                             |          | 0.5        |       |        | 0.5                                      | 2.0     | % FS  |  |

| No Missing Godes                                       | <b>\</b> |            |       |        | GUARANTEI                                | מנ      |       |  |

| ANALOG INPUT                                           |          |            |       |        |                                          |         |       |  |

| Input Range                                            |          | 1          |       |        | 1                                        | 20      | V p-I |  |

| Input Current                                          | \        | 7 )        | / 2/0 | _      | 5                                        | 20      | μΑ    |  |

| Input Capacitance                                      |          |            | 10    |        |                                          | 10      | pF    |  |

| REFERENCE INPUT                                        |          | ///        | /     |        | $\longrightarrow$                        | _       |       |  |

| Reference Input Resistance                             | 30       | 200        | /     | 50     | 200                                      |         | kΩ    |  |

| Reference Input                                        |          | 2.5        |       | / /    | 2.5                                      | $\sim$  | Volts |  |

| LOGIC INPUT                                            |          |            |       |        | 7 /                                      | T = T   |       |  |

| High Level Input Voltage                               | +3.5     |            |       | +3.5   | _ /                                      | / /     | V_    |  |

| Low Level Input Voltage                                |          |            | +1.0  |        | $\supset$                                | +1.0    | V     |  |

| High Level Input Current $(V_{IN} = DV_{DD})$          | -10      |            | +10   | -10    | $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ | +10     | μΑ    |  |

| Low Level Input Current $(V_{IN} = 0 V)$               | -10      |            | +10   | -10    |                                          | +10     | μA    |  |

| Input Capacitance                                      |          | 10         |       |        | 10                                       |         | pF    |  |

| LOGIC OUTPUTS                                          |          |            |       |        |                                          |         |       |  |

| High Level Output Voltage $(I_{OH} = 0.5 \text{ mA})$  | +2.4     |            |       | +2.4   |                                          |         | V     |  |

| Low Level Output Voltage ( $I_{OL} = 1.6 \text{ mA}$ ) |          |            | +0.4  |        |                                          | +0.4    | V     |  |

| POWER SUPPLIES                                         |          |            | •     |        |                                          |         |       |  |

| Operating Voltages                                     |          |            |       |        |                                          |         |       |  |

| $AV_{DD}$                                              | +4.75    |            | +5.25 | +4.75  |                                          | +5.25   | Volts |  |

| $AV_{SS}$                                              | -5.25    |            | -4.75 | -5.25  |                                          | -4.75   | Volts |  |

| $DV_{DD}$ , $DRV_{DD}$                                 | +4.75    |            | +5.25 | +4.75  |                                          | +5.25   | Volts |  |

| Operating Current                                      |          |            |       |        |                                          |         |       |  |

| $IAV_{DD}$                                             |          | 85         | 110   |        | 85                                       | 110     | mA    |  |

| IAV <sub>SS</sub>                                      |          | -140       | -205  |        | -140                                     | -205    | mA    |  |

| $IDV_{DD}$                                             |          | 15         | 25    |        | 15                                       | 25      | mA    |  |

| IDRV <sub>DD</sub> <sup>1</sup>                        |          | 10         | 15    |        | 10                                       | 15      | mA    |  |

| POWER CONSUMPTION <sup>2</sup>                         |          | 1.2        | 1.5   |        | 1.2                                      | 1.5     | W     |  |

| POWER SUPPLY REJECTION                                 |          | 6          | 16    |        | 6                                        | 16      | mV/V  |  |

| TEMPERATURE RANGE                                      |          |            |       |        |                                          |         |       |  |

| Specified (J/K)                                        | 0        |            | +70   | 0      |                                          | +70     | °C    |  |

NOTES

Specifications subject to change without notice. See Definition of Specifications for additional information.

$<sup>{}^{1}</sup>C_{L} = 15 \text{ pF typical.}$  ${}^{2}100\% \text{ production tested.}$

# AC SPECIFICATIONS ( $T_{MIN}$ to $T_{MAX}$ with $AV_{DD}=+5$ V $\pm$ 5%, $AV_{SS}=-5$ V $\pm$ 5%, $DV_{DD}=+5$ V $\pm$ 5%, $DRV_{DD}=+5$ V $\pm$ 5%, $V_{REF}=+2.500$ V unless otherwise indicated, $f_{SAMPLE}=18$ MSPS, $f_{IN}$ amplitude =-0.5 dB)

|                                               |                | AD773J            |                    |     | AD773K              |            |       |

|-----------------------------------------------|----------------|-------------------|--------------------|-----|---------------------|------------|-------|

| Parameter                                     | Min            | Typ               | Max                | Min | Typ                 | Max        | Units |

| DYNAMIC PERFORMANCE <sup>1</sup>              |                |                   |                    |     |                     |            |       |

| Signal-to-Noise plus Distortion               |                |                   |                    |     |                     | ,          |       |

| (S/N+D) Ratio                                 |                |                   |                    |     |                     | ,          |       |

| $f_{IN} = 1 MHz$                              | 52             | 56                |                    | 54  | 56                  | ,          | dB    |

| f <sub>IN</sub> = 8.1 MHz                     | 45             | 53                |                    | 47  | 53                  |            | dB    |

| f <sub>IN</sub> 9 MHz                         | ******         | 53                |                    |     | 53                  | 1          | dB    |

| Effective Number of Bits (ENOB)               |                |                   |                    |     |                     | ,          |       |

| $f_{IN} = 1 \text{ MHz}$                      | +              | 9.0               |                    |     | 9.0                 | ,          | Bits  |

| $f_{IN} = 8.1 \text{ MHz}$                    | $\leftarrow$   | 8.5               |                    |     | 8.5                 | ,          | Bits  |

| free 9 MHz                                    | (1)            | 8.5               |                    |     | 8.5                 | ,          | Bits  |

| Total Harmoric Distortion (THD)               | . \_ /         | $\langle \rangle$ | · ~                |     |                     | ,          |       |

| $f_{IN} = 1 \text{ MHz}$                      | $\times$ \ \ \ | -66               | \ <del>/</del> 57/ |     | -66                 | -59        | dB    |

| $f_{IN} = 8.1 \text{ MHz}$                    | .   ) ] [      | -58               | -46                |     | -58                 | -48        | dB    |

| $f_{IN} = 9 \text{ MHz}$                      | +//            | -56               | ]                  | / ~ | -76/                | <b>~</b> . | dB    |

| Spurious Free Dynamic Range <sup>2</sup>      | + \            | 67                | ′ / /              |     | 67                  |            | dB    |

| Full Power Bandwidth                          | \              | 100               | / /                | /   | 100                 | 1 / /      | MH    |

| Intermodulation Distortion (IMD) <sup>3</sup> |                | $\smile$          | /                  |     | $\longrightarrow$ 1 | 1 1        |       |

| Second Order Products                         |                | -69               |                    | 7/  | -69                 | - / - / '  | dB    |

| Third Order Products                          |                | -61               | 7                  | 1   | -61                 | 1 1        | dB    |

| Differential Phase                            |                | 0.2               |                    | _   | 0.2                 | / / /      | Deg   |

| Differential Gain                             |                | 0.4               |                    |     | 0.4                 | J   L'     | %     |

| Transient Response                            |                | 25                |                    |     | 25                  |            | ns    |

| Overvoltage Recovery Time                     |                | 25                |                    |     | 25                  | 7          | ns    |

#### NOTES

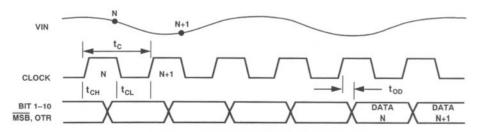

# TIMING SPECIFICATIONS (for all grades $T_{MIN}$ to $T_{MAX}$ with $AV_{DD}=+5$ V $\pm$ 5%, $AV_{SS}=-5$ V $\pm$ 5%, $DV_{DD}=+5$ V $\pm$ 5%, $DRV_{DD}=+5$ V $\pm$ 5%, $V_{REF}=+2.500$ V unless otherwise indicated, $f_{SAMPLE}=18$ MSPS)

|                          | Symbol           | Min | Тур | Max | Units       |

|--------------------------|------------------|-----|-----|-----|-------------|

| Conversion Rate          |                  |     |     | 18  | MSPS        |

| Clock Period             | t <sub>CLK</sub> | 55  |     |     | ns          |

| Clock High               | t <sub>CH</sub>  | 27  |     |     | ns          |

| Clock Low                | t <sub>CL</sub>  | 27  |     |     | ns          |

| Output Delay             | t <sub>op</sub>  |     | 20  |     | ns          |

| Aperture Delay           |                  |     | 7   |     | ns          |

| Aperture Jitter          |                  |     | 8   |     | ps          |

| Pipeline Delay (Latency) |                  |     |     | 4   | Clock Cycle |

Figure 1. AD773 Timing Diagram

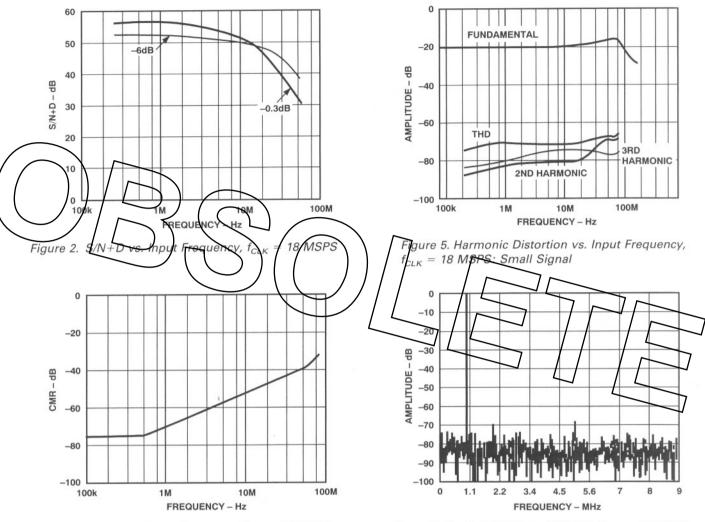

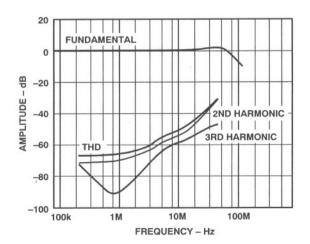

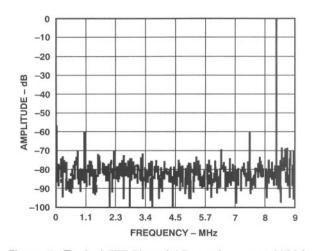

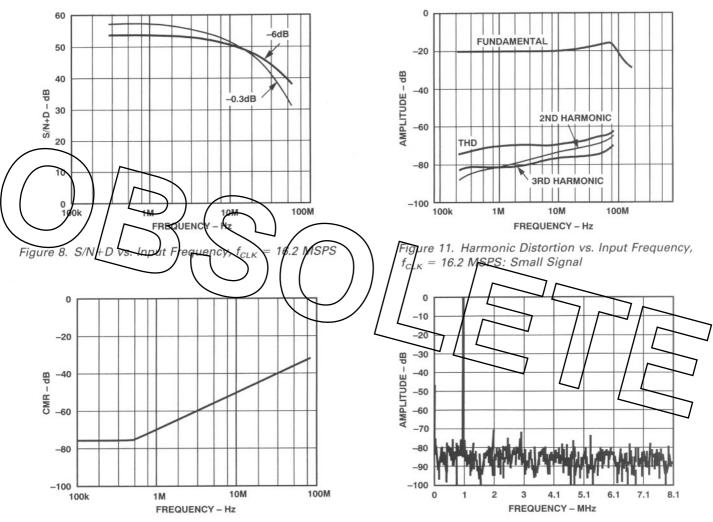

<sup>&</sup>lt;sup>1</sup>For typical dynamic performance curves at f<sub>SAMPLE</sub> = 16.2 MSPS and 18 MSPS, see Figures 2 through 13.

$<sup>^{2}</sup>f_{IN} = 1 MHz.$

$<sup>^{3}</sup>$ fa = 1.0 MHz, fb = 1.05 MHz.

Specifications subject to change without notice.

### CAUTION .

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are inserted.

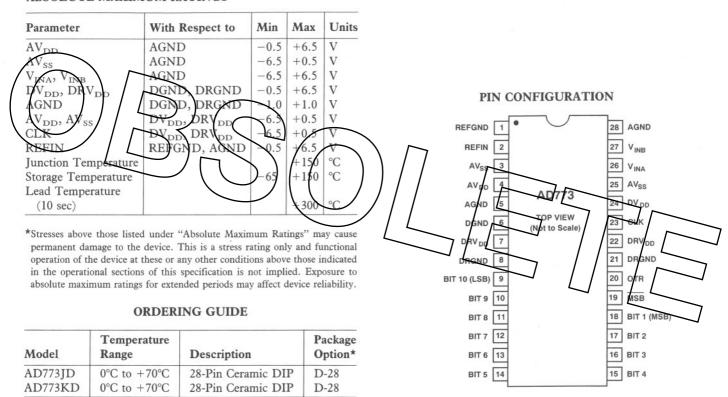

### ABSOLUTE MAXIMUM RATINGS\*

<sup>\*</sup>D = Ceramic DIP.

# PIN DESCRIPTION

| Symbol           | Pin No. | Type | Name and Function                                                                                 |

|------------------|---------|------|---------------------------------------------------------------------------------------------------|

| AGND             | 5, 28   | P    | Analog Ground.                                                                                    |

| $AV_{DD}$        | 4       | P    | +5 V Analog Supply.                                                                               |

| $AV_{SS}$        | 3, 25   | P    | -5 V Analog Supply.                                                                               |

| BIT 1 (MSB)      | 18      | DO   | Most Significant Bit.                                                                             |

| BIT 2-BIT 9      | 17-10   | DO   | Data Bit 2 through Data Bit 9.                                                                    |

| BIT 10 (LSB)     | 9       | DO   | Least Significant Bit.                                                                            |

| CLK              | 23      | DI   | Clock Input. The AD773 will initiate a conversion on the falling edge of the clock input. See the |

|                  |         |      | Timing Diagram for details.                                                                       |

| $DV_{DD}$        | 24      | P    | +5 V Digital Supply.                                                                              |

| $DRV_{DD}$       | 7, 22   | P    | +5 V Digital Supply for the output drivers.                                                       |

| DGND             | 6       | P    | Digital Ground.                                                                                   |

| DRGND            | 8, 21   | P    | Digital Ground for the output drivers.                                                            |

| MSB              | 19      | DO   | Inverted Most Significant Bit. Provides twos complement output data format.                       |

| OTR              | 20      | DO   | Out of Range is Active HIGH on the leading edge of Code 0 or the trailing edge of Code 1023.      |

|                  |         |      | See Output Data Format Table II.                                                                  |

| REF GND          | 1       | AI   | REF GND is connected to the ground of the external reference.                                     |

| REF IN           | 2       | AI   | REF IN is the external 2.5 V reference input, taken with respect to REF GND.                      |

| $V_{INA}$        | 26      | AI   | (+) Analog input signal to the differential input THA.                                            |

| V <sub>INB</sub> | 27      | AI   | (-) Analog input signal to the differential input THA.                                            |

# **Definitions of Specifications—AD773**

# INTEGRAL NONLINEARITY (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "zero" through "full scale." The point used as "zero" occurs 1/2 LSB before the first code transition. "Full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the center of each particular code to the true straight line.

# DIFFERENTIAL LINEARITY ERROR (DNL, NO MISSING CODES)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value.

### OFFSET

The first transition should occur at a level 1/2 LSB above "zero." Offset is defined as the deviation of the actual first code transition from that point

#### GAIN ERROR

The last code transition should occur for an analog value 1 1/2 LSB below the nominal full scale. The gain error is the deviation of the actual level at the last transition from the ideal level

# POWER SUPPLY REJECTION

One of the effects of power supply variation on the performance of the device will be a change in gain error. The specification shows the maximum gain error deviation as the supplies are varied from their nominal values to their specified limits.

# SIGNAL-TO-NOISE PLUS DISTORTION (S/N+D) RATIO

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components including harmonics but excluding dc. The value for S/N+D is expressed in decibels.

#### EFFECTIVE NUMBER OF BITS (ENOB)

ENOB is calculated from the following expression:

S/N+D = 6.02N + 1.76, where N is equal to the effective number of bits.

## TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

## SPURIOUS FREE DYNAMIC RANGE

The peak spurious or peak harmonic component is the largest spectral component excluding the input signal and dc. This value is expressed in decibels relative to the rms value of a full-scale input signal.

# INTERMODULATION DISTORTION (IMD)

With inputs consisting of sine waves at two frequencies, fa and fb, any device with nonlinearities will create distortion products, of order (m+n), at sum and difference frequencies of  $mfa\pm nfb$ , where  $m,\,n=0,\,1,\,2,\,3\,\ldots$ . Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms are (fa+fb) and (fa-fb) and the third order terms are  $(2fa+fb),\,(2fa-fb),\,(fa+2fb)$  and (fa-2fb). The IMD products are expressed as the decibel ratio of the rms sum of the measured input signals to the rms sum of the distortion terms. The two signals are of equal amplitude and the peak value of their sums is -0.5 dB from full scale. The IMD products are normalized to a 0 dB input signal.

### DIFFERENTIAL GAIN

The percentage difference between the output amplitudes of a small high frequency sine wave at two stated levels of a low frequency signal on which it is superimposed.

# DIFFERENTIAL PHASE

The difference in the output phase of a small high frequency sine wave at two stated levels of a low frequency signal on which it is superimposed.

# TRANSIENT RESPONSE

The time required for the AD773 to achieve its rated accuracy after a full-scale step function is applied to its input.

## OVERVOLTAGE RECOVERY TIME

The time required for the ADC to recover to full accuracy after an analog input signal 150% of full scale is reduced to 50% of the full-scale value.

#### APERTURE DELAY

The difference between the switch delay and the analog delay of the THA. This effective delay represents the point in time, relative to the falling edge of the CLOCK input, that the analog input is sampled.

# APERTURE JITTER

The variations in aperture delay for successive samples.

## PIPELINE DELAY (LATENCY)

The number of clock cycles between conversion initiation and the associated output data being made available. New output data is provided every clock cycle.

# FULL POWER BANDWIDTH

The input frequency at which the amplitude of the reconstructed fundamental is reduced by 3 dB for a full-scale input.

# AD773 — Dynamic Characteristics

Figure 3. CMR vs. Input Frequency  $f_{CLK} = 18 \text{ MSPS}$

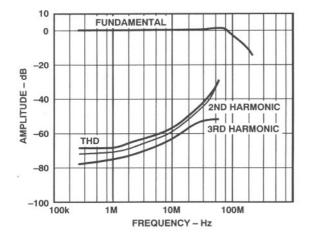

Figure 4. Harmonic Distortion vs. Input Frequency,  $f_{CLK} = 18$  MSPS: Full Power

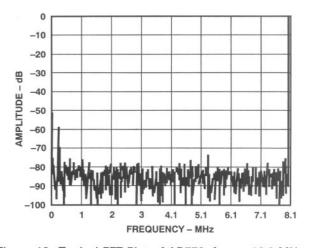

Figure 7. Typical FFT Plot of AD773,  $f_{CLK}=18$  MSPS,  $f_{IN}=8.5$  MHz at 1 V p-p

# Dynamic Characteristics—AD773

Figure 9. CMR vs. Input Frequency,  $f_{CLK} = 16.2 \text{ MSPS}$

Figure 12. Typical FFT Plot of AD773,  $f_{CLK} = 16.2$  MHz,  $f_{IN} = 1$  MHz at 1 V p–p

Figure 10. Harmonic Distortion vs. Input Frequency,  $f_{CLK} = 16.2$  MSPS: Full Power

Figure 13. Typical FFT Plot of AD773,  $f_{\rm CLK}=16.2$  MHz,  $f_{\rm IN}=8.05$  MHz at 1 V p–p

# Theory of Operation

The AD773 uses a pipelined multistage architecture with a differential input, fast settling track-and-hold amplifier (THA). Traditionally, high speed ADCs have used parallel, or flash architectures. When compared to flash converters, multistage architectures reduce the power dissipation and die size by reducing the number of comparators. For example, the AD773 uses 48 comparators compared to 1023 comparators for a 10-bit flash architecture.

The AD773's main signal path transmits differential current mode signals. Low impedance current summing techniques are employed, increasing speed by reducing sensitivity to parasitic capacitances. Pipelining allows the stages to operate concurrently and maximizes system throughput.

The input THA is followed by three 4-bit donversion stages. At any given time, the first stage operates on the most recent sample, while the second stage operates on a signal dependent on the previous sample. This process continues throughout all three stages. The twelve digital bits provided by the three 4-bit stages are combined in the correction logic to produce a 10-bit representation of the sampled analog input.

Pipeline delay, or latency, is four clock cycles. New output data is provided every clock cycle and is provided in both binary and twos complement format. The AD773 will flag an out-of-range condition when the analog input exceeds the specified analog input range.

# Applying the AD773

#### **DRIVING THE AD773 INPUT**

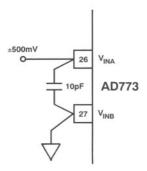

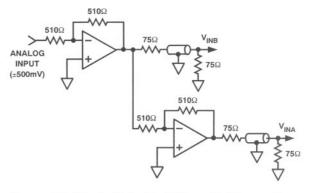

The AD773 may be driven in a single-ended or differential fashion.  $V_{\rm INA}$  is the positive input, and  $V_{\rm INB}$  is the negative input. In the signle-ended configuration either  $V_{\rm INA}$  or  $V_{\rm INB}$  is connected to Analog Ground (AGND) while the other input is driven with a full-scale input of  $\pm 500$  mV p–p. An inverted mode of operation can be achieved by simply interchanging the input connections.

Both inputs of the AD773,  $V_{\rm INA}$  and  $V_{\rm INB}$ , are high impedance and do not need to be driven by a low impedance source. Note, however, that as the source impedance increases, the input node becomes more susceptible to noise. The increased noise at the input will degrade performance. A 10 pF capacitor across  $V_{\rm INA}$  and  $V_{\rm INB}$  as shown in Figure 14 is recommended to bypass high frequency noise.

Figure 14. AD773 Single-Ended Input Connection

#### INPUT CONDITIONING

In some cases, it may be appropriate to buffer the input source, add dc offset, or otherwise condition the input signal of the AD773. Choosing an appropriate op amp will vary with system requirements and the desired level of performance. Some suggested op amps are the AD9617, AD842, and AD827.

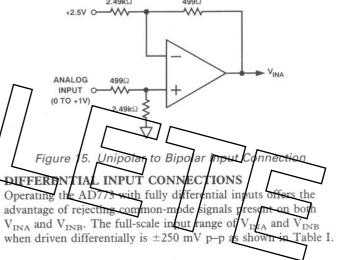

Figure 15 shows a typical application where a unipolar signal is level shifted to the bipolar input range of the AD773. Note that the reference used with the AD773 can also provide a noise-free voltage source to generate the dc offset.

Table I. AD773's Maximum Differential Input Voltage

| V <sub>INA</sub>   | V <sub>INB</sub> | V <sub>INA</sub> -V <sub>INB</sub> |

|--------------------|------------------|------------------------------------|

| +250 mV            | -250 mV          | +500 mV                            |

| $-250~\mathrm{mV}$ | +250 mV          | -500 mV                            |

In some applications it may be desirable to convert a singleended signal to a differential signal before being applied to the AD773. Figure 16 shows a single-ended to differential video line driver capable of driving doubly terminated cables.

Figure 16. Single-Ended to Differential Connection

#### REFERENCE INPUT

The AD773's high impedance reference input allows direct connection with standard voltage references. Unlike the resistor ladder requirements of a flash converter the AD773's single pin, high impedance input can be driven from one low cost, low power reference. The high impedance input allows multiple AD773's to be driven from one reference thus minimizing drift errors.

Figure 17 shows the AD773 connected to the AD680. The AD680 is a single supply, low power, low cost 2.5 V reference with performance specifications ideally suited for the AD773. The low pass filter minimizes the AD680's wideband noise. Other recommended 2.5 V references are the AD580 and

Figure 17. Recommended AD773 to AD680 Connection

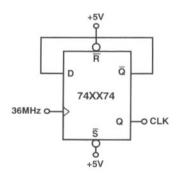

## **CLOCK INPUT**

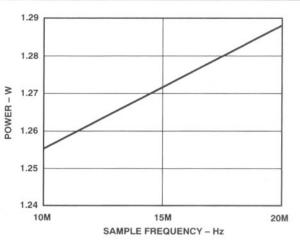

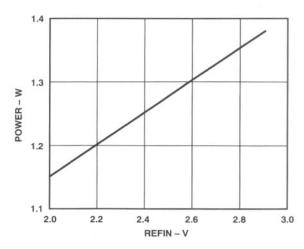

The AD773's pipelined architecture operates on both the rising and falling edges of the clock input. A low jitter, symmetrical clock will provide the highest level of performance. The recommended logic family to drive the clock input is HC. The AD773's minimum clock half cycle may necessitate the use of an external divide-by-two circuit as shown in Figure 18. Power dissipation will vary with input clock frequency. Figure 19 shows the AD773's power dissipation vs. input clock frequency.

Figure 18. Divide-by-Two Clock Circuit

Figure 19. Power Dissipation vs. Sample Frequency

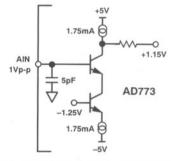

# QUIVALENT ANALOG INPUT CIRCUIT

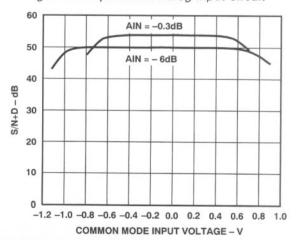

The AD773 equivalent analog input circuit is shown in Figure 20. The typical input bias current is 5 µA, while input capacitance is typically 5 pF. In the single-ended isput configuration one input is connected to AGND while the second input is driven to full scale ( $\pm 500~\text{mV}$ ). Under nominal conditions the collector of the input transistor is at +1.15~V. This allows signals to be offset by up to +0.65~V without significantly degrading performance. In the negative direction, the emitter of the input transistor should not drop below -1.25~V. Therefore, signals can be offset by -0.65~V without significant performance degradation. Figure 21 shows signal-to-noise ratio vs. common mode input voltage.

Figure 20. Equivalent Analog Input Circuit

Figure 21. S/N+D vs. Common-Mode Input Voltage,  $f_{CLK} = 18 \text{ MSPS}$

# **AD773**

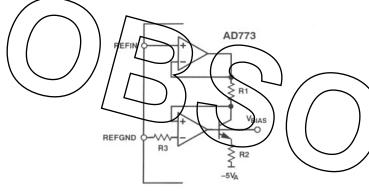

# EQUIVALENT REFERENCE INPUT CIRCUIT

The AD773 is designed to have a reference to analog input voltage ratio of 2.5:1. When the AD773 is configured for single-ended operation a 2.5 volt reference input establishes a full-scale analog input voltage of 1 V p–p ( $\pm500$  mV with respect to  $V_{\rm INB}$ ). Although the AD773 is specified and tested with  $V_{\rm REF}$  equal to 2.5 V and  $V_{\rm IN}$  equal to  $\pm500$  mV the reference input voltage and analog input voltages can be changed. To optimize the AD773's performance the 2.5:1 ratio should be maintained. The simplified model of the AD773's reference input circuit is shown in Figure 22.

Figure 22. Typical Reference Input Circuit

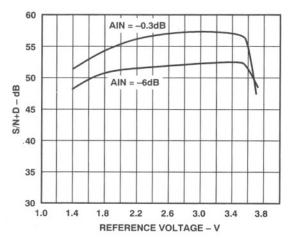

The 2.5 V external reference is applied across resistor R1 producing a current which in turn generates a voltage  $V_{\rm BIAS}$ . Multiple reference currents are generated from  $V_{\rm BIAS}$  and are used throughout the converter. R3 is used to cancel errors induced by the input bias current of the REFGND buffer. Figure 23 shows the SNR performance as the reference voltage is varied from its nominal value of 2.5 V. The input full-scale voltage is defined by the following equation,

Input Full-Scale Voltage =

$$\frac{Reference\ Voltage}{2.5}$$

The power dissipation is modulated by variations in the reference voltage. Figure 24 shows the variation in power dissipation versus reference voltage.

Figure 23. S/N+D vs. Reference Input Voltage,  $f_{CLK} = 18$  MSPS,  $f_{IN} = 1$  MHz

Figure 24. Power Dissipation vs. Reference Input Voltage

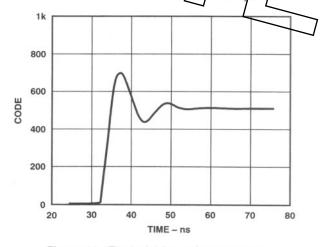

RANSIENT RESPONSE

The fast settling input THA accurately converts full-scale input voltage swings in under one clock cycle. The THA's high impedance, fast slewing performance is critical in multiplexed or de stepped (charge coupled devices, infrared detectors) systems. Figure 25 show the AD773's settling performance with an input signal stepped from 500 mV to 0V. As can be seen, the output code settles to its final value in under one clock cycle.

Figure 25. Typical AD773 Settling Time

### **OUTPUT DATA FORMAT**

The AD773 provides both MSB and MSB outputs, delivering positive true offset binary and twos complement output data. Table II shows the AD773's output data format.

Table II. Output Data Format

| Analog Input                       | Digital Output   |                    |     |  |  |

|------------------------------------|------------------|--------------------|-----|--|--|

| V <sub>INA</sub> -V <sub>INB</sub> | Offset<br>Binary | Twos<br>Complement | OTR |  |  |

| ≥499.5 mV                          | 11 1111 1111     | 01 1111 1111       | 1   |  |  |

| 499 mV                             | 1 111114111      | 01 1111 1111       | 0   |  |  |

| 0 mV                               | 10 0000 0000     | 00 0000 0000       | 0   |  |  |

| -500  mV                           | 00 0000 0000     | 10 0000 0000       | 0   |  |  |

| $\leq$ -500.5 mV                   | 00 0000 0000     | 10 0000 0000       | 1   |  |  |

|                                    |                  | 7 (                | )/  |  |  |

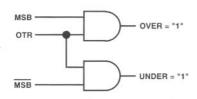

**OUT OF RANGE** An out-of-range condition exists when the analog input is beyond the input range ( $\pm 500 \text{ mV}$ ) of the converter. the AD773 has a 4 clock cycle latency rating.] OTR (Pin 20) is set low when the analog input voltage is within the analog input range. OTR is set HIGH and will remain HIGH when the analog input voltage exceeds the input range by 1/2 LSB from the center of the ± full-scale output codes. OTR will remain HIGH until the analog input is within the input range. By logical ANDing OTR with the MSB and its complement, overrange high or underrange low conditions can be detected. Table III is a truth table for the over/under range circuit in Figure 26. Systems requiring programmable gain conditioning prior to the AD773 can immediately detect an out of range condition, thus eliminating gain selection iterations.

Figure 26. Overrange or Underrange Logic

Table III. Out-of-Range Truth Table

| OTR | MSB | ANALOG INPUT IS |

|-----|-----|-----------------|

| 0   | 0   | In Range        |

| 0   | 1   | In Range        |

| 1   | 0   | Underrange      |

| 1   | 1   | Overrange       |

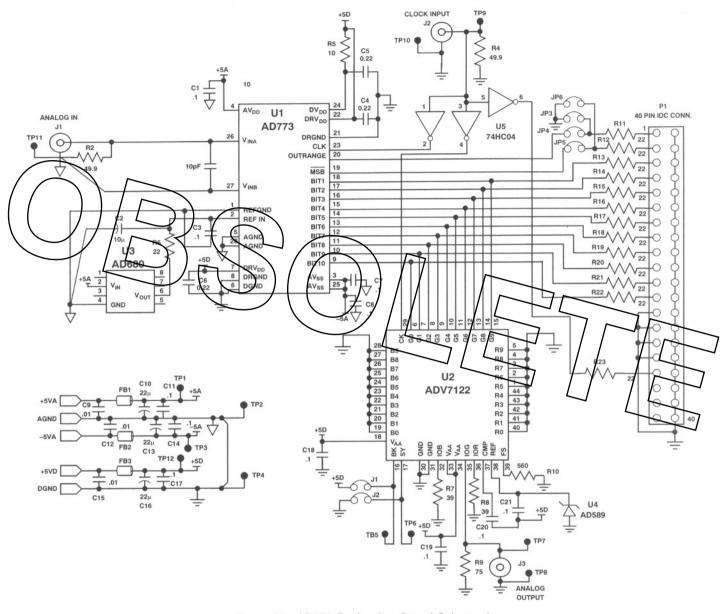

## GROUNDING AND LAYOUT RULES

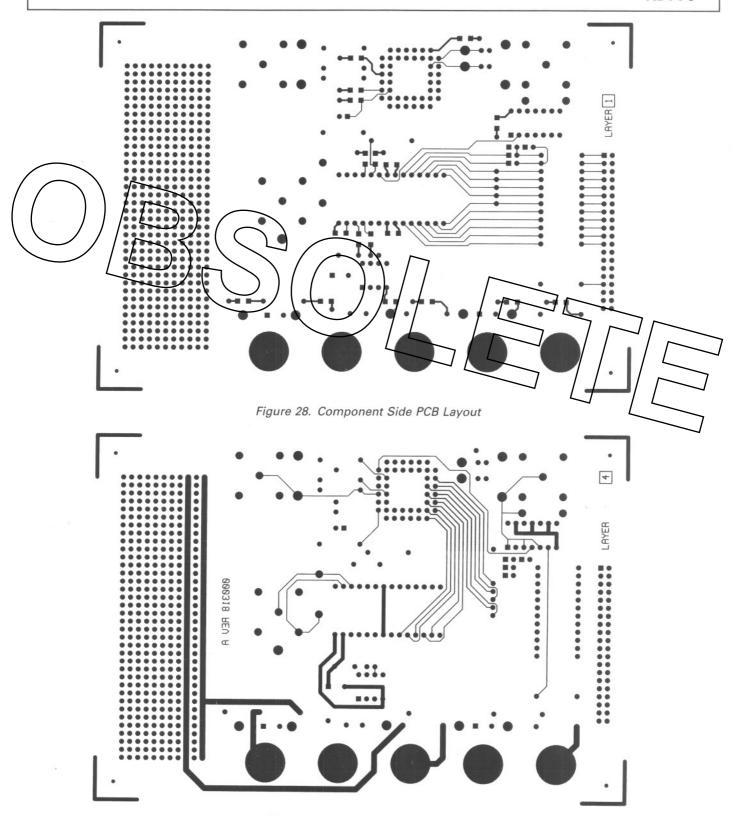

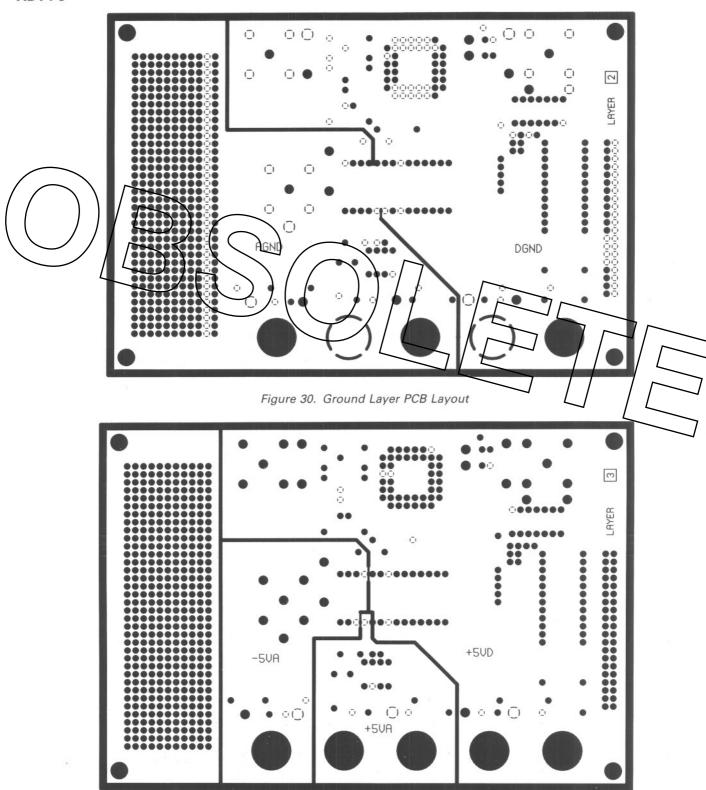

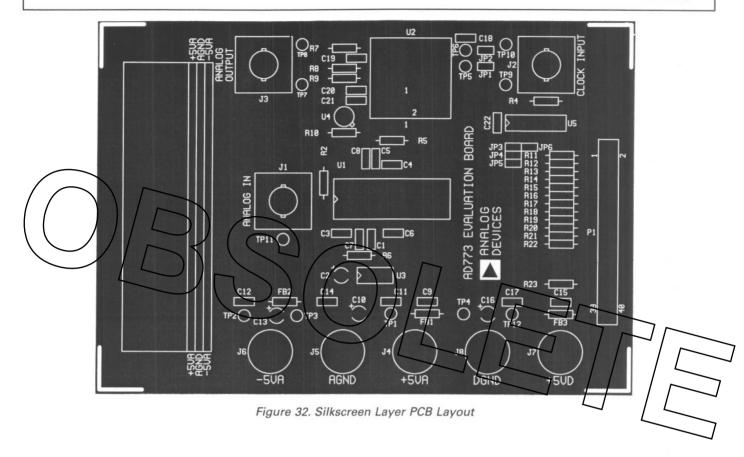

As is the case for any high performance device, proper grounding and layout techniques are essential in achieving optimal performance. (Note—Figures 28–32 are not to scale.) The analog and digital grounds on the AD773 have been separated to optimize the management of return currents in a system. It is recommended that a 4-layer printed circuit board (PCB) which employs ground planes and power planes be used with the AD773. The use of ground and power planes offers distinct advantages:

- The minimization of the loop area encompassed by a signal and its return path.

- 2. The minimization of the impedance associated with ground and power paths.

- The inherent distributed capacitor formed by the power plane, PCB insulation, and ground plane.

These characteristics result in both a reduction of electromagnetic interference (EMI) and an overall improvement in performance.

It is important to design a ayout which prevents noise from coupling onto the input signal. The wide input bandwidth of the AD773 permits noise outside the desired Nyquist bandwidth to be digitized along with the desired signal. This can result in a higher overall level of spurious noise in the digitized spectrum. Digital signals should not be run in parallel with the input signal traces and should be routed away from the input circuitry. It is also suggested that the traces associated with V<sub>INA</sub> and V<sub>INB</sub> be the same length.

Separate analog and digital grounds should be joined together directly under the AD773 (see Figure 30). A solid ground plane under the AD773 is also acceptable if care is taken in the management of the power and ground return currents. A general "rule-of-thumb" for mixed signal layouts dictate that the return currents from digital circuitry should not pass through critical analog circuitry.

# POWER SUPPLY DECOUPLING

The analog and digital supplies of the AD773 have been separated to prevent the typically large transients associated with digital circuitry from coupling into the analog supplies (AV $_{\rm DD}$ , AV $_{\rm SS}$ ). Each analog power supply pin should be decoupled with a 0.1  $\mu F$  capacitor located as close to the pin as possible. Additionally, 0.22  $\mu F$  capacitors for the DRV $_{\rm DD}$  and DV $_{\rm DD}$  supplies are required to adequately suppress high frequency noise. For optimal performance, surface-mount capacitors are recommended. The inductance associated with the leads of throughhole ceramic capacitors typically render them ineffective at higher frequencies. A complete system will also incorporate tantalum capacitors in the 10–100  $\mu F$  range to decouple low frequency noise and ferrite beads to limit high frequency noise.

The digital supplies have also been separated into  $DRV_{\rm DD}$  and  $DV_{\rm DD}$ . The  $DRV_{\rm DD}$  pins provide power for the digital output drivers of the AD773 and are likely to contain high energy transients. Pin 22 should be decoupled directly to Pin 21 (DRGND) and Pin 7 should be decoupled directly to Pin 8 (DRGND) to minimize the length of the return path for these transients. A single +5 V supply is all that is required for  $DRV_{\rm DD}$  and  $DV_{\rm DD}$ , but decoupling  $DV_{\rm DD}$  with an RC filter network is suggested (see Figure 27).

Figure 27. AD773 Evaluation Board Schematic

Table IV. Components List

| Reference Designator         | Description                | Quantity |

|------------------------------|----------------------------|----------|

| R2, R4                       | Resistor, 1%, 49.9 Ω       | 2        |

| R5, R6, R11-R22              | Resistor, 5%, 22 Ω         | 14       |

| R7, R8                       | Resistor, 5%, 39 Ω         | 2        |

| R9                           | Resistor, 5%, 75 Ω         | 1        |

| R10                          | Resistor, 5%, 560 Ω        | 1        |

| C1, C3-C8, C11, C14, C17-C21 | Chip Cap, 0.1 μF           | 14       |

| C2                           | Capacitor, Tantalum, 10 µF | 1        |

| C9, C12, C15                 | Chip Cap, 0.01 µF          | 3        |

| C10, C13, C16                | Capacitor, Tantalum, 22 µF | 3        |

| U1                           | AD773                      | 1        |

| U2                           | ADV7122                    | 1        |

| U3                           | AD680                      | 1        |

| U4                           | AD589                      | 1        |

| U5                           | 74AS04                     | 1        |

| FB1-FB3                      | Ferrite Bead               | 3        |

Figure 29. Solder Side PCB Layout

Figure 31. Power Layer PCB Layout

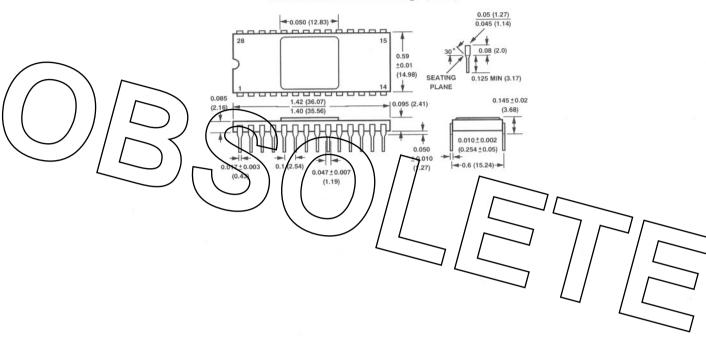

# **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

# 28-Pin Ceramic DIP Package (D-28)