# **ASPM 27 Series**

# 3-Phase 650 V, 40 A Automotive Smart Power Module

# NFVA34065L32

#### **General Description**

NFVA34065L32 is an advanced Automotive SPM<sup>®</sup> module providing a fully-featured, high-performance inverter output stage for hybrid and electric vehicles. These modules integrate optimized gate drive of the built-in IGBTs to minimize EMI and losses, while also providing multiple on-module protection features including under-voltage lockouts, over-current shutdown, thermal monitoring of drive IC, and fault reporting. The built-in, high-speed HVIC requires only a single supply voltage and translates the incoming logic-level gate inputs to the high-voltage, high-current drive signals required to properly drive the module's internal IGBTs. Separate negative IGBT terminals are available for each phase to support the widest variety of control algorithms.

#### **Features**

- Automotive SPM in 27 Pin DIP Package

- AEC & AQG324 Qualified and PPAP Capable

- 650 V/40 A 3-Phase IGBT Inverter with Integral Gate Drivers and Protections

- 175°C Guaranteed Short-Circuit Rated FS Trench IGBTs with Low Vce(sat) and Fast Switching

- Outstanding Thermal Resistance Using AI<sub>2</sub>O<sub>3</sub> DBC Substrate

- Separated Open-Emitter Pins from Low-Side IGBTs for Three-Phase Current Sensing

- Single-Grounded Power Supply

- LVIC Temperature–Sensing Built–In for Temperature Monitoring

- Isolation Rating: 2500 V<sub>rms</sub>/1 min.

- Pb-Free and RoHS Compliant

- UI1557 Certified (File No. E209204) and UL94V-0 Compliant

#### **Applications**

- Automotive high voltage auxiliary motors

- Climate e-Compressors

- Oil/Water Pumps

- Super/Turbo Chargers

- Variety Fans

#### **Related Resources**

<u>AND9800</u> – Automotive Smart Power Module, 650 V ASPM27 Series

1

• AN-9086 - SPM 3 Package Mounting Guidance

#### **Integrated Power Functions**

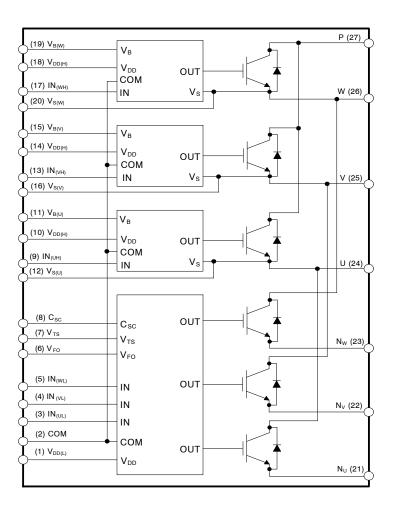

• 650 V-40 A IGBT inverter for three-phase DC/AC power conversion (Refer to Figure 2)

3D Package Drawing (Click to Activate 3D Content)

ASPM27-CCA CASE MODCB

#### MARKING DIAGRAM

ON = onsemi Logo

XX = Version and Current Rate

XXXXXXXXXXX = Specific Device Code

XXX = Lot Number

Y = Year

WW = Work Week

0000001 = Serial Number

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet.

# Integrated Drive, Protection and System Control Functions

- For inverter high-side IGBTs: gate drive circuit, high-voltage isolated high-speed level shifting control circuit, Under-Voltage Lock-Out (UVLO) protection

- For inverter low-side IGBTs: gate drive circuit, Short-Circuit Protection (SCP) control circuit, Under-Voltage Lock-Out Protection (UVLO)

- Fault signaling: corresponding to UVLO (low-side supply) and SC faults

- Input interface: active-HIGH interface, works with 3.3/5 V logic, Schmitt-trigger input

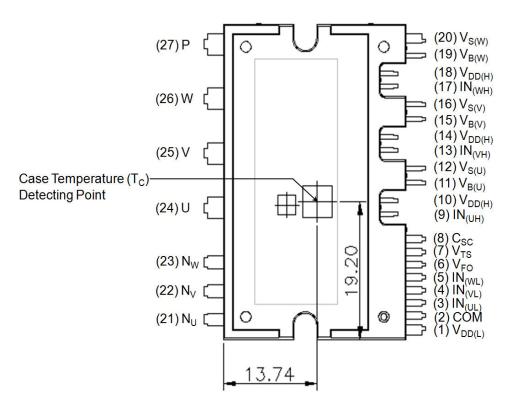

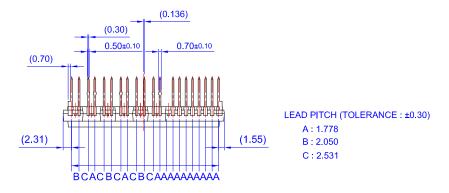

#### **PIN CONFIGURATION**

Figure 1. Top View

#### **PIN DESCRIPTIONS**

| Pin Number | Pin Name             | Pin Description                                           |

|------------|----------------------|-----------------------------------------------------------|

| 1          | $V_{\mathrm{DD(L)}}$ | Low-Side Common Bias Voltage for IC and IGBTs Driving     |

| 2          | СОМ                  | Common Supply Ground                                      |

| 3          | IN <sub>(UL)</sub>   | Signal Input for Low-Side U-Phase                         |

| 4          | IN <sub>(VL)</sub>   | Signal Input for Low-Side V-Phase                         |

| 5          | IN <sub>(WL)</sub>   | Signal Input for Low-Side W-Phase                         |

| 6          | V <sub>FO</sub>      | Fault Output                                              |

| 7          | V <sub>TS</sub>      | Output for LVIC Temperature Sensing Voltage Output        |

| 8          | C <sub>SC</sub>      | Shut Down Input for Short-Circuit Current Detection Input |

| 9          | IN <sub>(UH)</sub>   | Signal Input for High-Side U-Phase                        |

| 10         | V <sub>DD(H)</sub>   | High-Side Common Bias Voltage for IC and IGBTs Driving    |

| 11         | V <sub>B(U)</sub>    | High-Side Bias Voltage for U-Phase IGBT Driving           |

| 12         | V <sub>S(U)</sub>    | High-Side Bias Voltage Ground for U-Phase IGBT Driving    |

| 13         | IN <sub>(VH)</sub>   | Signal Input for High-Side V-Phase                        |

| 14         | V <sub>DD(H)</sub>   | High-Side Common Bias Voltage for IC and IGBTs Driving    |

| 15         | $V_{B(V)}$           | High-Side Bias Voltage for V-Phase IGBT Driving           |

| 16         | V <sub>S(V)</sub>    | High-Side Bias Voltage Ground for V-Phase IGBT Driving    |

| 17         | IN <sub>(WH)</sub>   | Signal Input for High-Side W-Phase                        |

| 18         | V <sub>DD(H)</sub>   | High-Side Common Bias Voltage for IC and IGBTs Driving    |

| 19         | V <sub>B(W)</sub>    | High-Side Bias Voltage for W-Phase IGBT Driving           |

| 20         | V <sub>S(W)</sub>    | High-Side Bias Voltage Ground for W-Phase IGBT Driving    |

| 21         | N <sub>U</sub>       | Negative DC-Link Input for U-Phase                        |

| 22         | N <sub>V</sub>       | Negative DC-Link Input for V-Phase                        |

| 23         | N <sub>W</sub>       | Negative DC-Link Input for W-Phase                        |

| 24         | U                    | Output for U-Phase                                        |

| 25         | V                    | Output for V-Phase                                        |

| 26         | W                    | Output for W-Phase                                        |

| 27         | Р                    | Positive DC-Link Input                                    |

#### INTERNAL EQUIVALENT CIRCUIT AND INPUT/OUTPUT PINS

# NOTES:

- 1. Inverter low-side is composed of three IGBTs, freewheeling diodes for each IGBT, and one control IC. It has gate drive and protection functions.

- Inverter power side is composed of four inverter DC-link input terminals and three inverter output terminals.

Inverter high-side is composed of three IGBTs, freewheeling diodes, and three drive ICs for each IGBT.

Figure 2. Internal Block Diagram

# **ABSOLUTE MAXIMUM RATINGS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

| Symbol                 | Parameter                          | Conditions                                                                                                                                                                                                          | Rating                    | Unit             |

|------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|

| IVERTER PA             | RT                                 | •                                                                                                                                                                                                                   |                           | •                |

| $V_{PN}$               | Supply Voltage                     | Applied between P-N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>                                                                                                                                                  | 500                       | V                |

| V <sub>PN(Surge)</sub> | Supply Voltage (Surge)             | Applied between P-N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>                                                                                                                                                  | 550                       | V                |

| V <sub>CES</sub>       | Collector-Emitter Voltage          |                                                                                                                                                                                                                     | 650                       | V                |

| ±Ι <sub>C</sub>        | Each IGBT Collector Current        | $T_{C} = 100^{\circ}C, V_{DD} \ge 15 \text{ V}, T_{J} \le 175^{\circ}C$ (Note 4)                                                                                                                                    | 40                        | Α                |

| ±I <sub>CP</sub>       | Each IGBT Collector Current (Peak) | $T_C$ = 25°C, $T_J$ ≤175°C, Under 1 ms<br>Pulse Width (Note 4)                                                                                                                                                      | 80                        | А                |

| P <sub>C</sub>         | Collector Dissipation              | T <sub>C</sub> = 25°C per One Chip (Note 4)                                                                                                                                                                         | 107                       | W                |

| TJ                     | Operating Junction Temperature     | IGBT and Diode                                                                                                                                                                                                      | <b>−40~175</b>            | °C               |

|                        |                                    | Driver IC                                                                                                                                                                                                           | <b>−40~150</b>            |                  |

| NTROL PA               | RT                                 |                                                                                                                                                                                                                     |                           |                  |

| $V_{DD}$               | Control Supply Voltage             | Applied between V <sub>DD(H)</sub> , V <sub>DD(L)</sub> -COM                                                                                                                                                        | 20                        | V                |

| $V_{BS}$               | High-Side Control Bias Voltage     | Applied between $V_{B(U)}$ – $V_{S(U)}$ , $V_{B(V)}$ – $V_{S(V)}$ , $V_{B(W)}$ – $V_{S(W)}$                                                                                                                         | 20                        | V                |

| V <sub>IN</sub>        | Input Signal Voltage               | $\begin{array}{c} \text{Applied between IN}_{(\text{UH})}, \text{IN}_{(\text{VH})}, \text{IN}_{(\text{WH})}, \\ \text{IN}_{(\text{UL})}, \text{IN}_{(\text{VL})}, \text{IN}_{(\text{WL})} - \text{COM} \end{array}$ | -0.3~V <sub>DD</sub> +0.3 | V                |

| V <sub>FO</sub>        | Fault Output Supply Voltage        | Applied between V <sub>FO</sub> –COM                                                                                                                                                                                | -0.3~V <sub>DD</sub> +0.3 | V                |

| I <sub>FO</sub>        | Fault Output Current               | Sink Current at V <sub>FO</sub> pin                                                                                                                                                                                 | 2                         | mA               |

| V <sub>SC</sub>        | Current Sensing Input Voltage      | Applied between C <sub>SC</sub> -COM                                                                                                                                                                                | -0.3~V <sub>DD</sub> +0.3 | V                |

| TAL SYSTE              | М                                  |                                                                                                                                                                                                                     |                           |                  |

| t <sub>SC</sub>        | Short Circuit Withstand Time       | $V_{DD} = V_{BS} \le 16.5 \text{ V}, V_{PN} \le 400 \text{ V}, \\ T_J = 150^{\circ}\text{C} \\ \text{Non-repetitive}$                                                                                               | 3                         | μs               |

| T <sub>STG</sub>       | Storage Temperature                |                                                                                                                                                                                                                     | <b>−</b> 55~175           | °C               |

| V <sub>ISO</sub>       | Isolation Voltage                  | 60 Hz, Sinusoidal, AC 1 minute,<br>Connection Pins to Heat Sink Plate                                                                                                                                               | 2500                      | V <sub>rms</sub> |

#### THERMAL RESISTANCE

| Symbol         | Parameter                           | Conditions                                                     | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------------|----------------------------------------------------------------|------|------|------|------|

| $R_{th(j-c)Q}$ | Junction to Case Thermal Resistance | Inverter IGBT part (per 1/6 module)                            | -    | -    | 1.40 | °C/W |

| $R_{th(j-c)F}$ | (Note 5)                            | Inverter FWD part (per 1/6 module)                             | -    | -    | 2.20 | °C/W |

| $L_\sigma$     | Package Stray Inductance            | P to N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub> (Note 5) | 1    | 24   | -    | nH   |

These values had been made an acquisition by the calculation considered to design factor.

For the measurement point of case temperature (T<sub>C</sub>), please refer to Figure 1. DBC discoloration and Picker Circle Printing allowed, please refer to application note AN-9190 (Impact of DBC Oxidation on SPM<sup>®</sup> Module Performance).

Stray inductance per phase measured per IEC 60747-15.

# **ELECTRICAL CHARACTERISTICS - INVERTER PART** (T<sub>J</sub> as specified)

|    | Symbol                       | Parameter                              | Conditions                                                                                                                                   | Min. | Тур. | Max. | Unit |

|----|------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|    | V <sub>CE(SAT)</sub>         | Collector - Emitter Saturation Voltage | $V_{DD} = V_{BS} = 15 \text{ V}, V_{IN} = 5 \text{ V},$<br>$I_{C} = 40 \text{ A}, T_{J} = 25^{\circ}\text{C}$                                | -    | 1.50 | 2.05 | V    |

|    |                              |                                        | V <sub>DD</sub> = V <sub>BS</sub> = 15 V, V <sub>IN</sub> = 5 V,<br>I <sub>C</sub> = 40 A, T <sub>J</sub> = 175°C                            |      | 1.90 | 2.50 | V    |

|    | V <sub>F</sub>               | FWDi Forward Voltage                   | $V_{IN} = 0 \text{ V}, I_F = 40 \text{ A}, T_J = 25^{\circ}\text{C}$                                                                         | -    | 1.75 | 2.35 | V    |

|    |                              |                                        | $V_{IN} = 0 \text{ V}, I_F = 40 \text{ A}, T_J = 175^{\circ}\text{C}$                                                                        |      | 1.70 | 2.30 | V    |

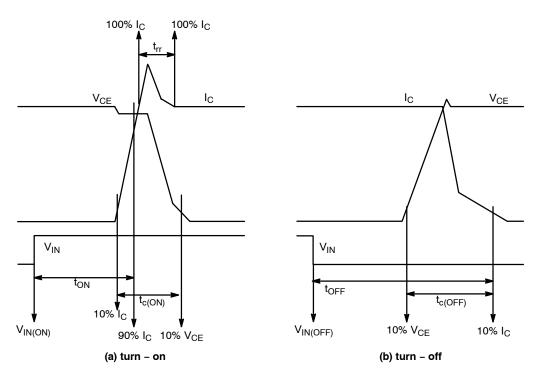

| HS | t <sub>ON</sub>              | High Side Switching Times              | $V_{PN}$ = 300 V, $V_{DD}$ = 15 V, $I_{C}$ = 40 A, $T_{J}$ = 25°C $V_{IN}$ = 0 V $\Leftrightarrow$ 5 V, Inductive Load See Figure 5 (Note 7) | 0.75 | 1.15 | 1.75 | μs   |

|    | t <sub>C(ON)</sub>           |                                        |                                                                                                                                              | -    | 0.25 | 0.75 | μs   |

|    | t <sub>OFF</sub>             |                                        |                                                                                                                                              | -    | 1.20 | 1.70 | μs   |

|    | t <sub>C(OFF)</sub> (Note /) | (Note 1)                               | -                                                                                                                                            | 0.15 | 0.50 | μs   |      |

|    | t <sub>rr</sub>              |                                        |                                                                                                                                              | -    | 0.14 | _    | μs   |

| LS | t <sub>ON</sub>              | Low Side Switching Times               | $V_{PN}$ = 300 V, $V_{DD}$ = 15 V, $I_{C}$ = 40 A, $T_{.1}$ = 25°C                                                                           | 0.60 | 1.00 | 1.60 | μs   |

|    | t <sub>C(ON)</sub>           |                                        | $V_{IN} = 0 V \Leftrightarrow 5 V$ , Inductive Load                                                                                          | -    | 0.25 | 0.70 | μs   |

|    | t <sub>OFF</sub>             |                                        | See Figure 5<br>(Note 7)                                                                                                                     | -    | 1.25 | 1.75 | μs   |

|    | t <sub>C(OFF)</sub>          |                                        |                                                                                                                                              | -    | 0.20 | 0.55 | μs   |

|    | t <sub>rr</sub>              |                                        |                                                                                                                                              | -    | 0.14 | _    | μs   |

|    | I <sub>CES</sub>             | Collector-Emitter Leakage Current      | $T_J = 25^{\circ}C$ , $V_{CE} = V_{CES}$                                                                                                     | -    | -    | 3    | mA   |

<sup>7.</sup> t<sub>ON</sub> and t<sub>OFF</sub> include the propagation delay time of the internal drive IC. t<sub>C(ON)</sub> and t<sub>C(OFF)</sub> are the switching time of IGBT itself under the given gate driving condition internally. For the detailed information see Figure 3.

# PACKAGE MARKING AND ORDERING INFORMATION

| Part Number  | Top Marking  | Package    | Shipping      |

|--------------|--------------|------------|---------------|

| NFVA34065L32 | NFVA34065L32 | ASPM27-CCA | 10 Units/Tube |

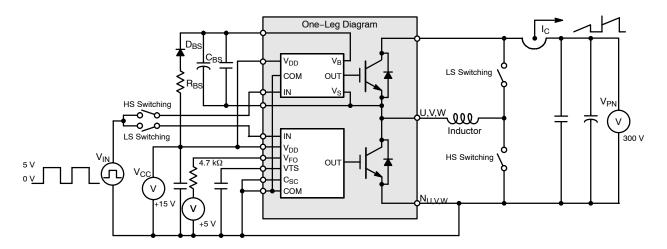

Figure 3. Switching Time Definition

Figure 4. Example Circuit for Switching Test

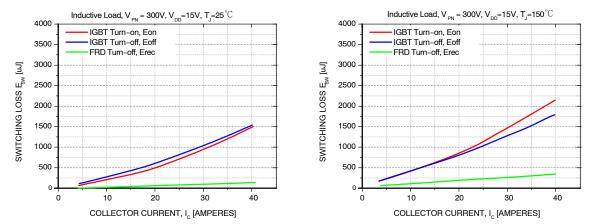

Figure 5. Switching Loss Characteristics

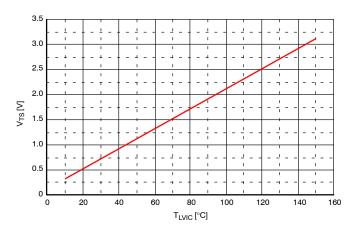

Figure 6. Temperature Profile of V<sub>TS</sub> (Typical)

# $\textbf{CONTROL PART} \; (T_J = 25^{\circ} C)$

| Symbol               | Parameter                                  | Conditions                                                                                                                              |                                                                                                           | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>QDDH</sub>    | Quiescent V <sub>DD</sub> Supply Current   | V <sub>DD(H)</sub> = 15 V,<br>IN <sub>(UH,VH,WH)</sub> = 0 V                                                                            | V <sub>DD(H)</sub> – COM                                                                                  | -    | -    | 0.40 | mA   |

| I <sub>QDDL</sub>    |                                            | V <sub>DD(L)</sub> = 15 V,<br>IN <sub>(UL,VL.WL)</sub> = 0 V                                                                            | V <sub>DD(L)</sub> – COM                                                                                  | -    | -    | 4.80 | mA   |

| I <sub>PDDH</sub>    | Operating V <sub>DD</sub> Supply Current   | V <sub>DD(H)</sub> = 15 V, f <sub>PWM</sub> = 20 kHz,<br>duty = 50%, applied to one<br>PWM signal input for High–<br>Side               | V <sub>DD(H)</sub> – COM                                                                                  | _    | -    | 0.48 | mA   |

| I <sub>PDDL</sub>    |                                            | V <sub>DD(L)</sub> = 15 V, f <sub>PWM</sub> = 20 kHz,<br>duty = 50%, applied to one<br>PWM signal input for Low–<br>Side                | V <sub>DD(L)</sub> – COM                                                                                  | -    | -    | 8.80 | mA   |

| I <sub>QBS</sub>     | Quiescent V <sub>BS</sub> Supply Current   | V <sub>BS</sub> = 15 V,<br>IN <sub>(UH,VH.WH)</sub> = 0 V                                                                               | $ \begin{aligned} &V_{B(U)} - V_{S(U)}, \\ &V_{B(V)} - V_{S(V)}, \\ &V_{B(W)} - V_{S(W)}, \end{aligned} $ | -    | -    | 0.24 | mA   |

| I <sub>PBS</sub>     | Operating V <sub>BS</sub> Supply Current   | V <sub>DD</sub> = V <sub>BS</sub> = 15 V,<br>f <sub>PWM</sub> = 20 kHz, duty = 50%,<br>applied to one PWM signal<br>input for High–Side | $ \begin{aligned} &V_{B(U)} - V_{S(U)}, \\ &V_{B(V)} - V_{S(V)}, \\ &V_{B(W)} - V_{S(W)}, \end{aligned} $ | _    | -    | 4.40 | mA   |

| V <sub>FOH</sub>     | Fault Output Voltage                       | $V_{DD}$ = 15 V, $V_{SC}$ = 0 V, $V_{FO}$ Circuit: 4.7 k $\Omega$ to 5 V Pull–up                                                        |                                                                                                           | 4.5  | -    | -    | V    |

| V <sub>FOL</sub>     |                                            | V <sub>DD</sub> = 15 V, V <sub>SC</sub> = 1 V, V <sub>FO</sub> Circ<br>Pull-up                                                          | cuit: 4.7 kΩ to 5 V                                                                                       | -    | -    | 0.50 | V    |

| V <sub>SC(ref)</sub> | Short Circuit Trip Level                   | V <sub>DD</sub> = 15 V (Note 8)                                                                                                         | C <sub>SC</sub> - COM <sub>(L)</sub>                                                                      | 0.45 | 0.50 | 0.55 | V    |

| $UV_DDD$             | Supply Circuit Under-Voltage               | Detection Level                                                                                                                         |                                                                                                           | 9.80 | _    | 13.3 | V    |

| UV <sub>DDR</sub>    | Protection                                 | Reset Level                                                                                                                             |                                                                                                           | 10.3 | -    | 13.8 | V    |

| UV <sub>BSD</sub>    |                                            | Detection Level                                                                                                                         |                                                                                                           | 9.00 | _    | 12.5 | V    |

| UV <sub>BSR</sub>    |                                            | Reset Level                                                                                                                             |                                                                                                           | 9.50 | _    | 13.0 | V    |

| t <sub>FOD</sub>     | Fault-Out Pulse Width                      |                                                                                                                                         |                                                                                                           | 50   | _    | -    | μs   |

| V <sub>TS</sub>      | LVIC Temperature Sensing<br>Voltage Output | V <sub>DD(L)</sub> = 15 V, T <sub>LVIC</sub> = 25°C (No<br>See Figure 6                                                                 | ote 9)                                                                                                    | 540  | 640  | 740  | mV   |

| V <sub>IN(ON)</sub>  | ON Threshold Voltage                       | Applied between IN <sub>(UH,VH.WH)</sub> -                                                                                              | - COM                                                                                                     | -    | _    | 2.60 | V    |

| V <sub>IN(OFF)</sub> | OFF Threshold Voltage                      | IN <sub>(UL,VL.WL)</sub> – COM                                                                                                          |                                                                                                           | 0.80 | -    | -    | V    |

# **RECOMMENDED OPERATING CONDITIONS**

|                                                |                                           |                                                                                                                                            |      | Value |      |      |

|------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| Symbol                                         | Parameter                                 | Conditions                                                                                                                                 | Min. | Тур.  | Max. | Unit |

| V <sub>PN</sub>                                | Supply Voltage                            | Applied between P – N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub>                                                                       | -    | 300   | 400  | V    |

| $V_{DD}$                                       | Control Supply Voltage                    | Applied between V <sub>DD(H)</sub> – COM, V <sub>DD(L)</sub> – COM                                                                         | 14.0 | 15    | 16.5 | V    |

| V <sub>BS</sub>                                | High-Side Bias Voltage                    | $\begin{array}{c} \text{Applied between } V_{B(U)} - V_{S(U)}, \ V_{B(V)} - V_{S(V)}, \\ V_{B(W)} - V_{S(W)} \end{array}$                  | 13.0 | 15    | 18.5 | V    |

| dV <sub>DD</sub> /dt,<br>dV <sub>BS</sub> /dt, | Control Supply Variation                  |                                                                                                                                            | -1   | -     | 1    | V/μs |

| t <sub>dead</sub>                              | Blanking Time for Preventing<br>Arm-Short | For Each Input Signal                                                                                                                      | 2.0  | -     | -    | μs   |

| f <sub>PWM</sub>                               | PWM Input Signal                          | $-40^{\circ}\text{C} \le \text{T}_{\text{C}} \le 125^{\circ}\text{C}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$ | -    | -     | 20   | kHz  |

| V <sub>SEN</sub>                               | Voltage for Current Sensing               | Applied between N <sub>U</sub> , N <sub>V</sub> , N <sub>W</sub> – COM (Including Surge Voltage)                                           | -5   | -     | 5    | V    |

Short-circuit current protection os functioning only at the low-sides.

T<sub>LVIC</sub> is the temperature of LVIC itself. V<sub>TS</sub> is only for sensing temperature of LVIC and can not shutdown IGBTs automatically.

#### **RECOMMENDED OPERATING CONDITIONS (continued)**

| PW <sub>IN(ON)</sub>  | Minimum Input Pulse Width | $V_{DD} = V_{BS} = 15 \text{ V, I}_C \le 40 \text{ A, Wiring Inductance}$ between $N_{\text{UV,V},W}$ and DC Link N < 10 nH            | 2.0 | - | -   | μs |

|-----------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|----|

| PW <sub>IN(OFF)</sub> |                           | (Note 10)                                                                                                                              | 2.0 | - | _   |    |

| PW <sub>IN(ON)</sub>  |                           | $V_{DD} = V_{BS} = 15 \text{ V}$ , 40 A $\leq$ I <sub>C</sub> $\leq$ 80 A, Wiring Inductance between $N_{H,V,W}$ and DC Link N < 10 nH | 2.5 | - | -   | μs |

| PW <sub>IN(OFF)</sub> |                           | (Note 10)                                                                                                                              | 2.5 | - | -   |    |

| $T_J$                 | Junction Temperature      |                                                                                                                                        | -40 | - | 150 | °C |

<sup>10.</sup> This product might not make response if input pulse width is less than the recommended value.

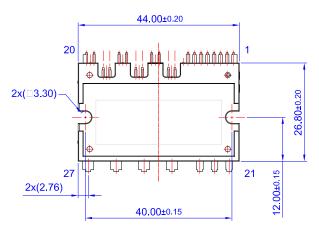

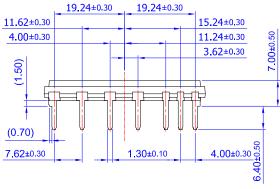

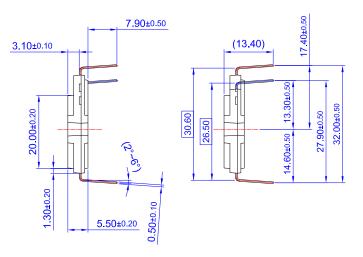

#### **MECHANICAL CHARACTERISTICS AND RATINGS**

|                           | Value                   |                         |     |      |      |       |

|---------------------------|-------------------------|-------------------------|-----|------|------|-------|

| Parameter                 |                         | Conditions              |     | Тур. | Max. | Unit  |

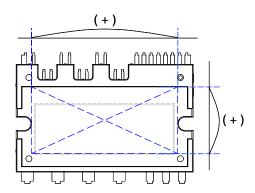

| Device Flatness           | See Figure 7            |                         | 0   | -    | +150 | μm    |

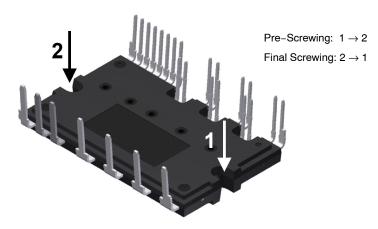

| Mounting Torque           | Mounting Screw: M3      | Recommended 0.7 N•m     | 0.6 | 0.7  | 0.8  | N∙m   |

|                           | See Figure 8 Recom      | Recommended 7.1 kg•cm   | 6.2 | 7.1  | 8.1  | kg∙cm |

| Terminal Pulling Strength | Load 19.8 N             |                         | 10  | -    | -    | s     |

| Terminal Bending Strength | Load 9.8 N 90 deg. bend | Load 9.8 N 90 deg. bend |     | -    | -    | times |

| Weight                    |                         |                         | _   | 15   | -    | g     |

Figure 7. Flatness Measurement Position

#### NOTES:

- 11. Do not make over torque when mounting screws. Much mounting torque may cause DBC cracks, as well as bolts and Al heat-sink destruction

- 12. Avoid one–sided tightening stress. Figure 8 shows the recommended torque order for mounting screws. Uneven mounting can cause the DBC substrate of package to be damaged. The pre–screwing torque is set to 20 ~ 30% of maximum torque rating.

Figure 8. Mounting Screws Torque Order

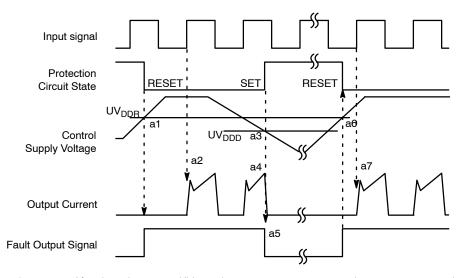

- a1: Control supply voltage rises: After the voltage rises UVDDR, the circuits start to operate when next input is applied.

- a2: Normal operation: IGBT ON and carrying current.

- a3: Under voltage detection (UV<sub>DDD</sub>).

- a4: IGBT OFF in spite of control input condition.

- a5: Fault output operation starts with a fixed pulse width.

- a6: Under voltage reset (UV<sub>DDR</sub>).

- a7: Normal operation: IGBT ON and carrying current by triggering next signal from LOW to HIGH.

Input signal Protection RESET SE1 **RESET** Circuit State UV<sub>BSB</sub> UV<sub>BSD</sub> Control b3 Supply Voltage b6 b2 ، Output Current High-level (no fault output) Fault Output Signal

Figure 9. Under-Voltage Protection (Low-Side)

- b1: Control supply voltage rises: After the voltage rises UV<sub>BSR</sub>, the circuits start to operate when next input is applied.

- b2: Normal operation: IGBT ON and carrying current.

- b3: Under voltage detection (UV<sub>BSD</sub>).

- b4: IGBT OFF in spite of control input condition, but there is no fault output signal.

- b5: Under voltage reset (UV<sub>BSB</sub>).

- b6: Normal operation: IGBT ON and carrying current by triggering next signal from LOW to HIGH.

Figure 10. Under-Voltage Protection (High-Side)

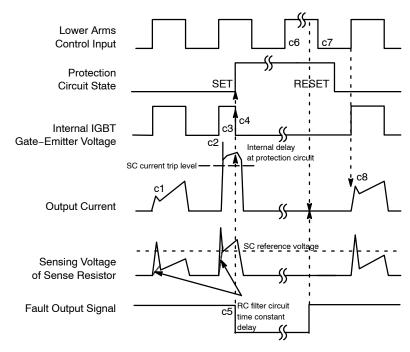

(with the external sense resistance and RC filter connection)

- c1: Normal operation: IGBT ON and carrying current.

- c2: Short circuit current detection (SC trigger).

- c3: All low-side IGBT's gate are hard interrupted.

- c4: All low-side IGBTs turn OFF.

- c5: Fault output operation starts with a fixed pulse width.

- c6: Input HIGH: IGBT ON state, but during the active period of fault output the IGBT doesn't turn ON.

- c7: Fault output operation finishes, but IGBT doesn't turn on until triggering next signal from LOW to HIGH.

- c8: Normal operation: IGBT ON and carrying current.

Figure 11. Short-Circuit Current Protection (Low-Side Operation Only)

# INPUT/OUTPUT INTERFACE CIRCUIT +5V (MCU or Control power) ASPM IN<sub>(UL)</sub>, IN<sub>(VL)</sub>, IN<sub>(WL)</sub> IN<sub>(UL)</sub>, IN<sub>(VL)</sub>, IN<sub>(WL)</sub> COM

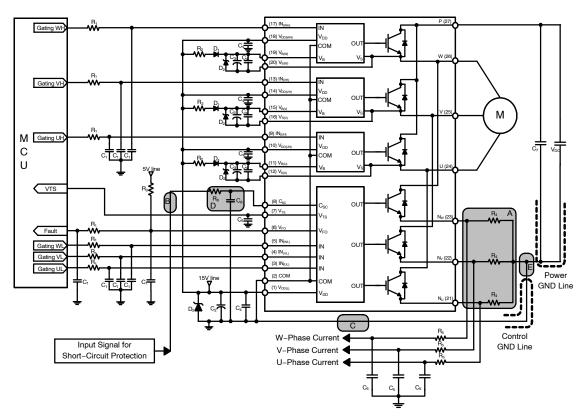

#### NOTE:

13.RC coupling at each input might change depending on the PWM control scheme used in the application and the wiring impedance of the application's printed circuit board. The input signal section of the ASPM27 product integrates 5kΩ (typ.) pull–down resistor. Therefore, when using an external filtering resistor, please pay attention to the signal voltage drop at input terminal.

Figure 12. Recommended CPU I/O Interface Circuit

#### NOTES:

- 14. To avoid malfunction, the wiring of each input should be as short as possible. (less than 2-3 cm)

- 15.V<sub>FO</sub> output is open-drain type. The signal line should be pulled up to the positive side of the MCU or control power supply with a resistor that makes I<sub>FO</sub> up to 2mA. Refer to Figure 12.

- 16. Input signal is active–HIGH type. There is a 5 kΩ resistor inside the IC to pull–down each input signal line to GND. RC coupling circuits should be adopted for the prevention of input signal oscillation. R<sub>1</sub>C<sub>1</sub> time constant should be selected in the range 50~150 ns. (Recommended R<sub>1</sub> = 100 Ω, C<sub>1</sub> = 1 nF)

- 17. Each wiring pattern inductance of A point should be minimized (Recommended less than 10 nH). Use the shunt resistor R<sub>4</sub> of surface mounted (SMD) type to reduce wiring inductance. To prevent malfunction, wiring of point E should be connected to the terminal of the shunt resistor R<sub>4</sub> as close as possible.

- 18. To prevent errors of the protection function, the wiring of B, C and D point should be as short as possible.

- 19. In the short-circuit protection circuit, please select the R<sub>6</sub>C<sub>6</sub> time constant in the range 1.5~2 µs.

- 20. Each capacitor should be mounted as close to the pins of the ASPM27 product as possible.

- 21. To prevent surge destruction, the wiring between the smoothing capacitor C<sub>7</sub> and the P & GND pins should be as short as possible. The use of a high-frequency non-inductive capacitor between the P & GND pins is recommended.

- 22. Relays are used at almost every systems of electrical equipment at industrial application. In these cases, there should be sufficient distance between the CPU and the relays.

- 23. The zener diode or transient voltage suppressor should be adopted for the protection of ICs from the surge destruction between each pair of control supply terminals (Recommended zener diode is 22 V/1 W. which has the lower zener impedance characteristic than about 15 Ω).

- 24. C<sub>2</sub> of around 7 times larger than bootstrap capacitor C<sub>3</sub> is recommended.

- 25. Choose the electrolytic capacitor with good temperature characteristic in  $C_3$ . Also choose 0.1~0.2  $\mu F$  R-category ceramic capacitors with good temperature and frequency characteristics in  $C_4$ .

Figure 13. Typical Application Circuit

SPM is a registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

#### 27LD MODULE PDD STD CASE MODCB ISSUE A

**DATE 30 JAN 2023**

A) THIS PACKAGE DOES NOT COMPLY

TO ANY CURRENT PACKAGING STANDARD

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS ARE EXCLUSIVE OF BURRS,

MOLD FLASH, AND TIE BAR EXTRUSIONS.

D) ( ) IS REFERENCE

NOTES: UNLESS OTHERWISE SPECIFIED

| DOCUMENT NUMBER: 98AON13500G |                     | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:                 | 27LD MODULE PDD STD | •                                                                                                                                                                                   | PAGE 1 OF 1 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative