**ADS8688AT** SBAS813 – JUNE 2018

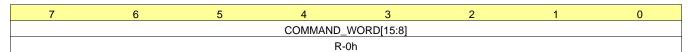

# ADS8688AT 16-Bit, 500-kSPS, 8-Channel, Single-Supply, SAR ADC With Bipolar Input Ranges

## 1 Features

- 16-Bit ADC With Integrated Analog Front-End

- 8-Channel MUX With Auto and Manual Scan

- Channel-Independent Programmable Inputs:

- ±10.24 V, ±5.12 V, ±2.56 V, ±1.28 V, ±0.64 V

- 10.24 V, 5.12 V, 2.56 V, 1.28 V

- 5-V Analog Supply: 1.65-V to 5-V I/O Supply

- Constant Resistive Input Impedance: 1 MΩ

- Input Overvoltage Protection: Up to ±20 V

- Integrated 4.096-V Reference With 6 ppm/°C Drift

- Excellent Performance:

- 500-kSPS Aggregate Throughput

- DNL: ±0.5 LSB; INL: ±0.75 LSB

- 1-ppm/°C Drift for Gain Error and Offset

- SNR: 92 dB; THD: –102 dB

- Low Power: 65 mW

- AUX Input → Direct Connection to ADC Inputs

- ALARM → High and Low Thresholds per Channel

- SPI™-Compatible Interface With Daisy-Chain

- Temperature Range: -55°C to +125°C

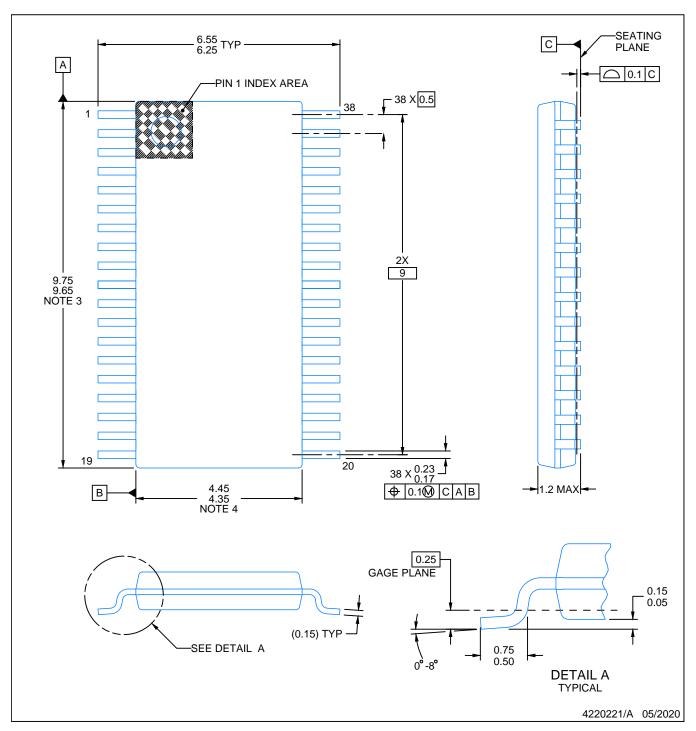

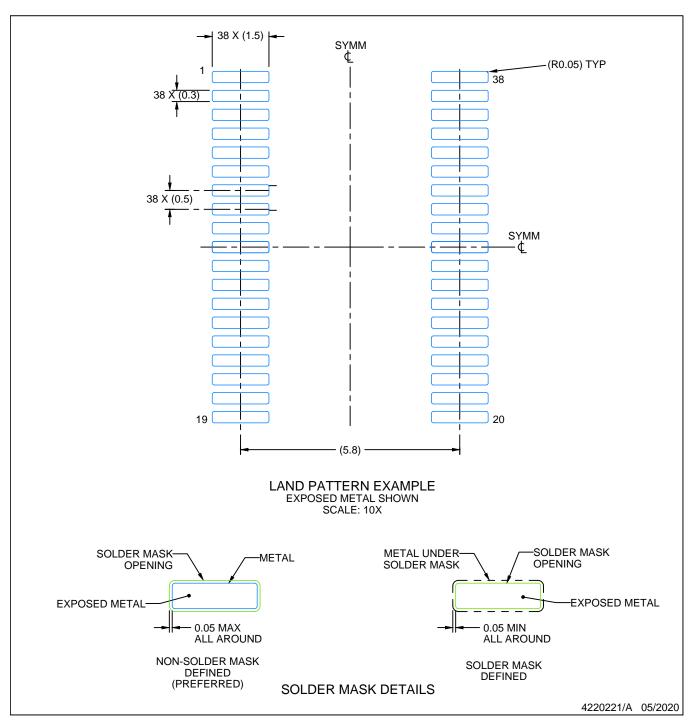

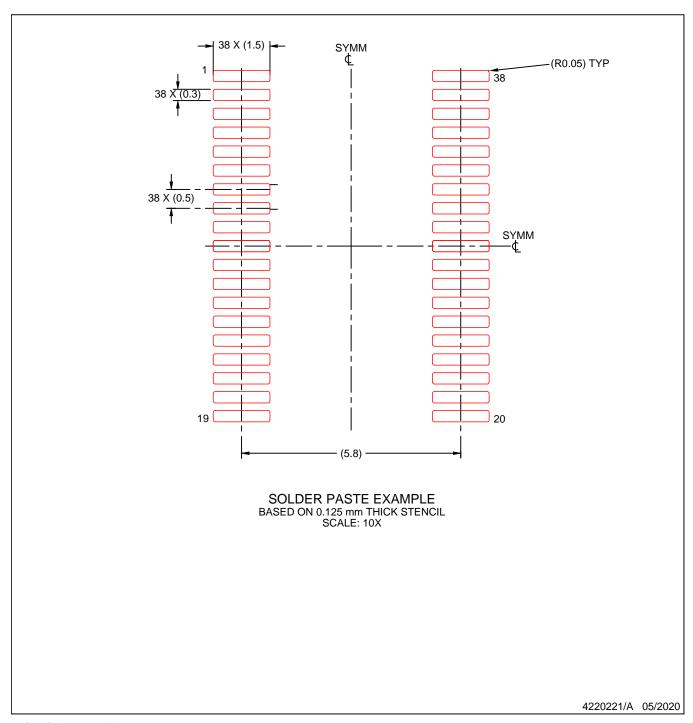

- TSSOP-38 Package (9.7 mm x 4.4 mm)

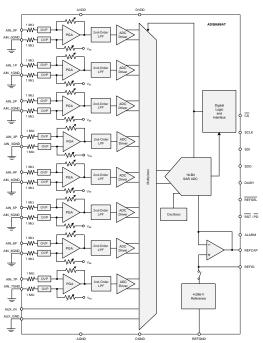

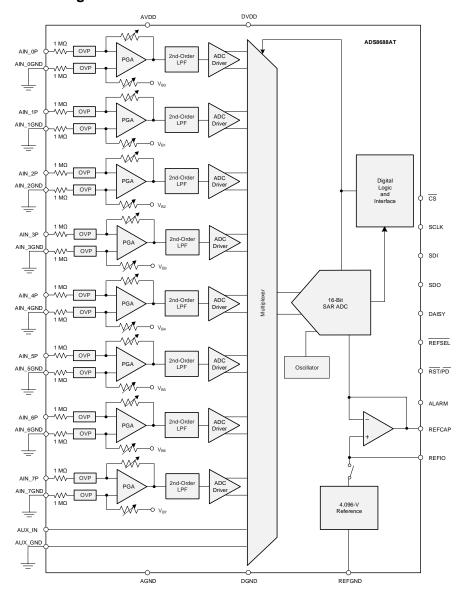

## **Block Diagram**

# 2 Applications

- Power Automation

- Protection Relays

- PLC Analog Input Modules

## 3 Description

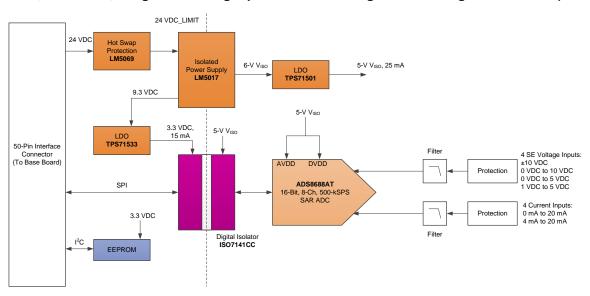

The ADS8688AT is an 8-channel, integrated data acquisition system based on a 16-bit successive approximation (SAR) analog-to-digital converter (ADC), operating at a throughput of up to 500 kSPS. The device features integrated analog front-end circuitry for each input channel with up to ±20-V overvoltage protection, an 8-channel multiplexer with automatic and manual scanning modes, and an integrated 4.096-V reference with low temperature drift.

Operating on a single 5-V analog supply, each input channel can support multiple true bipolar as well as unipolar input ranges. Each input range is software-programmable and independent for each channel, enabling maximum system flexibility. The analog front-end gain is accurately trimmed to ensure high dc precision for all input ranges. The device offers a 1-M $\Omega$  constant resistive input impedance for any selected input range, enabling direct sensor connection to the device.

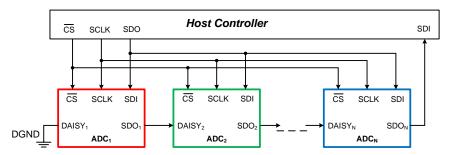

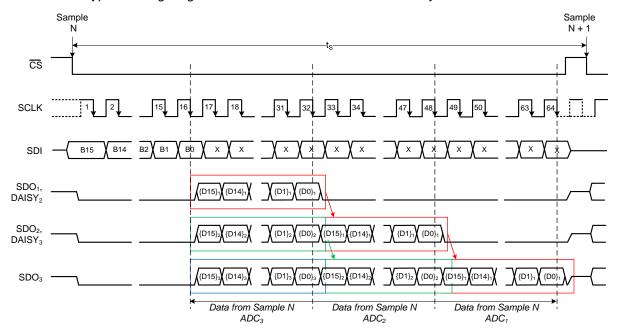

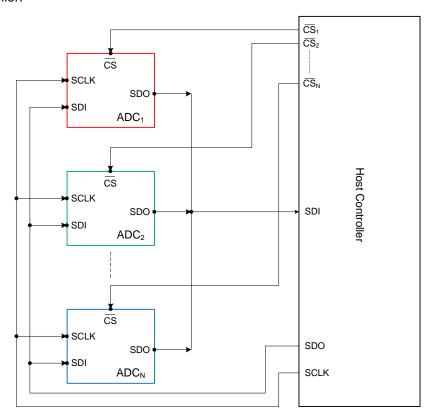

The ADS8688AT offers a simple SPI-compatible serial interface to the digital host and also supports daisy-chaining of multiple devices. The digital supply operates from 1.65 V to 5.25 V, enabling direct interface to a wide range of host controllers.

# **Device Information**(1)

| PART NUMBER | ART NUMBER PACKAGE |                   |

|-------------|--------------------|-------------------|

| ADS8688AT   | TSSOP (38)         | 9.70 mm × 4.40 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

# **Table of Contents**

| 1 | Features 1                                                                     | 7.4 Device Functional Modes3                            |

|---|--------------------------------------------------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                                                                 | 7.5 Register Maps 48                                    |

| 3 | Description 1                                                                  | 8 Application and Implementation 65                     |

| 4 | Revision History2                                                              | 8.1 Application Information 68                          |

| 5 | Pin Configuration and Functions3                                               | 8.2 Typical Applications 68                             |

| 6 | Specifications5                                                                | 9 Power Supply Recommendations 70                       |

| • | 6.1 Absolute Maximum Ratings 5                                                 | 10 Layout 7′                                            |

|   | 6.2 ESD Ratings                                                                | 10.1 Layout Guidelines 7                                |

|   | 6.3 Recommended Operating Conditions5                                          | 10.2 Layout Example72                                   |

|   | 6.4 Thermal Information5                                                       | 11 Device and Documentation Support 73                  |

|   | 6.5 Electrical Characteristics                                                 | 11.1 Documentation Support                              |

|   | 6.6 Timing Requirements: Serial Interface                                      | 11.2 Receiving Notification of Documentation Updates 73 |

|   | 6.7 Switching Characteristics: Serial Interface                                | 11.3 Community Resources                                |

|   | 6.8 Typical Characteristics                                                    | 11.4 Trademarks                                         |

| 7 | Detailed Description23                                                         | 11.5 Electrostatic Discharge Caution                    |

|   | 7.1 Overview                                                                   | 11.6 Glossary                                           |

|   | 7.2 Functional Block Diagram       23         7.3 Feature Description       24 | 12 Mechanical, Packaging, and Orderable Information     |

# 4 Revision History

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| June 2018 | *        | Initial release. |

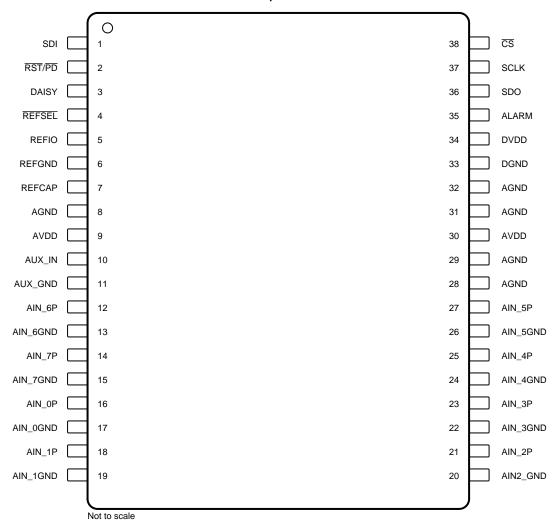

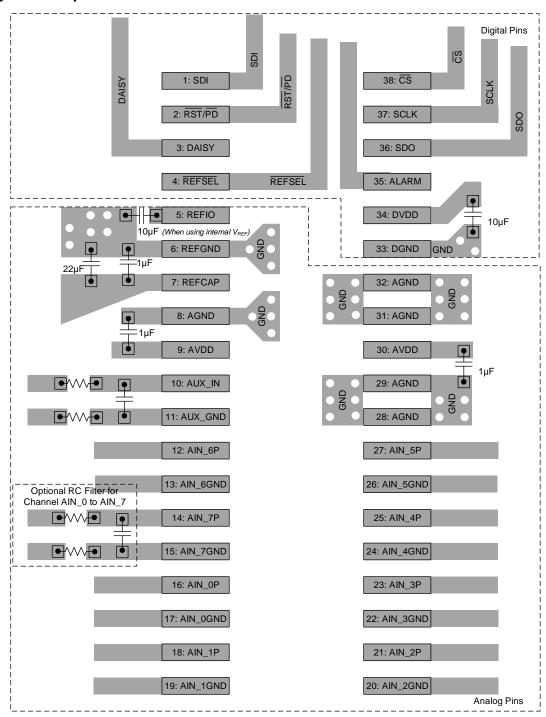

# **Pin Configuration and Functions**

# **Pin Functions**

| NO. | NAME     | I/O                  | DESCRIPTION                                                                                                                                                                                                                                                                       |

|-----|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SDI      | Digital input        | Data input for serial communication.                                                                                                                                                                                                                                              |

| 2   | RST/PD   | Digital input        | Active low logic input. Dual functionality to reset or power-down the device.                                                                                                                                                                                                     |

| 3   | DAISY    | Digital input        | Chain the data input during serial communication in daisy-chain mode.                                                                                                                                                                                                             |

| 4   | REFSEL   | Digital input        | Active low logic input to enable the internal reference. When low, the internal reference is enabled; REFIO becomes an output that includes the $V_{REF}$ voltage. When high, the internal reference is disabled; REFIO becomes an input to apply the external $V_{REF}$ voltage. |

| 5   | REFIO    | Analog input, output | Internal reference output and external reference input pin. Decouple with REFGND on pin 6.                                                                                                                                                                                        |

| 6   | REFGND   | Power supply         | Reference GND pin; short to the analog GND plane. Decouple with REFIO on pin 5 and REFCAP on pin 7.                                                                                                                                                                               |

| 7   | REFCAP   | Analog output        | ADC reference decoupling capacitor pin. Decouple with REFGND on pin 6.                                                                                                                                                                                                            |

| 8   | AGND     | Power supply         | Analog ground pin. Decouple with AVDD on pin 9.                                                                                                                                                                                                                                   |

| 9   | AVDD     | Power supply         | Analog supply pin. Decouple with AGND on pin 8.                                                                                                                                                                                                                                   |

| 10  | AUX_IN   | Analog input         | Auxiliary input channel: positive input. Decouple with AUX_GND on pin 11.                                                                                                                                                                                                         |

| 11  | AUX_GND  | Analog input         | Auxiliary input channel: negative input. Decouple with AUX_IN on pin 10.                                                                                                                                                                                                          |

| 12  | AIN_6P   | Analog input         | Analog input channel 6, positive input. Decouple with AIN_6GND on pin 13.                                                                                                                                                                                                         |

| 13  | AIN_6GND | Analog input         | Analog input channel 6, negative input. Decouple with AIN_6P on pin 12.                                                                                                                                                                                                           |

| 14  | AIN_7P   | Analog input         | Analog input channel 7, positive input. Decouple with AIN_7GND on pin 15.                                                                                                                                                                                                         |

| 15  | AIN_7GND | Analog input         | Analog input channel 7, negative input. Decouple with AIN_7P on pin 14.                                                                                                                                                                                                           |

| 16  | AIN_0P   | Analog input         | Analog input channel 0, positive input. Decouple with AIN_0GND on pin 17.                                                                                                                                                                                                         |

| 17  | AIN_0GND | Analog input         | Analog input channel 0, negative input. Decouple with AIN_0P on pin 16.                                                                                                                                                                                                           |

| 18  | AIN_1P   | Analog input         | Analog input channel 1, positive input. Decouple with AIN_1GND on pin 19.                                                                                                                                                                                                         |

| 19  | AIN_1GND | Analog input         | Analog input channel 1, negative input. Decouple with AIN_1P on pin 18.                                                                                                                                                                                                           |

| 20  | AIN2_GND | Analog input         | Analog input channel 2, negative input. Decouple with AIN_2P on pin 21.                                                                                                                                                                                                           |

| 21  | AIN_2P   | Analog input         | Analog input channel 2, positive input. Decouple with AIN_2GND on pin 20.                                                                                                                                                                                                         |

| 22  | AIN_3GND | Analog input         | Analog input channel 3, negative input. Decouple with AIN_3P on pin 23.                                                                                                                                                                                                           |

| 23  | AIN_3P   | Analog input         | Analog input channel 3, positive input. Decouple with AIN_3GND on pin 22.                                                                                                                                                                                                         |

| 24  | AIN_4GND | Analog input         | Analog input channel 4, negative input. Decouple with AIN_4P on pin 25.                                                                                                                                                                                                           |

| 25  | AIN_4P   | Analog input         | Analog input channel 4, positive input. Decouple with AIN_4GND on pin 24.                                                                                                                                                                                                         |

| 26  | AIN_5GND | Analog input         | Analog input channel 5, negative input. Decouple with AIN_5P on pin 27.                                                                                                                                                                                                           |

| 27  | AIN_5P   | Analog input         | Analog input channel 5, positive input. Decouple with AIN_5GND on pin 26.                                                                                                                                                                                                         |

| 28  | AGND     | Power supply         | Analog ground pin                                                                                                                                                                                                                                                                 |

| 29  | AGND     | Power supply         | Analog ground pin                                                                                                                                                                                                                                                                 |

| 30  | AVDD     | Power supply         | Analog supply pin. Decouple with AGND on pin 31.                                                                                                                                                                                                                                  |

| 31  | AGND     | Power supply         | Analog ground pin. Decouple with AVDD on pin 30.                                                                                                                                                                                                                                  |

| 32  | AGND     | Power supply         | Analog ground pin                                                                                                                                                                                                                                                                 |

| 33  | DGND     | Power supply         | Digital ground pin. Decouple with DVDD on pin 34.                                                                                                                                                                                                                                 |

| 34  | DVDD     | Power supply         | Digital supply pin. Decouple with DGND on pin 33.                                                                                                                                                                                                                                 |

| 35  | ALARM    | Digital output       | Active high alarm output                                                                                                                                                                                                                                                          |

| 36  | SDO      | Digital output       | Data output for serial communication                                                                                                                                                                                                                                              |

| 37  | SCLK     | Digital input        | Clock input for serial communication                                                                                                                                                                                                                                              |

| 38  | CS       | Digital input        | Active low logic input; chip-select signal                                                                                                                                                                                                                                        |

www.ti.com SBAS813

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                        | MIN  | MAX        | UNIT |

|----------------------------------------|------|------------|------|

| AIN_nP, AIN_nGND to GND <sup>(2)</sup> | -20  | 20         | V    |

| AIN_nP, AIN_nGND to GND <sup>(3)</sup> | -11  | 11         | V    |

| AUX_GND to GND                         | -0.3 | 0.3        | V    |

| AUX_IN to GND                          | -0.3 | AVDD + 0.3 | V    |

| AVDD to GND or DVDD to GND             | -0.3 | 7          | V    |

| REFCAP to REFGND or REFIO to REFGND    | -0.3 | 5.7        | V    |

| GND to REFGND                          | -0.3 | 0.3        | V    |

| Digital input pins to GND              | -0.3 | DVDD + 0.3 | V    |

| Digital output pins to GND             | -0.3 | DVDD + 0.3 | V    |

| Operating temperature, T <sub>A</sub>  | -55  | 125        | °C   |

| Storage temperature, T <sub>stg</sub>  | -65  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(3) AVDD = floating.

# 6.2 ESD Ratings

|                                            |                                                                   |                                                                     |       |      | UNIT |

|--------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|-------|------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | Analog input pins (AIN_nP; AIN_nGND)                                | ±4000 |      |      |

|                                            |                                                                   | All other pins                                                      | ±2000 | V    |      |

|                                            |                                                                   | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) |       | ±500 |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      | 3 1 3 - (              | ,    |     |      |      |

|------|------------------------|------|-----|------|------|

|      |                        | MIN  | NOM | MAX  | UNIT |

| AVDD | Analog supply voltage  | 4.75 | 5   | 5.25 | V    |

| DVDD | Digital supply voltage | 1.65 | 3.3 | AVDD | V    |

### 6.4 Thermal Information

|                      |                                              | ADS8688AT   |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DBT (TSSOP) | UNIT |

|                      |                                              | 38 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 68.8        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 19.9        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 30.4        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.3         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 29.8        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | NA          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Copyright © 2018, Texas Instruments Incorporated

<sup>(2)</sup> AVDD = 5 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# TEXAS INSTRUMENTS

## 6.5 Electrical Characteristics

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

|                      | PARAMETER                      | TEST CONDITIONS                                                                                                        | MIN                                          | TYP                                       | MAX                                  | UNIT     | TEST<br>LEVEL <sup>(1)</sup> |

|----------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------|--------------------------------------|----------|------------------------------|

| ANALOG INP           | UTS                            |                                                                                                                        |                                              |                                           |                                      |          |                              |

|                      |                                | Input range = $\pm 2.5 \times V_{REF}$                                                                                 | −2.5 × V <sub>REF</sub>                      |                                           | $2.5 \times V_{REF}$                 |          | Α                            |

|                      |                                | Input range = ±1.25 × V <sub>REF</sub>                                                                                 | −1.25 × V <sub>REF</sub>                     |                                           | $1.25 \times V_{REF}$                |          | Α                            |

|                      |                                | Input range = ±0.625 × V <sub>REF</sub>                                                                                | -0.625 × V <sub>REF</sub>                    |                                           | 0.625 × V <sub>REF</sub>             |          | Α                            |

|                      | <b>-</b>                       | Input range = $\pm 0.3125 \times V_{REF}$                                                                              | −0.3125 <b>x</b><br>V <sub>REF</sub>         | (                                         | 0.3125 × V <sub>REF</sub>            | V V V MΩ | А                            |

|                      |                                | Input range = ±0.15625 × V <sub>REF</sub>                                                                              | –0.15625 ×<br>V <sub>REF</sub>               |                                           | 0.15625 <b>x</b><br>V <sub>REF</sub> | V        | А                            |

|                      |                                | Input range = $2.5 \times V_{REF}$                                                                                     | 0                                            |                                           | $2.5 \times V_{REF}$                 |          | Α                            |

|                      |                                | Input range = 1.25 x V <sub>REF</sub>                                                                                  | 0                                            |                                           | $1.25 \times V_{REF}$                |          | Α                            |

|                      |                                | Input range = 0.625 x V <sub>REF</sub>                                                                                 | 0                                            |                                           | $0.625 \times V_{REF}$               |          | Α                            |

|                      |                                | Input range = 0.3125 x V <sub>REF</sub>                                                                                | 0                                            | (                                         | 0.3125 × V <sub>REF</sub>            |          | Α                            |

|                      |                                | Input range = ±2.5 x V <sub>REF</sub>                                                                                  | -2.5 × V <sub>REF</sub>                      |                                           | 2.5 × V <sub>REF</sub>               |          | А                            |

|                      |                                | Input range = ±1.25 × V <sub>REF</sub>                                                                                 | -1.25 × V <sub>REF</sub>                     |                                           | 1.25 × V <sub>REF</sub>              |          | Α                            |

|                      |                                | Input range = ±0.625 × V <sub>REF</sub>                                                                                | -0.625 × V <sub>REF</sub>                    |                                           | 0.625 × V <sub>REF</sub>             |          | Α                            |

|                      |                                | Input range = ±0.3125 × V <sub>REF</sub>                                                                               | -0.3125 x<br>V <sub>REF</sub>                | (                                         | 0.3125 × V <sub>REF</sub>            |          | А                            |

| AIN_ <i>n</i> P      |                                | Input range = ±0.15625 × V <sub>REF</sub>                                                                              | -0.15625 ×<br>V <sub>REF</sub>               |                                           | 0.15625 <b>x</b><br>V <sub>REF</sub> | V        | А                            |

|                      |                                | Input range = 2.5 x V <sub>REF</sub>                                                                                   | 0                                            | $2.5 \times V_{REF}$                      |                                      |          | Α                            |

|                      |                                | Input range = 1.25 x V <sub>REF</sub>                                                                                  | 0                                            |                                           | $1.25 \times V_{REF}$                |          | Α                            |

|                      |                                | Input range = 0.625 x V <sub>REF</sub>                                                                                 | 0                                            |                                           | 0.625 × V <sub>REF</sub>             |          | Α                            |

|                      |                                | Input range = 0.3125 × V <sub>REF</sub>                                                                                | 0                                            | (                                         | 0.3125 × V <sub>REF</sub>            |          | Α                            |

| AIN_nGND             |                                | All input ranges                                                                                                       | -0.1                                         | 0                                         | 0.1                                  | V        | В                            |

| z <sub>i</sub>       | Input impedance                | At $T_A = 25$ °C, all input ranges                                                                                     | 0.85                                         | 1                                         | 1.15                                 | ΜΩ       | В                            |

|                      | Input impedance drift          | All input ranges                                                                                                       |                                              | 7                                         | 32                                   | ppm/°C   | В                            |

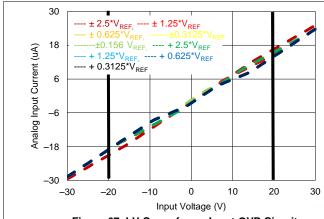

|                      |                                | With voltage at AIN_ $n$ P pin = V <sub>IN</sub> , input range = $\pm 2.5 \times V_{REF}$                              |                                              | V <sub>IN</sub> – 2.25<br>R <sub>IN</sub> |                                      |          | А                            |

|                      |                                | With voltage at AIN_nP pin = $V_{IN}$ , input range = $\pm 1.25 \times V_{REF}$                                        | $\frac{V_{\text{IN}} - 2.00}{R_{\text{IN}}}$ |                                           |                                      |          | А                            |

| I <sub>Ikg(in)</sub> | Input leakage current          | With voltage at AIN_nP pin = $V_{IN}$ , input ranges = ±0.625 × $V_{REF}$ ; ±0.3125 × $V_{REF}$ ; ±0.15625 × $V_{REF}$ |                                              | V <sub>IN</sub> – 1.60<br>R <sub>IN</sub> |                                      | μΑ       | А                            |

|                      |                                | With voltage at AIN_ $n$ P pin = V <sub>IN</sub> , input range = 2.5 × V <sub>REF</sub>                                |                                              | V <sub>IN</sub> - 2.50<br>R <sub>IN</sub> |                                      |          | Α                            |

|                      |                                | With voltage at AIN_nP pin = $V_{IN}$ , input range = 1.25 × $V_{REF}$ ; 0.625 × $V_{REF}$ ; 0.3125 × $V_{REF}$        | V <sub>IN</sub> – 2.50<br>R <sub>IN</sub>    |                                           |                                      |          | А                            |

| INPUT OVER           | VOLTAGE PROTECTION             |                                                                                                                        | -1                                           |                                           |                                      |          | 1                            |

|                      |                                | AVDD = 5 V                                                                                                             | -20                                          |                                           | 20                                   |          | В                            |

| $V_{OVP}$            | Overvoltage protection voltage | AVDD = floating                                                                                                        | -11                                          |                                           | 11                                   | V        | В                            |

<sup>(1)</sup> Test Levels: **(A)** Tested at final test. Overtemperature limits are set by characterization and simulation. **(B)** Limits set by characterization and simulation, across temperature range. **(C)** Typical value only for information, provided by design simulation.

<sup>(2)</sup> Ideal input span, does not include gain or offset error.

www.ti.com SBAS813-JUNE 2018

# **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

|                   | PARAMETER                                | TEST CONDITIONS                                                            | MIN   | TYP   | MAX   | UNIT                | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------|------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|---------------------|------------------------------|

| SYSTEM P          | ERFORMANCE                               |                                                                            |       |       |       |                     |                              |

|                   | Resolution                               |                                                                            | 16    |       |       | Bits                | Α                            |

| NMC               | No missing codes                         |                                                                            | 16    |       |       | Bits                | Α                            |

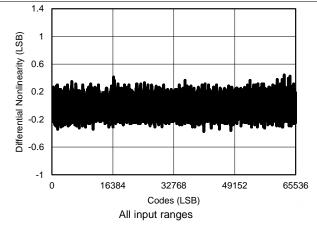

| DNL               | Differential nonlinearity                |                                                                            | -0.99 | ±0.5  | 1.5   | LSB <sup>(3)</sup>  | Α                            |

| INL               | Integral nonlinearity (4)                |                                                                            | -2    | ±0.75 | 2     | LSB                 | Α                            |

| E <sub>G</sub>    | Gain error                               | At T <sub>A</sub> = 25°C, all input ranges                                 |       | ±0.02 | ±0.05 | %FSR <sup>(5)</sup> | Α                            |

|                   | Gain error matching (channel-to-channel) | At T <sub>A</sub> = 25°C, all input ranges                                 |       | ±0.02 | ±0.05 | %FSR                | А                            |

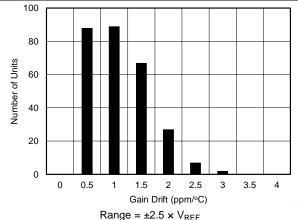

|                   | Gain error temperature drift             | All input ranges                                                           |       | 1     | 6     | ppm/°C              | В                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = $\pm 2.5 \times V_{REF}$ <sup>(6)</sup> |       | ±0.5  | ±1    |                     | А                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = $\pm 1.25 \times V_{REF}$               |       | ±0.5  | ±1    |                     | А                            |

| Eo                | Offset error                             | At $T_A = 25$ °C,<br>input range = ±0.625 × $V_{REF}$                      |       | ±0.5  | ±1.5  | mV                  | Α                            |

| _0                | Oliset elloi                             | At $T_A = 25$ °C,<br>input range = ±0.3125 × $V_{REF}$                     |       | ±0.5  | ±1.5  | IIIV                | Α                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = ±0.15625 × $V_{REF}$                    |       | ±0.5  | ±1.5  |                     | А                            |

|                   |                                          | At $T_A = 25$ °C, all unipolar input ranges                                |       | ±0.5  | ±2    |                     | Α                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = $\pm 2.5 \times V_{REF}$ <sup>(6)</sup> |       | ±0.5  | ±1    |                     | Α                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = ±1.25 × $V_{REF}$                       |       | ±0.5  | ±1    |                     | А                            |

|                   | Offset error matching                    | At $T_A = 25$ °C,<br>input range = ±0.625 × $V_{REF}$                      |       | ±0.5  | ±1.5  |                     | Α                            |

|                   | (channel-to-channel)                     | At $T_A = 25$ °C,<br>input range = ±0.3125 × $V_{REF}$                     |       | ±0.5  | ±1.5  | mV                  | Α                            |

|                   |                                          | At $T_A = 25$ °C,<br>input range = ±0.15625 × $V_{REF}$                    |       | ±0.5  | ±1.5  |                     | Α                            |

|                   |                                          | At $T_A = 25$ °C, all unipolar input ranges                                |       | ±0.5  | ±2    |                     | Α                            |

|                   |                                          | Input range = ±2.5 x V <sub>REF</sub>                                      |       | 1     | 15    |                     | В                            |

|                   |                                          | Input range = ±1.25 x V <sub>REF</sub>                                     |       | 1     | 4     |                     | В                            |

|                   |                                          | Input range = ±0.625 × V <sub>REF</sub>                                    |       | 1     | 4     |                     | В                            |

|                   |                                          | Input range = ±0.3125 × V <sub>REF</sub>                                   |       | 2     | 15    |                     | В                            |

|                   | Offset error temperature drift           | Input range = ±0.15625 × V <sub>REF</sub>                                  |       | 4     | 26    | ppm/°C              | В                            |

|                   |                                          | Input range = 0 to $2.5 \times V_{REF}$                                    |       | 1     | 12    |                     | В                            |

|                   |                                          | Input range = 0 to 1.25 × V <sub>REF</sub>                                 |       | 1     | 6     |                     | В                            |

|                   |                                          | Input range = 0 to 0.625 x V <sub>REF</sub>                                |       | 2     | 15    |                     | В                            |

|                   |                                          | Input range = 0 to 0.3125 × V <sub>REF</sub>                               |       | 4     | 26    | -                   | В                            |

| SAMPLING          | DYNAMICS                                 |                                                                            |       |       |       |                     |                              |

| t <sub>CONV</sub> | Conversion time                          |                                                                            |       |       | 850   | ns                  | Α                            |

| t <sub>ACQ</sub>  | Acquisition time                         |                                                                            | 1150  |       |       | ns                  | Α                            |

| f <sub>S</sub>    | Maximum throughput rate without latency  |                                                                            |       |       | 500   | kSPS                | А                            |

LSB = least significant bit.

Product Folder Links: ADS8688AT

This parameter is the endpoint INL, not best-fit INL.

FSR = full-scale range. (5)

Does not include the shift in offset over time.

## **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

|                         | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                 | MIN  | TYP  | MAX | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|------------------------------|

| DYNAMIC CH              | HARACTERISTICS                                                 |                                                                                                                                                 |      |      |     |      |                              |

|                         |                                                                | Input range = $\pm 2.5 \times V_{REF}$                                                                                                          | 90   | 92   |     |      | Α                            |

|                         |                                                                | Input range = ±1.25 x V <sub>REF</sub>                                                                                                          | 89   | 91   |     |      | Α                            |

|                         |                                                                | Input range = ±0.625 × V <sub>REF</sub>                                                                                                         | 87.5 | 89   |     |      | Α                            |

|                         |                                                                | Input range = ±0.3125 × V <sub>REF</sub>                                                                                                        | 81.5 | 83   |     |      | Α                            |

| SNR                     | Signal-to-noise ratio<br>(V <sub>IN</sub> – 0.5 dBFS at 1 kHz) | Input range = ±0.15625 × V <sub>REF</sub>                                                                                                       | 75.5 | 77   |     | dB   | Α                            |

| ГНО                     | (VIN 0.0 abi e at i iii.2)                                     | Input range = 2.5 × V <sub>REF</sub>                                                                                                            | 88.5 | 90.5 |     |      | Α                            |

|                         |                                                                | Input range = 1.25 × V <sub>REF</sub>                                                                                                           | 87.5 | 89   |     |      | Α                            |

|                         |                                                                | Input range = 0.625 x V <sub>REF</sub>                                                                                                          | 81.5 | 83   |     |      | Α                            |

|                         |                                                                | Input range = 0.3125 × V <sub>REF</sub>                                                                                                         | 75.5 | 77   |     |      | Α                            |

| TUD                     | Total harmonic distortion <sup>(7)</sup>                       | Input ranges = $\pm 2.5 \times V_{REF}$ , $\pm 1.25 \times V_{REF}$ , $\pm 0.625 \times V_{REF}$ , $2.5 \times V_{REF}$ , $1.25 \times V_{REF}$ |      | -102 |     | dB   | В                            |

| חו                      | (V <sub>IN</sub> – 0.5 dBFS at 1 kHz)                          | Input ranges = $\pm 0.3125 \times V_{REF}$ ,<br>$\pm 0.15625 \times V_{REF}$ , $0.625 \times V_{REF}$ ,<br>$0.3125 \times V_{REF}$              |      | -100 |     |      | Б                            |

|                         |                                                                | Input range = $\pm 2.5 \times V_{REF}$                                                                                                          | 89   | 91.5 |     |      | Α                            |

|                         | Signal-to-noise ratio<br>(V <sub>IN</sub> – 0.5 dBFS at 1 kHz) | Input range = ±1.25 x V <sub>REF</sub>                                                                                                          | 88.5 | 91   |     | dB   | Α                            |

|                         |                                                                | Input range = ±0.625 × V <sub>REF</sub>                                                                                                         | 87   | 89   |     |      | Α                            |

|                         |                                                                | Input range = $\pm 0.3125 \times V_{REF}$                                                                                                       | 81   | 83   |     |      | Α                            |

| SINAD                   |                                                                | Input range = $\pm 0.15625 \times V_{REF}$                                                                                                      | 75   | 77   |     |      | Α                            |

|                         | (1111 010 000 000 1111 000 000 000 000 0                       | Input range = 2.5 × V <sub>REF</sub>                                                                                                            | 87.5 | 90.5 |     |      | Α                            |

|                         |                                                                | Input range = 1.25 x V <sub>REF</sub>                                                                                                           | 87   | 89   |     |      | Α                            |

|                         |                                                                | Input range = 0.625 x V <sub>REF</sub>                                                                                                          | 81   | 83   |     |      | Α                            |

|                         |                                                                | Input range = 0.3125 x V <sub>REF</sub>                                                                                                         | 75   | 77   |     |      | Α                            |

| SFDR                    | Spurious-free dynamic range                                    | Input ranges = $\pm 2.5 \times V_{REF}$ , $\pm 1.25 \times V_{REF}$ , $\pm 0.625 \times V_{REF}$ , $2.5 \times V_{REF}$ , $1.25 \times V_{REF}$ |      | 103  |     | dB   | В                            |

| SI DK                   | (V <sub>IN</sub> – 0.5 dBFS at 1 kHz)                          | Input ranges = $\pm 0.3125 \times V_{REF}$ ,<br>$\pm 0.15625 \times V_{REF}$ , $0.625 \times V_{REF}$ ,<br>$0.3125 \times V_{REF}$              |      | 101  |     | ив   | В                            |

|                         | Crosstalk isolation (8)                                        | Aggressor channel input overdriven to 2 × maximum input voltage                                                                                 |      | 110  |     | dB   | В                            |

|                         | Crosstalk memory (9)                                           | Aggressor channel input overdriven to 2 × maximum input voltage                                                                                 |      | 90   |     | dB   | В                            |

| BW <sub>(-3 dB)</sub>   | Small-signal bandwidth, –3 dB                                  | At T <sub>A</sub> = 25°C, all input ranges                                                                                                      |      | 15   |     | kHz  | В                            |

| BW <sub>(-0.1 dB)</sub> | Small-signal bandwidth, -0.1 dB                                | At T <sub>A</sub> = 25°C, all input ranges                                                                                                      |      | 2.5  |     | kHz  | В                            |

<sup>(7)</sup> Calculated on the first nine harmonics of the input frequency.

<sup>(8)</sup> Isolation crosstalk is measured by applying a full-scale sinusoidal signal up to 10 kHz to a channel, not selected in the multiplexing sequence, and measuring its effect on the output of any selected channel.

<sup>(9)</sup> Memory crosstalk is measured by applying a full-scale sinusoidal signal up to 10 kHz to a channel that is selected in the multiplexing sequence, and measuring its effect on the output of the next selected channel for all combinations of input channels.

www.ti.com SBAS813 – JUNE 2018

# **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

| SAMPLE - 000                             | PARAMETER                                                 | TEST CONDITIONS                                                  | MIN   | TYP   | MAX       | UNIT   | TEST<br>LEVEL <sup>(1)</sup> |

|------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|-------|-------|-----------|--------|------------------------------|

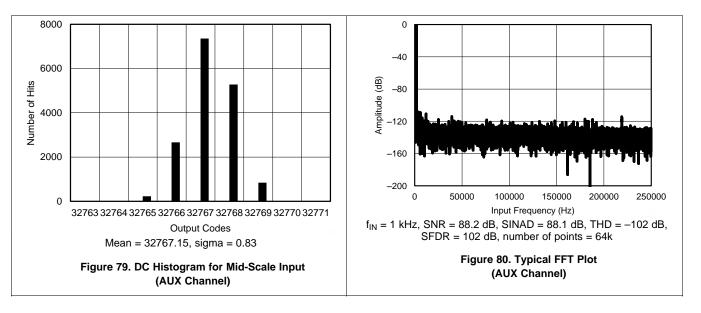

| AUXILIARY CH                             | IANNEL                                                    |                                                                  |       |       |           |        |                              |

|                                          | Resolution                                                |                                                                  | 16    |       |           | Bits   | Α                            |

| V <sub>(AUX_IN)</sub>                    | AUX_IN voltage range                                      | (AUX_IN – AUX_GND)                                               | 0     |       | $V_{REF}$ | V      | Α                            |

|                                          | 0                                                         | AUX_IN                                                           | 0     |       | $V_{REF}$ | V      | Α                            |

|                                          | Operating input range                                     | AUX_GND                                                          |       | 0     |           | V      | Α                            |

| Ci                                       | Input conceitones                                         | During sampling                                                  |       | 75    |           | pF     | С                            |

| Ci                                       | Input capacitance                                         | During conversion                                                |       | 5     |           | pF     | С                            |

| I <sub>Ikg(in)</sub>                     | Input leakage current                                     |                                                                  |       | 100   |           | nA     | Α                            |

| DNL                                      | Differential nonlinearity                                 |                                                                  | -0.99 | ±0.6  | 2         | LSB    | Α                            |

| INL                                      | Integral nonlinearity                                     |                                                                  | -4    | ±1.5  | 4         | LSB    | Α                            |

| $E_{G(AUX)}$                             | Gain error                                                | At T <sub>A</sub> = 25°C                                         |       | ±0.02 | ±0.2      | %FSR   | Α                            |

| E <sub>O(AUX)</sub>                      | Offset error                                              | At T <sub>A</sub> = 25°C                                         | -5    |       | 5         | mV     | Α                            |

| SNR                                      | Signal-to-noise ratio                                     | $V_{(AUX_IN)} = -0.5 \text{ dBFS at 1 kHz}$                      | 87    | 89    |           | dB     | Α                            |

| THD                                      | Total harmonic distortion <sup>(7)</sup>                  | $V_{(AUX_IN)} = -0.5 \text{ dBFS at 1 kHz}$                      |       | -102  |           | dB     | В                            |

| SINAD                                    | Signal-to-noise + distortion                              | $V_{(AUX_IN)} = -0.5 \text{ dBFS at 1 kHz}$                      | 86    | 88.5  |           | dB     | Α                            |

| SFDR                                     | Spurious-free dynamic range                               | $V_{(AUX_IN)} = -0.5 \text{ dBFS at 1 kHz}$                      |       | 103   |           | dB     | В                            |

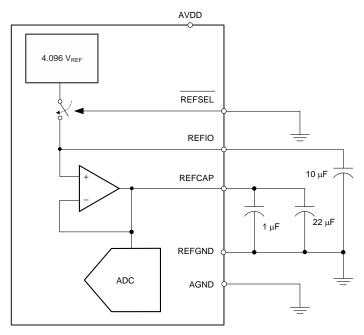

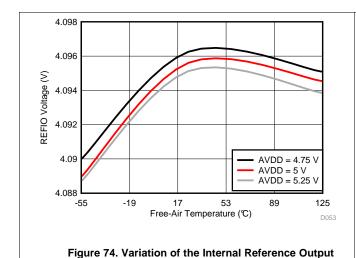

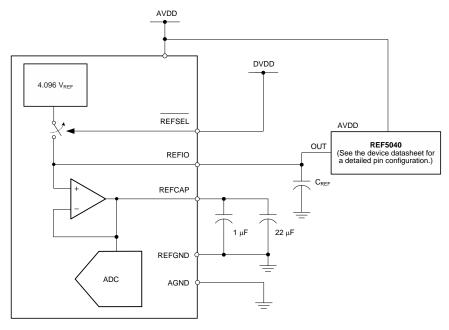

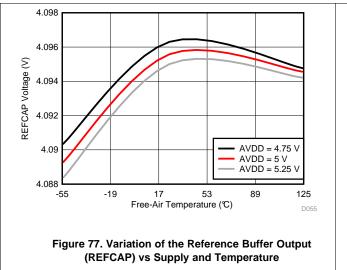

| INTERNAL REI                             | FERENCE OUTPUT                                            |                                                                  |       |       | •         |        | •                            |

| V <sub>(REFIO_INT)</sub> <sup>(10)</sup> | Voltage on REFIO pin (configured as output)               | At T <sub>A</sub> = 25°C                                         | 4.095 | 4.096 | 4.097     | V      | А                            |

|                                          | Internal reference temperature drift                      |                                                                  |       | 6     | 17        | ppm/°C | В                            |

| $C_{(OUT\_REFIO)}$                       | Decoupling capacitor on REFIO                             |                                                                  | 10    | 22    |           | μF     | В                            |

| $V_{(REFCAP)}$                           | Reference voltage to ADC (on REFCAP pin)                  | At T <sub>A</sub> = 25°C                                         | 4.095 | 4.096 | 4.097     | V      | А                            |

|                                          | Reference buffer output impedance                         |                                                                  |       | 0.5   | 1         | Ω      | В                            |

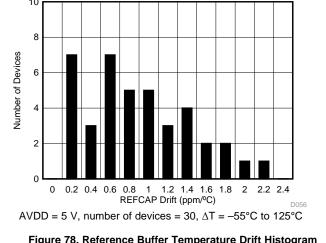

|                                          | Reference buffer temperature drift                        |                                                                  |       | 0.6   | 4.5       | ppm/°C | В                            |

| C <sub>(OUT_REFCAP)</sub>                | Decoupling capacitor on REFCAP                            |                                                                  | 10    | 22    |           | μF     | В                            |

|                                          | Turn-on time                                              | $C_{(OUT\_REFCAP)} = 22 \mu F,$<br>$C_{(OUT\_REFIO)} = 22 \mu F$ |       | 15    |           | ms     | В                            |

| EXTERNAL RE                              | FERENCE INPUT                                             |                                                                  |       |       |           |        |                              |

| V <sub>REFIO_EXT</sub>                   | External reference voltage on REFIO (configured as input) |                                                                  | 4.046 | 4.096 | 4.146     | V      | С                            |

<sup>(10)</sup> Does not include the variation in voltage resulting from solder-shift and long-term effects.

# **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

|                       | PARAMETER                       |                  | TEST CONDITIONS                                             | MIN               | TYP | MAX        | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|-----------------------|---------------------------------|------------------|-------------------------------------------------------------|-------------------|-----|------------|------|------------------------------|

| POWER-SUP             | PLY REQUIREMENTS                |                  |                                                             |                   |     |            |      | •                            |

| AVDD                  | Analog power-supply v           | oltage           | Analog supply                                               | 4.75              | 5   | 5.25       | V    | В                            |

|                       | Digital power-supply voltage    |                  | Digital supply range                                        | 1.65              | 3.3 | AVDD       |      | В                            |

| DVDD                  |                                 |                  | Digital supply range for specified performance              | 2.7 3.3 5.25      |     | V          | В    |                              |

| I <sub>AVDD_DYN</sub> |                                 | Dynamic,<br>AVDD | AVDD = 5 V, f <sub>S</sub> = maximum and internal reference |                   | 13  | 16         | mA   | А                            |

| I <sub>AVDD_STC</sub> | A 1                             | Static           | AVDD = 5 V, device not converting and internal reference    |                   | 10  | 12         | mA   | А                            |

| I <sub>STDBY</sub>    | Analog supply current           | Standby          | At AVDD = 5 V, device in STDBY mode and internal reference  |                   | 3   | 4.5        | mA   | А                            |

| I <sub>PWR_DN</sub>   | Powe                            |                  | At AVDD = 5 V, device in PWR_DN                             |                   | 3   | 20         | μΑ   | В                            |

| I <sub>DVDD_DYN</sub> | Digital supply current          |                  | At DVDD = 3.3 V, output = 0000h                             |                   | 0.5 |            | mA   | Α                            |

| DIGITAL INP           | UTS (CMOS)                      |                  |                                                             |                   |     |            |      |                              |

| \/                    | Digital input high logic levels |                  | DVDD > 2.1 V                                                | 0.7 × DVDD        |     | DVDD + 0.3 | V    | Α                            |

| $V_{IH}$              |                                 |                  | DVDD ≤ 2.1 V                                                | $0.8 \times DVDD$ |     | DVDD + 0.3 | V    | Α                            |

| M                     | Digital input low logic levels  |                  | DVDD > 2.1 V                                                | -0.3              |     | 0.3 × DVDD | V    | Α                            |

| V <sub>IL</sub>       |                                 |                  | DVDD ≤ 2.1 V                                                | -0.3              |     | 0.2 × DVDD | V    | Α                            |

|                       | Input leakage current           |                  |                                                             |                   | 100 |            | nA   | Α                            |

|                       | Input pin capacitance           |                  |                                                             |                   | 5   |            | pF   | С                            |

| DIGITAL OU            | TPUTS (CMOS)                    |                  |                                                             |                   |     |            |      |                              |

| V <sub>OH</sub>       | Digital output logic levels     |                  | I <sub>O</sub> = 500-μA source                              | 0.8 × DVDD        |     | DVDD       | V    | Α                            |

| V <sub>OL</sub>       |                                 |                  | I <sub>O</sub> = 500-μA sink                                | 0                 |     | 0.2 × DVDD | V    | Α                            |

|                       | Floating state leakage          | current          | Only for SDO                                                |                   | 1   |            | μΑ   | Α                            |

|                       | Internal pin capacitance        | е                |                                                             |                   | 5   |            | pF   | С                            |

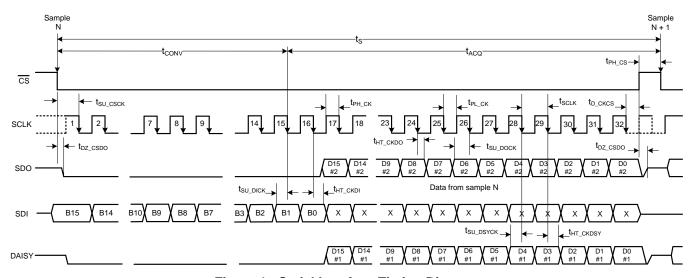

## 6.6 Timing Requirements: Serial Interface

minimum and maximum specifications are at  $T_A = -55^{\circ}\text{C}$  to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), SDO load = 20 pF, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted); typical specifications are at  $T_A = 25^{\circ}\text{C}$

|                       |                                                           | MIN  | NOM | MAX | UNIT              |

|-----------------------|-----------------------------------------------------------|------|-----|-----|-------------------|

| t <sub>ACQ</sub>      | Acquisition time                                          | 1150 |     |     | ns                |

| t <sub>PH_CK</sub>    | Clock high time                                           | 0.4  |     | 0.6 | t <sub>SCLK</sub> |

| t <sub>PL_CK</sub>    | Clock low time                                            | 0.4  |     | 0.6 | t <sub>SCLK</sub> |

| t <sub>PH_CS</sub>    | CS high time                                              | 30   |     |     | ns                |

| t <sub>SU_CSCK</sub>  | Setup time: CS falling to SCLK falling                    | 30   |     |     | ns                |

| t <sub>HT_CKDO</sub>  | Hold time: SCLK falling to (previous) data valid on SDO   | 10   |     |     | ns                |

| t <sub>SU_DOCK</sub>  | Setup time: SDO data valid to SCLK falling                | 25   |     |     | ns                |

| t <sub>SU_DICK</sub>  | Setup time: SDI data valid to SCLK falling                | 5    |     |     | ns                |

| t <sub>HT_CKDI</sub>  | Hold time: SCLK falling to (previous) data valid on SDI   | 5    |     |     | ns                |

| t <sub>SU_DSYCK</sub> | Setup time: DAISY data valid to SCLK falling              | 5    |     |     | ns                |

| t <sub>HT_CKDSY</sub> | Hold time: SCLK falling to (previous) data valid on DAISY | 5    |     |     | ns                |

# 6.7 Switching Characteristics: Serial Interface

minimum and maximum specifications are at  $T_A = -55$ °C to +125°C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), SDO load = 20 pF, and  $f_{SAMPLF}$  = 500 kSPS (unless otherwise noted); typical specifications are at  $T_A$  = 25°C

|                      | PARAMETER                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>S</sub>       | Sampling frequency (f <sub>CLK</sub> = max)     |                 |     |     | 500 | kSPS |

| t <sub>S</sub>       | ADC cycle time period (f <sub>CLK</sub> = max)  |                 | 2   |     |     | μs   |

| f <sub>SCLK</sub>    | Serial clock frequency (f <sub>S</sub> = max)   |                 |     |     | 17  | MHz  |

| t <sub>SCLK</sub>    | Serial clock time period (f <sub>S</sub> = max) |                 | 59  |     |     | ns   |

| t <sub>CONV</sub>    | Conversion time                                 |                 |     |     | 850 | ns   |

| t <sub>DZ_CSDO</sub> | Delay time: CS falling to data enable           |                 |     |     | 10  | ns   |

| t <sub>D_CKCS</sub>  | Delay time: last SCLK falling to CS rising      |                 | 10  |     |     | ns   |

| t <sub>DZ_CSDO</sub> | Delay time: CS rising to SDO going to 3-state   |                 | 10  |     |     | ns   |

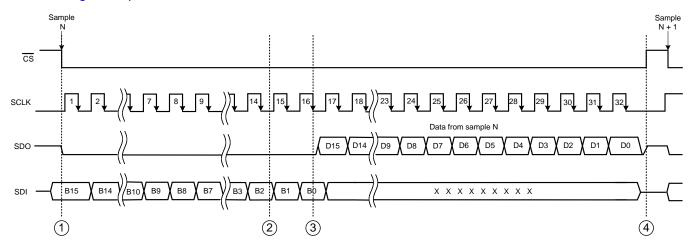

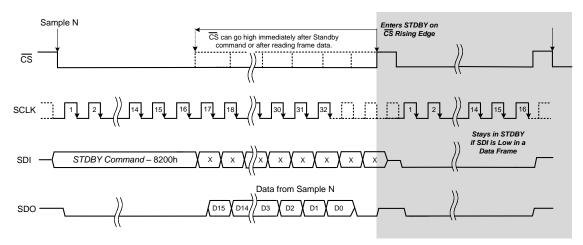

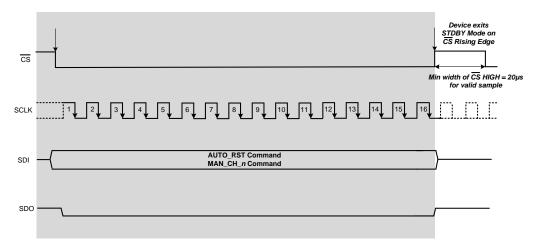

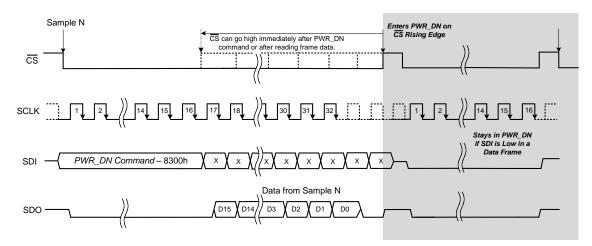

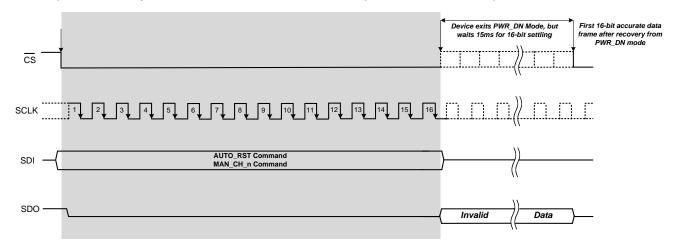

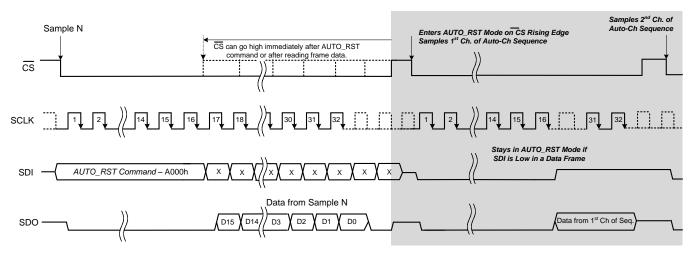

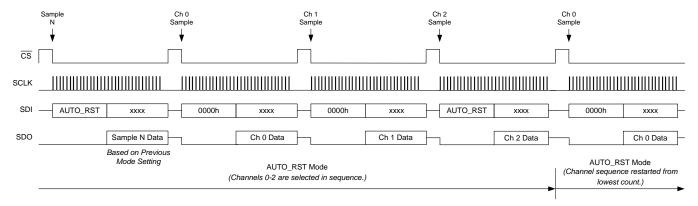

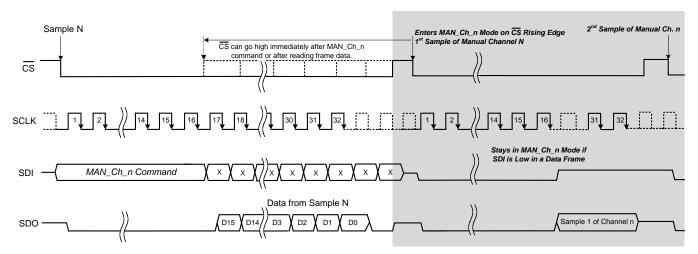

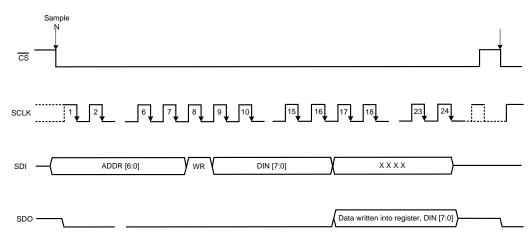

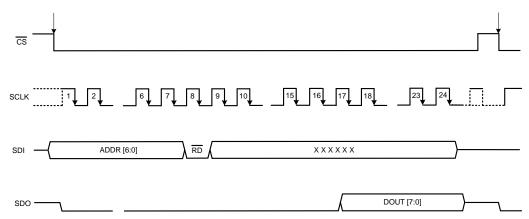

Figure 1. Serial Interface Timing Diagram

Submit Documentation Feedback Copyright © 2018, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

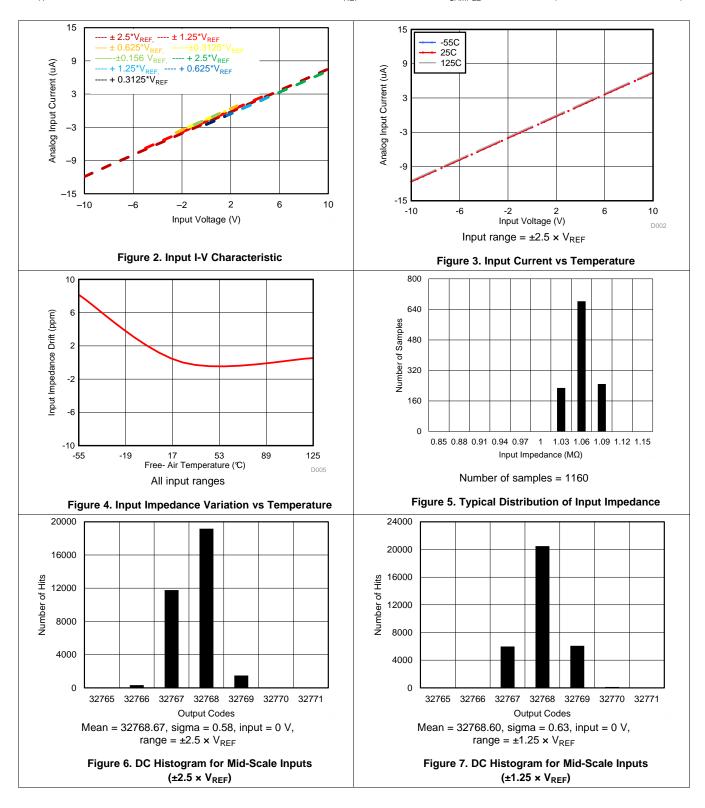

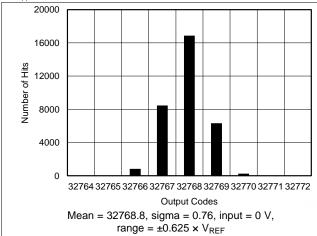

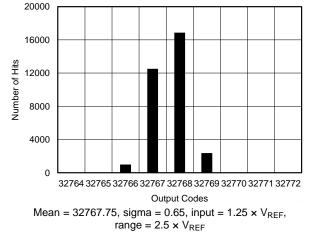

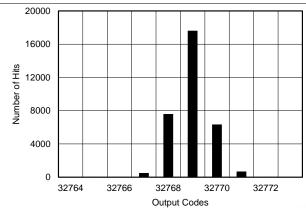

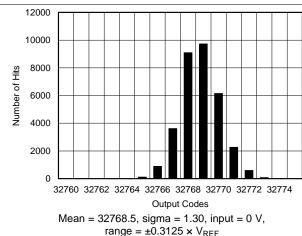

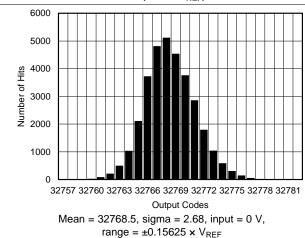

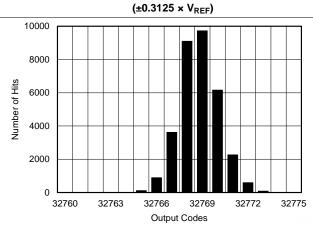

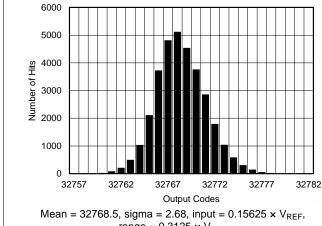

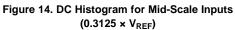

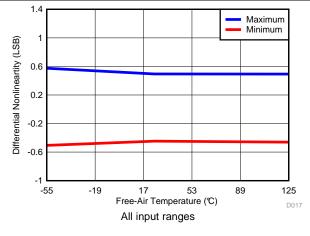

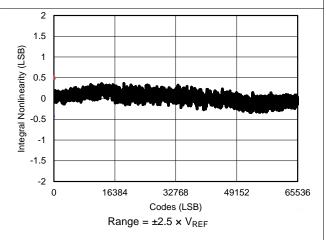

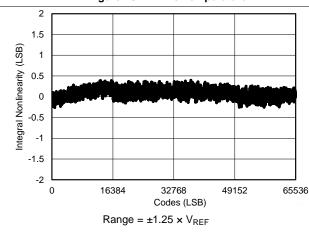

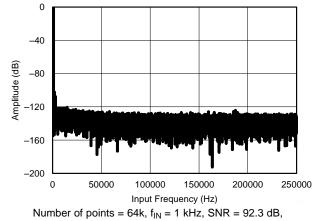

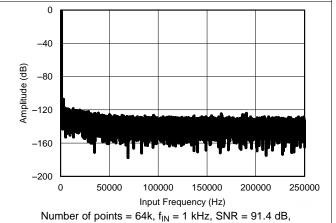

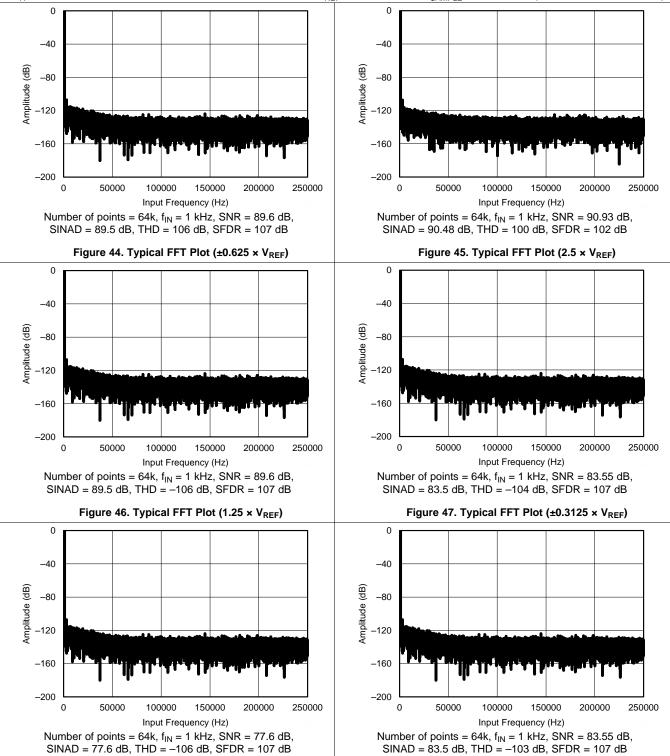

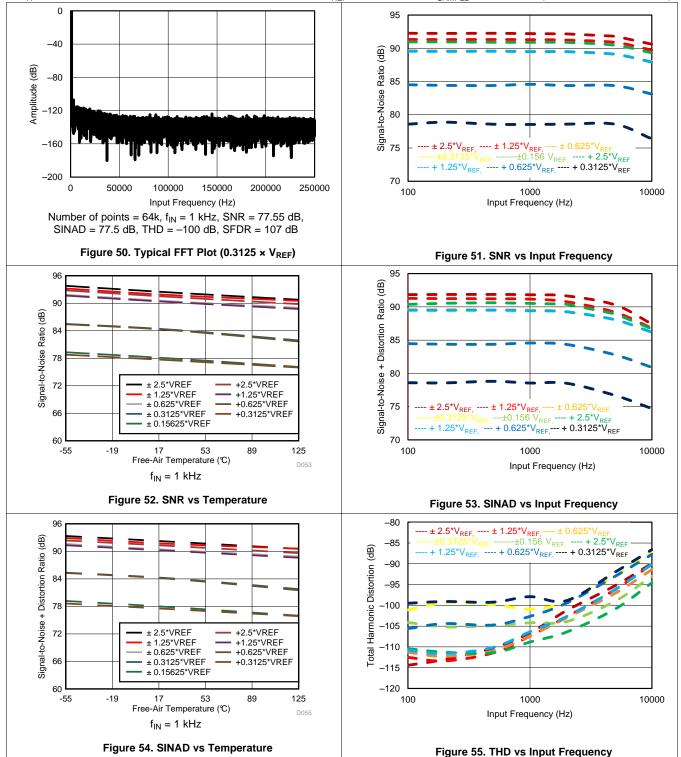

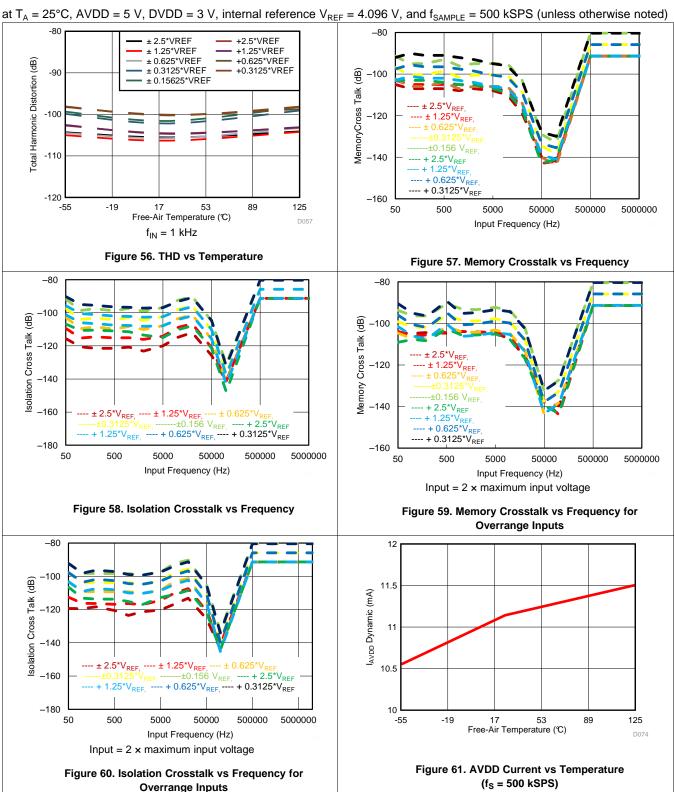

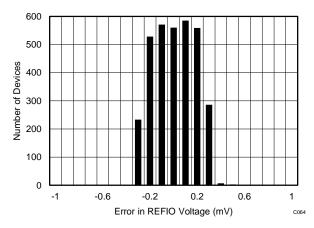

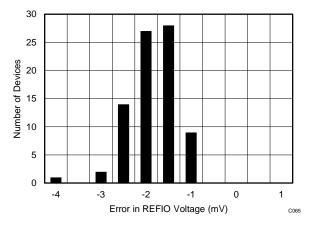

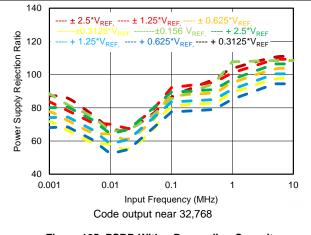

## 6.8 Typical Characteristics

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

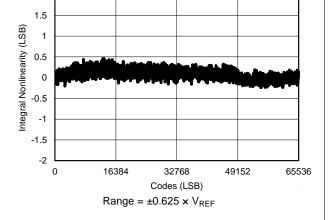

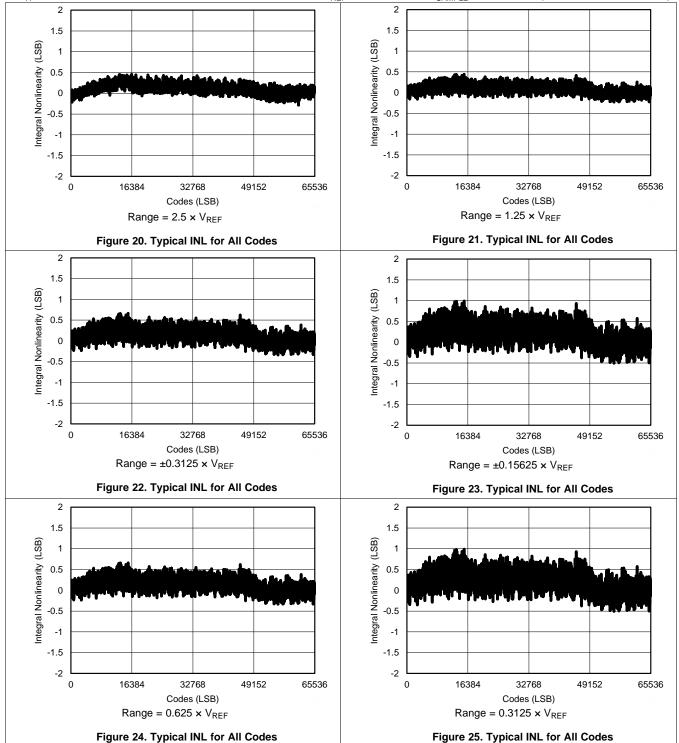

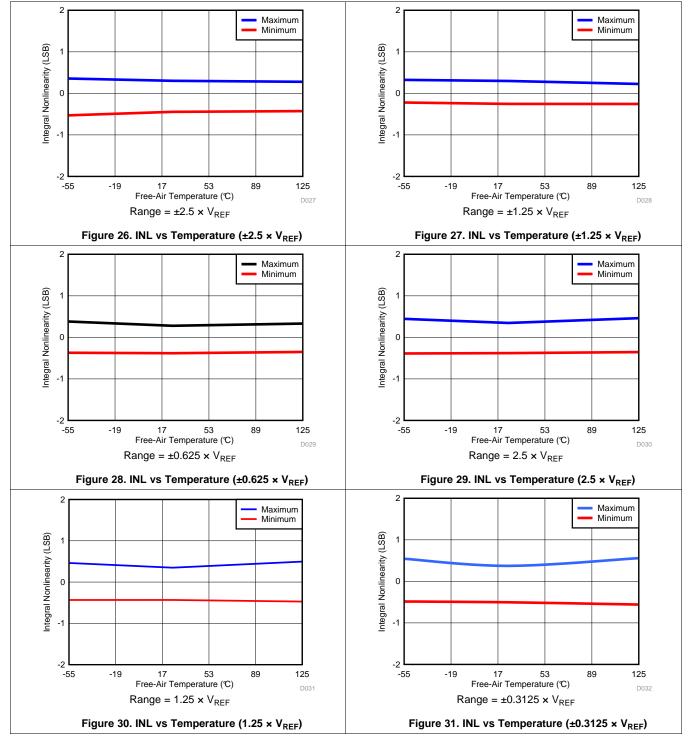

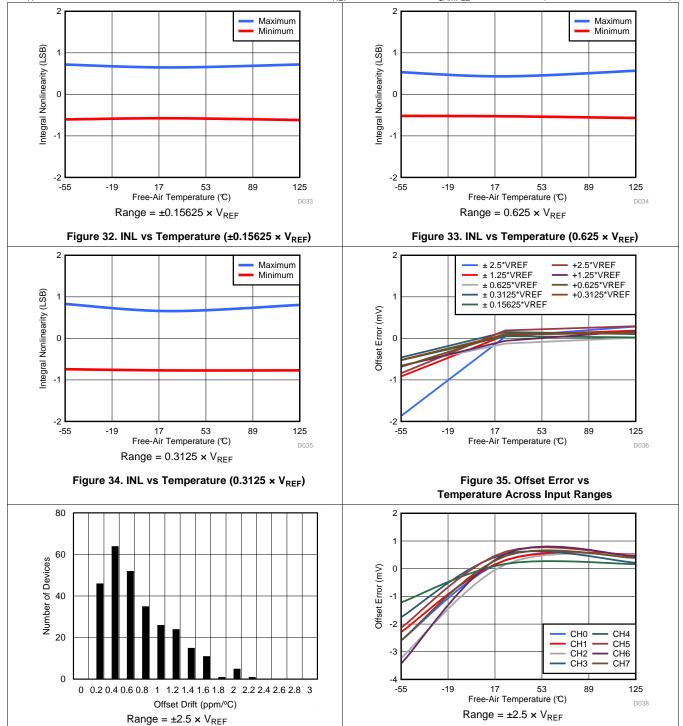

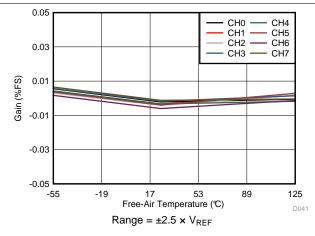

# **Typical Characteristics (continued)**

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, internal reference V<sub>REF</sub> = 4.096 V, and f<sub>SAMPLE</sub> = 500 kSPS (unless otherwise noted)

Figure 8. DC Histogram for Mid-Scale Inputs  $(\pm 0.625 \times V_{REF})$

Figure 9. DC Histogram for Mid-Scale Inputs  $(2.5 \times V_{REF})$

Mean = 32768.2, sigma = 0.75, input =  $0.625 \times V_{REF}$ , range =  $1.25 \times V_{REF}$

Figure 11. DC Histogram for Mid-Scale Inputs

# Figure 10. DC Histogram for Mid-Scale Inputs $(1.25 \times V_{REF})$

Figure 12. DC Histogram for Mid-Scale Inputs  $(\pm 0.15625 \times V_{REF})$

$\label{eq:Mean} \begin{aligned} \text{Mean} &= 32768.5, \, \text{sigma} = 1.30, \, \text{input} = 0.3125 \times \text{V}_{\text{REF}}, \\ &\text{range} = 0.625 \times \text{V}_{\text{REF}} \end{aligned}$

Figure 13. DC Histogram for Mid-Scale Inputs (0.625 × V<sub>REF</sub>)

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

an = 32768.5, sigma = 2.68, input = 0.15625 x  $V_{REF}$ , range = 0.3125 x  $V_{REF}$

Figure 15. Typical DNL for All Codes

Figure 16. DNL vs Temperature

Figure 17. Typical INL for All Codes

Figure 18. Typical INL for All Codes

Figure 19. Typical INL for All Codes

2

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

Figure 36. Typical Histogram for Offset Drift

Figure 37. Offset Error vs Temperature Across Channels

# NSTRUMENTS

## **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

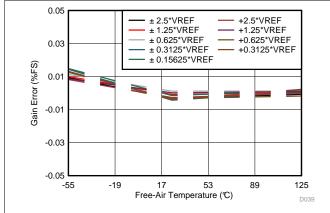

Figure 38. Gain Error vs Temperature Across Input Ranges

Figure 39. Typical Histogram for Gain Error Drift

Figure 40. Gain Error vs Temperature Across Channels

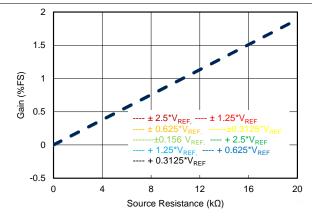

Figure 41. Gain Error vs External Resistance (R<sub>EXT</sub>)

SINAD = 91.9 dB, THD = 101 dB, SFDR = 104 dB

SINAD = 91.2 dB, THD = 105 dB, SFDR = 107 dB

Figure 42. Typical FFT Plot (±2.5 × V<sub>REF</sub>)

Figure 43. Typical FFT Plot (±1.25 × V<sub>REF</sub>)

# **Typical Characteristics (continued)**

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, internal reference V<sub>REF</sub> = 4.096 V, and f<sub>SAMPLE</sub> = 500 kSPS (unless otherwise noted)

Figure 48. Typical FFT Plot (±0.15625 × V<sub>REF</sub>)

Figure 49. Typical FFT Plot (0.625 × V<sub>REF</sub>)

## TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

T : 101 ( : : / :: 1)

# Typical Characteristics (continued)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V, internal reference  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

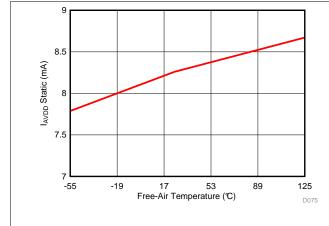

Figure 62. AVDD Current vs Temperature (During Sampling)

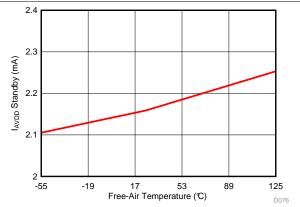

Figure 63. AVDD Current vs Temperature (STANDBY)

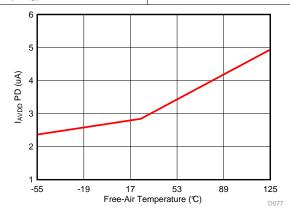

Figure 64. AVDD Current vs Temperature (Power Down)

www.ti.com SBAS813 – JUNE 2018

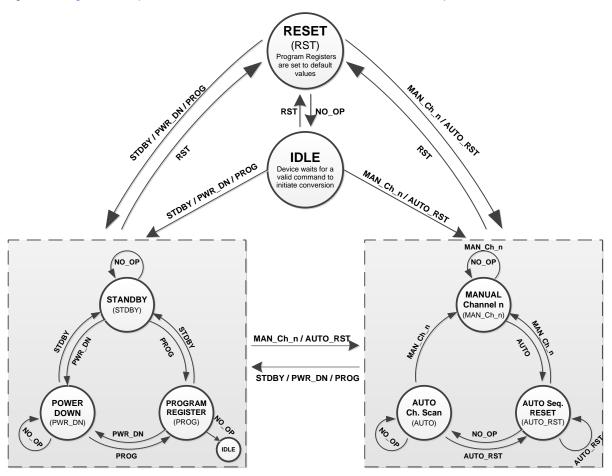

## 7 Detailed Description

#### 7.1 Overview

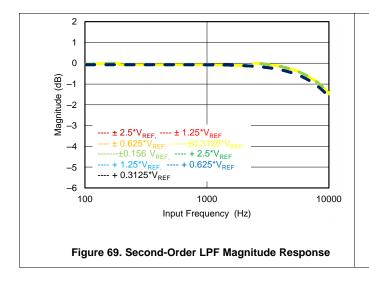

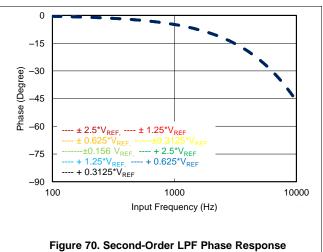

The ADS8688AT is a 16-bit data acquisition system with 8-channel analog inputs. Each analog input channel consists of an overvoltage protection circuit, a programmable gain amplifier (PGA), and a second-order, antialiasing filter that conditions the input signal before being fed into an 8-channel analog multiplexer (MUX). The output of the MUX is digitized using a 16-bit analog-to-digital converter (ADC), based on the successive approximation register (SAR) architecture. This overall system can achieve a maximum throughput of 500 kSPS, combined across all channels. The device features a 4.096-V internal reference with a fast-settling buffer and a simple SPI-compatible serial interface with daisy-chain (DAISY) and ALARM features.

The device operates from a single 5-V analog supply and can accommodate true bipolar input signals up to  $\pm 2.5 \times V_{REF}$ . The device offers a constant 1-M $\Omega$  resistive input impedance irrespective of the sampling frequency or the selected input range. The integration of multichannel precision analog front-end circuits with high input impedance and a precision ADC operating from a single 5-V supply offers a simplified end solution without requiring external high-voltage bipolar supplies and complicated driver circuits.

## 7.2 Functional Block Diagram

# TEXAS INSTRUMENTS

### 7.3 Feature Description

### 7.3.1 Analog Inputs

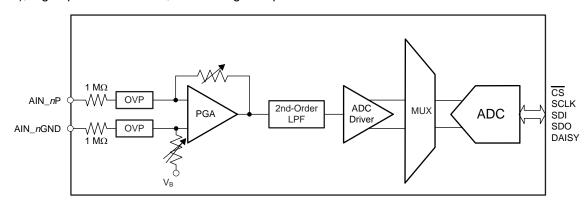

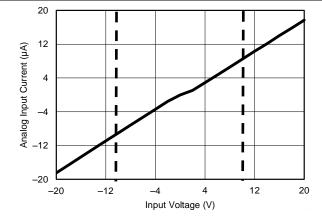

The ADS8688AT has eight analog input channels, such that the positive inputs  $AIN_nP$  (n = 0 to 7) are the single-ended analog inputs and the negative inputs  $AIN_nGND$  are tied to GND. Figure 65 shows the simplified circuit schematic for each analog input channel, including the input overvoltage protection circuit, PGA, low-pass filter (LPF), high-speed ADC driver, and analog multiplexer.

NOTE: n = 0 to 7.

Figure 65. Front-End Circuit Schematic for Each Analog Input Channel

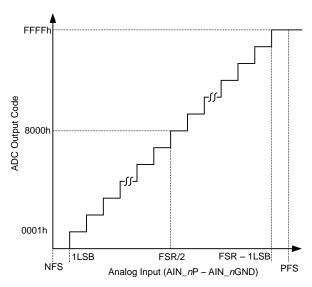

The device can support multiple unipolar or bipolar, single-ended input voltage ranges based on the configuration of the program registers. As explained in the *range select registers*, the input voltage range for each analog channel can be configured to bipolar  $\pm 2.5 \times V_{REF}$ ,  $\pm 1.25 \times V_{REF}$ ,  $\pm 0.625 \times V_{REF}$ ,  $\pm 0.3125 \times V_{REF}$ , and  $\pm 0.15625 \times V_{REF}$  or unipolar 0 to  $2.5 \times V_{REF}$ , 0 to  $1.25 \times V_{REF}$ , 0 to  $0.625 \times V_{REF}$ , and 0 to  $0.3125 \times V_{REF}$ . With the internal or external reference voltage set to 4.096 V, the input ranges of the device can be configured to bipolar ranges of  $\pm 10.24 \text{ V}$ ,  $\pm 2.56 \text{ V}$ ,  $\pm 1.28 \text{ V}$ , and  $\pm 0.64 \text{ V}$  or unipolar ranges of 0 V to  $\pm 1.24 \times 1.24 \times$

The device samples the voltage difference (AIN\_nP - AIN\_nGND) between the selected analog input channel and the AIN\_nGND pin. The device allows a ±0.1-V range on the AIN\_nGND pin for all analog input channels. This feature is useful in modular systems where the sensor or signal-conditioning block is further away from the ADC on the board and when a difference in the ground potential of the sensor or signal conditioner from the ADC ground is possible. In such cases, running separate wires from the AIN\_nGND pin of the device to the sensor or signal-conditioning ground is recommended.

If the analog input pins (AIN\_nP) to the device are left floating, the output of the ADC corresponds to an internal biasing voltage. The output from the ADC must be considered as invalid if the device is operated with floating input pins. This condition does not cause any damage to the device, which is fully functional when a valid input voltage is applied to the pins.

### 7.3.2 Analog Input Impedance

Each analog input channel in the device presents a constant resistive impedance of 1  $M\Omega$ . The input impedance is independent of either the ADC sampling frequency, the input signal frequency, or range. The primary advantage of such high-impedance inputs is the ease of driving the ADC inputs without requiring driving amplifiers with low output impedance. Bipolar, high-voltage power supplies are not required in the system because this ADC does not require any high-voltage front-end drivers. In most applications, the signal sources or sensor outputs can be directly connected to the ADC input, thus significantly simplifying the design of the signal chain.

In order to maintain the dc accuracy of the system, matching the external source impedance on the AIN\_nP input pin with an equivalent resistance on the AIN\_nGND pin is recommended. This matching helps to cancel any additional offset error contributed by the external resistance.

24

## **Feature Description (continued)**

### 7.3.3 Input Overvoltage Protection Circuit

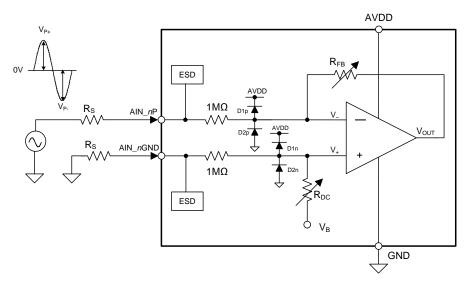

The ADS8688AT features an internal overvoltage protection circuit on each of the eight analog input channels. Use these protection circuits as a secondary protection scheme to protect the device. Using external protection devices against surges, electrostatic discharge (ESD), and electrical fast transient (EFT) conditions is highly recommended. Figure 66 shows the conceptual block diagram of the internal overvoltage protection (OVP)

Figure 66. Input Overvoltage Protection Circuit Schematic

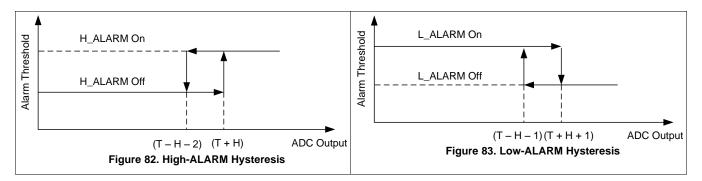

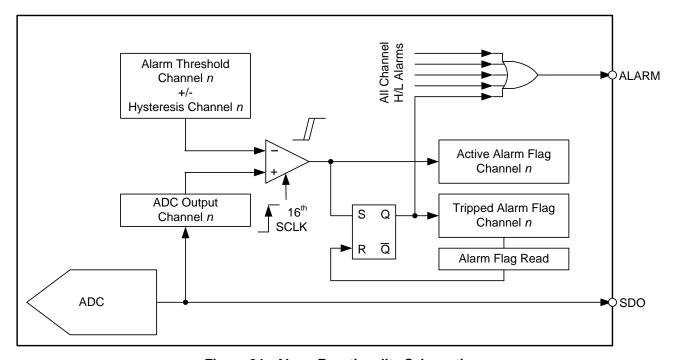

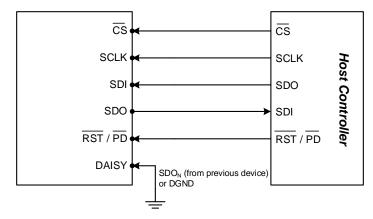

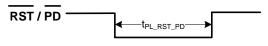

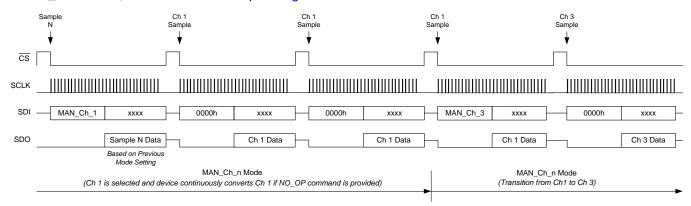

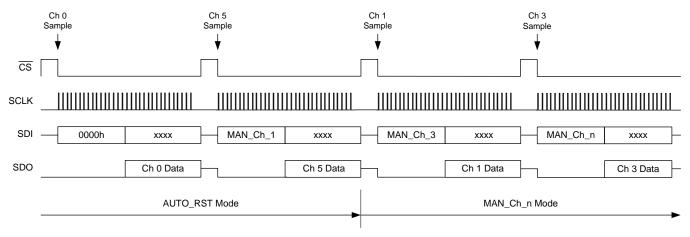

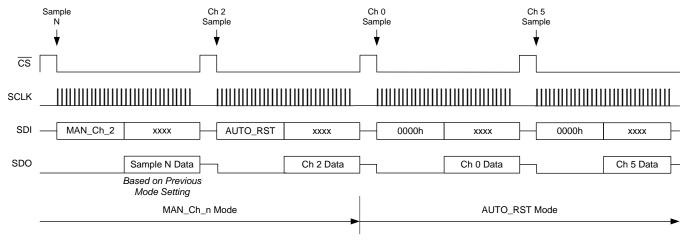

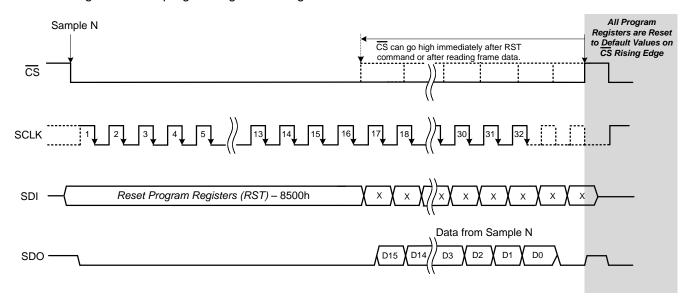

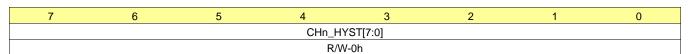

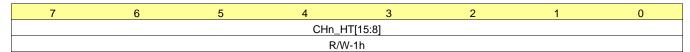

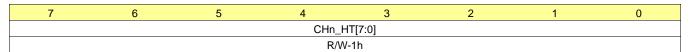

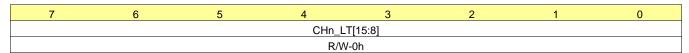

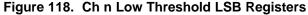

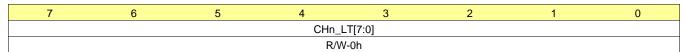

As shown in Figure 66, the combination of the 1-M $\Omega$  input resistors along with the PGA gain-setting resistors (R<sub>FB</sub> and R<sub>DC</sub>) limit the current flowing into the input pins. A combination of antiparallel diodes (D1 and D2) are added on each input pin to protect the internal circuitry and set the overvoltage protection limits.